#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Details                            |                                                                                                                     |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Product Status                     | Active                                                                                                              |

| Core Processor                     | ARM® Cortex®-A9                                                                                                     |

| Number of Cores/Bus<br>Width       | 4 Core, 32-Bit                                                                                                      |

| Speed                              | 1.0GHz                                                                                                              |

| Co-Processors/DSP                  | Multimedia; NEON™ SIMD                                                                                              |

| RAM Controllers                    | LPDDR2, LVDDR3, DDR3                                                                                                |

| Graphics Acceleration              | Yes                                                                                                                 |

| Display & Interface<br>Controllers | Keypad, LCD                                                                                                         |

| Ethernet                           | 10/100/1000Mbps (1)                                                                                                 |

| SATA                               | SATA 3Gbps (1)                                                                                                      |

| USB                                | USB 2.0 + PHY (4)                                                                                                   |

| Voltage - I/O                      | 1.8V, 2.5V, 2.8V, 3.3V                                                                                              |

| Operating Temperature              | -40°C ~ 125°C (TJ)                                                                                                  |

| Security Features                  | ARM TZ, Boot Security, Cryptography, RTIC, Secure Fusebox, Secure JTAG, Secure Memory, Secure RTC, Tamper Detection |

| Package / Case                     | 624-FBGA, FCBGA                                                                                                     |

| Supplier Device Package            | 624-FCBGA (21x21)                                                                                                   |

| Purchase URL                       | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcimx6q6avt10adr                                            |

|                                    |                                                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3 Modules List

The i.MX 6Dual/6Quad processors contain a variety of digital and analog modules. Table 2 describes these modules in alphabetical order.

| Block<br>Mnemonic | Block Name                                                                          | Subsystem                               | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------|-------------------------------------------------------------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 512x8 Fuse<br>Box | Electrical Fuse Array                                                               | Security                                | Electrical Fuse Array. Enables to setup Boot Modes, Security Levels,<br>Security Keys, and many other system parameters.<br>The i.MX 6Dual/6Quad processors consist of 512x8-bit fuse box<br>accessible through OCOTP_CTRL interface.                                                                                                                                                                                                                                                                                                                                                |

| APBH-DMA          | NAND Flash and<br>BCH ECC DMA<br>Controller                                         | System<br>Control<br>Peripherals        | DMA controller used for GPMI2 operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ARM               | ARM Platform                                                                        | ARM                                     | The ARM Cortex-A9 platform consists of 4x (four) Cortex-A9 cores<br>version r2p10 and associated sub-blocks, including Level 2 Cache<br>Controller, SCU (Snoop Control Unit), GIC (General Interrupt Controller),<br>private timers, Watchdog, and CoreSight debug modules.                                                                                                                                                                                                                                                                                                          |

| ASRC              | Asynchronous<br>Sample Rate<br>Converter                                            | Multimedia<br>Peripherals               | The Asynchronous Sample Rate Converter (ASRC) converts the sampling rate of a signal associated to an input clock into a signal associated to a different output clock. The ASRC supports concurrent sample rate conversion of up to 10 channels of about -120dB THD+N. The sample rate conversion of each channel is associated to a pair of incoming and outgoing sampling rates. The ASRC supports up to three sampling rate pairs.                                                                                                                                               |

| AUDMUX            | Digital Audio Mux                                                                   | Multimedia<br>Peripherals               | The AUDMUX is a programmable interconnect for voice, audio, and<br>synchronous data routing between host serial interfaces (for example,<br>SSI1, SSI2, and SSI3) and peripheral serial interfaces (audio and voice<br>codecs). The AUDMUX has seven ports with identical functionality and<br>programming models. A desired connectivity is achieved by configuring<br>two or more AUDMUX ports.                                                                                                                                                                                    |

| BCH40             | Binary-BCH ECC<br>Processor                                                         | System<br>Control<br>Peripherals        | The BCH40 module provides up to 40-bit ECC encryption/decryption for NAND Flash controller (GPMI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CAAM              | Cryptographic<br>Accelerator and<br>Assurance Module                                | Security                                | CAAM is a cryptographic accelerator and assurance module. CAAM<br>implements several encryption and hashing functions, a run-time integrity<br>checker, and a Pseudo Random Number Generator (PRNG). The pseudo<br>random number generator is certified by Cryptographic Algorithm<br>Validation Program (CAVP) of National Institute of Standards and<br>Technology (NIST). Its DRBG validation number is 94 and its SHS<br>validation number is 1455.<br>CAAM also implements a Secure Memory mechanism. In i.MX<br>6Dual/6Quad processors, the security memory provided is 16 KB. |

| CCM<br>GPC<br>SRC | Clock Control<br>Module, General<br>Power Controller,<br>System Reset<br>Controller | Clocks,<br>Resets, and<br>Power Control | These modules are responsible for clock and reset distribution in the system, and also for the system power management.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Table 2. | i.MX | 6Dual/6Quad | <b>Modules List</b> |

|----------|------|-------------|---------------------|

|----------|------|-------------|---------------------|

\_\_\_\_\_

| Block<br>Mnemonic                                              | Block Name                                    | Subsystem                        | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|----------------------------------------------------------------|-----------------------------------------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| GPU2Dv2                                                        | Graphics Processing<br>Unit-2D, ver. 2        | Multimedia<br>Peripherals        | The GPU2Dv2 provides hardware acceleration for 2D graphics algorithms, such as Bit BLT, stretch BLT, and many other 2D functions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| GPU2Dv4                                                        | Graphics Processing<br>Unit, ver. 4           | Multimedia<br>Peripherals        | The GPU2Dv4 provides hardware acceleration for 3D graphics algorithm with sufficient processor power to run desktop quality interactive graphic applications on displays up to HD1080 resolution. The GPU3D provide OpenGL ES 2.0, including extensions, OpenGL ES 1.1, and OpenVG 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| GPUVGv2                                                        | Vector Graphics<br>Processing Unit,<br>ver. 2 | Multimedia<br>Peripherals        | OpenVG graphics accelerator provides OpenVG 1.1 support as well as<br>other accelerations, including Real-time hardware curve tesselation of<br>lines, quadratic and cubic Bezier curves, 16x Line Anti-aliasing, and<br>various Vector Drawing functions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| HDMI Tx                                                        | HDMI Tx interface                             | Multimedia<br>Peripherals        | The HDMI module provides HDMI standard interface port to an HDMI 1.4 compliant display.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| HSI                                                            | MIPI HSI interface                            | Connectivity<br>Peripherals      | The MIPI HSI provides a standard MIPI interface to the applications processor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| l <sup>2</sup> C-1<br>l <sup>2</sup> C-2<br>l <sup>2</sup> C-3 | I <sup>2</sup> C Interface                    | Connectivity<br>Peripherals      | I <sup>2</sup> C provide serial interface for external devices. Data rates of up to 400 kbps are supported.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| IOMUXC                                                         | IOMUX Control                                 | System<br>Control<br>Peripherals | This module enables flexible IO multiplexing. Each IO pad has default and several alternate functions. The alternate functions are software configurable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| IPUv3H-1<br>IPUv3H-2                                           | Image Processing<br>Unit, ver. 3H             | Multimedia<br>Peripherals        | <ul> <li>IPUv3H enables connectivity to displays and video sources, relevant processing and synchronization and control capabilities, allowing autonomous operation.</li> <li>The IPUv3H supports concurrent output to two display ports and concurrent input from two camera ports, through the following interfaces:</li> <li>Parallel Interfaces for both display and camera</li> <li>Single/dual channel LVDS display interface</li> <li>HDMI transmitter</li> <li>MIPI/DSI transmitter</li> <li>MIPI/CSI-2 receiver</li> <li>The processing includes:</li> <li>Image conversions: resizing, rotation, inversion, and color space conversion</li> <li>A high-quality de-interlacing filter</li> <li>Video/graphics combining</li> <li>Image enhancement: color adjustment and gamut mapping, gamma correction, and contrast enhancement</li> <li>Support for display backlight reduction</li> </ul> |  |  |  |

| KPP                                                            | Key Pad Port                                  | Connectivity<br>Peripherals      | <ul> <li>KPP Supports 8 x 8 external key pad matrix. KPP features are:</li> <li>Open drain design</li> <li>Glitch suppression circuit design</li> <li>Multiple keys detection</li> <li>Standby key press detection</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| Block<br>Mnemonic | Block Name                                  | Subsystem                        | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------|---------------------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ROM<br>96KB       | Boot ROM                                    | Internal<br>Memory               | Supports secure and regular Boot Modes. Includes read protection on 4K region for content protection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ROMCP             | ROM Controller with Patch                   | Data Path                        | ROM Controller with ROM Patch support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SATA              | Serial ATA                                  | Connectivity<br>Peripherals      | The SATA controller and PHY is a complete mixed-signal IP solution designed to implement SATA II, 3.0 Gbps HDD connectivity.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SDMA              | Smart Direct Memory<br>Access               | System<br>Control<br>Peripherals | <ul> <li>The SDMA is multi-channel flexible DMA engine. It helps in maximizing system performance by off-loading the various cores in dynamic data routing. It has the following features:</li> <li>Powered by a 16-bit Instruction-Set micro-RISC engine</li> <li>Multi-channel DMA supporting up to 32 time-division multiplexed DMA channels</li> <li>48 events with total flexibility to trigger any combination of channels</li> <li>Memory accesses including linear, FIFO, and 2D addressing</li> <li>Shared peripherals between ARM and SDMA</li> <li>Very fast context-switching with 2-level priority based preemptive multi-tasking</li> <li>DMA units with auto-flush and prefetch capability</li> <li>Flexible address management for DMA transfers (increment, decrement, and no address changes on source and destination address)</li> <li>DMA ports can handle unit-directional and bi-directional flows (copy mode)</li> <li>Up to 8-word buffer for configurable burst transfers</li> <li>Support of byte-swapping and CRC calculations</li> <li>Library of Scripts and API is available</li> </ul> |

| SJC               | System JTAG<br>Controller                   | System<br>Control<br>Peripherals | The SJC provides JTAG interface, which complies with JTAG TAP standards, to internal logic. The i.MX 6Dual/6Quad processors use JTAG port for production, testing, and system debugging. In addition, the SJC provides BSR (Boundary Scan Register) standard support, which complies with IEEE1149.1 and IEEE1149.6 standards. The JTAG port must be accessible during platform initial laboratory bring-up, for manufacturing tests and troubleshooting, as well as for software debugging by authorized entities. The i.MX 6Dual/6Quad SJC incorporates three security modes for protecting against unauthorized accesses. Modes are selected through eFUSE configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SNVS              | Secure Non-Volatile<br>Storage              | Security                         | Secure Non-Volatile Storage, including Secure Real Time Clock, Security State Machine, Master Key Control, and Violation/Tamper Detection and reporting.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SPDIF             | Sony Philips Digital<br>Interconnect Format | Multimedia<br>Peripherals        | A standard audio file transfer format, developed jointly by the Sony and Phillips corporations. It supports Transmitter and Receiver functionality.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

# Table 2. i.MX 6Dual/6Quad Modules List (continued)

| _ | _ |                   |   |   |  |

|---|---|-------------------|---|---|--|

|   |   | $\mathbf{\nabla}$ |   |   |  |

|   |   |                   | 7 |   |  |

|   |   |                   |   | _ |  |

|   |   | $\mathbf{A}$      |   |   |  |

| Table 2. i.MX 6Dual/6Quad Modules List (continued) |

|----------------------------------------------------|

|----------------------------------------------------|

| Block<br>Mnemonic             | Block Name                                                                             | Subsystem                   | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|-------------------------------|----------------------------------------------------------------------------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| uSDHC-1<br>uSDHC-2<br>uSDHC-4 | SD/MMC and SDXC<br>Enhanced<br>Multi-Media Card /<br>Secure Digital Host<br>Controller | Connectivity<br>Peripherals | <ul> <li>i.MX 6Dual/6Quad specific SoC characteristics:</li> <li>All four MMC/SD/SDIO controller IPs are identical and are based on the uSDHC IP. They are:</li> <li>Conforms to the SD Host Controller Standard Specification version 3.0</li> <li>Fully compliant with MMC command/response sets and Physical Layer as defined in the Multimedia Card System Specification, v4.2/4.3/4.4/.4.1 including high-capacity (size &gt; 2 GB) cards HC MMC. Hardware reset as specified for eMMC cards is supported at ports #3 and #4 only.</li> <li>Fully compliant with SD command/response sets and Physical Layer as defined in the SD Memory Card Specifications, v3.0 including high-capacity SDHC cards up to 32 GB and SDXC cards up to 2TB.</li> <li>Fully compliant with SDI command/response sets and interrupt/read-wait mode as defined in the SDIO Card Specification, Part E1, v1.10</li> <li>Fully compliant with SD Card Specification, Part A2, SD Host Controller Standard Specification, v2.00</li> <li>All four ports support:</li> <li>1-bit or 4-bit transfer mode specifications for SD and SDIO cards up to UHS-I SDR104 mode (104 MB/s max)</li> <li>1-bit, 4-bit, or 8-bit transfer mode specifications for MMC cards up to 52 MHz in both SDR and DDR modes (104 MB/s max)</li> <li>However, the SoC-level integration and I/O muxing logic restrict the functionality to the following:</li> <li>Instances #1 and #2 are primarily intended to serve as external slots or interfaces to on-board SDIO devices. These ports are equipped with "Card Detection" and "Write Protection" pads and do not support hardware reset.</li> <li>Instances #3 and #4 are primarily intended to serve interfaces to embedded MMC memory or interfaces to on-board SDIO devices. These ports do not have "Card detection" and "Write Protection" pads and do support hardware reset.</li> <li>All ports can work with 1.8 V and 3.3 V cards. There are two completely independent I/O power domains for Ports #1 and #2 in four bit configuration (SD interface). Port #3 is placed in his own independent power doma</li></ul> |  |

| VDOA                          | VDOA                                                                                   | Multimedia<br>Peripherals   | The Video Data Order Adapter (VDOA) is used to re-order video data from the "tiled" order used by the VPU to the conventional raster-scan order needed by the IPU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| VPU                           | Video Processing<br>Unit                                                               | Multimedia<br>Peripherals   | A high-performing video processing unit (VPU), which covers many<br>SD-level and HD-level video decoders and SD-level encoders as a<br>multi-standard video codec engine as well as several important video<br>processing, such as rotation and mirroring.<br>See the i.MX 6Dual/6Quad reference manual (IMX6DQRM) for comple-<br>list of VPU's decoding/encoding capabilities.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| WDOG-1                        | Watchdog                                                                               | Timer<br>Peripherals        | The Watchdog Timer supports two comparison points during each counting period. Each of the comparison points is configurable to evoke an interrupt to the ARM core, and a second point evokes an external event on the WDOG line.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| Denne Ormerka                            | O and it is an                                                                                           | Maximum                              | Maximum Current                      |      |  |  |

|------------------------------------------|----------------------------------------------------------------------------------------------------------|--------------------------------------|--------------------------------------|------|--|--|

| Power Supply                             | Conditions                                                                                               | Power Virus                          | CoreMark                             | Unit |  |  |

| i.MX 6Quad:<br>VDD_ARM_IN + VDD_ARM23_IN | <ul> <li>ARM frequency = 996 MHz</li> <li>ARM LDOs set to 1.3V</li> <li>T<sub>j</sub> = 125°C</li> </ul> | 3920                                 | 2500                                 | mA   |  |  |

|                                          | <ul> <li>ARM frequency = 852 MHz</li> <li>ARM LDOs set to 1.3V</li> <li>T<sub>j</sub> = 125°C</li> </ul> | 3630                                 | 2260                                 | mA   |  |  |

| i.MX 6Dual: VDD_ARM_IN                   | <ul> <li>ARM frequency = 996 MHz</li> <li>ARM LDOs set to 1.3V</li> <li>T<sub>j</sub> = 125°C</li> </ul> | 2350                                 | 1500                                 | mA   |  |  |

|                                          | <ul> <li>ARM frequency = 852 MHz</li> <li>ARM LDOs set to 1.3V</li> <li>T<sub>j</sub> = 125°C</li> </ul> | 2110                                 | 1360                                 | mA   |  |  |

| i.MX 6Dual: or i.MX 6Quad:<br>VDD_SOC_IN | • Running 3DMark<br>• GPU frequency = 600 MHz<br>• SOC LDO set to $1.3V$<br>• $T_j = 125^{\circ}C$       | 2500                                 | 2500                                 |      |  |  |

| VDD_HIGH_IN                              | -                                                                                                        | 125 <sup>1</sup>                     |                                      | mA   |  |  |

| VDD_SNVS_IN                              | —                                                                                                        | 275 <sup>2</sup>                     | 275 <sup>2</sup>                     |      |  |  |

| USB_OTG_VBUS/<br>USB_H1_VBUS (LDO 3P0)   | -                                                                                                        | 25 <sup>3</sup>                      | 25 <sup>3</sup>                      |      |  |  |

|                                          | Primary Interface (IO) Supplie                                                                           | es                                   |                                      |      |  |  |

| NVCC_DRAM                                | —                                                                                                        | (see no                              | (see note <sup>4</sup> )             |      |  |  |

| NVCC_ENET                                | N=10                                                                                                     | Use maximum I                        | Use maximum IO equation <sup>5</sup> |      |  |  |

| NVCC_LCD                                 | N=29                                                                                                     | Use maximum IO equation <sup>5</sup> |                                      |      |  |  |

| NVCC_GPIO                                | N=24                                                                                                     | Use maximum I                        | D equation <sup>5</sup>              |      |  |  |

| NVCC_CSI                                 | N=20                                                                                                     | Use maximum I                        | D equation <sup>5</sup>              |      |  |  |

| NVCC_EIM0                                | N=19                                                                                                     | Use maximum I                        |                                      |      |  |  |

| NVCC_EIM1                                | N=14                                                                                                     | Use maximum I                        | C equation <sup>5</sup>              |      |  |  |

| NVCC_EIM2                                | N=20                                                                                                     | Use maximum I                        | Use maximum IO equation <sup>5</sup> |      |  |  |

| NVCC_JTAG                                | N=6                                                                                                      | Use maximum I                        | D equation <sup>5</sup>              |      |  |  |

| NVCC_RGMII                               | N=6                                                                                                      | Use maximum I                        | D equation <sup>5</sup>              |      |  |  |

| NVCC_SD1                                 | N=6                                                                                                      | Use maximum IO equation <sup>5</sup> |                                      |      |  |  |

| NVCC_SD2                                 | N=6                                                                                                      | Use maximum I                        | D equation <sup>5</sup>              |      |  |  |

| NVCC_SD3                                 | N=11                                                                                                     | Use maximum I                        | D equation <sup>5</sup>              |      |  |  |

| NVCC_NANDF                               | N=26                                                                                                     | Use maximum I                        | D equation <sup>5</sup>              |      |  |  |

| NVCC_MIPI                                | —                                                                                                        | 25.5                                 |                                      | mA   |  |  |

# Table 8. Maximum Supply Currents

# 4.7.1 General Purpose I/O AC Parameters

The I/O AC parameters for GPIO in slow and fast modes are presented in the Table 27 and Table 28, respectively. Note that the fast or slow I/O behavior is determined by the appropriate control bits in the IOMUXC control registers.

| Parameter                                                             | Symbol | Test Condition                                             | Min | Тур | Мах                    | Unit |

|-----------------------------------------------------------------------|--------|------------------------------------------------------------|-----|-----|------------------------|------|

| Output Pad Transition Times, rise/fall<br>(Max Drive, ipp_dse=111)    | tr, tf | 15 pF Cload, slow slew rate<br>15 pF Cload, fast slew rate | —   | _   | 2.72/2.79<br>1.51/1.54 |      |

| Output Pad Transition Times, rise/fall<br>(High Drive, ipp_dse=101)   | tr, tf | 15 pF Cload, slow slew rate<br>15 pF Cload, fast slew rate | —   | _   | 3.20/3.36<br>1.96/2.07 | ns   |

| Output Pad Transition Times, rise/fall<br>(Medium Drive, ipp_dse=100) | tr, tf | 15 pF Cload, slow slew rate<br>15 pF Cload, fast slew rate | _   | _   | 3.64/3.88<br>2.27/2.53 | 115  |

| Output Pad Transition Times, rise/fall<br>(Low Drive. ipp_dse=011)    | tr, tf | 15 pF Cload, slow slew rate<br>15 pF Cload, fast slew rate | _   | _   | 4.32/4.50<br>3.16/3.17 |      |

| Input Transition Times <sup>1</sup>                                   | trm    | _                                                          | —   | —   | 25                     | ns   |

Table 27. General Purpose I/O AC Parameters 1.8 V Mode

<sup>1</sup> Hysteresis mode is recommended for inputs with transition times greater than 25 ns.

### Table 28. General Purpose I/O AC Parameters 3.3 V Mode

| Parameter                                                             | Symbol | Test Condition                                             | Min | Тур | Мах                    | Unit |

|-----------------------------------------------------------------------|--------|------------------------------------------------------------|-----|-----|------------------------|------|

| Output Pad Transition Times, rise/fall<br>(Max Drive, ipp_dse=101)    | tr, tf | 15 pF Cload, slow slew rate<br>15 pF Cload, fast slew rate | _   | _   | 1.70/1.79<br>1.06/1.15 |      |

| Output Pad Transition Times, rise/fall<br>(High Drive, ipp_dse=011)   | tr, tf | 15 pF Cload, slow slew rate<br>15 pF Cload, fast slew rate | _   | _   | 2.35/2.43<br>1.74/1.77 | ns   |

| Output Pad Transition Times, rise/fall<br>(Medium Drive, ipp_dse=010) | tr, tf | 15 pF Cload, slow slew rate<br>15 pF Cload, fast slew rate | _   | _   | 3.13/3.29<br>2.46/2.60 |      |

| Output Pad Transition Times, rise/fall<br>(Low Drive. ipp_dse=001)    | tr, tf | 15 pF Cload, slow slew rate<br>15 pF Cload, fast slew rate | _   | _   | 5.14/5.57<br>4.77/5.15 |      |

| Input Transition Times <sup>1</sup>                                   | trm    | _                                                          | —   | —   | 25                     | ns   |

<sup>1</sup> Hysteresis mode is recommended for inputs with transition times greater than 25 ns.

# 4.8.2 DDR I/O Output Buffer Impedance

The LPDDR2 interface fully complies with JESD209-2B LPDDR2 JEDEC standard release June, 2009. The DDR3 interface fully complies with JESD79-3D DDR3 JEDEC standard release April, 2008.

Table 35 shows DDR I/O output buffer impedance of i.MX 6Dual/6Quad processors.

| Parameter Symbol           |      |                                                                                | Тур                                              |                                                  |      |

|----------------------------|------|--------------------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------------|------|

|                            |      | Test Conditions                                                                | NVCC_DRAM=1.5 V<br>(DDR3)<br>DDR_SEL=11          | NVCC_DRAM=1.2 V<br>(LPDDR2)<br>DDR_SEL=10        | Unit |

| Output Driver<br>Impedance | Rdrv | Drive Strength (DSE) =<br>000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | Hi-Z<br>240<br>120<br>80<br>60<br>48<br>40<br>34 | Hi-Z<br>240<br>120<br>80<br>60<br>48<br>40<br>34 | Ω    |

# Table 35. DDR I/O Output Buffer Impedance

### Note:

1. Output driver impedance is controlled across PVTs using ZQ calibration procedure.

2. Calibration is done against 240 W external reference resistor.

3. Output driver impedance deviation (calibration accuracy) is ±5% (max/min impedance) across PVTs.

# 4.8.3 LVDS I/O Output Buffer Impedance

The LVDS interface complies with TIA/EIA 644-A standard. See, TIA/EIA STANDARD 644-A, "Electrical Characteristics of Low Voltage Differential Signaling (LVDS) Interface Circuits" for details.

# 4.8.4 MLB 6-Pin I/O Differential Output Impedance

Table 36 shows MLB 6-pin I/O differential output impedance of i.MX 6Dual/6Quad processors.

### Table 36. MLB 6-Pin I/O Differential Output Impedance

| Parameter                     | Symbol | Test Conditions | Min | Тур | Мах | Unit |

|-------------------------------|--------|-----------------|-----|-----|-----|------|

| Differential Output Impedance | ZO     | _               | 1.6 |     |     | kΩ   |

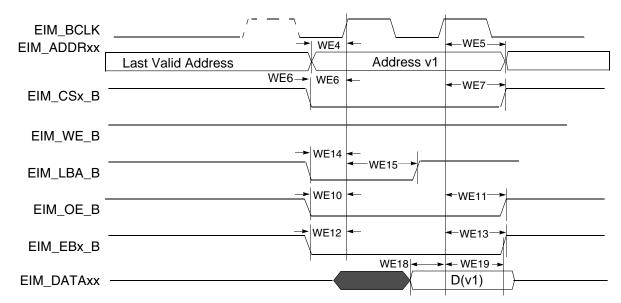

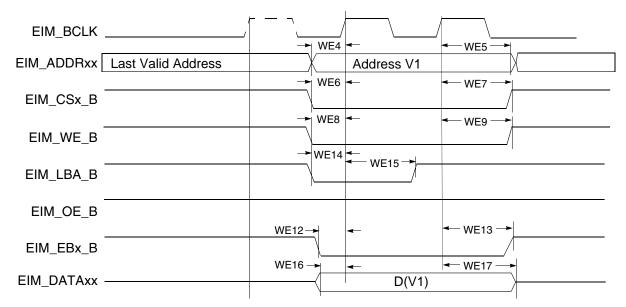

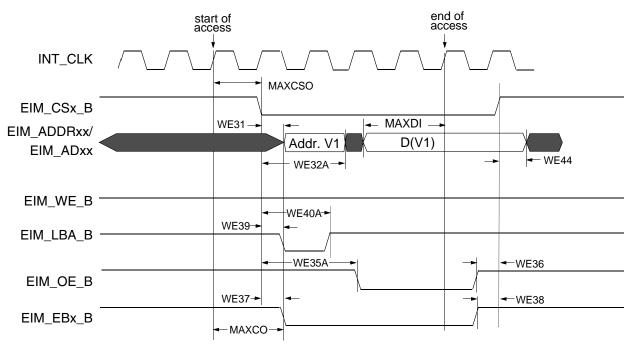

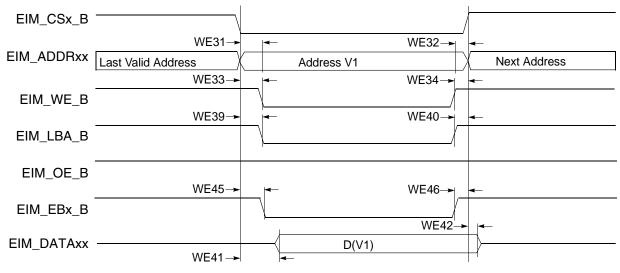

Figure 14 to Figure 17 provide few examples of basic EIM accesses to external memory devices with the timing parameters mentioned previously for specific control parameters settings.

Figure 14. Synchronous Memory Read Access, WSC=1

Figure 15. Synchronous Memory, Write Access, WSC=1, WBEA=0 and WADVN=0

Figure 20. Asynchronous Memory Write Access

1

#### **Electrical Characteristics**

# Table 48. Asynchronous Mode Timing Parameters<sup>1</sup> (continued)

| ID   | Parameter          | Symbol | Timing<br>T = GPMI Clock Cycle   |                                               | Unit |

|------|--------------------|--------|----------------------------------|-----------------------------------------------|------|

|      |                    |        | Min                              | Мах                                           |      |

| NF16 | Data setup on read | tDSR   | _                                | (DS $\times$ T $$ -0.67)/18.38 [see $^{5,6}]$ | ns   |

| NF17 | Data hold on read  | tDHR   | 0.82/11.83 [see <sup>5,6</sup> ] | —                                             | ns   |

The GPMI asynchronous mode output timing can be controlled by the module's internal registers HW\_GPMI\_TIMING0\_ADDRESS\_SETUP, HW\_GPMI\_TIMING0\_DATA\_SETUP, and HW\_GPMI\_TIMING0\_DATA\_HOLD. This AC timing depends on these registers settings. In the table, AS/DS/DH represents each of these settings.

<sup>2</sup> AS minimum value can be 0, while DS/DH minimum value is 1.

<sup>3</sup> T = GPMI clock period -0.075ns (half of maximum p-p jitter).

<sup>4</sup> NF12 is met automatically by the design.

<sup>5</sup> Non-EDO mode.

<sup>6</sup> EDO mode, GPMI clock ≈ 100 MHz (AS=DS=DH=1, GPMI\_CTL1 [RDN\_DELAY] = 8, GPMI\_CTL1 [HALF\_PERIOD] = 0).

In EDO mode (Figure 34), NF16/NF17 are different from the definition in non-EDO mode (Figure 33). They are called tREA/tRHOH (NAND\_RE\_B access time/NAND\_RE\_B HIGH to output hold). The typical value for them are 16 ns (max for tREA)/15 ns (min for tRHOH) at 50 MB/s EDO mode. In EDO mode, GPMI will sample NAND\_DATAxx at rising edge of delayed NAND\_RE\_B provided by an internal DPLL. The delay value can be controlled by GPMI\_CTRL1.RDN\_DELAY (see the GPMI chapter of the i.MX 6Dual/6Quad reference manual (IMX6DQRM)). The typical value of this control register is 0x8 at 50 MT/s EDO mode. However, if the board delay is large enough and cannot be ignored, the delay value should be made larger to compensate the board delay.

# 4.11.3 Enhanced Serial Audio Interface (ESAI) Timing Parameters

The ESAI consists of independent transmitter and receiver sections, each section with its own clock generator. Table 53 shows the interface timing values. The number field in the table refers to timing signals found in Figure 43 and Figure 44.

| ID | Parameter <sup>1,2</sup>                                                              | Symbol             | Expression <sup>2</sup>                                       | Min          | Мах          | Condition <sup>3</sup> | Unit |

|----|---------------------------------------------------------------------------------------|--------------------|---------------------------------------------------------------|--------------|--------------|------------------------|------|

| 62 | Clock cycle <sup>4</sup>                                                              | t <sub>SSICC</sub> | $\begin{array}{c} 4\times T_{C} \\ 4\times T_{C} \end{array}$ | 30.0<br>30.0 | —            | i ck<br>i ck           | ns   |

| 63 | Clock high period:<br>• For internal clock<br>• For external clock                    |                    | $2 \times T_{c} - 9.0$ $2 \times T_{c}$                       | 6<br>15      | _            | _                      | ns   |

| 64 | Clock low period:<br>• For internal clock<br>• For external clock                     |                    | $2 \times T_{c} - 9.0$ $2 \times T_{c}$                       | 6<br>15      |              |                        | ns   |

| 65 | ESAI_RX_CLK rising edge to ESAI_RX_FS out (bl) high                                   | —                  | —                                                             |              | 19.0<br>7.0  | x ck<br>i ck a         | ns   |

| 66 | ESAI_RX_CLK rising edge to ESAI_RX_FS out (bl) low                                    | —                  | —                                                             |              | 19.0<br>7.0  | x ck<br>i ck a         | ns   |

| 67 | ESAI_RX_CLK rising edge to ESAI_RX_FS out (wr)<br>high <sup>5</sup>                   | —                  | —                                                             |              | 19.0<br>9.0  | x ck<br>i ck a         | ns   |

| 68 | ESAI_RX_CLK rising edge to ESAI_RX_FS out (wr) low <sup>5</sup>                       | —                  | —                                                             |              | 19.0<br>9.0  | x ck<br>i ck a         | ns   |

| 69 | ESAI_RX_CLK rising edge to ESAI_RX_FS out (wI) high                                   |                    |                                                               |              | 19.0<br>6.0  | x ck<br>i ck a         | ns   |

| 70 | ESAI_RX_CLK rising edge to ESAI_RX_FSout (wl) low                                     | —                  | —                                                             |              | 17.0<br>7.0  | x ck<br>i ck a         | ns   |

| 71 | Data in setup time before ESAI_RX_CLK (serial clock in synchronous mode) falling edge |                    |                                                               | 12.0<br>19.0 | _            | x ck<br>i ck           | ns   |

| 72 | Data in hold time after ESAI_RX_CLK falling edge                                      |                    |                                                               | 3.5<br>9.0   | _            | x ck<br>i ck           | ns   |

| 73 | ESAI_RX_FS input (bl, wr) high before ESAI_RX_CLK falling edge <sup>5</sup>           | —                  | —                                                             | 2.0<br>19.0  | —            | x ck<br>i ck a         | ns   |

| 74 | ESAI_RX_FS input (wl) high before ESAI_RX_CLK falling edge                            | —                  | —                                                             | 2.0<br>19.0  | —            | x ck<br>i ck a         | ns   |

| 75 | ESAI_RX_FS input hold time after ESAI_RX_CLK falling edge                             |                    |                                                               | 2.5<br>8.5   | _            | x ck<br>i ck a         | ns   |

| 78 | ESAI_TX_CLK rising edge to ESAI_TX_FS out (bl) high                                   | —                  | —                                                             | _            | 19.0<br>8.0  | x ck<br>i ck           | ns   |

| 79 | ESAI_TX_CLK rising edge to ESAI_TX_FS out (bl) low                                    |                    | —                                                             |              | 20.0<br>10.0 | x ck<br>i ck           | ns   |

| 80 | ESAI_TX_CLK rising edge to ESAI_TX_FS out (wr) high <sup>5</sup>                      |                    | —                                                             |              | 20.0<br>10.0 | x ck<br>i ck           | ns   |

# Table 53. Enhanced Serial Audio Interface (ESAI) Timing

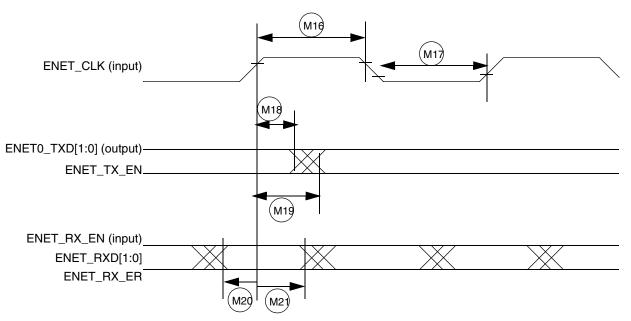

# 4.11.5.2 RMII Mode Timing

In RMII mode, ENET\_CLK is used as the REF\_CLK, which is a 50 MHz  $\pm$  50 ppm continuous reference clock. ENET\_RX\_EN is used as the ENET\_RX\_EN in RMII. Other signals under RMII mode include ENET\_TX\_EN, ENET0\_TXD[1:0], ENET\_RXD[1:0] and ENET\_RX\_ER.

Figure 52 shows RMII mode timings. Table 61 describes the timing parameters (M16–M21) shown in the figure.

Figure 52. RMII Mode Signal Timing Diagram

| Table | 61          | RMII          | Signal | Timing |

|-------|-------------|---------------|--------|--------|

| Table | <b>U</b> 1. | 1 1 1 1 1 1 1 | Jighai | rinnig |

| ID  | Characteristic                                                      | Min | Max  | Unit            |

|-----|---------------------------------------------------------------------|-----|------|-----------------|

| M16 | ENET_CLK pulse width high                                           | 35% | 65%  | ENET_CLK period |

| M17 | ENET_CLK pulse width low                                            | 35% | 65%  | ENET_CLK period |

| M18 | ENET_CLK to ENET0_TXD[1:0], ENET_TX_EN invalid                      | 4   | —    | ns              |

| M19 | ENET_CLK to ENET0_TXD[1:0], ENET_TX_EN valid                        | —   | 13.5 | ns              |

| M20 | ENET_RXD[1:0], ENET_RX_EN(ENET_RX_EN), ENET_RX_ER to ENET_CLK setup | 4   | _    | ns              |

| M21 | ENET_CLK to ENET_RXD[1:0], ENET_RX_EN, ENET_RX_ER hold              | 2   | —    | ns              |

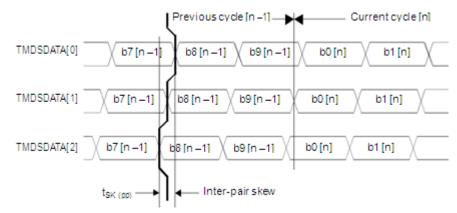

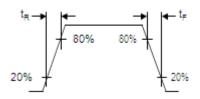

# Figure 63. TMDS Output Signals Rise and Fall Time Definition

| Symbol         | Parameter                            | Min                                                                     | Тур  | Max | Unit   |      |

|----------------|--------------------------------------|-------------------------------------------------------------------------|------|-----|--------|------|

|                | т                                    |                                                                         |      |     |        |      |

| —              | — Maximum serial data rate —         |                                                                         | _    | —   | 3.4    | Gbps |

| F<br>TMDSCLK   | TMDSCLK frequency                    | On TMDSCLKP/N outputs                                                   | 25   | —   | 340    | MHz  |

| P<br>TMDSCLK   | TMDSCLK period                       | RL = 50 Ω<br>See Figure 59.                                             | 2.94 | —   | 40     | ns   |

| t<br>CDC       | TMDSCLK duty cycle                   | $t_{CDC} = t_{CPH} / P_{TMDSCLK}$<br>RL = 50 $\Omega$<br>See Figure 59. | 40   | 50  | 60     | %    |

| t<br>CPH       | TMDSCLK high time                    | RL = 50 $\Omega$<br>See Figure 59.                                      | 4    | 5   | 6      | UI   |

| t<br>CPL       | TMDSCLK low time                     | RL = 50 $\Omega$<br>See Figure 59.                                      | 4    | 5   | 6      | UI   |

| _              | TMDSCLK jitter <sup>1</sup>          | RL = 50 Ω                                                               | _    | —   | 0.25   | UI   |

| t<br>SK(p)     | Intra-pair (pulse) skew              | RL = 50 $\Omega$<br>See Figure 61.                                      | -    | _   | 0.15   | UI   |

| t<br>SK(pp)    | Inter-pair skew                      | RL = 50 $\Omega$<br>See Figure 62.                                      | -    | -   | 1      | UI   |

| t <sub>R</sub> | Differential output signal rise time | 20-80%<br>RL = 50 $\Omega$<br>See Figure 63.                            | 75   | —   | 0.4 UI | ps   |

### Table 64. Switching Characteristics

# 4.11.10.1 IPU Sensor Interface Signal Mapping

The IPU supports a number of sensor input formats. Table 66 defines the mapping of the Sensor Interface Pins used for various supported interface formats.

| Signal<br>Name <sup>1</sup> | RGB565<br>8 bits<br>2 cycles | RGB565 <sup>2</sup><br>8 bits<br>3 cycles | RGB666 <sup>3</sup><br>8 bits<br>3 cycles | RGB888<br>8 bits<br>3 cycles | YCbCr <sup>4</sup><br>8 bits<br>2 cycles | RGB565 <sup>5</sup><br>16 bits<br>2 cycles | YCbCr <sup>6</sup><br>16 bits<br>1 cycle | YCbCr <sup>7</sup><br>16 bits<br>1 cycle | YCbCr <sup>8</sup><br>20 bits<br>1 cycle |

|-----------------------------|------------------------------|-------------------------------------------|-------------------------------------------|------------------------------|------------------------------------------|--------------------------------------------|------------------------------------------|------------------------------------------|------------------------------------------|

| IPUx_CSIx_<br>DATA00        | —                            | —                                         | —                                         | _                            |                                          | —                                          | —                                        | 0                                        | C[0]                                     |

| IPUx_CSIx_<br>DATA01        | —                            | —                                         | _                                         |                              | —                                        | _                                          | —                                        | 0                                        | C[1]                                     |

| IPUx_CSIx_<br>DATA02        | —                            | —                                         | —                                         | _                            | —                                        | -                                          | —                                        | C[0]                                     | C[2]                                     |

| IPUx_CSIx_<br>DATA03        | —                            | —                                         | —                                         | _                            | —                                        | —                                          | —                                        | C[1]                                     | C[3]                                     |

| IPUx_CSIx_<br>DATA04        | —                            | —                                         | _                                         | _                            |                                          | B[0]                                       | C[0]                                     | C[2]                                     | C[4]                                     |

| IPU2_CSIx_<br>DATA_05       | —                            | —                                         | _                                         | _                            |                                          | B[1]                                       | C[1]                                     | C[3]                                     | C[5]                                     |

| IPUx_CSIx_<br>DATA06        | —                            | —                                         | —                                         | _                            | _                                        | B[2]                                       | C[2]                                     | C[4]                                     | C[6]                                     |

| IPUx_CSIx_<br>DATA07        |                              | —                                         | _                                         | _                            |                                          | B[3]                                       | C[3]                                     | C[5]                                     | C[7]                                     |

| IPUx_CSIx_<br>DATA08        | _                            | —                                         | _                                         |                              |                                          | B[4]                                       | C[4]                                     | C[6]                                     | C[8]                                     |

| IPUx_CSIx_<br>DATA09        | —                            | —                                         | _                                         | _                            |                                          | G[0]                                       | C[5]                                     | C[7]                                     | C[9]                                     |

| IPUx_CSIx_<br>DATA10        | —                            | —                                         | —                                         | _                            |                                          | G[1]                                       | C[6]                                     | 0                                        | Y[0]                                     |

| IPUx_CSIx_<br>DATA11        | —                            | —                                         | _                                         | _                            |                                          | G[2]                                       | C[7]                                     | 0                                        | Y[1]                                     |

| IPUx_CSIx_<br>DATA12        | B[0], G[3]                   | R[2],G[4],B[2]                            | R/G/B[4]                                  | R/G/B[0]                     | Y/C[0]                                   | G[3]                                       | Y[0]                                     | Y[0]                                     | Y[2]                                     |

| IPUx_CSIx_<br>DATA13        | B[1], G[4]                   | R[3],G[5],B[3]                            | R/G/B[5]                                  | R/G/B[1]                     | Y/C[1]                                   | G[4]                                       | Y[1]                                     | Y[1]                                     | Y[3]                                     |

| IPUx_CSIx_<br>DATA14        | B[2], G[5]                   | R[4],G[0],B[4]                            | R/G/B[0]                                  | R/G/B[2]                     | Y/C[2]                                   | G[5]                                       | Y[2]                                     | Y[2]                                     | Y[4]                                     |

| IPUx_CSIx_<br>DATA15        | B[3], R[0]                   | R[0],G[1],B[0]                            | R/G/B[1]                                  | R/G/B[3]                     | Y/C[3]                                   | R[0]                                       | Y[3]                                     | Y[3]                                     | Y[5]                                     |

| IPUx_CSIx_<br>DATA16        | B[4], R[1]                   | R[1],G[2],B[1]                            | R/G/B[2]                                  | R/G/B[4]                     | Y/C[4]                                   | R[1]                                       | Y[4]                                     | Y[4]                                     | Y[6]                                     |

| IPUx_CSIx_<br>DATA17        | G[0], R[2]                   | R[2],G[3],B[2]                            | R/G/B[3]                                  | R/G/B[5]                     | Y/C[5]                                   | R[2]                                       | Y[5]                                     | Y[5]                                     | Y[7]                                     |