Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Core Processor  Core Size  | ST7 8-Bit                                                             |

|----------------------------|-----------------------------------------------------------------------|

| Speed                      | 8MHz                                                                  |

| Connectivity               | CANbus, I <sup>2</sup> C, SCI, SPI                                    |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 64                                                                    |

| Program Memory Size        | 60KB (60K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 2K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                           |

| Data Converters            | A/D 16x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 80-LQFP                                                               |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f521m9tce |

ST72521xx-Auto List of tables

| Table 49.  | PWM frequency versus resolution                     |     |

|------------|-----------------------------------------------------|-----|

| Table 50.  | PWMCR register description                          |     |

| Table 51.  | PWM output signal polarity selection                |     |

| Table 52.  | PWMDCRx register description                        |     |

| Table 53.  | ARTICCSR register description                       |     |

| Table 54.  | ARTICRx register description                        |     |

| Table 55.  | PWM auto-reload timer register map and reset values |     |

| Table 56.  | Effect of low power modes on 16-bit timer           |     |

| Table 57.  | 16-bit timer interrupt control/wake-up capability   |     |

| Table 58.  | Timer modes                                         |     |

| Table 59.  | CR1 register description                            |     |

| Table 60.  | CR2 register description                            |     |

| Table 61.  | Timer clock selection                               |     |

| Table 62.  | CSR register description                            |     |

| Table 63.  | 16-bit timer register map and reset values          |     |

| Table 64.  | Effect of low power modes on SPI                    |     |

| Table 65.  | SPI interrupt control/wake-up capability            |     |

| Table 66.  | SPICR register description                          |     |

| Table 67.  | SPI master mode SCK frequency                       |     |

| Table 68.  | SPICSR register description                         |     |

| Table 69.  | SPI register map and reset values                   |     |

| Table 70.  | Frame formats                                       |     |

| Table 71.  | Effect of low power modes on SCI                    |     |

| Table 72.  | SCI interrupt control/wake-up capability            |     |

| Table 73.  | SCISR register description                          |     |

| Table 74.  | SCICR1 register description                         |     |

| Table 75.  | SCICR2 register description                         |     |

| Table 76.  | SCIBRR register description                         |     |

| Table 77.  | SCIERPR register description                        |     |

| Table 78.  | SCIETPR register description                        |     |

| Table 79.  | Baud rate selection                                 |     |

| Table 80.  | SCI register map and reset values                   |     |

| Table 81.  | Effect of low power modes on I2C                    |     |

| Table 82.  | I2C interrupt control/wake-up capability            |     |

| Table 83.  | CR register description                             |     |

| Table 84.  | SR1 register description                            |     |

| Table 85.  | SR2 register description                            |     |

| Table 86.  | CCR register description                            |     |

| Table 87.  | DR register description                             |     |

| Table 88.  | OAR1 register description                           |     |

| Table 89.  | OAR2 register description                           |     |

| Table 90.  | I2C register map and reset values                   |     |

| Table 91.  | ISR register description                            |     |

| Table 92.  | ICR register description                            |     |

| Table 93.  | CSR register description                            |     |

| Table 94.  | BRPR register description                           |     |

| Table 95.  | BTR register description                            |     |

| Table 96.  | PSR register description                            |     |

| Table 97.  | LIDHR register description                          |     |

| Table 98.  | LIDLR register description                          |     |

| Table 99.  | TECR register description                           |     |

| Table 100. | RECR register description                           | 189 |

ST72521xx-Auto List of tables

| Table 153. | I <sup>2</sup> C control interface characteristics           | . 247 |

|------------|--------------------------------------------------------------|-------|

| Table 154. | SCL frequency table                                          | . 248 |

| Table 155. | CAN characteristics                                          | . 249 |

| Table 156. | 10-bit ADC characteristics                                   | . 249 |

| Table 157. | ADC accuracy                                                 | . 252 |

| Table 158. | 80-pin low profile quad flat package mechanical data         | . 253 |

| Table 159. | 64-pin (14x14) low profile quad flat package mechanical data | . 254 |

| Table 160. | 64-pin (10x10) low profile quad flat package mechanical data | . 255 |

| Table 161. | Thermal characteristics                                      | . 256 |

| Table 162. | Flash option bytes                                           | . 257 |

| Table 163. | Option byte 0 bit description                                | . 257 |

| Table 164. | Option byte 1 bit description                                | . 258 |

| Table 165. | Package selection (OPT7)                                     | . 259 |

| Table 166. | Oscillator frequency range selection (OPT3:1)                | . 259 |

| Table 167. | STMicroelectronics development tools                         | . 266 |

| Table 168. | Suggested list of socket types                               | . 266 |

| Table 169. | CAN cell limitations                                         | . 273 |

| Table 170. | Document revision history                                    | . 275 |

Description ST72521xx-Auto

8-bit CORE PROGRAM MEMORY (32 or 60 Kbytes) ALU RESET — CONTROL  $V_{PP} \longleftrightarrow \Box$ RAM TLI → [ 1024 or 2048 bytes V<sub>SS</sub>\_ LVD V<sub>DD</sub> \_ EVD → AVD WATCHDOG OSC1 ←→ osc OSC2 ←→ I2C PA7:0 (8-bits) ADDRESS AND DATA BUS MCC/RTC/BEEP PORT A PORT F PORT B PF7:0 (8-bits) PB7:0 (8-bits) TIMER A PWM ART BEEP PORT C PORT E PC7:0 (8-bits) PE7:0 (8-bits) TIMER B CAN SPI SCI PG7:0 (8-bits) PORT G<sup>(1)</sup> PORT D PD7:0 (8-bits) PH7:0 (8-bits) 10-bit ADC PORT H<sup>(1)</sup>  $V_{AREF}$

Figure 1. Device block diagram

1. On certain devices only (see Section Table 3.: Device pin description on page 23)

Table 4. Hardware register map (continued)

| Address        | Block                  | Register label | Register name                            | Reset status | Remarks    |

|----------------|------------------------|----------------|------------------------------------------|--------------|------------|

| 0031h          |                        | TACR2          | Timer A Control Register 2               | 00h          | R/W        |

| 0032h          |                        | TACR1          | Timer A Control Register 1               | 00h          | R/W        |

| 0033h          |                        | TACSR          | Timer A Control/Status Register          | xxxx x0xx b  | R/W        |

| 0034h          |                        | TAIC1HR        | Timer A Input Capture 1 High Register    | xxh          | Read Only  |

| 0035h          |                        | TAIC1LR        | Timer A Input Capture 1 Low Register     | xxh          | Read Only  |

| 0036h          |                        | TAOC1HR        | Timer A Output Compare 1 High Register   | 80h          | R/W        |

| 0037h          |                        | TAOC1LR        | Timer A Output Compare 1 Low Register    | 00h          | R/W        |

| 0038h          | TIMER A                | TACHR          | Timer A Counter High Register            | FFh          | Read Only  |

| 0039h          |                        | TACLR          | Timer A Counter Low Register             | FCh          | Read Only  |

| 003Ah          |                        | TAACHR         | Timer A Alternate Counter High Register  | FFh          | Read Only  |

| 003Bh          |                        | TAACLR         | Timer A Alternate Counter Low Register   | FCh          | Read Only  |

| 003Ch          |                        | TAIC2HR        | Timer A Input Capture 2 High Register    | xxh          | Read Only  |

| 003Dh          |                        | TAIC2LR        | Timer A Input Capture 2 Low Register     | xxh          | Read Only  |

| 003Eh          |                        | TAOC2HR        | Timer A Output Compare 2 High Register   | 80h          | R/W        |

| 003Fh          |                        | TAOC2LR        | Timer A Output Compare 2 Low Register    | 00h          | R/W        |

| 0040h          | Reserved Area (1 byte) |                |                                          |              |            |

|                |                        | TROPO          | · , ,                                    | 001-         | DAY        |

| 0041h          |                        | TBCR2          | Timer B Control Register 2               | 00h          | R/W        |

| 0042h          |                        | TBCR1          | Timer B Control Register 1               | 00h          | R/W        |

| 0043h          |                        | TBCSR          | Timer B Control/Status Register          | xxxx x0xx b  | R/W        |

| 0044h          |                        | TBIC1HR        | Timer B Input Capture 1 High Register    | xxh          | Read Only  |

| 0045h          |                        | TBIC1LR        | Timer B Input Capture 1 Low Register     | xxh          | Read Only  |

| 0046h          |                        | TBOC1HR        | Timer B Output Compare 1 High Register   | 80h          | R/W        |

| 0047h          |                        | TBOC1LR        | Timer B Output Compare 1 Low Register    | 00h          | R/W        |

| 0048h          | TIMER B                | TBCHR          | Timer B Counter High Register            | FFh          | Read Only  |

| 0049h          |                        | TBCLR          | Timer B Counter Low Register             | FCh          | Read Only  |

| 004Ah          |                        | TBACHR         | Timer B Alternate Counter High Register  | FFh          | Read Only  |

| 004Bh          |                        | TBACLR         | Timer B Alternate Counter Low Register   | FCh          | Read Only  |

| 004Ch          |                        | TBIC2HR        | Timer B Input Capture 2 High Register    | xxh          | Read Only  |

| 004Dh          |                        | TBIC2LR        | Timer B Input Capture 2 Low Register     | xxh          | Read Only  |

| 004Eh          |                        | TBOC2HR        | Timer B Output Compare 2 High Register   | 80h          | R/W        |

| 004Fh          |                        | TBOC2LR        | Timer B Output Compare 2 Low Register    | 00h          | R/W        |

| 0050h          |                        | SCISR          | SCI Status Register                      | C0h          | Read Only  |

| 0051h          |                        | SCIDR          | SCI Data Register                        | xxh          | R/W        |

| 0052h          |                        | SCIBRR         | SCI Baud Rate Register                   | 00h          | R/W        |

| 0053h          | SCI                    | SCICR1         | SCI Control Register 1                   | x000 0000b   | R/W        |

| 0054h          | 001                    | SCICR2         | SCI Control Register 2                   | 00h          | R/W        |

| 0055h          |                        | SCIERPR        | SCI Extended Receive Prescaler Register  | 00h          | R/W        |

| 0056h          |                        |                | Reserved area                            |              |            |

| 0057h          |                        | SCIETPR        | SCI Extended Transmit Prescaler Register | 00h          | R/W        |

| 0058h<br>0059h |                        |                | Reserved Area (2 Bytes)                  |              |            |

|                |                        |                |                                          |              | R/W        |

| 005Ah          |                        | CANISR         | CAN Interrupt Status Register            | 00h          | R/W        |

| 005Bh          |                        | CANICR         | CAN Interrupt Control Register           | 00h          | R/W        |

| 005Ch          |                        | CANCSR         | CAN Control / Status Register            | 00h          | R/W        |

| 005Dh          |                        | CANBRPR        | CAN Baud Rate Prescaler Register         | 00h          | R/W        |

| 005Eh          | CAN                    | CANBTR         | CAN Bit Timing Register                  | 23h          | R/W        |

| 005Fh          |                        | CANPSR         | CAN Page Selection Register              | 00h          | See CAN    |

| 0060h          |                        |                | First address                            |              |            |

| to             |                        |                | to                                       |              | Descriptio |

| 006Fh          |                        |                | Last address of CAN page x               |              | n          |

|                |                        |                | _                                        |              |            |

30/276 Doc ID 17660 Rev 1

# 5 Central processing unit (CPU)

### 5.1 Introduction

This CPU has a full 8-bit architecture and contains six internal registers allowing efficient 8-bit data manipulation.

### 5.2 Main features

- Enable executing 63 basic instructions

- Fast 8-bit by 8-bit multiply

- 17 main addressing modes (with indirect addressing mode)

- Two 8-bit index registers

- 16-bit stack pointer

- Low power Halt and Wait modes

- Priority maskable hardware interrupts

- Non-maskable software/hardware interrupts

# 5.3 CPU registers

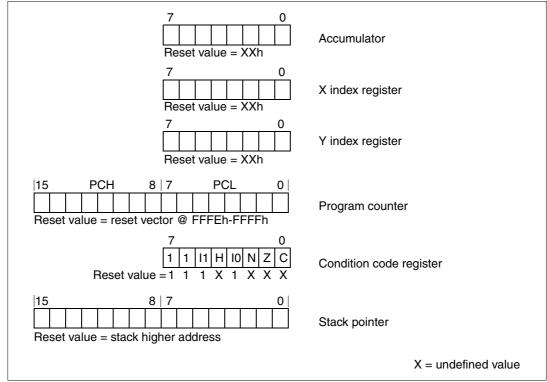

The six CPU registers shown in *Figure 7* are not present in the memory mapping and are accessed by specific instructions.

Figure 7. CPU registers

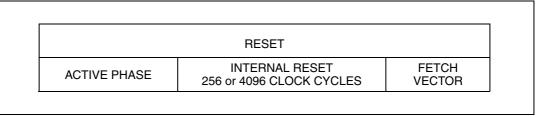

Figure 12. RESET sequence phases

### 6.5.2 Asynchronous external RESET pin

The  $\overline{\text{RESET}}$  pin is both an input and an open-drain output with integrated R<sub>ON</sub> weak pull-up resistor. This pull-up has no fixed value but varies in accordance with the input voltage. It can be pulled low by external circuitry to reset the device. See *Section 20.9: Control pin characteristics on page 240* for more details.

A RESET signal originating from an external source must have a duration of at least  $t_{h(RSTL)in}$  in order to be recognized (see *Figure 13*). This detection is asynchronous and therefore the MCU can enter reset state even in Halt mode.

The RESET pin is an asynchronous signal which plays a major role in EMS performance. In a noisy environment, it is recommended to follow the guidelines mentioned in *Section 20:* Electrical characteristics.

If the external  $\overline{\text{RESET}}$  pulse is shorter than  $t_{w(RSTL)out}$  (see short ext. Reset in *Figure 13*), the signal on the  $\overline{\text{RESET}}$  pin may be stretched. Otherwise the delay will not be applied (see long ext. Reset in *Figure 13*). Starting from the external RESET pulse recognition, the device  $\overline{\text{RESET}}$  pin acts as an output that is pulled low during at least  $t_{w(RSTL)out}$ .

### 6.5.3 External power-on RESET

If the LVD is disabled by option byte, to start up the microcontroller correctly, the user must ensure by means of an external reset circuit that the reset signal is held low until  $V_{DD}$  is over the minimum level specified for the selected  $f_{OSC}$  frequency (see *Section 20.3: Operating conditions on page 221*).

A proper reset signal for a slow rising  $V_{DD}$  supply can generally be provided by an external RC network connected to the  $\overline{RESET}$  pin.

### 6.5.4 Internal low voltage detector (LVD) RESET

Two different RESET sequences caused by the internal LVD circuitry can be distinguished:

- Power-on RESET

- Voltage drop RESET

The device  $\overline{\text{RESET}}$  pin acts as an output that is pulled low when  $V_{DD} < V_{IT+}$  (rising edge) or  $V_{DD} < V_{IT-}$  (falling edge) as shown in *Figure 13*.

The LVD filters spikes on  $V_{DD}$  larger than  $t_{\alpha(VDD)}$  to avoid parasitic resets.

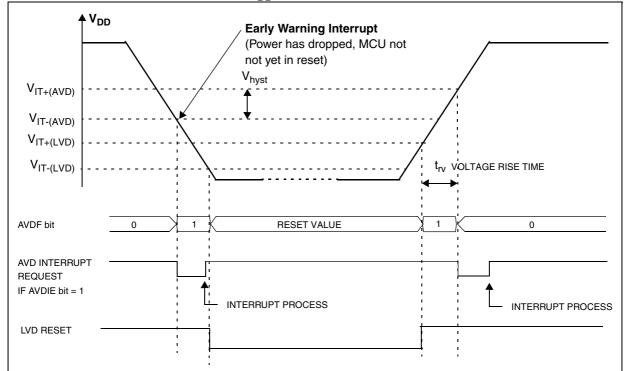

Figure 15. Using the AVD to monitor  $V_{DD}$  (AVDS bit = 0)

#### Monitoring a voltage on the EVD pin

This mode is selected by setting the AVDS bit in the SICSR register.

The AVD circuitry can generate an interrupt when the AVDIE bit of the SICSR register is set. This interrupt is generated on the rising and falling edges of the comparator output. This means it is generated when either one of these two events occur:

- V<sub>EVD</sub> rises up to V<sub>IT+(EVD)</sub>

- V<sub>EVD</sub> falls down to V<sub>IT-(EVD)</sub>

The EVD function is illustrated in Figure 16.

For more details, refer to Section 20: Electrical characteristics.

ST72521xx-Auto Interrupts

flag is set in the peripheral status registers and if the corresponding enable bit is set in the peripheral control register.

The general sequence for clearing an interrupt is based on an access to the status register followed by a read or write to an associated register.

Note:

The clearing sequence resets the internal latch. A pending interrupt (that is, waiting to be serviced) will therefore be lost if the clear sequence is executed.

## 7.3 Interrupts and low power modes

All interrupts allow the processor to exit the Wait low power mode. On the contrary, only external and other specified interrupts allow the processor to exit from the Halt modes (see column "Exit from Halt/Active Halt" in *Table 20: Interrupt mapping*). When several pending interrupts are present while exiting Halt mode, the first one serviced can only be an interrupt with "exit from Halt mode" capability and it is selected through the same decision process shown in *Figure 18*.

Note:

If an interrupt that is not able to exit from Halt mode is pending with the highest priority when exiting Halt mode, this interrupt is serviced after the first one serviced.

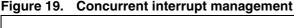

## 7.4 Concurrent and nested management

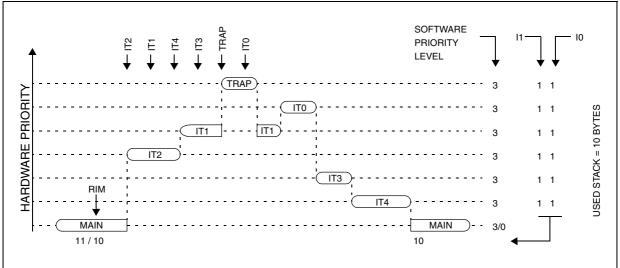

The following *Figure 19* and *Figure 20* show two different interrupt management modes. The first is called concurrent mode and does not allow an interrupt to be interrupted, unlike the nested mode in *Figure 20*. The interrupt hardware priority is given in this order from the lowest to the highest: MAIN, IT4, IT3, IT2, IT1, IT0, TLI. The software priority is given for each interrupt.

Warning: A stack overflow may occur without notifying the software of the failure.

ST72521xx-Auto I/O ports

Table 34. I/O port register map and reset values

| Address (Hex.)     | Register label                        | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

|--------------------|---------------------------------------|-----|---|---|---|---|---|---|-----|

| Reset value of all | Reset value of all I/O port registers |     | 0 | 0 | 0 | 0 | 0 | 0 | 0   |

| 0000h              | PADR                                  |     |   |   |   |   |   |   |     |

| 0001h              | PADDR                                 | MSB |   |   |   |   |   |   | LSB |

| 0002h              | PAOR                                  |     |   |   |   |   |   |   |     |

| 0003h              | PBDR                                  |     |   |   |   |   |   |   |     |

| 0004h              | PBDDR                                 | MSB |   |   |   |   |   |   | LSB |

| 0005h              | PBOR                                  |     |   |   |   |   |   |   |     |

| 0006h              | PCDR                                  |     |   |   |   |   |   |   |     |

| 0007h              | PCDDR                                 | MSB |   |   |   |   |   |   | LSB |

| 0008h              | PCOR                                  |     |   |   |   |   |   |   |     |

| 0009h              | PDDR                                  |     |   |   |   |   |   |   |     |

| 000Ah              | PDDDR                                 | MSB |   |   |   |   |   |   | LSB |

| 000Bh              | PDOR                                  |     |   |   |   |   |   |   |     |

| 000Ch              | PEDR                                  |     |   |   |   |   |   |   |     |

| 000Dh              | PEDDR                                 | MSB |   |   |   |   |   |   | LSB |

| 000Eh              | PEOR                                  |     |   |   |   |   |   |   |     |

| 000Fh              | PFDR                                  |     |   |   |   |   |   |   |     |

| 0010h              | PFDDR                                 | MSB |   |   |   |   |   |   | LSB |

| 0011h              | PFOR                                  |     |   |   |   |   |   |   |     |

| 0012h              | PGDR                                  |     |   |   |   |   |   |   |     |

| 0013h              | PGDDR                                 | MSB |   |   |   |   |   |   | LSB |

| 0014h              | PGOR                                  |     |   |   |   |   |   |   |     |

| 0015h              | PHDR                                  |     |   |   |   |   |   |   |     |

| 0016h              | PHDDR                                 | MSB |   |   |   |   |   |   | LSB |

| 0017h              | PHOR                                  |     |   |   |   |   |   |   |     |

## **Related documentation**

SPI Communication between ST7 and EEPROM (AN 970)

S/W implementation of I2C bus master (AN1045)

Software LCD driver (AN1048)

# 11.8 Main clock controller registers

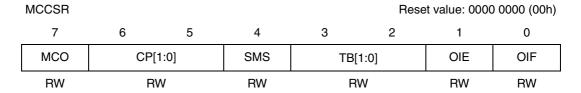

## 11.8.1 MCC control/status register (MCCSR)

Table 40. MCCSR register description

| Bit | Name    | Function                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | МСО     | Main clock out selection  This bit enables the MCO alternate function on the PF0 I/O port. It is set and cleared by software.  0: MCO alternate function disabled (I/O pin free for general-purpose I/O)  1: MCO alternate function enabled (f <sub>CPU</sub> on I/O port)  Note: To reduce power consumption, the MCO function is not active in Active Halt mode.                                |

| 6:5 | CP[1:0] | CPU clock prescaler  These bits select the CPU clock prescaler which is applied in the different slow modes. Their action is conditioned by the setting of the SMS bit. These two bits are set and cleared by software.  00: $f_{CPU}$ in Slow mode = $f_{OSC2}/2$ 01: $f_{CPU}$ in Slow mode = $f_{OSC2}/4$ 10: $f_{CPU}$ in Slow mode = $f_{OSC2}/8$ 11: $f_{CPU}$ in Slow mode = $f_{OSC2}/16$ |

| 4   | SMS     | Slow mode select  This bit is set and cleared by software.  0: Normal mode. f <sub>CPU</sub> = f <sub>OSC2</sub> 1: Slow mode. f <sub>CPU</sub> is given by CP1, CP0  See Section 8.2: Slow mode on page 65 and Chapter 11: Main clock controller with real-time clock and beeper (MCC/RTC) for more details.                                                                                     |

| 3:2 | TB[1:0] | Time base control  These bits select the programmable divider time base. They are set and cleared by software (see <i>Table 41</i> ).  A modification of the time base is taken into account at the end of the current period (previously set) to avoid an unwanted time shift. This allows to use this time base as a real-time clock.                                                           |

| 1   | OIE     | Oscillator interrupt enable This bit set and cleared by software. 0: Oscillator interrupt disabled 1: Oscillator interrupt enabled This interrupt can be used to exit from Active Halt mode. When this bit is set, calling the ST7 software HALT instruction enters the Active Halt power saving mode.                                                                                            |

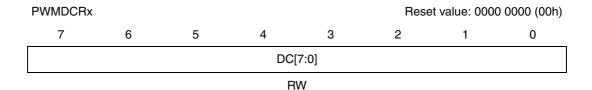

## 12.3.5 Duty cycle registers (PWMDCRx)

Table 52. PWMDCRx register description

| Bit | Name    | Function                                                    |

|-----|---------|-------------------------------------------------------------|

| 7:0 | DC[7:0] | Duty Cycle Data These bits are set and cleared by software. |

A PWMDCRx register is associated with the OCRx register of each PWM channel to determine the second edge location of the PWM signal (the first edge location is common to all channels and given by the ARTARR register). These PWMDCR registers allow the duty cycle to be set independently for each PWM channel.

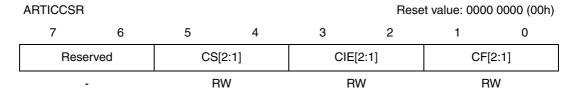

## 12.3.6 Input capture control / status register (ARTICCSR)

Table 53. ARTICCSR register description

| Bit | Name     | Function                                                                                                                                                                                                                                                        |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | -        | Reserved, always read as 0.                                                                                                                                                                                                                                     |

| 5:4 | CS[2:1]  | Capture Sensitivity  These bits are set and cleared by software. They determine the trigger event polarity on the corresponding input capture channel.  0: Falling edge triggers capture on channel x  1: Rising edge triggers capture on channel x             |

| 3:2 | CIE[2:1] | Capture Interrupt Enable  These bits are set and cleared by software. They enable or disable the Input capture channel interrupts independently.  0: Input capture channel x interrupt disabled  1: Input capture channel x interrupt enabled                   |

| 1:0 | CF[2:1]  | Capture Flag  These bits are set by hardware and cleared by software reading the corresponding ARTICRx register. Each CFx bit indicates that an input capture x has occurred.  0: No input capture on channel x  1: An input capture has occurred on channel x. |

ST72521xx-Auto 16-bit timer

Table 59. CR1 register description (continued)

| Bit | Name  | Function                                                                                                                                                                                                                                         |

|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3   | FOLV1 | Forced Output Compare 1  This bit is set and cleared by software.  0: No effect on the OCMP1 pin  1: Forces OLVL1 to be copied to the OCMP1 pin, if the OC1E bit is set and even if there is no successful comparison                            |

| 2   | OLVL2 | Output Level 2  This bit is copied to the OCMP2 pin whenever a successful comparison occurs with the OC2R register and OCxE is set in the CR2 register. This value is copied to the OCMP1 pin in One Pulse Mode and Pulse Width Modulation mode. |

| 1   | IEDG1 | Input Edge 1  This bit determines which type of level transition on the ICAP1 pin will trigger the capture.  0: A falling edge triggers the capture.  1: A rising edge triggers the capture.                                                     |

| 0   | OLVL1 | Output Level 1  The OLVL1 bit is copied to the OCMP1 pin whenever a successful comparison occurs with the OC1R register and the OC1E bit is set in the CR2 register.                                                                             |

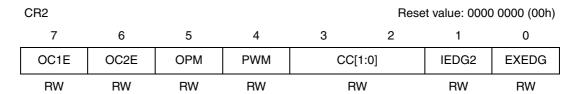

# 13.7.2 Control register 2 (CR2)

Table 60. CR2 register description

| Bit | Name | Function                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | OC1E | Output Compare 1 Pin Enable  This bit is used only to output the signal from the timer on the OCMP1 pin (OLV1 in Output Compare mode, both OLV1 and OLV2 in PWM and one-pulse mode).  Whatever the value of the OC1E bit, the Output Compare 1 function of the timer remains active.  0: OCMP1 pin alternate function disabled (I/O pin free for general-purpose I/O)  1: OCMP1 pin alternate function enabled |

| 6   | OC2E | Output Compare 2 Pin Enable  This bit is used only to output the signal from the timer on the OCMP2 pin (OLV2 in Output Compare mode). Whatever the value of the OC2E bit, the Output Compare 2 function of the timer remains active.  0: OCMP2 pin alternate function disabled (I/O pin free for general-purpose I/O)  1: OCMP2 pin alternate function enabled                                                |

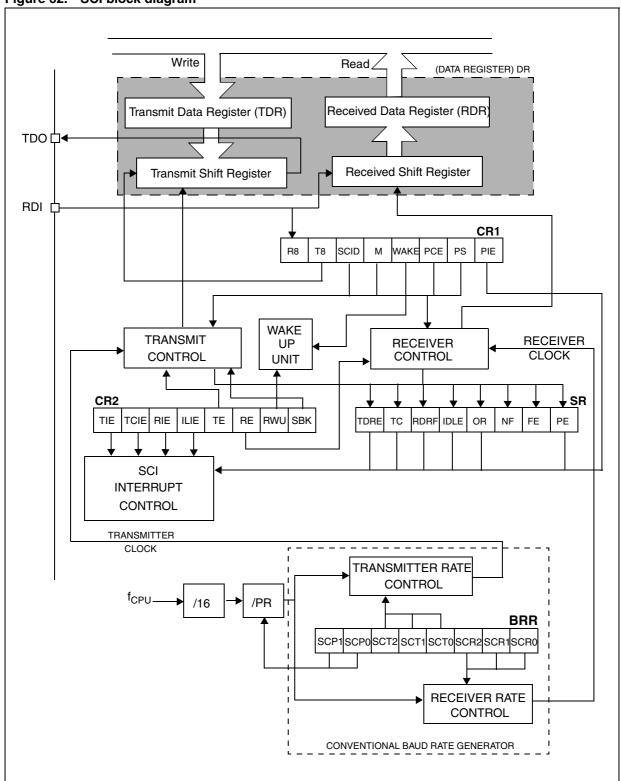

Figure 62. SCI block diagram

# 18 10-bit A/D converter (ADC)

### 18.1 Introduction

The on-chip Analog to Digital Converter (ADC) peripheral is a 10-bit, successive approximation converter with internal sample and hold circuitry. This peripheral has up to 16 multiplexed analog input channels (refer to device pin out description) that allow the peripheral to convert the analog voltage levels from up to 16 different sources.

The result of the conversion is stored in a 10-bit data register. The A/D converter is controlled through a control/status register.

#### 18.2 Main features

- 10-bit conversion

- Up to 16 channels with multiplexed input

- Linear successive approximation

- Data register (DR) which contains the results

- Conversion complete status flag

- On/off bit (to reduce consumption)

The block diagram is shown in Figure 85.

Figure 85. ADC block diagram  $f_{CPU}$ DIV 4 f<sub>ADC</sub> DIV 2 SPEED ADON **ADCCSR** AIN0 AIN1 ANALOG TO DIGITAL ANALOG CONVERTER MUX AINx → **ADCDRH** D9 D8 D7 D6 D5 D4 D3 D2 **ADCDRL** 0 0 0 D0 0 0 0 D1

ST72521xx-Auto Instruction set

Table 122. Instruction groups (continued)

| Group                            | Instructions |      |      |      |      |       |     |     |  |

|----------------------------------|--------------|------|------|------|------|-------|-----|-----|--|

| Logical operations               | AND          | OR   | XOR  | CPL  | NEG  |       |     |     |  |

| Bit Operation                    | BSET         | BRES |      |      |      |       |     |     |  |

| Conditional Bit Test and Branch  | BTJT         | BTJF |      |      |      |       |     |     |  |

| Arithmetic operations            | ADC          | ADD  | SUB  | SBC  | MUL  |       |     |     |  |

| Shift and Rotates                | SLL          | SRL  | SRA  | RLC  | RRC  | SWAP  | SLA |     |  |

| Unconditional Jump or Call       | JRA          | JRT  | JRF  | JP   | CALL | CALLR | NOP | RET |  |

| Conditional Branch               | JRxx         |      |      |      |      |       |     |     |  |

| Interruption management          | TRAP         | WFI  | HALT | IRET |      |       |     |     |  |

| Condition Code Flag modification | SIM          | RIM  | SCF  | RCF  |      |       |     |     |  |

## 19.2.1 Using a prebyte

The instructions are described with one to four opcodes.

In order to extend the number of available opcodes for an 8-bit CPU (256 opcodes), three different prebyte opcodes are defined. These prebytes modify the meaning of the instruction they precede.

The whole instruction becomes:

PC - 2 End of previous instruction

PC - 1 Prebyte

PC Opcode

PC + 1 Additional word (0 to 2) according to the number of bytes required to compute the effective address

These prebytes enable instruction in Y as well as indirect addressing modes to be implemented. They precede the opcode of the instruction in X or the instruction using direct addressing mode. The prebytes are:

PDY 90 Replace an X based instruction using immediate, direct, indexed, or inherent addressing mode by a Y one.

PIX 92 Replace an instruction using direct, direct bit, or direct relative addressing mode to an instruction using the corresponding indirect addressing mode.

It also changes an instruction using X indexed addressing mode to an instruction using indirect X indexed addressing mode.

PIY 91 Replace an instruction using X indirect indexed addressing mode by a Y one.

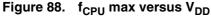

# 20.3 Operating conditions

## 20.3.1 General operating conditions

Table 127. General operating conditions

| Symbol           | Parameter                                         | Conditions                      | Min | Max | Unit |

|------------------|---------------------------------------------------|---------------------------------|-----|-----|------|

| f <sub>CPU</sub> | Internal clock frequency                          |                                 | 0   | 8   | MHz  |

| V <sub>DD</sub>  | Standard voltage range (except Flash Write/Erase) |                                 | 3.8 | 5.5 | ٧    |

|                  | Operating voltage for Flash Write/Erase           | V <sub>PP</sub> = 11.4 to 12.6V | 4.5 | 5.5 |      |

|                  |                                                   | A suffix version                |     | 85  |      |

| T <sub>A</sub>   | Ambient temperature range                         | B suffix version                | -40 | 105 | °C   |

|                  |                                                   | C suffix version                |     | 125 |      |

Note:

Some temperature ranges are only available with a specific package and memory size. Refer to Section 22: Device configuration and ordering information on page 257.

Electrical characteristics ST72521xx-Auto

# 20.9 Control pin characteristics

## 20.9.1 Asynchronous RESET pin

Subject to general operating conditions for  $V_{DD}$ ,  $f_{CPU}$ , and  $T_A$  unless otherwise specified.

Table 148. Asynchronous RESET pin characteristics

| Symbol                  | Parameter                                         | Conditions                        | Min        | Тур | Max                 | Unit |

|-------------------------|---------------------------------------------------|-----------------------------------|------------|-----|---------------------|------|

| V <sub>IL</sub>         | Input low level voltage <sup>(1)</sup>            |                                   |            |     | 0.16xV <sub>D</sub> |      |

| · IL                    | mparion for rollage                               |                                   |            |     | D                   |      |

| V <sub>IH</sub>         | Input high level voltage <sup>(1)</sup>           |                                   | $0.85xV_D$ |     |                     |      |

|                         |                                                   |                                   | D          |     |                     | V    |

| V <sub>hys</sub>        | Schmitt trigger voltage hysteresis <sup>(2)</sup> |                                   |            | 2.5 |                     |      |

| V <sub>OL</sub>         | Output low level voltage <sup>(3)</sup>           | $V_{DD} = 5V$ , $I_{IO} = +2mA$   |            | 0.2 | 0.5                 |      |

| I <sub>IO</sub>         | Input current on RESET pin                        |                                   |            | 2   |                     | mA   |

| R <sub>ON</sub>         | Weak pull-up equivalent resistor                  |                                   | 20         | 30  | 120                 | kΩ   |

| t <sub>w(RSTL)out</sub> | Generated reset pulse duration                    | Stretch applied on external pulse | 0          |     | 42 <sup>(4)</sup>   |      |

|                         |                                                   | Internal reset sources            | 20         | 30  | 42 <sup>(4)</sup>   | μs   |

| t <sub>h(RSTL)in</sub>  | External reset pulse hold time <sup>(5)</sup>     |                                   | 2.5        | _   |                     |      |

| t <sub>g(RSTL)in</sub>  | Filtered glitch duration <sup>(6)</sup>           |                                   |            | 200 |                     | ns   |

<sup>1.</sup> Data based on characterization results, not tested in production.

<sup>2.</sup> Hysteresis voltage between Schmitt trigger switching levels.

<sup>3.</sup> The  $I_{IO}$  current sunk must always respect the absolute maximum rating specified in Section 20.2.2 and the sum of  $I_{IO}$  (I/O ports and control pins) must not exceed  $I_{VSS}$ .

<sup>4.</sup> Data guaranteed by design, not tested in production.

<sup>5. &</sup>lt;u>To guar</u>antee the reset of the device, a minimum pulse has to be applied to the RESET pin. All short pulses applied on the RESET pin with a duration below t<sub>h(RSTL)in</sub> can be ignored.

<sup>6.</sup> The reset network (the resistor and two capacitors) protects the device against parasitic resets, especially in noisy environments

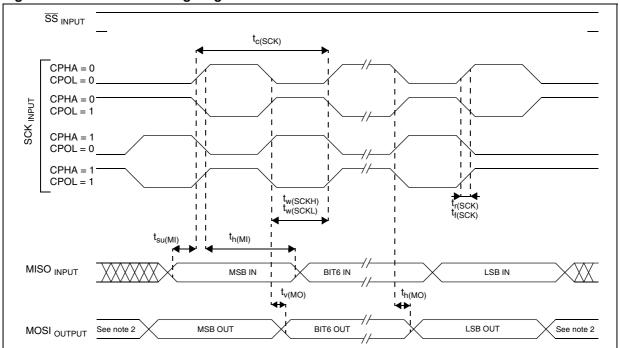

Figure 110. SPI master timing diagram<sup>(1)</sup>

- 1. Measurement points are done at CMOS levels:  $0.3 \mathrm{xV}_\mathrm{DD}$  and  $0.7 \mathrm{xV}_\mathrm{DD}$ .

- 2. When no communication is on-going the data output line of the SPI (MOSI in master mode, MISO in slave mode) has its alternate function capability released. In this case, the pin status depends of the I/O port configuration.

Table 164. Option byte 1 bit description (continued)

| Bit                        | Name          | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|----------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| OPT5:4                     | OSCTYPE[1:0]  | Oscillator type These option bits select the ST7 main clock source type. 00: Clock source = Resonator oscillator 01: Reserved 10: Clock source = Internal RC oscillator 11: Clock source = External source                                                                                                                                                                                                                                                                          |  |  |

| OPT3:1                     | OSCRANGE[2:0] | Oscillator range When the resonator oscillator type is selected, these option bits select the resonator oscillator current source corresponding to the frequency range of the used resonator. Otherwise, these bits are used to select the normal operating frequency range (see <i>Table 166: Oscillator</i> frequency range selection (OPT3:1)).                                                                                                                                  |  |  |

| OPTO PLLOFF 9: 1: Cau bits |               | L activation This option bit activates the PLL which allows multiplication by two of the main input clock frequency. The PLL must not be used with the internal RC oscillator or with external clock source. The PLL is guaranteed only with an input frequency between 2 and 4 MHz. 0: PLL x2 enabled 1: PLL x2 disabled aution: The PLL can be enabled only if the "OSCRANGE" (OPT3:1) as are configured to "MP - 2~4 MHz". Otherwise, the device inctionality is not guaranteed. |  |  |

Table 165. Package selection (OPT7)

| Version | Selected package | PKG1 | PKG0 |

|---------|------------------|------|------|

| М       | LQFP80           | 1    | 1    |

| (A)R    | LQFP64           | 1    | 0    |

Note:

On the chip, each I/O port has eight pads. Pads that are not bonded to external pins are in input pull-up configuration after reset. The configuration of these pads must be kept at reset state to avoid added current consumption.

Table 166. Oscillator frequency range selection (OPT3:1)

| Typical frequency range |          | OSCRANGE |   |   |  |

|-------------------------|----------|----------|---|---|--|

|                         |          | 2        | 1 | 0 |  |

| LP                      | 1~2 MHz  | 0        | 0 | 0 |  |

| MP                      | 2~4 MHz  | 0        | 0 | 1 |  |

| MS                      | 4~8 MHz  | 0        | 1 | 0 |  |

| HS                      | 8~16 MHz | 0        | 1 | 1 |  |

Figure 123. ST72521xxx-Auto ROM commercial product structure