Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Obsolete                                                               |

| Core Processor             | ST7                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | CANbus, I <sup>2</sup> C, SCI, SPI                                     |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 64                                                                     |

| Program Memory Size        | 60KB (60K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                |                                                                        |

| RAM Size                   | 2K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                            |

| Data Converters            | A/D 16x10b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 80-LQFP                                                                |

| Supplier Device Package    | -                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f521m9tctr |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|    | 6.4   | Multi-c  | oscillator (MO)                                         | 41    |

|----|-------|----------|---------------------------------------------------------|-------|

|    | 6.5   | Reset    | sequence manager (RSM)                                  | 43    |

|    |       | 6.5.1    | Introduction                                            | 43    |

|    |       | 6.5.2    | Asynchronous external RESET pin                         | 44    |

|    |       | 6.5.3    | External power-on RESET                                 | 44    |

|    |       | 6.5.4    | Internal low voltage detector (LVD) RESET               | 44    |

|    |       | 6.5.5    | Internal watchdog RESET                                 | 45    |

|    | 6.6   | Syster   | n integrity management (SI)                             | 46    |

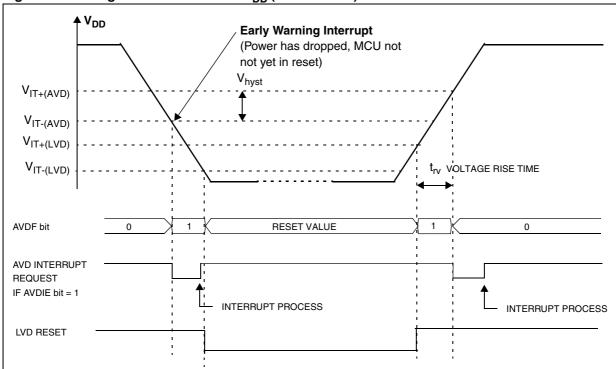

|    |       | 6.6.1    | Low voltage detector (LVD)                              | 46    |

|    |       | 6.6.2    | Auxiliary voltage detector (AVD)                        | 47    |

|    |       | 6.6.3    | Low power modes                                         | 49    |

|    |       | 6.6.4    | Interrupts                                              | 49    |

|    |       | 6.6.5    | System Integrity (SI) Control/Status register (SICSR) . | 50    |

| 7  | Inter | rupts .  |                                                         |       |

|    | 7.1   | Introdu  | uction                                                  |       |

|    | 7.2   | Maskir   | ng and processing flow                                  |       |

|    | 7.3   |          | pts and low power modes                                 |       |

|    | 7.4   |          | rrent and nested management                             |       |

|    | 7.5   |          | pt register description                                 |       |

|    | 7.5   | 7.5.1    | CPU CC register interrupt bits                          |       |

|    |       | 7.5.2    | Interrupt software priority registers (ISPRx)           |       |

|    | 7.6   |          | al interrupts                                           |       |

|    | 7.0   | 7.6.1    | I/O port interrupt sensitivity                          |       |

|    |       | 7.6.2    | External interrupt control register (EICR)              |       |

|    |       | 7.0.2    |                                                         |       |

| 8  | Pow   | er savir | ng modes                                                | 65    |

|    | 8.1   | Introdu  | uction                                                  | 65    |

|    | 8.2   | Slow n   | node                                                    | 65    |

|    | 8.3   | Wait m   | node                                                    |       |

|    | 8.4   | Active   | Halt and Halt modes                                     | 68    |

|    |       | 8.4.1    | Active Halt mode                                        | 68    |

|    |       | 8.4.2    | Halt mode                                               | 70    |

| 9  | l/O n | oorts    |                                                         |       |

|    | 9.1   |          |                                                         |       |

|    |       |          |                                                         |       |

| 57 |       |          | Doc ID 17660 Rev 1                                      | 3/276 |

|    |       | 16.7.2    | I2C status register 1 (SR1)                               | 168 |

|----|-------|-----------|-----------------------------------------------------------|-----|

|    |       | 16.7.3    | I2C status register 2 (SR2)                               | 170 |

|    |       | 16.7.4    | I2C clock control register (CCR)                          | 171 |

|    |       | 16.7.5    | I2C data register (DR)                                    | 172 |

|    |       | 16.7.6    | I2C own address register (OAR1)                           | 172 |

|    |       | 16.7.7    | I2C own address register (OAR2)                           | 173 |

| 17 | Cont  | roller ar | ea network (CAN)                                          | 175 |

|    | 17.1  | Introdu   | ction                                                     | 175 |

|    | 17.2  | Main fe   | atures                                                    | 176 |

|    | 17.3  | Functio   | nal description                                           | 176 |

|    |       | 17.3.1    | Frame formats                                             | 176 |

|    |       | 17.3.2    | Hardware blocks                                           | 177 |

|    |       | 17.3.3    | Modes of operation                                        | 179 |

|    |       | 17.3.4    | Bit timing logic                                          | 181 |

|    | 17.4  | Registe   | er description                                            | 182 |

|    |       | 17.4.1    | General purpose registers                                 | 182 |

|    |       | 17.4.2    | Paged registers                                           | 187 |

|    | 17.5  | List of ( | CAN cell limitations                                      | 196 |

|    |       | 17.5.1    | Omitted SOF bit                                           | 196 |

|    |       | 17.5.2    | CPU write access (more than one cycle) corrupts CAN frame | 196 |

|    |       | 17.5.3    | Unexpected message transmission                           | 197 |

|    |       | 17.5.4    | WKPS functionality                                        | 202 |

|    |       | 17.5.5    | Bus-off state not entered                                 | 203 |

| 18 | 10-bi | t A/D co  | onverter (ADC)                                            | 205 |

|    | 18.1  | Introdu   | ction                                                     | 205 |

|    | 18.2  | Main fe   | atures                                                    | 205 |

|    | 18.3  | Functio   | nal description                                           | 206 |

|    |       | 18.3.1    | A/D converter configuration                               | 206 |

|    |       | 18.3.2    | Starting the conversion                                   | 206 |

|    |       | 18.3.3    | Changing the conversion channel                           | 207 |

|    | 18.4  | Low po    | wer modes                                                 | 207 |

|    | 18.5  | Interrup  | ots                                                       | 207 |

|    | 18.6  |           | gisters                                                   |     |

|    |       | 18.6.1    | Control/status register (ADCCSR)                          |     |

|    |       |           |                                                           |     |

| 22.1.1     | Flash configuration                                                                                                                                                                                                                                                              |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22.1.2     | Flash ordering information                                                                                                                                                                                                                                                       |

| 2 ROM d    | evice ordering information and transfer of customer code 261                                                                                                                                                                                                                     |

| 3 Develo   | pment tools                                                                                                                                                                                                                                                                      |

| 22.3.1     | Introduction                                                                                                                                                                                                                                                                     |

| 22.3.2     | Evaluation tools and starter kits                                                                                                                                                                                                                                                |

| 22.3.3     | Development and debugging tools                                                                                                                                                                                                                                                  |

| 22.3.4     | Programming tools                                                                                                                                                                                                                                                                |

| 22.3.5     | Socket and emulator adapter information                                                                                                                                                                                                                                          |

|            |                                                                                                                                                                                                                                                                                  |

| own limita | ations 267                                                                                                                                                                                                                                                                       |

| 1 All Flas | h and ROM devices 267                                                                                                                                                                                                                                                            |

| 23.1.1     | External RC option                                                                                                                                                                                                                                                               |

| 23.1.2     | Safe connection of OSC1/OSC2 pins                                                                                                                                                                                                                                                |

| 23.1.3     | Reset pin protection with LVD enabled                                                                                                                                                                                                                                            |

| 23.1.4     | Unexpected reset fetch                                                                                                                                                                                                                                                           |

| 23.1.5     | External interrupt missed                                                                                                                                                                                                                                                        |

| 23.1.6     | Clearing active interrupts outside interrupt routine                                                                                                                                                                                                                             |

| 23.1.7     | SCI wrong break duration                                                                                                                                                                                                                                                         |

| 23.1.8     | 16-bit timer PWM mode                                                                                                                                                                                                                                                            |

| 23.1.9     | TIMD set simultaneously with OC interrupt                                                                                                                                                                                                                                        |

| 23.1.10    | CAN cell limitations                                                                                                                                                                                                                                                             |

| 23.1.11    | I <sup>2</sup> C multimaster                                                                                                                                                                                                                                                     |

| 2 All Flas | h devices                                                                                                                                                                                                                                                                        |

| 23.2.1     | Internal RC oscillator with LVD                                                                                                                                                                                                                                                  |

| 23.2.2     | I/O behavior during ICC mode entry sequence                                                                                                                                                                                                                                      |

| 23.2.3     | Readout protection with LVD 274                                                                                                                                                                                                                                                  |

|            |                                                                                                                                                                                                                                                                                  |

|            | 22.1.2<br>2 ROM d<br>3 Develop<br>22.3.1<br>22.3.2<br>22.3.3<br>22.3.4<br>22.3.5<br><b>nown limita</b><br>1 All Flas<br>23.1.1<br>23.1.2<br>23.1.3<br>23.1.4<br>23.1.5<br>23.1.6<br>23.1.7<br>23.1.8<br>23.1.7<br>23.1.8<br>23.1.10<br>23.1.11<br>2 All Flas<br>23.2.1<br>23.2.2 |

### Monitoring a voltage on the EVD pin

This mode is selected by setting the AVDS bit in the SICSR register.

The AVD circuitry can generate an interrupt when the AVDIE bit of the SICSR register is set. This interrupt is generated on the rising and falling edges of the comparator output. This means it is generated when either one of these two events occur:

- V<sub>EVD</sub> rises up to V<sub>IT+(EVD)</sub>

- V<sub>EVD</sub> falls down to V<sub>IT-(EVD)</sub>

The EVD function is illustrated in Figure 16.

For more details, refer to Section 20: Electrical characteristics.

ST72521xx-Auto

48/276

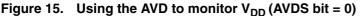

Figure 28. Halt mode flowchart

1. WDGHALT is an option bit. See Section 22.1.1: Flash configuration on page 257 for more details.

- 2. Peripheral clocked with an external clock source can still be active.

- 3. Only some specific interrupts can exit the MCU from Halt mode (such as external interrupt). Refer to *Table 20: Interrupt mapping* for more details.

- 4. Before servicing an interrupt, the CC register is pushed on the stack. The I[1:0] bits of the CC register are set to the current software priority level of the interrupt routine and recovered when the CC register is popped.

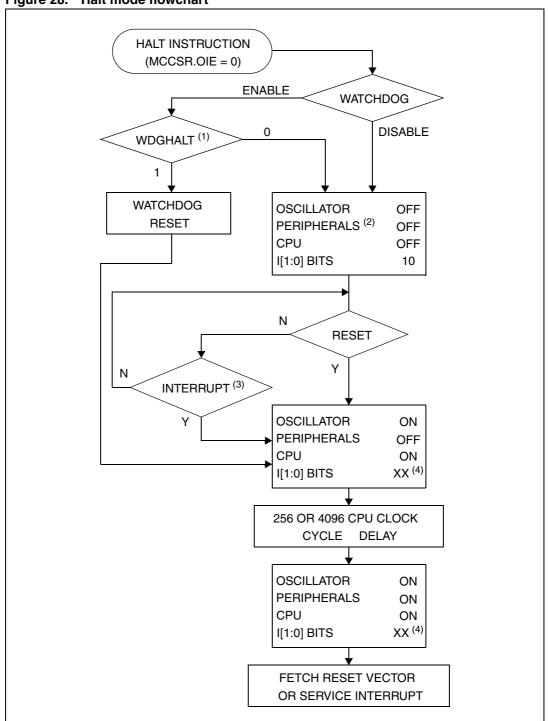

Figure 29. I/O port general block diagram

### Table 29.I/O port mode options

|        | Configuration mode              | Pull-up | P-buffer | Diodes             |                    |  |

|--------|---------------------------------|---------|----------|--------------------|--------------------|--|

|        | Configuration mode              | Pull-up | P-buller | to V <sub>DD</sub> | to V <sub>SS</sub> |  |

| Input  | Floating with/without Interrupt | Off     | Off      |                    |                    |  |

| mput   | Pull-up with/without Interrupt  | On      |          | - On               | On                 |  |

|        | Push-pull                       | Off     | On       |                    |                    |  |

| Output | Open-drain (logic level)        | Oli     | Off      |                    |                    |  |

|        | True open-drain                 | NI      | NI       | NI <sup>(1)</sup>  |                    |  |

1. The diode to  $V_{DD}$  is not implemented in the true open-drain pads. A local protection between the pad and  $V_{SS}$  is implemented to protect the device against positive stress.

Legend:

- Off Implemented not activated

- On Implemented and activated

- NI Not implemented

| Table 60. CR2 register description (continued) |         |                                                                                                                                                                                                                                                                                                                      |  |  |  |

|------------------------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Bit                                            | Name    | Function                                                                                                                                                                                                                                                                                                             |  |  |  |

| 5                                              | OPM     | <ul> <li>One Pulse Mode</li> <li>0: One Pulse Mode is not active.</li> <li>1: One Pulse Mode is active, the ICAP1 pin can be used to trigger one pulse on the OCMP1 pin; the active transition is given by the IEDG1 bit. The length of the generated pulse depends on the contents of the OC1R register.</li> </ul> |  |  |  |

| 4                                              | PWM     | <ul> <li>Pulse Width Modulation</li> <li>0: PWM mode is not active.</li> <li>1: PWM mode is active, the OCMP1 pin outputs a programmable cyclic signal; the length of the pulse depends on the value of OC1R register; the period depends on the value of OC2R register.</li> </ul>                                  |  |  |  |

| 3:2                                            | CC[1:0] | <i>Clock Control</i><br>The timer clock mode depends on these bits (see <i>Table 61</i> ).                                                                                                                                                                                                                           |  |  |  |

| 1                                              | IEDG2   | <ul> <li>Input Edge 2</li> <li>This bit determines which type of level transition on the ICAP2 pin will trigger the capture.</li> <li>0: A falling edge triggers the capture.</li> <li>1: A rising edge triggers the capture.</li> </ul>                                                                             |  |  |  |

| 0                                              | EXEDG   | <ul> <li>External Clock Edge</li> <li>This bit determines which type of level transition on the external clock pin EXTCLK will trigger the counter register.</li> <li>0: A falling edge triggers the counter register.</li> <li>1: A rising edge triggers the counter register.</li> </ul>                           |  |  |  |

| Table 60. | <b>CR2 register</b> | description ( | (continued) | ) |

|-----------|---------------------|---------------|-------------|---|

|-----------|---------------------|---------------|-------------|---|

### Table 61.Timer clock selection

| Timer clock                                     | CC1 | CC0 |

|-------------------------------------------------|-----|-----|

| f <sub>CPU</sub> / 4                            | 0   | 0   |

| f <sub>CPU</sub> / 2                            | 0   | 1   |

| f <sub>CPU</sub> / 8                            | 1   | 0   |

| External clock (where available) <sup>(1)</sup> | 1   | 1   |

1. If the external clock pin is not available, programming the external clock configuration stops the counter.

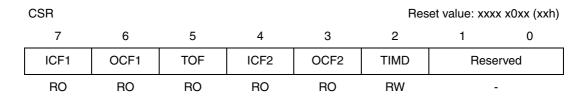

### 13.7.3 Control/status register (CSR)

|                      | - J                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Register<br>label    | 7                                                                                                                                                                                                                                                                                        | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4                                                                                                                                                                                                                  | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CR1<br>Reset value   | ICIE<br>0                                                                                                                                                                                                                                                                                | OCIE<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | TOIE<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | FOLV2<br>0                                                                                                                                                                                                         | FOLV1<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | OLVL2<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IEDG1<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | OLVL1<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| CR2<br>Reset value   | OC1E<br>0                                                                                                                                                                                                                                                                                | OC2E<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | OPM<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | PWM<br>0                                                                                                                                                                                                           | CC1<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | CC0<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | IEDG2<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | EXEDG<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| CSR<br>Reset value   | ICF1<br>x                                                                                                                                                                                                                                                                                | OCF1<br>x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | TOF<br>x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ICF2<br>x                                                                                                                                                                                                          | OCF2<br>x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | TIMD<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -<br>X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -<br>x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| IC1HR<br>Reset value | MSB<br>x                                                                                                                                                                                                                                                                                 | x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | x                                                                                                                                                                                                                  | х                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | LSB<br>x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| IC1LR<br>Reset value | MSB<br>x                                                                                                                                                                                                                                                                                 | x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | x                                                                                                                                                                                                                  | х                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | LSB<br>x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| OC1HR<br>Reset value | MSB<br>1                                                                                                                                                                                                                                                                                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0                                                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | LSB<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| OC1LR<br>Reset value | MSB<br>0                                                                                                                                                                                                                                                                                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0                                                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | LSB<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| OC2HR<br>Reset value | MSB<br>1                                                                                                                                                                                                                                                                                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0                                                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | LSB<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| OC2LR<br>Reset value | MSB<br>0                                                                                                                                                                                                                                                                                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0                                                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | LSB<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |