Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                      |

|----------------------------|----------------------------------------------------------------------|

| Product Status             | Obsolete                                                             |

| Core Processor             | ST7                                                                  |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 8MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, SCI, SPI                                   |

| Peripherals                | LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 48                                                                   |

| Program Memory Size        | 32KB (32K x 8)                                                       |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 1K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                          |

| Data Converters            | A/D 16x10b                                                           |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 64-LQFP                                                              |

| Supplier Device Package    | -                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f521r6ta |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|    | 9.2  | Functional description                                       | 3 |

|----|------|--------------------------------------------------------------|---|

|    |      | 9.2.1 Input modes                                            | 3 |

|    |      | 9.2.2 Output modes                                           | 4 |

|    |      | 9.2.3 Alternate functions                                    | 4 |

|    | 9.3  | I/O port implementation                                      | 7 |

|    | 9.4  | Low power modes                                              | 8 |

|    | 9.5  | Interrupts                                                   | 8 |

| 10 | Watc | hdog timer (WDG)8                                            | 0 |

|    | 10.1 | Introduction 8                                               | 0 |

|    | 10.2 | Main features 8                                              | 0 |

|    | 10.3 | Functional description 8                                     | 0 |

|    | 10.4 | How to program the watchdog timeout                          | 1 |

|    | 10.5 | Low power modes                                              | 3 |

|    | 10.6 | Hardware watchdog option                                     | 3 |

|    | 10.7 | Using Halt mode with the WDG (WDGHALT option)                | 3 |

|    | 10.8 | Interrupts 8                                                 | 3 |

|    | 10.9 | Register description                                         | 4 |

|    |      | 10.9.1 Control register (WDGCR)                              | 4 |

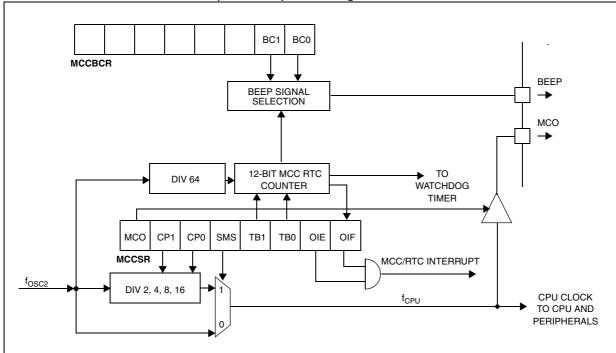

| 11 | Main | clock controller with real-time clock and beeper (MCC/RTC) 8 | 5 |

|    | 11.1 | Introduction                                                 | 5 |

|    | 11.2 | Programmable CPU clock prescaler                             | 5 |

|    | 11.3 | Clock-out capability                                         | 5 |

|    | 11.4 | Real-time clock timer (RTC)                                  | 5 |

|    | 11.5 | Beeper                                                       | 5 |

|    | 11.6 | Low power modes                                              | 6 |

|    | 11.7 | Interrupts                                                   | 6 |

|    | 11.8 | Main clock controller registers 8                            | 7 |

|    |      | 11.8.1 MCC control/status register (MCCSR)                   | 7 |

|    |      | 11.8.2 MCC beep control register (MCCBCR)                    | 8 |

| 12 | PWM  | l auto-reload timer (ART)9                                   | 0 |

|    | 12.1 | Introduction                                                 | 0 |

|    | 12.2 | Functional description9                                      | 1 |

|    |      |                                                              |   |

List of tables ST72521xx-Auto

# List of tables

| Table 1.  | Device summary                                        | . 1 |

|-----------|-------------------------------------------------------|-----|

| Table 2.  | Device summary                                        | 19  |

| Table 3.  | Device pin description                                | 23  |

| Table 4.  | Hardware register map                                 | 28  |

| Table 5.  | Sectors available in Flash devices                    | 32  |

| Table 6.  | Flash control/status register address and reset value | 35  |

| Table 7.  | Arithmetic management bits                            | 37  |

| Table 8.  | Interrupt management bits                             | 38  |

| Table 9.  | Interrupt software priority selection                 | 38  |

| Table 10. | ST7 clock sources                                     | 42  |

| Table 11. | Effect of low power modes on SI                       | 49  |

| Table 12. | AVD interrupt control/wake-up capability              | 49  |

| Table 13. | SICSR description                                     | 50  |

| Table 14. | Reset source flags                                    |     |

| Table 15. | Interrupt software priority levels                    | 53  |

| Table 16. | CPU CC register interrupt bits description            | 56  |

| Table 17. | Interrupt software priority levels                    | 57  |

| Table 18. | Interrupt priority bits                               |     |

| Table 19. | Interrupt dedicated instruction set                   | 58  |

| Table 20. | Interrupt mapping                                     | 59  |

| Table 21. | EICR register description                             | 62  |

| Table 22. | Interrupt sensitivity - ei2 (port B30)                | 63  |

| Table 23. | Interrupt sensitivity - ei3 (port B74)                |     |

| Table 24. | Interrupt sensitivity - ei0 (port A30)                |     |

| Table 25. | Interrupt sensitivity - ei1 (port F20)                | 63  |

| Table 26. | Nested interrupts register map and reset values       |     |

| Table 27. | MCC/RTC low power mode selection                      |     |

| Table 28. | I/O output mode selection                             |     |

| Table 29. | I/O port mode options                                 |     |

| Table 30. | I/O port configurations                               |     |

| Table 31. | I/O port configuration                                |     |

| Table 32. | Effect of low power modes on I/O ports                |     |

| Table 33. | I/O port interrupt control/wake-up capability         |     |

| Table 34. | I/O port register map and reset values                |     |

| Table 35. | Effect of low power modes on WDG                      | 83  |

| Table 36. | WDGCR register description                            |     |

| Table 37. | Watchdog timer register map and reset values          |     |

| Table 38. | Effect of low power modes on MCC/RTC                  |     |

| Table 39. | MCC/RTC interrupt control/wake-up capability          | 86  |

| Table 40. | MCCSR register description                            |     |

| Table 41. | Time base selection                                   |     |

| Table 42. | MCCBCR register description                           |     |

| Table 43. | Beep frequency selection                              |     |

| Table 44. | Main clock controller register map and reset values   |     |

| Table 45. | ARTCSR register description                           |     |

| Table 46. | Prescaler selection for ART                           |     |

| Table 47. | ARTCAR register description                           |     |

| Table 48  | · ·                                                   | 97  |

577

ST72521xx-Auto List of tables

| Table 153. | I <sup>2</sup> C control interface characteristics           | . 247 |

|------------|--------------------------------------------------------------|-------|

| Table 154. | SCL frequency table                                          | . 248 |

| Table 155. | CAN characteristics                                          | . 249 |

| Table 156. | 10-bit ADC characteristics                                   | . 249 |

| Table 157. | ADC accuracy                                                 | . 252 |

| Table 158. | 80-pin low profile quad flat package mechanical data         | . 253 |

| Table 159. | 64-pin (14x14) low profile quad flat package mechanical data | . 254 |

| Table 160. | 64-pin (10x10) low profile quad flat package mechanical data | . 255 |

| Table 161. | Thermal characteristics                                      | . 256 |

| Table 162. | Flash option bytes                                           | . 257 |

| Table 163. | Option byte 0 bit description                                | . 257 |

| Table 164. | Option byte 1 bit description                                | . 258 |

| Table 165. | Package selection (OPT7)                                     | . 259 |

| Table 166. | Oscillator frequency range selection (OPT3:1)                | . 259 |

| Table 167. | STMicroelectronics development tools                         | . 266 |

| Table 168. | Suggested list of socket types                               | . 266 |

| Table 169. | CAN cell limitations                                         | . 273 |

| Table 170. | Document revision history                                    | . 275 |

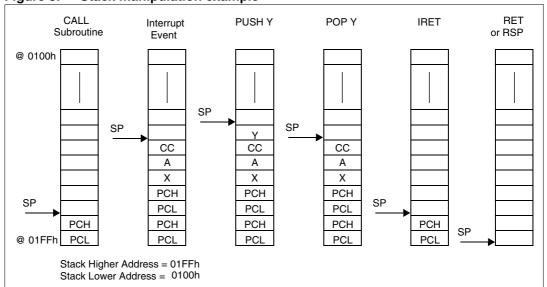

The stack pointer is a 16-bit register which is always pointing to the next free location in the stack. It is then decremented after data has been pushed onto the stack and incremented before data is popped from the stack (see *Figure 8*).

Since the stack is 256 bytes deep, the 8 most significant bits are forced by hardware. Following an MCU Reset, or after a reset stack pointer instruction (RSP), the stack pointer contains its reset value (the SP7 to SP0 bits are set) which is the stack higher address.

The least significant byte of the stack pointer (called S) can be directly accessed by an LD instruction.

Note:

When the lower limit is exceeded, the stack pointer wraps around to the stack upper limit, without indicating the stack overflow. The previously stored information is then overwritten and therefore lost. The stack also wraps in case of an underflow.

The stack is used to save the return address during a subroutine call and the CPU context during an interrupt. The user may also directly manipulate the stack by means of the PUSH and POP instructions. In the case of an interrupt, the PCL is stored at the first location pointed to by the SP. The other registers are then stored in the next locations as shown in *Figure 8*.

- When an interrupt is received, the SP is decremented and the context is pushed on the stack

- On return from interrupt, the SP is incremented and the context is popped from the stack.

A subroutine call occupies two locations and an interrupt five locations in the stack area.

Figure 8. Stack manipulation example

Interrupts ST72521xx-Auto

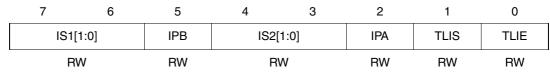

# 7.6.2 External interrupt control register (EICR)

EICR Reset value: 0000 0000 (00h)

Table 21. EICR register description

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                 |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | IS1[1:0] | ei2 and ei3 sensitivity  The interrupt sensitivity, defined using the IS1[1:0] bits, is applied to the following external interrupts: - ei2 (port B30) (see Table 22) - ei3 (port B74) (see Table 23)  These 2 bits can be written only when I1 and I0 of the CC register are both set to 1 (level 3).   |

| 5   | IPB      | Interrupt polarity for port B  This bit is used to invert the sensitivity of the port B [3:0] external interrupts. It can be set and cleared by software only when I1 and I0 of the CC register are both set to 1 (level 3).  0: No sensitivity inversion 1: Sensitivity inversion                       |

| 4:3 | IS2[1:0] | ei0 and ei1 sensitivity  The interrupt sensitivity, defined using the IS2[1:0] bits, is applied to the following external interrupts:  - ei0 (port A30) (see Table 24)  - ei1 (port F20) (see Table 25)  These 2 bits can be written only when I1 and I0 of the CC register are both set to 1 (level 3). |

| 2   | IPA      | Interrupt polarity for port A  This bit is used to invert the sensitivity of the port A [3:0] external interrupts. It can be set and cleared by software only when I1 and I0 of the CC register are both set to 1 (level 3).  0: No sensitivity inversion 1: Sensitivity inversion                       |

| 1   | TLIS     | TLI sensitivity  This bit allows to toggle the TLI edge sensitivity. It can be set and cleared by software only when TLIE bit is cleared.  0: Falling edge 1: Rising edge                                                                                                                                |

| 0   | TLIE     | TLI enable This bit allows to enable or disable the TLI capability on the dedicated pin. It is set and cleared by software. 0: TLI disabled 1: TLI enabled Note: A parasitic interrupt can be generated when clearing the TLIE bit.                                                                      |

Figure 34. Main clock controller (MCC/RTC) block diagram

# 11.6 Low power modes

Table 38. Effect of low power modes on MCC/RTC

| Mode Effect                                                                                                                                               |                                                                                                                                                |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Wait                                                                                                                                                      | No effect on MCC/RTC peripheral. MCC/RTC interrupt causes the device to exit from Wait mode.                                                   |  |  |  |  |

| Active Halt  No effect on MCC/RTC counter (OIE bit is set), the registers are frozen.  MCC/RTC interrupt causes the device to exit from Active Halt mode. |                                                                                                                                                |  |  |  |  |

| Halt                                                                                                                                                      | MCC/RTC counter and registers are frozen. MCC/RTC operation resumes when the MCU is woken up by an interrupt with "exit from HALT" capability. |  |  |  |  |

# 11.7 Interrupts

The MCC/RTC interrupt event generates an interrupt if the OIE bit of the MCCSR register is set and the interrupt mask in the CC register is not active (RIM instruction).

Table 39. MCC/RTC interrupt control/wake-up capability

| Interrupt event          | Event flag | Enable control bit | Exit from<br>Wait | Exit from<br>Halt |

|--------------------------|------------|--------------------|-------------------|-------------------|

| Time base overflow event | OIF        | OIE                | Yes               | No <sup>(1)</sup> |

<sup>1.</sup> The MCC/RTC interrupt wakes up the MCU from Active Halt mode, not from Halt mode.

86/276 Doc ID 17660 Rev 1

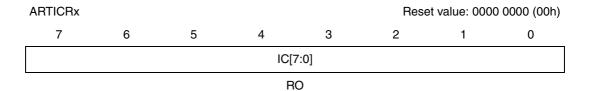

# 12.3.7 Input capture registers (ARTICRx)

Table 54. ARTICRx register description

| Bit | Name    | Function                                                                                                                                                                                     |

|-----|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | IC[7:0] | Input Capture Data  These read only bits are set and cleared by hardware. An ARTICRx register contains the 8-bit auto-reload counter value transferred by the input capture channel x event. |

Table 55. PWM auto-reload timer register map and reset values

| Address (Hex.) | Register label          | 7    | 6   | 5        | 4        | 3         | 2         | 1        | 0        |

|----------------|-------------------------|------|-----|----------|----------|-----------|-----------|----------|----------|

| 0073h          | PWMDCR3                 | DC7  | DC6 | DC5      | DC4      | DC3       | DC2       | DC1      | DC0      |

|                | Reset value             | 0    | 0   | 0        | 0        | 0         | 0         | 0        | 0        |

| 0074h          | PWMDCR2                 | DC7  | DC6 | DC5      | DC4      | DC3       | DC2       | DC1      | DC0      |

|                | Reset value             | 0    | 0   | 0        | 0        | 0         | 0         | 0        | 0        |

| 0075h          | PWMDCR1                 | DC7  | DC6 | DC5      | DC4      | DC3       | DC2       | DC1      | DC0      |

|                | Reset value             | 0    | 0   | 0        | 0        | 0         | 0         | 0        | 0        |

| 0076h          | PWMDCR0                 | DC7  | DC6 | DC5      | DC4      | DC3       | DC2       | DC1      | DC0      |

|                | Reset value             | 0    | 0   | 0        | 0        | 0         | 0         | 0        | 0        |

| 0077h          | PWMCR                   | OE3  | OE2 | OE1      | OE0      | OP3       | OP2       | OP1      | OP0      |

|                | Reset value             | 0    | 0   | 0        | 0        | 0         | 0         | 0        | 0        |

| 0078h          | ARTCSR                  | EXCL | CC2 | CC1      | CC0      | TCE       | FCRL      | RIE      | OVF      |

|                | Reset value             | 0    | 0   | 0        | 0        | 0         | 0         | 0        | 0        |

| 0079h          | ARTCAR                  | CA7  | CA6 | CA5      | CA4      | CA3       | CA2       | CA1      | CA0      |

|                | Reset value             | 0    | 0   | 0        | 0        | 0         | 0         | 0        | 0        |

| 007Ah          | ARTARR                  | AR7  | AR6 | AR5      | AR4      | AR3       | AR2       | AR1      | AR0      |

|                | Reset value             | 0    | 0   | 0        | 0        | 0         | 0         | 0        | 0        |

| 007Bh          | ARTICCSR<br>Reset value | 0    | 0   | CS2<br>0 | CS1<br>0 | CIE2<br>0 | CIE1<br>0 | CF2<br>0 | CF1<br>0 |

| 007Ch          | ARTICR1                 | IC7  | IC6 | IC5      | IC4      | IC3       | IC2       | IC1      | IC0      |

|                | Reset value             | 0    | 0   | 0        | 0        | 0         | 0         | 0        | 0        |

| 007Dh          | ARTICR2                 | IC7  | IC6 | IC5      | IC4      | IC3       | IC2       | IC1      | IC0      |

|                | Reset value             | 0    | 0   | 0        | 0        | 0         | 0         | 0        | 0        |

100/276 Doc ID 17660 Rev 1

16-bit timer ST72521xx-Auto

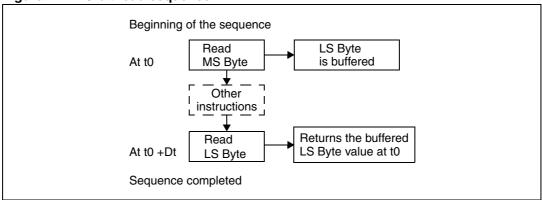

#### 16-bit read sequence

The 16-bit read sequence (from either the Counter Register or the Alternate Counter Register) is illustrated in *Figure 42*.

Figure 42. 16-bit read sequence

The user must read the MS Byte first; the LS Byte value is then buffered automatically.

This buffered value remains unchanged until the 16-bit read sequence is completed, even if the user reads the MS Byte several times.

After a complete reading sequence, if only the CLR register or ACLR register are read, they return the LS Byte of the count value at the time of the read.

Whatever timer mode is used (input capture, output compare, one pulse mode or PWM mode) an overflow occurs when the counter rolls over from FFFFh to 0000h, after which

- the TOF bit of the SR register is set

- a timer interrupt is generated if

- the TOIE bit of the CR1 register is set and

- the I bit of the CC register is cleared

If one of these conditions is false, the interrupt remains pending to be issued as soon as they are both true.

Clearing the overflow interrupt request is done in two steps:

- 1. Reading the SR register while the TOF bit is set

- 2. An access (read or write) to the CLR register

Note:

The TOF bit is not cleared by accesses to ACLR register. The advantage of accessing the ACLR register rather than the CLR register is that it allows simultaneous use of the overflow function and reading the free running counter at random times (for example, to measure elapsed time) without the risk of clearing the TOF bit erroneously.

The timer is not affected by Wait mode.

In Halt mode, the counter stops counting until the mode is exited. Counting then resumes from the previous count (MCU awakened by an interrupt) or from the reset count (MCU awakened by a Reset).

ST72521xx-Auto 16-bit timer

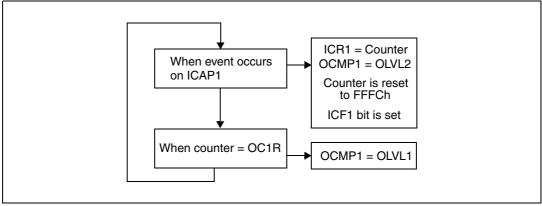

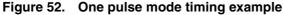

#### 13.3.6 One Pulse mode

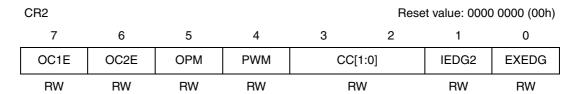

One Pulse mode enables the generation of a pulse when an external event occurs. This mode is selected via the OPM bit in the CR2 register.

The one pulse mode uses the Input Capture1 function and the Output Compare1 function.

#### **Procedure**

To use one pulse mode:

- 1. Load the OC1R register with the value corresponding to the length of the pulse (using the appropriate formula below according to the timer clock source used).

- 2. Select the following in the CR1 register:

- Using the OLVL1 bit, select the level to be applied to the OCMP1 pin after the pulse.

- Using the OLVL2 bit, select the level to be applied to the OCMP1 pin during the pulse.

- Select the edge of the active transition on the ICAP1 pin with the IEDG1 bit (the ICAP1 pin must be configured as floating input).

- 3. Select the following in the CR2 register:

- Set the OC1E bit, the OCMP1 pin is then dedicated to the Output Compare 1 function.

- Set the OPM bit

- Select the timer clock CC[1:0] (see Table 61: Timer clock selection).

Then, on a valid event on the ICAP1 pin, the counter is initialized to FFFCh and OLVL2 bit is loaded on the OCMP1 pin, the ICF1 bit is set and the value FFFDh is loaded in the IC1R register.

Figure 51. One pulse mode cycle flowchart

Because the ICF1 bit is set when an active edge occurs, an interrupt can be generated if the ICIE bit is set.

Clearing the input capture interrupt request (that is, clearing the  $ICF_i$  bit) is done in two steps:

- 1. Reading the SR register while the ICF*i* bit is set

- 2. An access (read or write) to the ICiLR register

16-bit timer ST72521xx-Auto

The OC1R register value required for a specific timing application can be calculated using the following formula:

$$OC_iR$$

value =

$$\frac{t * f_{CPU} - 5}{PRESC}$$

Where:

t = Pulse period (in seconds)

f<sub>CPU</sub> = CPU clock frequency (in hertz)

PRESC = Timer prescaler factor (2, 4 or 8 depending on the CC[1:0] bits; see *Table 61: Timer clock selection*)

If the timer clock is an external clock the formula is:

$$OCiR = t * f_{EXT} - 5$$

Where:

t = Pulse period (in seconds)

f<sub>EXT</sub> = External clock frequency (in hertz)

When the value of the counter is equal to the value of the contents of the OC1R register, the OLVL1 bit is output on the OCMP1 pin (see *Figure 52*).

Note: 1 The OCF1 bit cannot be set by hardware in one pulse mode but the OCF2 bit can generate an Output Compare interrupt.

- When the Pulse Width Modulation (PWM) and One Pulse Mode (OPM) bits are both set, the PWM mode is the only active one.

- 3 If OLVL1 = OLVL2 a continuous signal will be seen on the OCMP1 pin.

- 4 The ICAP1 pin cannot be used to perform input capture. The ICAP2 pin can be used to perform input capture (ICF2 can be set and IC2R can be loaded) but the user must take care that the counter is reset each time a valid edge occurs on the ICAP1 pin and ICF1 can also generates interrupt if ICIE is set.

- When one pulse mode is used OC1R is dedicated to this mode. Nevertheless OC2R and OCF2 can be used to indicate a period of time has been elapsed but cannot generate an output waveform because the level OLVL2 is dedicated to the one pulse mode.

ST72521xx-Auto 16-bit timer

Table 59. CR1 register description (continued)

| Bit | Name  | Function                                                                                                                                                                                                                                         |  |  |  |  |  |

|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 3   | FOLV1 | Forced Output Compare 1  This bit is set and cleared by software.  0: No effect on the OCMP1 pin  1: Forces OLVL1 to be copied to the OCMP1 pin, if the OC1E bit is set and even if there is no successful comparison                            |  |  |  |  |  |

| 2   | OLVL2 | Output Level 2  This bit is copied to the OCMP2 pin whenever a successful comparison occurs with the OC2R register and OCxE is set in the CR2 register. This value is copied to the OCMP1 pin in One Pulse Mode and Pulse Width Modulation mode. |  |  |  |  |  |

| 1   | IEDG1 | Input Edge 1  This bit determines which type of level transition on the ICAP1 pin will trigger the capture.  0: A falling edge triggers the capture.  1: A rising edge triggers the capture.                                                     |  |  |  |  |  |

| 0   | OLVL1 | Output Level 1  The OLVL1 bit is copied to the OCMP1 pin whenever a successful comparison occurs with the OC1R register and the OC1E bit is set in the CR2 register.                                                                             |  |  |  |  |  |

# 13.7.2 Control register 2 (CR2)

Table 60. CR2 register description

| Bit | Name | Function                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | OC1E | Output Compare 1 Pin Enable  This bit is used only to output the signal from the timer on the OCMP1 pin (OLV1 in Output Compare mode, both OLV1 and OLV2 in PWM and one-pulse mode).  Whatever the value of the OC1E bit, the Output Compare 1 function of the timer remains active.  0: OCMP1 pin alternate function disabled (I/O pin free for general-purpose I/O)  1: OCMP1 pin alternate function enabled |

|     | OC2E | Output Compare 2 Pin Enable  This bit is used only to output the signal from the timer on the OCMP2 pin (OLV2 in Output Compare mode). Whatever the value of the OC2E bit, the Output Compare 2 function of the timer remains active.  0: OCMP2 pin alternate function disabled (I/O pin free for general-purpose I/O)  1: OCMP2 pin alternate function enabled                                                |

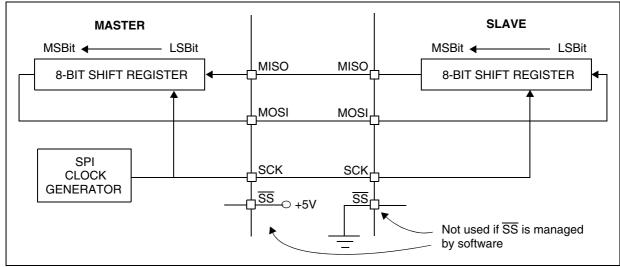

Figure 56. Single master/single slave application

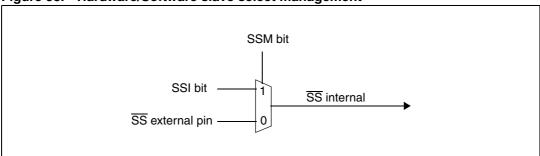

#### 14.3.2 Slave select management

As an alternative to using the  $\overline{SS}$  pin to control the Slave Select signal, the application can choose to manage the Slave Select signal by software. This is configured by the SSM bit in the SPICSR register (see *Figure 58*)

In software management, the external  $\overline{SS}$  pin is free for other application uses and the internal  $\overline{SS}$  signal level is driven by writing to the SSI bit in the SPICSR register.

#### In Master mode

SS internal must be held high continuously

#### In Slave mode

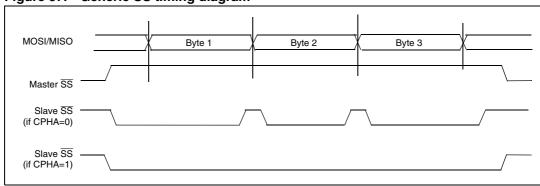

There are two cases depending on the data/clock timing relationship (see Figure 57):

If CPHA = 1 (data latched on 2nd clock edge):

SS internal must be held low during the entire transmission. This implies that in single slave applications the SS pin either can be tied to V<sub>SS</sub>, or made free for standard I/O by managing the SS function by software (SSM = 1 and SSI = 0 in the in the SPICSR register)

If CPHA = 0 (data latched on 1st clock edge):

SS internal must be held low during byte transmission and pulled high between each byte to allow the slave to write to the shift register. If SS is not pulled high, a Write Collision error will occur when the slave writes to the shift register (see *Write collision error (WCOL) on page 131*).

Figure 57. Generic SS timing diagram

Figure 58. Hardware/Software slave select management

#### 14.3.3 Master mode operation

In master mode, the serial clock is output on the SCK pin. The clock frequency, polarity and phase are configured by software (refer to the description of the SPICSR register).

Note:

The idle state of SCK must correspond to the polarity selected in the SPICSR register (by pulling up SCK if CPOL = 1 or pulling down SCK if CPOL = 0).

#### How to operate the SPI in master mode

To operate the SPI in master mode, perform the following steps in order:

- 1. Write to the SPICR register:

- a) Select the clock frequency by configuring the SPR[2:0] bits.

- b) Select the clock polarity and clock phase by configuring the CPOL and CPHA bits. *Figure 59* shows the four possible configurations.

Note:

The slave must have the same CPOL and CPHA settings as the master.

- 2. Write to the SPICSR register:

- Either set the SSM bit and set the SSI bit or clear the SSM bit and tie the SS pin high for the complete byte transmit sequence.

- 3. Write to the SPICR register:

Set the MSTR and SPE bits

Note:

MSTR and SPE bits remain set only if  $\overline{SS}$  is high).

**IMPORTANT**: If the SPICSR register is not written first, the SPICR register setting (MSTR bit) may not be taken into account.

The transmit sequence begins when software writes a byte in the SPIDR register.

### 14.5 Error flags

### 14.5.1 Master mode fault (MODF)

Master mode fault occurs when the master device has its SS pin pulled low.

When a Master mode fault occurs:

- The MODF bit is set and an SPI interrupt request is generated if the SPIE bit is set.

- The SPE bit is reset. This blocks all output from the device and disables the SPI peripheral.

- The MSTR bit is reset, thus forcing the device into slave mode.

Clearing the MODF bit is done through a software sequence:

- A read access to the SPICSR register while the MODF bit is set.

- 2. A write to the SPICR register.

Note:

To avoid any conflicts in an application with multiple slaves, the  $\overline{SS}$  pin must be pulled high during the MODF bit clearing sequence. The SPE and MSTR bits may be restored to their original state during or after this clearing sequence.

Hardware does not allow the user to set the SPE and MSTR bits while the MODF bit is set except in the MODF bit clearing sequence.

### 14.5.2 Overrun condition (OVR)

An overrun condition occurs, when the master device has sent a data byte and the slave device has not cleared the SPIF bit issued from the previously transmitted byte.

When an Overrun occurs:

The OVR bit is set and an interrupt request is generated if the SPIE bit is set.

In this case, the receiver buffer contains the byte sent after the SPIF bit was last cleared. A read to the SPIDR register returns this byte. All other bytes are lost.

The OVR bit is cleared by reading the SPICSR register.

### 14.5.3 Write collision error (WCOL)

A write collision occurs when the software tries to write to the SPIDR register while a data transfer is taking place with an external device. When this happens, the transfer continues uninterrupted; and the software write will be unsuccessful.

Write collisions can occur both in master and slave mode. See also *Slave select management on page 126*.

Note:

A "read collision" will never occur since the received data byte is placed in a buffer in which access is always synchronous with the MCU operation.

The WCOL bit in the SPICSR register is set if a write collision occurs.

No SPI interrupt is generated when the WCOL bit is set (the WCOL bit is a status flag only).

Clearing the WCOL bit is done through a software sequence (see *Figure 60*).

Table 76. SCIBRR register description

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | SCP[1:0] | First SCI Prescaler  These 2 prescaling bits allow several standard clock division ranges.  00: PR prescaling factor = 1  01: PR prescaling factor = 3  10: PR prescaling factor = 4  11: PR prescaling factor = 13                                                                                                                                                                                                                                        |

| 5:3 | SCT[2:0] | SCI Transmitter rate divisor  These 3 bits, in conjunction with the SCP1 and SCP0 bits define the total division applied to the bus clock to yield the transmit rate clock in conventional Baud Rate Generator mode.  000: TR dividing factor = 1 001: TR dividing factor = 2 010: TR dividing factor = 4 011: TR dividing factor = 8 100: TR dividing factor = 16 101: TR dividing factor = 32 110: TR dividing factor = 64 111: TR dividing factor = 128 |

| 2:0 | SCR[2:0] | SCI Receiver rate divisor  These 3 bits, in conjunction with the SCP[1:0] bits define the total division applied to the bus clock to yield the receive rate clock in conventional Baud Rate Generator mode.  000: RR dividing factor = 1 001: RR dividing factor = 2 010: RR dividing factor = 4 011: RR dividing factor = 8 100: RR dividing factor = 16 101: RR dividing factor = 32 110: RR dividing factor = 64 111: RR dividing factor = 128          |

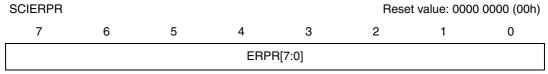

### 15.7.6 Extended receive prescaler division register (SCIERPR)

This register allows setting of the extended prescaler rate division factor for the receive circuit.

RW

### 18.3 Functional description

The conversion is monotonic, meaning that the result never decreases if the analog input does not and never increases if the analog input does not.

If the input voltage  $(V_{AIN})$  is greater than  $V_{AREF}$  (high-level voltage reference) then the conversion result is FFh in the ADCDRH register and 03h in the ADCDRL register (without overflow indication).

If the input voltage ( $V_{AIN}$ ) is lower than  $V_{SSA}$  (low-level voltage reference) then the conversion result in the ADCDRH and ADCDRL registers is 00 00h.

The A/D converter is linear and the digital result of the conversion is stored in the ADCDRH and ADCDRL registers. The accuracy of the conversion is described in *Section 20:*Electrical characteristics.

R<sub>AIN</sub> is the maximum recommended impedance for an analog input signal. If the impedance is too high, this will result in a loss of accuracy due to leakage and sampling not being completed in the allotted time.

### 18.3.1 A/D converter configuration

The analog input ports must be configured as input, no pull-up, no interrupt. Refer to the *Chapter 9: I/O ports*. Using these pins as analog inputs does not affect the ability of the port to be read as a logic input.

In the ADCCSR register:

• Select the CS[3:0] bits to assign the analog channel to convert.

### 18.3.2 Starting the conversion

In the ADCCSR register:

Set the ADON bit to enable the A/D converter and to start the conversion. From this

time on, the ADC performs a continuous conversion of the selected channel.

When a conversion is complete:

- The EOC bit is set by hardware.

- The result is in the ADCDR registers.

A read to the ADCDRH or a write to any bit of the ADCCSR register resets the EOC bit.

To read the 10 bits, perform the following steps:

- 1. Poll the EOC bit.

- 2. Read the ADCDRL register.

- 3. Read the ADCDRH register. This clears EOC automatically.

Note:

The data is not latched, so both the low and the high data register must be read before the next conversion is complete, so it is recommended to disable interrupts while reading the conversion result.

To read only 8 bits, perform the following steps:

- 1. Poll the EOC bit.

- 2. Read the ADCDRH register. This clears EOC automatically.

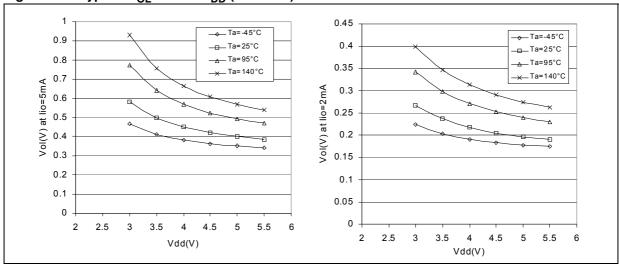

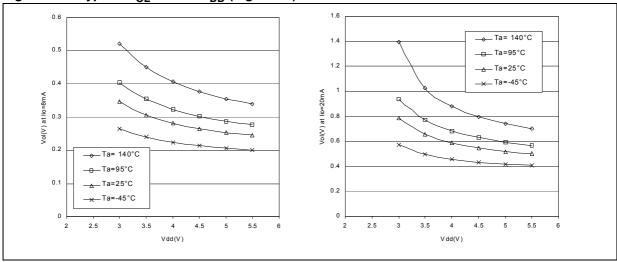

Figure 102. Typical V<sub>OL</sub> versus V<sub>DD</sub> (standard)

Figure 103. Typical V<sub>OL</sub> versus V<sub>DD</sub> (high-sink)

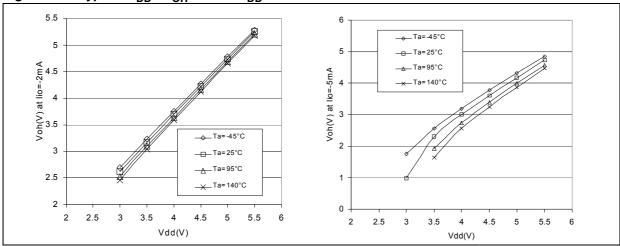

Figure 104. Typical  $V_{\rm DD}$  -  $V_{\rm OH}$  versus  $V_{\rm DD}$

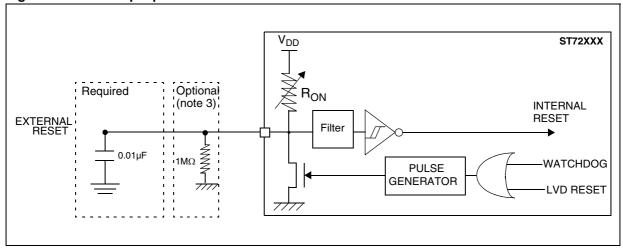

Figure 105. RESET pin protection when LVD is enabled

Note: 1 The reset network protects the device against parasitic resets.

The output of the external reset circuit must have an open-drain output to drive the ST7 reset pad. Otherwise the device can be damaged when the ST7 generates an internal reset (LVD or watchdog).

Whether the reset source is internal or external, the user must ensure that the level on the  $\overline{RESET}$  pin can go below the  $V_{IL}$  maximum level specified in Section 20.9.1 on page 240. Otherwise the reset will not be taken into account internally.

Because the reset circuit is designed to allow the internal RESET to be output in the  $\overline{RESET}$  pin, the user must ensure that the current sunk on the  $\overline{RESET}$  pin is less than the absolute maximum value specified for  $I_{INJ(RESET)}$  in Section 20.2.2 on page 220.

- When the LVD is enabled, it is recommended not to connect a pull-up resistor or capacitor. A 10nF pull-down capacitor is required to filter noise on the reset line.

- 3 In case a capacitive power supply is used, it is recommended to connect a  $1M\Omega$  pull-down resistor to the  $\overline{RESET}$  pin to discharge any residual voltage induced by the capacitive effect of the power supply (this will add  $5\mu$ A to the power consumption of the MCU).

- 4 Tips when using the LVD:

- A. Check that all recommendations related to reset circuit have been applied (see notes above).

- B. Check that the power supply is properly decoupled (100nF + 10 $\mu$ F close to the MCU). Refer to AN1709 and AN2017. If this cannot be done, it is recommended to put a 100nF + 1M $\Omega$  pull-down on the RESET pin.

- C. The capacitors connected on the  $\overline{RESET}$  pin and also the power supply are key to avoid any start-up marginality. In most cases, steps A and B above are sufficient for a robust solution. Otherwise, replace 10nF pull-down on the  $\overline{RESET}$  pin with a 5 $\mu$ F to 20 $\mu$ F capacitor.