Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Obsolete                                                               |

| Core Processor             | ST7                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | CANbus, I <sup>2</sup> C, SCI, SPI                                     |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 48                                                                     |

| Program Memory Size        | 32KB (32K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 1K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                            |

| Data Converters            | A/D 16x10b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 64-LQFP                                                                |

| Supplier Device Package    | -                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f521r6tatr |

ST72521xx-Auto List of tables

| Table 49.  | PWM frequency versus resolution                     |     |

|------------|-----------------------------------------------------|-----|

| Table 50.  | PWMCR register description                          |     |

| Table 51.  | PWM output signal polarity selection                |     |

| Table 52.  | PWMDCRx register description                        |     |

| Table 53.  | ARTICCSR register description                       |     |

| Table 54.  | ARTICRx register description                        |     |

| Table 55.  | PWM auto-reload timer register map and reset values |     |

| Table 56.  | Effect of low power modes on 16-bit timer           |     |

| Table 57.  | 16-bit timer interrupt control/wake-up capability   |     |

| Table 58.  | Timer modes                                         |     |

| Table 59.  | CR1 register description                            |     |

| Table 60.  | CR2 register description                            |     |

| Table 61.  | Timer clock selection                               |     |

| Table 62.  | CSR register description                            |     |

| Table 63.  | 16-bit timer register map and reset values          |     |

| Table 64.  | Effect of low power modes on SPI                    |     |

| Table 65.  | SPI interrupt control/wake-up capability            |     |

| Table 66.  | SPICR register description                          |     |

| Table 67.  | SPI master mode SCK frequency                       |     |

| Table 68.  | SPICSR register description                         |     |

| Table 69.  | SPI register map and reset values                   |     |

| Table 70.  | Frame formats                                       |     |

| Table 71.  | Effect of low power modes on SCI                    |     |

| Table 72.  | SCI interrupt control/wake-up capability            |     |

| Table 73.  | SCISR register description                          |     |

| Table 74.  | SCICR1 register description                         |     |

| Table 75.  | SCICR2 register description                         |     |

| Table 76.  | SCIBRR register description                         |     |

| Table 77.  | SCIERPR register description                        |     |

| Table 78.  | SCIETPR register description                        |     |

| Table 79.  | Baud rate selection                                 |     |

| Table 80.  | SCI register map and reset values                   |     |

| Table 81.  | Effect of low power modes on I2C                    |     |

| Table 82.  | I2C interrupt control/wake-up capability            |     |

| Table 83.  | CR register description                             |     |

| Table 84.  | SR1 register description                            |     |

| Table 85.  | SR2 register description                            |     |

| Table 86.  | CCR register description                            |     |

| Table 87.  | DR register description                             |     |

| Table 88.  | OAR1 register description                           |     |

| Table 89.  | OAR2 register description                           |     |

| Table 90.  | I2C register map and reset values                   |     |

| Table 91.  | ISR register description                            |     |

| Table 92.  | ICR register description                            |     |

| Table 93.  | CSR register description                            |     |

| Table 94.  | BRPR register description                           |     |

| Table 95.  | BTR register description                            |     |

| Table 96.  | PSR register description                            |     |

| Table 97.  | LIDHR register description                          |     |

| Table 98.  | LIDLR register description                          |     |

| Table 99.  | TECR register description                           |     |

| Table 100. | RECR register description                           | 189 |

| Table 101. | IDHRx register description                                                               |     |

|------------|------------------------------------------------------------------------------------------|-----|

| Table 102. | IDLRx register description                                                               |     |

| Table 103. | DATA0-7x register description                                                            |     |

| Table 104. | BCSRx register description                                                               |     |

| Table 105. | FHRx register description                                                                |     |

| Table 106. | FLRx register description                                                                | 192 |

| Table 107. | MHRx register description                                                                | 192 |

| Table 108. | MLRx register description                                                                |     |

| Table 109. | CAN register map and reset values                                                        |     |

| Table 110. | WKPS functionality modifications                                                         |     |

| Table 111. | Effect of low power modes on ADC                                                         |     |

| Table 112. | ADCCSR register description                                                              | 207 |

| Table 113. | ADCDRH register description                                                              | 208 |

| Table 114. | ADCDRL register description                                                              | 209 |

| Table 115. | ADC register map and reset values                                                        | 209 |

| Table 116. | Addressing modes                                                                         | 210 |

| Table 117. | CPU addressing mode overview                                                             | 210 |

| Table 118. | Inherent instructions                                                                    | 211 |

| Table 119. | Immediate instructions                                                                   |     |

| Table 120. | Instructions supporting direct, indexed, indirect, and indirect indexed addressing modes | 213 |

| Table 121. | Available relative direct/indirect instructions                                          | 214 |

| Table 122. | Instruction groups                                                                       | 214 |

| Table 123. | Instruction set overview                                                                 | 216 |

| Table 124. | Voltage characteristics                                                                  | 219 |

| Table 125. | Current characteristics                                                                  | 220 |

| Table 126. | Thermal characteristics                                                                  | 220 |

| Table 127. | General operating conditions                                                             | 221 |

| Table 128. | Operating conditions with low voltage detector (LVD)                                     | 222 |

| Table 129. | Auxiliary voltage detector (AVD) thresholds                                              | 222 |

| Table 130. | External voltage detector (EVD) thresholds                                               |     |

| Table 131. | Current consumption                                                                      |     |

| Table 132. | Oscillators, PLL and LVD current consumption                                             | 226 |

| Table 133. | On-chip peripherals current consumption                                                  |     |

| Table 134. | General timings                                                                          | 228 |

| Table 135. | External clock source                                                                    |     |

| Table 136. | Crystal and ceramic resonator oscillators                                                |     |

| Table 137. | OSCRANGE selection for typical resonators                                                |     |

| Table 138. | RC oscillator characteristics                                                            | 230 |

| Table 139. | PLL characteristics                                                                      |     |

| Table 140. | RAM supply voltage                                                                       |     |

| Table 141. | Dual voltage HDFlash memory                                                              |     |

| Table 142. | EMS test results                                                                         |     |

| Table 143. | EMI emissions                                                                            |     |

| Table 144. | ESD absolute maximum ratings                                                             |     |

| Table 145. | Electrical sensitivities                                                                 |     |

| Table 146. | I/O port pin general characteristics                                                     |     |

| Table 147. | Output driving current                                                                   |     |

| Table 148. | Asynchronous RESET pin characteristics                                                   |     |

| Table 149. | ICCSEL/V <sub>PP</sub> pin characteristics                                               |     |

| Table 150. | 8-bit PWM-ART auto-reload timer characteristics                                          |     |

| Table 151. | 16-bit timer characteristics                                                             |     |

| Table 152  | SPI characteristics                                                                      | 244 |

Table 3. Device pin description (continued)

|        | Pin<br>No. |                                  |      |                |        | Port  |     |     |     |     |     |                             |                                                     |                        |

|--------|------------|----------------------------------|------|----------------|--------|-------|-----|-----|-----|-----|-----|-----------------------------|-----------------------------------------------------|------------------------|

| N      |            |                                  | g.   | Le             | vel    |       |     | PC  | ort |     |     | Main function               |                                                     |                        |

| 980    | 64         | Name                             | Туре | Ħ              | ut     |       | Inp | out |     | Out | put | (after reset)               | Alternate                                           | function               |

| LQFP80 | LQFP64     |                                  |      | Input          | Output | float | mbn | int | ana | ОО  | ЬР  | iesetj                      |                                                     |                        |

| 23     | 17         | PD4/AIN4                         | I/O  | СТ             |        | Х     | Χ   |     | Χ   | Χ   | Χ   | Port D4                     | ADC Analog I                                        | nput 4                 |

| 24     | 18         | PD5/AIN5                         | I/O  | СТ             |        | Х     | Х   |     | Χ   | Х   | Χ   | Port D5                     | ADC Analog I                                        | nput 5                 |

| 25     | 19         | PD6/AIN6                         | I/O  | $C_{T}$        |        | Х     | Х   |     | Χ   | Х   | Χ   | Port D6                     | ADC Analog I                                        | nput 6                 |

| 26     | 20         | PD7/AIN7                         | I/O  | C <sub>T</sub> |        | X     | Х   |     | Χ   | Х   | Х   | Port D7                     | ADC Analog I                                        | nput 7                 |

| 27     | 21         | V <sub>AREF</sub> <sup>(2)</sup> | I    |                |        |       |     |     |     |     |     | Analog R                    | eference Voltag                                     | e for ADC              |

| 28     | 22         | 00/1                             | S    |                |        |       |     |     |     |     |     | Analog G                    | round Voltage                                       |                        |

| 29     | 23         | V <sub>DD_3</sub> <sup>(2)</sup> | S    |                |        |       |     |     |     |     |     | Digital Ma                  | in Supply Volta                                     | ıge                    |

| 30     | 24         | V <sub>SS_3</sub> <sup>(2)</sup> | S    |                |        |       |     |     |     |     |     | Digital Gr                  | ound Voltage                                        |                        |

| 31     | -<br>(1)   | PG4                              | I/O  | T <sub>T</sub> |        | X     | Х   |     |     | Х   | Х   | Port G4                     |                                                     |                        |

| 32     | -<br>(1)   | PG5                              | I/O  | T <sub>T</sub> |        | X     | X   |     |     | Х   | X   | Port G5                     |                                                     |                        |

| 33     | 25         | PF0/MCO/AIN8                     | I/O  | СТ             |        | X     | ei  | 1   | X   | X   | X   | Port F0                     | ort F0 Main clock out (f <sub>CPU</sub> ) ADC Analo |                        |

| 34     | 26         | PF1 (HS)/BEEP                    | I/O  | C <sub>T</sub> | HS     | X     | ei  | 1   |     | Х   | Х   | Port F1                     | Beep signal or                                      | utput                  |

| 35     | 27         | PF2 (HS)                         | I/O  | C <sub>T</sub> | HS     | X     |     | ei1 |     | Х   | Χ   | Port F2                     |                                                     |                        |

| 36     | 28         | PF3/OCMP2_A/AIN9                 | I/O  | C <sub>T</sub> |        | x     | Х   |     | X   | х   | X   | Port F3                     | Timer A<br>Output<br>Compare 2                      | ADC Analog<br>Input 9  |

| 37     | 29         | PF4/OCMP1_A/AIN10                | I/O  | C <sub>T</sub> |        | x     | х   |     | X   | х   | X   | Port F4                     | Timer A<br>Output<br>Compare 1                      | ADC Analog<br>Input 10 |

| 38     | 30         | PF5/ICAP2_A/AIN11                | I/O  | C <sub>T</sub> |        | X     | Х   |     | Х   | Х   | Х   | Port F5                     | Timer A Input<br>Capture 2                          | ADC Analog<br>Input 11 |

| 39     | 31         | PF6 (HS)/ICAP1_A                 | I/O  | C <sub>T</sub> | HS     | X     | Х   |     |     | Х   | Х   | Port F6                     | Timer A Input                                       | Capture 1              |

| 40     | 32         | PF7 (HS)/EXTCLK_A                | I/O  | C <sub>T</sub> | HS     | X     | Х   |     |     | Х   | Х   | Port F7                     | Timer A External Clock<br>Source                    |                        |

| 41     | 33         | V <sub>DD_0</sub> <sup>(2)</sup> | S    |                |        |       |     |     |     |     |     | Digital Main Supply Voltage |                                                     | ıge                    |

| 42     | 34         | V <sub>SS_0</sub> <sup>(2)</sup> | S    |                |        |       |     |     |     |     |     | Digital Ground Voltage      |                                                     |                        |

| 43     | 35         | PC0/OCMP2_B/AIN12                | I/O  | СТ             |        | x     | Х   |     | Х   | х   | x   | Port C0                     | Timer B<br>Output<br>Compare 2                      | ADC Analog<br>Input 12 |

| 44     | 36         | PC1/OCMP1_B/AIN13                | I/O  | C <sub>T</sub> |        | X     | Х   |     | Х   | Х   | Х   | Port C1                     | Timer B<br>Output<br>Compare 1                      | ADC Analog<br>Input 13 |

## 4 Flash program memory

### 4.1 Introduction

The ST7 dual voltage High Density Flash (HDFlash) is a non-volatile memory that can be electrically erased as a single block or by individual sectors and programmed on a byte-by-byte basis using an external V<sub>PP</sub> supply.

The HDFlash devices can be programmed and erased off-board (plugged in a programming tool) or on-board using ICP (in-circuit programming) or IAP (in-application programming).

The array matrix organization allows each sector to be erased and reprogrammed without affecting other sectors.

### 4.2 Main features

- 3 Flash programming modes:

- Insertion in a programming tool. In this mode, all sectors including option bytes can be programmed or erased.

- ICP (in-circuit programming). In this mode, all sectors including option bytes can be programmed or erased without removing the device from the application board.

- IAP (in-application programming). In this mode, all sectors except Sector 0 can be programmed or erased without removing the device from the application board and while the application is running.

- ICT (in-circuit testing) for downloading and executing user application test patterns in RAM

- Readout protection

- Register Access Security System (RASS) to prevent accidental programming or erasing

#### 4.3 Structure

The Flash memory is organized in sectors and can be used for both code and data storage.

Depending on the overall Flash memory size in the microcontroller device, there are up to three user sectors (see *Table 5*). Each of these sectors can be erased independently to avoid unnecessary erasing of the whole Flash memory when only a partial erasing is required.

Table 5. Sectors available in Flash devices

| Flash size (bytes) | Available sectors |

|--------------------|-------------------|

| 4K                 | Sector 0          |

| 8K                 | Sectors 0, 1      |

| > 8K               | Sectors 0, 1, 2   |

The first two sectors have a fixed size of 4 Kbytes (see *Figure 5*). They are mapped in the upper part of the ST7 addressing space so the reset and interrupt vectors are located in Sector 0 (F000h-FFFFh).

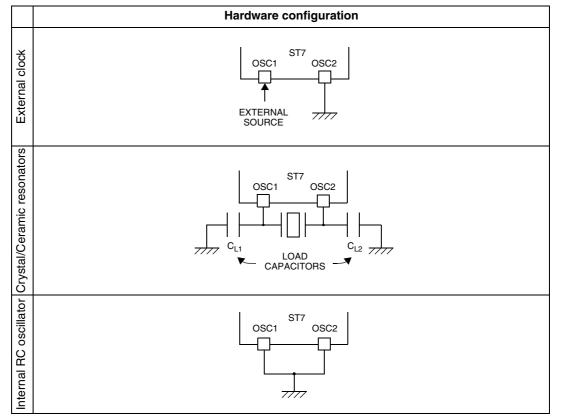

### Crystal/ceramic oscillators

This family of oscillators has the advantage of producing a very accurate rate on the main clock of the ST7. The selection within a list of four oscillators with different frequency ranges has to be done by option byte in order to reduce consumption (refer to Section 22.1.1: Flash configuration on page 257 for more details on the frequency ranges). In this mode of the multi-oscillator, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and start-up stabilization time. The loading capacitance values must be adjusted according to the selected oscillator.

These oscillators are not stopped during the RESET phase to avoid losing time in the oscillator start-up phase.

#### Internal RC oscillator

This oscillator allows a low cost solution for the main clock of the ST7 using only an internal resistor and capacitor. Internal RC oscillator mode has the drawback of a lower frequency accuracy and should not be used in applications that require accurate timing.

In this mode, the two oscillator pins have to be tied to ground.

Table 10. ST7 clock sources

Interrupts ST72521xx-Auto

Table 26. Nested interrupts register map and reset values

| Address (Hex.) | Register label       | 7          | 6          | 5          | 4          | 3          | 2          | 1          | 0          |

|----------------|----------------------|------------|------------|------------|------------|------------|------------|------------|------------|

|                |                      | е          | i1         | е          | ei0        |            | MCC        |            | LI         |

| 0024h          | ISPR0<br>Reset value | I1_3<br>1  | I0_3<br>1  | I1_2<br>1  | 10_2<br>1  | 11_1<br>1  | I0_1<br>1  | 1          | 1          |

|                |                      | S          | PI         | CA         | AN         | е          | i3         | е          | 2          |

| 0025h          | ISPR1<br>Reset value | l1_7<br>1  | I0_7<br>1  | I1_6<br>1  | I0_6<br>1  | I1_5<br>1  | I0_5<br>1  | I1_4<br>1  | I0_4<br>1  |

|                |                      | A۱         | /D         | S          | CI         | TIME       | ER B       | TIME       | ER A       |

| 0026h          | ISPR2<br>Reset value | l1_11<br>1 | I0_11<br>1 | I1_10<br>1 | I0_10<br>1 | I1_9<br>1  | I0_9<br>1  | I1_8<br>1  | I0_8<br>1  |

|                |                      |            |            |            |            | PWM        | IART       | 12         | С          |

| 0027h          | ISPR3<br>Reset value | 1          | 1          | 1          | 1          | l1_13<br>1 | I0_13<br>1 | l1_12<br>1 | I0_12<br>1 |

| 0028h          | EICR<br>Reset value  | IS11<br>0  | IS10<br>0  | IPB<br>0   | IS21<br>0  | IS20<br>0  | IPA<br>0   | TLIS<br>0  | TLIE<br>0  |

HALT INSTRUCTION (MCCSR.OIE = 0)**ENABLE** WATCHDOG 0 **DISABLE** WDGHALT (1) 1 WATCHDOG **OSCILLATOR OFF RESET** PERIPHERALS (2) OFF CPU OFF I[1:0] BITS 10 Ν RESET Υ Ν INTERRUPT (3) **OSCILLATOR** ON **PERIPHERALS** OFF CPU ON XX (4) I[1:0] BITS 256 OR 4096 CPU CLOCK **CYCLE** DELAY **OSCILLATOR** ON **PERIPHERALS** ON CPU ON  $XX^{(4)}$ I[1:0] BITS FETCH RESET VECTOR OR SERVICE INTERRUPT

Figure 28. Halt mode flowchart

- 1. WDGHALT is an option bit. See Section 22.1.1: Flash configuration on page 257 for more details.

- 2. Peripheral clocked with an external clock source can still be active.

- Only some specific interrupts can exit the MCU from Halt mode (such as external interrupt). Refer to Table 20: Interrupt mapping for more details.

- Before servicing an interrupt, the CC register is pushed on the stack. The I[1:0] bits of the CC register are set to the current software priority level of the interrupt routine and recovered when the CC register is popped.

ST72521xx-Auto 16-bit timer

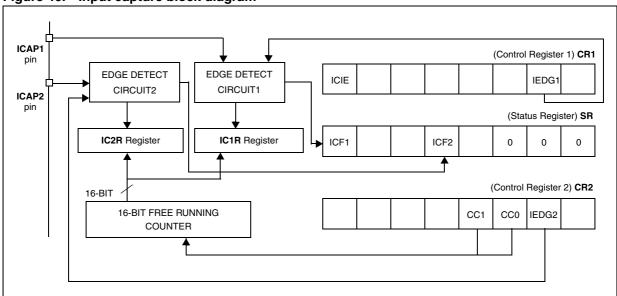

5 The alternate inputs (ICAP1 and ICAP2) are always directly connected to the timer. So any transitions on these pins activates the input capture function.

- 6 Moreover if one of the ICAPi pins is configured as an input and the second one as an output, an interrupt can be generated if the user toggles the output pin and if the ICIE bit is set.

- 7 This can be avoided if the input capture function i is disabled by reading the ICiHR (see note 1).

- 8 The TOF bit can be used with interrupt generation in order to measure events that go beyond the timer range (FFFFh).

Figure 46. Input capture block diagram

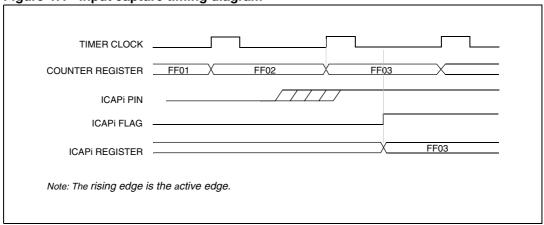

Figure 47. Input capture timing diagram

ST72521xx-Auto 16-bit timer

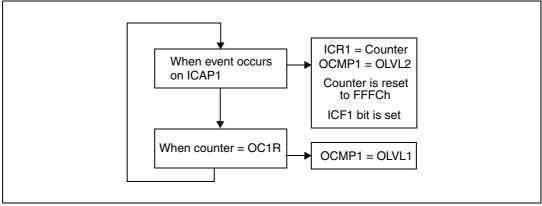

#### 13.3.6 One Pulse mode

One Pulse mode enables the generation of a pulse when an external event occurs. This mode is selected via the OPM bit in the CR2 register.

The one pulse mode uses the Input Capture1 function and the Output Compare1 function.

#### **Procedure**

To use one pulse mode:

- 1. Load the OC1R register with the value corresponding to the length of the pulse (using the appropriate formula below according to the timer clock source used).

- 2. Select the following in the CR1 register:

- Using the OLVL1 bit, select the level to be applied to the OCMP1 pin after the pulse.

- Using the OLVL2 bit, select the level to be applied to the OCMP1 pin during the pulse.

- Select the edge of the active transition on the ICAP1 pin with the IEDG1 bit (the ICAP1 pin must be configured as floating input).

- 3. Select the following in the CR2 register:

- Set the OC1E bit, the OCMP1 pin is then dedicated to the Output Compare 1 function.

- Set the OPM bit

- Select the timer clock CC[1:0] (see Table 61: Timer clock selection).

Then, on a valid event on the ICAP1 pin, the counter is initialized to FFFCh and OLVL2 bit is loaded on the OCMP1 pin, the ICF1 bit is set and the value FFFDh is loaded in the IC1R register.

Figure 51. One pulse mode cycle flowchart

Because the ICF1 bit is set when an active edge occurs, an interrupt can be generated if the ICIE bit is set.

Clearing the input capture interrupt request (that is, clearing the  $ICF_i$  bit) is done in two steps:

- 1. Reading the SR register while the ICF*i* bit is set

- 2. An access (read or write) to the ICiLR register

16-bit timer ST72521xx-Auto

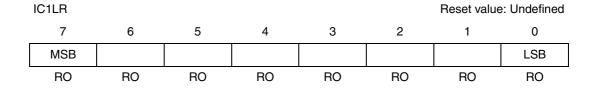

### 13.7.5 Input capture 1 low register (IC1LR)

This is an 8-bit read only register that contains the low part of the counter value (transferred by the input capture 1 event).

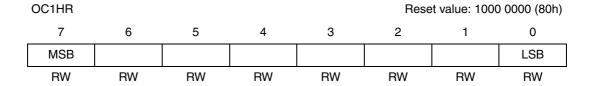

### 13.7.6 Output compare 1 high register (OC1HR)

This is an 8-bit register that contains the high part of the value to be compared to the CHR register.

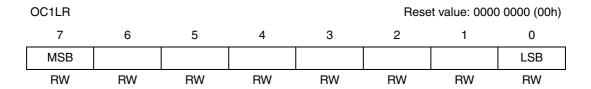

### 13.7.7 Output compare 1 low register (OC1LR)

This is an 8-bit register that contains the low part of the value to be compared to the CLR register.

### 13.7.8 Output compare 2 high register (OC2HR)

This is an 8-bit register that contains the high part of the value to be compared to the CHR register.

| OC2HR |    |    |    |    | Rese | t value: 1000 | 0000 (80h) |

|-------|----|----|----|----|------|---------------|------------|

| 7     | 6  | 5  | 4  | 3  | 2    | 1             | 0          |

| MSB   |    |    |    |    |      |               | LSB        |

| RW    | RW | RW | RW | RW | RW   | RW            | RW         |

# 14.8 SPI registers

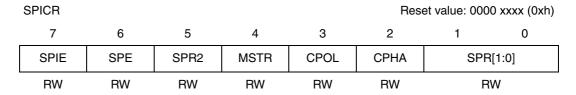

## 14.8.1 Control register (SPICR)

Table 66. SPICR register description

| Bit | Name | Function                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | SPIE | Serial Peripheral Interrupt Enable  This bit is set and cleared by software. 0: Interrupt is inhibited 1: An SPI interrupt is generated whenever SPIF = 1, MODF = 1 or OVR = 1 in the SPICSR register.                                                                                                                                                                                       |

| 6   | SPE  | Serial Peripheral Output Enable  This bit is set and cleared by software. It is also cleared by hardware when, in master mode, $\overline{SS} = 0$ (see Master mode fault (MODF) on page 131). The SPE bit is cleared by reset, so the SPI peripheral is not initially connected to the external pins.  0: I/O pins free for general purpose I/O  1: SPI I/O pin alternate functions enabled |

| 5   | SPR2 | Divider Enable  This bit is set and cleared by software and is cleared by reset. It is used with the SPR[1:0] bits to set the baud rate. Refer to Table 67.  0: Divider by 2 enabled  1: Divider by 2 disabled  Note: This bit has no effect in slave mode.                                                                                                                                  |

| 4   | MSTR | Master Mode  This bit is set and cleared by software. It is also cleared by hardware when, in master mode, $\overline{SS} = 0$ (see Master mode fault (MODF) on page 131).  0: Slave mode  1: Master mode. The function of the SCK pin changes from an input to an output and the functions of the MISO and MOSI pins are reversed.                                                          |

| 3   | CPOL | Clock Polarity This bit is set and cleared by software. This bit determines the idle state of the serial Clock. The CPOL bit affects both the master and slave modes.  0: SCK pin has a low level idle state  1: SCK pin has a high level idle state  Note: If CPOL is changed at the communication byte boundaries, the SPI must be disabled by resetting the SPE bit.                      |

| 2   | СРНА | Clock Phase This bit is set and cleared by software. 0: The first clock transition is the first data capture edge. 1: The second clock transition is the first capture edge. Note: The slave must have the same CPOL and CPHA settings as the master.                                                                                                                                        |

Table 66. SPICR register description (continued)

| Bit | Name     | Function                                                                                                                                                                                                                             |

|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1:0 | SPR[1:0] | Serial Clock Frequency These bits are set and cleared by software. Used with the SPR2 bit, they select the baud rate of the SPI serial clock SCK output by the SPI in master mode.  Note: These 2 bits have no effect in slave mode. |

Table 67. SPI master mode SCK frequency

| Serial clock          | SPR2 | SPR1 | SPR0 |

|-----------------------|------|------|------|

| f <sub>CPU</sub> /4   | 1    | 0    | 0    |

| f <sub>CPU</sub> /8   | 0    | 0    | 0    |

| f <sub>CPU</sub> /16  | 0    | 0    | 1    |

| f <sub>CPU</sub> /32  | 1    | 1    | 0    |

| f <sub>CPU</sub> /64  | 0    | 1    | 0    |

| f <sub>CPU</sub> /128 | 0    | 1    | 1    |

### 14.8.2 Control/status register (SPICSR)

**SPICSR** Reset value: 0000 0000 (00h) 7 6 5 4 2 0 WCOL SOD **SPIF** OVR MODF Reserved SSM SSI RO RO RO RO RWRW RW

Table 68. SPICSR register description

| Bit | Name | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | SPIF | Serial Peripheral Data Transfer Flag  This bit is set by hardware when a transfer has been completed. An interrupt is generated if SPIE = 1 in the SPICR register. It is cleared by a software sequence (an access to the SPICSR register followed by a write or a read to the SPIDR register).  0: Data transfer is in progress or the flag has been cleared  1: Data transfer between the device and an external device has been completed. While the SPIF bit is set, all writes to the SPIDR register are inhibited until the SPICSR register is read. |

| 6   | WCOL | Write Collision status  This bit is set by hardware when a write to the SPIDR register is done during a transmit sequence. It is cleared by a software sequence (see Figure 60).  0: No write collision occurred.  1: A write collision has been detected.                                                                                                                                                                                                                                                                                                 |

| 5   | OVR  | SPI Overrun error  This bit is set by hardware when the byte currently being received in the shift register is ready to be transferred into the SPIDR register while SPIF = 1 (see Overrun condition (OVR) on page 131). An interrupt is generated if SPIE = 1 in SPICR register. The OVR bit is cleared by software reading the SPICSR register.  0: No overrun error  1: Overrun error detected                                                                                                                                                          |

## 15 Serial communications interface (SCI)

### 15.1 Introduction

The Serial Communications Interface (SCI) offers a flexible means of full-duplex data exchange with external equipment requiring an industry standard NRZ asynchronous serial data format. The SCI offers a very wide range of baud rates using two baud rate generator systems.

### 15.2 Main features

- Full duplex, asynchronous communications

- NRZ standard format (Mark/Space)

- Dual baud rate generator systems

- Independently programmable transmit and receive baud rates up to 500K baud

- Programmable data word length (8 or 9 bits)

- Receive buffer full, Transmit buffer empty and End of Transmission flags

- 2 receiver wake-up modes:

- Address bit (MSB)

- Idle line

- Muting function for multiprocessor configurations

- Separate enable bits for Transmitter and Receiver

- 4 error detection flags:

- Overrun error

- Noise error

- Frame error

- Parity error

- 5 interrupt sources with flags:

- Transmit data register empty

- Transmission complete

- Receive data register full

- Idle line received

- Overrun error detected

- Parity control:

- Transmits parity bit

- Checks parity of received data byte

- Reduced power consumption mode

Table 84. SR1 register description (continued)

| Bit | Name | Function                                                                                                                                                                                                                                                                                                                                                                                               |

|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | M/SL | Master/Slave This bit is set by hardware as soon as the interface is in Master mode (writing START = 1). It is cleared by hardware after detecting a Stop condition on the bus or a loss of arbitration (ARLO = 1). It is also cleared when the interface is disabled (PE = 0).  0: Slave mode 1: Master mode                                                                                          |

| 0   | SB   | Start bit (Master mode)  This bit is set by hardware as soon as the Start condition is generated (following a write START = 1). An interrupt is generated if ITE = 1. It is cleared by software reading SR1 register followed by writing the address byte in DR register. It is also cleared by hardware when the interface is disabled (PE = 0).  0: No Start condition  1: Start condition generated |

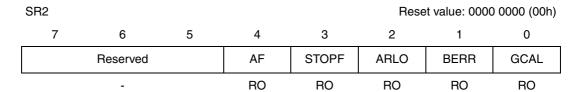

# 16.7.3 I<sup>2</sup>C status register 2 (SR2)

Table 85. SR2 register description

| Bit | Name  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:5 | -     | Reserved. Forced to 0 by hardware.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4   | AF    | Acknowledge failure  This bit is set by hardware when no acknowledge is returned. An interrupt is generated if ITE = 1. It is cleared by software reading SR2 register or by hardware when the interface is disabled (PE = 0).  The SCL line is not held low while AF = 1 but by other flags (SB or BTF) that are set at the same time.  0: No acknowledge failure  1: Acknowledge failure  Note: When an AF event occurs, the SCL line is not held low; however, the SDA line can remain low if the last bits transmitted are all 0. It is then necessary to release both lines by software. |

| 3   | STOPF | Stop detection (Slave mode)  This bit is set by hardware when a Stop condition is detected on the bus after an acknowledge (if ACK = 1). An interrupt is generated if ITE = 1. It is cleared by software reading SR2 register or by hardware when the interface is disabled (PE = 0).  The SCL line is not held low while STOPF = 1.  0: No Stop condition detected  1: Stop condition detected                                                                                                                                                                                               |

Table 86. CCR register description (continued)

| Bit | Name    | Function                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 6:0 | CC[6:0] | 7-bit clock divider  These bits select the speed of the bus ( $f_{SCL}$ ) depending on the $I^2C$ mode. They are not cleared when the interface is disabled (PE = 0).  Refer to Section 20: Electrical characteristics for the table of values.  Note: The programmed $f_{SCL}$ assumes no load on SCL and SDA lines. |  |  |  |  |

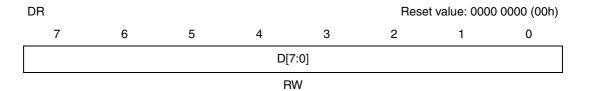

# 16.7.5 I<sup>2</sup>C data register (DR)

Table 87. DR register description

| Bit | Name   | Function                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | D[7:0] | 8-bit Data Register  These bits contain the byte to be received or transmitted on the bus.  Transmitter mode: Byte transmission start automatically when the software writes in the DR register.  Receiver mode: The first data byte is received automatically in the DR register using the least significant bit of the address.  Then, the following data bytes are received one by one after reading the DR register. |

# 16.7.6 I<sup>2</sup>C own address register (OAR1)

| OAR1 Reset value: 0000 0000 (0 |      |      |      |      |      |      |      |      |

|--------------------------------|------|------|------|------|------|------|------|------|

|                                | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|                                | ADD7 | ADD6 | ADD5 | ADD4 | ADD3 | ADD2 | ADD1 | ADD0 |

| ,                              | RW   |

Electrical characteristics ST72521xx-Auto

## 20.6 Memory characteristics

### 20.6.1 RAM and hardware registers

Table 140. RAM supply voltage

| Symbol   | Parameter                          | Conditions           | Min | Тур | Max | Unit |

|----------|------------------------------------|----------------------|-----|-----|-----|------|

| $V_{RM}$ | Data retention mode <sup>(1)</sup> | Halt mode (or RESET) | 1.6 |     |     | V    |

<sup>1.</sup> Minimum  $V_{\rm DD}$  supply voltage without losing data stored in RAM (in Halt mode or under RESET) or in hardware registers (only in Halt mode). Not tested in production.

### 20.6.2 Flash memory

Table 141. Dual voltage HDFlash memory

| Symbol                                  | Parameter                                   | Conditions                          | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit   |  |

|-----------------------------------------|---------------------------------------------|-------------------------------------|--------------------|-----|--------------------|--------|--|

| f.                                      | Operating fraguency                         | Read mode                           | 0                  |     | 8                  | - MHz  |  |

| f <sub>CPU</sub>                        | Operating frequency                         | Write / Erase mode                  | 1                  |     | 8                  |        |  |

| $V_{PP}$                                | Programming voltage <sup>(2)</sup>          | $4.5V \le V_{DD} \le 5.5V$          | 11.4               |     | 12.6               | V      |  |

|                                         |                                             | Run mode (f <sub>CPU</sub> = 4 MHz) |                    |     | 3                  | mA     |  |

| I <sub>DD</sub>                         | Supply current <sup>(3)</sup>               | Write / Erase                       |                    | 0   |                    | IIIA   |  |

|                                         |                                             | Power down mode / HALT              |                    | 1   | 10                 |        |  |

|                                         | V <sub>PP</sub> current <sup>(3)</sup>      | Read (V <sub>PP</sub> = 12V)        |                    |     | 200                | μΑ     |  |

| l <sub>PP</sub>                         | Vpp current                                 | Write / Erase                       |                    |     | 30                 | mA     |  |

| t <sub>VPP</sub>                        | Internal V <sub>PP</sub> stabilization time |                                     |                    | 10  |                    | μs     |  |

| t <sub>RET</sub>                        | Data retention                              | T <sub>A</sub> = 55°C               | 20                 |     |                    | years  |  |

| N <sub>RW</sub>                         | Write erase cycles                          | T <sub>A</sub> = 85°C               | 100                |     |                    | cycles |  |

| T <sub>PROG</sub><br>T <sub>ERASE</sub> | Programming or erasing temperature range    |                                     | -40                | 25  | 85                 | °C     |  |

<sup>1.</sup> Data based on characterization results, not tested in production

Warning: Do not connect 12V to  $V_{PP}$  before  $V_{DD}$  is powered on, as this may damage the device.

<sup>2.</sup> V<sub>PP</sub> must be applied only during the programming or erasing operation and not permanently for reliability reasons

<sup>3.</sup> Data based on simulation results, not tested in production

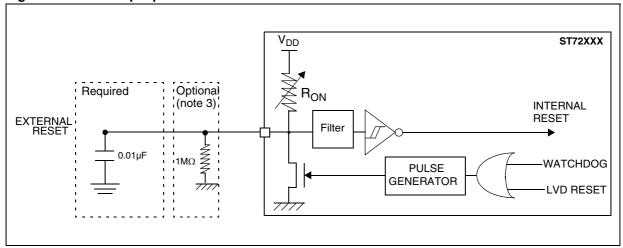

Figure 105. RESET pin protection when LVD is enabled

Note: 1 The reset network protects the device against parasitic resets.

The output of the external reset circuit must have an open-drain output to drive the ST7 reset pad. Otherwise the device can be damaged when the ST7 generates an internal reset (LVD or watchdog).

Whether the reset source is internal or external, the user must ensure that the level on the  $\overline{RESET}$  pin can go below the  $V_{IL}$  maximum level specified in Section 20.9.1 on page 240. Otherwise the reset will not be taken into account internally.

Because the reset circuit is designed to allow the internal RESET to be output in the  $\overline{RESET}$  pin, the user must ensure that the current sunk on the  $\overline{RESET}$  pin is less than the absolute maximum value specified for  $I_{INJ(RESET)}$  in Section 20.2.2 on page 220.

- When the LVD is enabled, it is recommended not to connect a pull-up resistor or capacitor. A 10nF pull-down capacitor is required to filter noise on the reset line.

- 3 In case a capacitive power supply is used, it is recommended to connect a  $1M\Omega$  pull-down resistor to the  $\overline{RESET}$  pin to discharge any residual voltage induced by the capacitive effect of the power supply (this will add  $5\mu$ A to the power consumption of the MCU).

- 4 Tips when using the LVD:

- A. Check that all recommendations related to reset circuit have been applied (see notes above).

- B. Check that the power supply is properly decoupled (100nF + 10 $\mu$ F close to the MCU). Refer to AN1709 and AN2017. If this cannot be done, it is recommended to put a 100nF + 1M $\Omega$  pull-down on the RESET pin.

- C. The capacitors connected on the  $\overline{RESET}$  pin and also the power supply are key to avoid any start-up marginality. In most cases, steps A and B above are sufficient for a robust solution. Otherwise, replace 10nF pull-down on the  $\overline{RESET}$  pin with a 5 $\mu$ F to 20 $\mu$ F capacitor.

Figure 118. 64-pin (14x14) low profile quad flat package outline

Table 159. 64-pin (14x14) low profile quad flat package mechanical data

| 142.5 1001 | • . p (1 1X 1 | <u>, , , , , , , , , , , , , , , , , , , </u> | o quan nat p | inches <sup>(1)</sup> |        |        |  |

|------------|---------------|-----------------------------------------------|--------------|-----------------------|--------|--------|--|

| Dimension  | mm            |                                               |              | Inches                |        |        |  |

|            | Min           | Тур                                           | Max          | Min                   | Тур    | Max    |  |

| Α          |               |                                               | 1.600        |                       |        | 0.0630 |  |

| A1         | 0.050         |                                               | 0.150        | 0.0020                |        | 0.0059 |  |

| A2         | 1.350         | 1.400                                         | 1.450        | 0.0531                | 0.0551 | 0.0571 |  |

| b          | 0.300         | 0.370                                         | 0.450        | 0.0118                | 0.0146 | 0.0177 |  |

| С          | 0.090         |                                               | 0.200        | 0.0035                |        | 0.0079 |  |

| D          |               | 16.000                                        |              |                       | 0.6299 |        |  |

| D1         |               | 14.000                                        |              |                       | 0.5512 |        |  |

| E          |               | 16.000                                        |              |                       | 0.6299 |        |  |

| E1         |               | 14.000                                        |              |                       | 0.5512 |        |  |

| е          |               | 0.800                                         |              |                       | 0.0315 |        |  |

| θ          | 0°            | 3.5°                                          | 7°           | 0°                    | 3.5°   | 7°     |  |

| L          | 0.450         | 0.600                                         | 0.750        | 0.0177                | 0.0236 | 0.0295 |  |

| L1         |               | 1.000                                         |              |                       | 0.0394 | _      |  |

<sup>1.</sup> Values in inches are converted from mm and rounded to 4 decimal digits.

Table 164. Option byte 1 bit description (continued)

| Bit    | Name          | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OPT5:4 | OSCTYPE[1:0]  | Oscillator type These option bits select the ST7 main clock source type. 00: Clock source = Resonator oscillator 01: Reserved 10: Clock source = Internal RC oscillator 11: Clock source = External source                                                                                                                                                                                                                                                                                    |

| OPT3:1 | OSCRANGE[2:0] | Oscillator range When the resonator oscillator type is selected, these option bits select the resonator oscillator current source corresponding to the frequency range of the used resonator. Otherwise, these bits are used to select the normal operating frequency range (see <i>Table 166: Oscillator</i> frequency range selection (OPT3:1)).                                                                                                                                            |

| ОРТ0   | PLLOFF        | PLL activation  This option bit activates the PLL which allows multiplication by two of the main input clock frequency. The PLL must not be used with the internal RC oscillator or with external clock source. The PLL is guaranteed only with an input frequency between 2 and 4 MHz.  0: PLL x2 enabled  1: PLL x2 disabled  Caution: The PLL can be enabled only if the "OSCRANGE" (OPT3:1) bits are configured to "MP - 2~4 MHz". Otherwise, the device functionality is not guaranteed. |

Table 165. Package selection (OPT7)

| Version | Selected package | PKG1 | PKG0 |

|---------|------------------|------|------|

| М       | LQFP80           | 1    | 1    |

| (A)R    | LQFP64           | 1    | 0    |

Note:

On the chip, each I/O port has eight pads. Pads that are not bonded to external pins are in input pull-up configuration after reset. The configuration of these pads must be kept at reset state to avoid added current consumption.

Table 166. Oscillator frequency range selection (OPT3:1)

| Tun                     | ical fraguency range | OSCRANGE |   |   |  |

|-------------------------|----------------------|----------|---|---|--|

| Typical frequency range |                      | 2        | 1 | 0 |  |

| LP                      | 1~2 MHz              | 0        | 0 | 0 |  |

| MP                      | 2~4 MHz              | 0        | 0 | 1 |  |

| MS                      | 4~8 MHz              | 0        | 1 | 0 |  |

| HS                      | 8~16 MHz             | 0        | 1 | 1 |  |

Known limitations ST72521xx-Auto

```

; check for falling edge

cp A, #$02

jrne OUT

TNZ Y

jrne OUT

LD A, #$01

LD sema, A

; set the semaphore to '1' if edge is detected

; reset the interrupt mask

LD A, sema

; check the semaphore status

CP A, #$01

jrne OUT

call call_routine

; call the interrupt routine

RIM

OUT:

RIM

JP while_loop

.call_routine

; entry to call_routine

PUSH A

PUSH X

PUSH CC

.ext1_rt

; entry to interrupt routine

LD A, #$00

LD sema, A

```

IRET