Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

| Product Status             | Obsolete                                                             |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | ST7                                                                  |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 8MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, SCI, SPI                                   |

| Peripherals                | LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 48                                                                   |

| Program Memory Size        | 60KB (60K x 8)                                                       |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 2K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                          |

| Data Converters            | A/D 16x10b                                                           |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                   |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 64-LQFP                                                              |

| Supplier Device Package    | -                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f521r9tc |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address         | Block                   | Register label   | Register name                                 | Reset status | Remarks          |

|-----------------|-------------------------|------------------|-----------------------------------------------|--------------|------------------|

| 0070h<br>0071h  | ADC                     | ADCCSR<br>ADCDRH | Control/Status Register<br>Data High Register | 00h<br>00h   | R/W<br>Read Only |

| 007111<br>0072h | ADO                     | ADCDRL           | Data Low Register                             | 00h          | Read Only        |

| 0073h           |                         | PWMDCR3          | PWM AR Timer Duty Cycle Register 3            | 00h          | R/W              |

| 0074h           |                         | PWMDCR2          | PWM AR Timer Duty Cycle Register 2            | 00h          | R/W              |

| 0075h           |                         | PWMDCR1          | PWM AR Timer Duty Cycle Register 1            | 00h          | R/W              |

| 0076h           |                         | PWMDCR0          | PWM AR Timer Duty Cycle Register 0            | 00h          | R/W              |

| 0077h           |                         | PWMCR            | PWM AR Timer Control Register                 | 00h          | R/W              |

| 0078h           | PWM ART                 | ARTCSR           | Auto-Reload Timer Control/Status Register     | 00h          | R/W              |

| 0079h           |                         | ARTCAR           | Auto-Reload Timer Counter Access Register     | 00h          | R/W              |

| 007Ah           |                         | ARTARR           | Auto-Reload Timer Auto-Reload Register        | 00h          | R/W              |

| 007Bh           |                         | ARTICCSR         | AR Timer Input Capture Control/Status Reg.    | 00h          | R/W              |

| 007Ch           |                         | ARTICR1          | AR Timer Input Capture Register 1             | 00h          | Read Only        |

| 007Dh           |                         | ARTICR2          | AR Timer Input Capture Register 1             | 00h          | Read Only        |

| 007Eh<br>007Fh  | Reserved Area (2 bytes) |                  |                                               |              |                  |

## Table 4. Hardware register map (continued)

1. The contents of the I/O port DR registers are readable only in output configuration. In input configuration, the values of the I/O pins are returned instead of the DR register contents.

2. The bits associated with unavailable pins must always keep their reset value.

# Note: Legend: x = undefined, R/W = read/write

## Halt mode recommendations

- Make sure that an external event is available to wake up the microcontroller from Halt mode.

- When using an external interrupt to wake up the microcontroller, re-initialize the corresponding I/O as "Input Pull-up with Interrupt" before executing the HALT instruction. The main reason for this is that the I/O may be wrongly configured due to external interference or by an unforeseen logical condition.

- For the same reason, reinitialize the level sensitiveness of each external interrupt as a precautionary measure.

- The opcode for the HALT instruction is 0x8E. To avoid an unexpected HALT instruction due to a program counter failure, it is advised to clear all occurrences of the data value 0x8E from memory. For example, avoid defining a constant in ROM with the value 0x8E.

- As the HALT instruction clears the interrupt mask in the CC register to allow interrupts, the user may choose to clear all pending interrupt bits before executing the HALT instruction. This avoids entering other peripheral interrupt routines after executing the external interrupt routine corresponding to the wake-up event (reset or external interrupt).

## **Related documentation**

ST7 Keypad Decoding Techniques, Implementing Wake-Up on Keystroke (AN 980) How to Minimize the ST7 Power Consumption (AN1014) Using an active RC to wake up the ST7LITE0 from power saving mode (AN1605)

## WHERE:

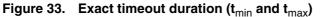

t<sub>min0</sub> = (LSB + 128) x 64 x t<sub>OSC2</sub>

$t_{max0} = 16384 \text{ x} t_{OSC2}$

$t_{OSC2}$  = 125ns if  $f_{OSC2}$  = 8 MHz

CNT = Value of T[5:0] bits in the WDGCR register (6 bits)

MSB and LSB are values from the table below depending on the timebase selected by the TB[1:0] bits in the MCCSR register

| TB1 bit<br>(MCCSR reg.) | TB0 bit<br>(MCCSR reg.) | Selected MCCSR timebase | MSB | LSB |

|-------------------------|-------------------------|-------------------------|-----|-----|

| 0                       | 0                       | 2ms                     | 4   | 59  |

| 0                       | 1                       | 4ms                     | 8   | 53  |

| 1                       | 0                       | 10ms                    | 20  | 35  |

| 1                       | 1                       | 25ms                    | 49  | 54  |

To calculate the minimum Watchdog Timeout (t<sub>min</sub>):

**IF** CNT <

$$\left[\frac{\text{MSB}}{4}\right]$$

**THEN**

$$t_{min} = t_{min0} + 16384 \times CNT \times t_{osc2}$$

**ELSE**  $t_{min} = t_{min0} + \left[ 16384 \times \left( CNT - \left[ \frac{4CNT}{MSB} \right] \right) + (192 + LSB) \times 64 \times \left[ \frac{4CNT}{MSB} \right] \right] \times t_{osc2}$

To calculate the maximum Watchdog Timeout (t<sub>max</sub>):

$$\begin{aligned} \textbf{IF} \ \textbf{CNT} \leq & \left[\frac{\textbf{MSB}}{4}\right] & \textbf{THEN} \ \textbf{t}_{max} = \textbf{t}_{max0} + 16384 \times \textbf{CNT} \times \textbf{t}_{osc2} \\ & \textbf{ELSE} \ \textbf{t}_{max} = \textbf{t}_{max0} + \left[16384 \times \left(\textbf{CNT} - \left[\frac{4\textbf{CNT}}{\textbf{MSB}}\right]\right) + (192 + \textbf{LSB}) \times 64 \times \left[\frac{4\textbf{CNT}}{\textbf{MSB}}\right]\right] \times \textbf{t}_{osc2} \end{aligned}$$

**Note:** In the above formulae, division results must be rounded down to the next integer value. **Example:**

With 2ms timeout selected in MCCSR register

| Value of T[5:0] bits in<br>WDGCR register (Hex.) | Min. Watchdog<br>Timeout (ms)<br>t <sub>min</sub> | Max. Watchdog<br>Timeout (ms)<br>t <sub>max</sub> |

|--------------------------------------------------|---------------------------------------------------|---------------------------------------------------|

| 00                                               | 1.496                                             | 2.048                                             |

| 3F                                               | 128                                               | 128.552                                           |

Figure 39. External event detector example (3 counts)

# 12.2.8 Input capture function

This mode allows the measurement of external signal pulse widths through ARTICRx registers.

Each input capture can generate an interrupt independently on a selected input signal transition. This event is flagged by a set of the corresponding CFx bits of the Input Capture Control/Status register (ARTICCSR).

These input capture interrupts are enabled through the CIEx bits of the ARTICCSR register.

The active transition (falling or rising edge) is software programmable through the CSx bits of the ARTICCSR register.

The read only input capture registers (ARTICRx) are used to latch the auto-reload counter value when a transition is detected on the ARTICx pin (CFx bit set in ARTICCSR register). After fetching the interrupt vector, the CFx flags can be read to identify the interrupt source.

Note: After a capture detection, data transfer in the ARTICRx register is inhibited until it is read (clearing the CFx bit).

The timer interrupt remains pending while the CFx flag is set when the interrupt is enabled (CIEx bit set). This means that the ARTICRx register has to be read at each capture event to clear the CFx flag.

The timing resolution is given by auto-reload counter cycle time (1/f<sub>COUNTER</sub>).

Note: During Halt mode, if both the input capture and the external clock are enabled, the ARTICRx register value is not guaranteed if the input capture pin and the external clock change simultaneously.

If the timer clock is an external clock, the formula is:

$$\Delta OC iR = \Delta t * f_{EXT}$$

Where:

$\Delta t$  = Output compare period (in seconds)

f<sub>CPU</sub> = External timer clock frequency (in hertz)

Clearing the output compare interrupt request (that is, clearing the OCF*i* bit) is done by:

- 1. Reading the SR register while the OCF*i* bit is set

- 2. An access (read or write) to the OCiLR register

The following procedure is recommended to prevent the OCF*i* bit from being set between the time it is read and the write to the OC*i*R register:

- Write to the OC*i*HR register (further compares are inhibited).

- Read the SR register (first step of the clearance of the OCF*i* bit, which may be already set).

- Write to the OC*i*LR register (enables the output compare function and clears the OCF*i* bit).

- Note: 1 After a processor write cycle to the OCiHR register, the output compare function is inhibited until the OCiLR register is also written.

- 2 If the OCiE bit is not set, the OCMPi pin is a general I/O port and the OLVLi bit will not appear when a match is found but an interrupt could be generated if the OCIE bit is set.

- 3 In both internal and external clock modes, OCFi and OCMPi are set while the counter value equals the OCiR register value (see Figure 49 on page 110 for an example with f<sub>CPU</sub>/2 and Figure 50 on page 110 for an example with f<sub>CPU</sub>/4). This behavior is the same in OPM or PWM mode.

- 4 The output compare functions can be used both for generating external events on the OCMPi pins even if the input capture mode is also used.

- 5 The value in the 16-bit OCiR register and the OLVi bit should be changed after each successful comparison in order to control an output waveform or establish a new elapsed timeout.

## 13.3.5 Forced compare output capability

When the FOLV*i* bit is set by software, the OLVL*i* bit is copied to the OCMP*i* pin. The OLV*i* bit has to be toggled in order to toggle the OCMP*i* pin when it is enabled (OC*i*E bit = 1). The OCF*i* bit is then not set by hardware, and thus no interrupt request is generated.

The FOLVL*i* bits have no effect in both one pulse mode and PWM mode.

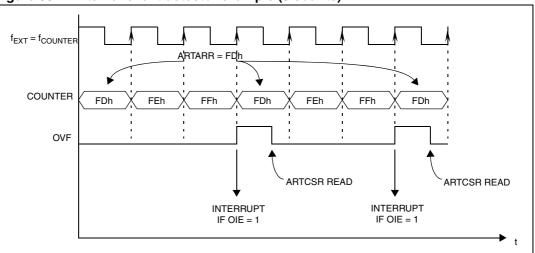

If OLVL1 = 1 and OLVL2 = 0 the length of the positive pulse is the difference between the OC2R and OC1R registers.

If OLVL1 = OLVL2 a continuous signal will be seen on the OCMP1 pin.

The OC<sub>i</sub>R register value required for a specific timing application can be calculated using the following formula:

$$OCiR value = \frac{t \cdot f_{CPU} - 5}{PRESC}$$

Where:

t

= Signal or pulse period (in seconds)

$f_{CPU} = CPU \operatorname{clock} \operatorname{frequency} (\operatorname{in} \operatorname{hertz})$

PRESC = Timer prescaler factor (2, 4 or 8 depending on CC[1:0] bits; see *Table 61: Timer clock selection*)

If the timer clock is an external clock the formula is:

$$OCiR = t * f_{EXT} - 5$$

Where:

t

Signal or pulse period (in seconds)

f<sub>EXT</sub> = External timer clock frequency (in hertz)

The Output Compare 2 event causes the counter to be initialized to FFFCh (see Figure 53).

- Note: 1 After a write instruction to the OCiHR register, the output compare function is inhibited until the OCiLR register is also written.

- 2 The OCF1 and OCF2 bits cannot be set by hardware in PWM mode therefore the Output Compare interrupt is inhibited.

- 3 The ICF1 bit is set by hardware when the counter reaches the OC2R value and can produce a timer interrupt if the ICIE bit is set and the I bit is cleared.

- 4 In PWM mode the ICAP1 pin cannot be used to perform input capture because it is disconnected to the timer. The ICAP2 pin can be used to perform input capture (ICF2 can be set and IC2R can be loaded) but the user must take care that the counter is reset each period and ICF1 can also generates interrupt if ICIE is set.

- 5 When the Pulse Width Modulation (PWM) and One Pulse Mode (OPM) bits are both set, the PWM mode is the only active one.

| Table | able 60. CH2 register description (continued) |                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|-------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Bit   | Name                                          | Function                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| 5     | OPM                                           | <ul> <li>One Pulse Mode</li> <li>0: One Pulse Mode is not active.</li> <li>1: One Pulse Mode is active, the ICAP1 pin can be used to trigger one pulse on the OCMP1 pin; the active transition is given by the IEDG1 bit. The length of the generated pulse depends on the contents of the OC1R register.</li> </ul> |  |  |  |  |

| 4     | PWM                                           | <ul> <li>Pulse Width Modulation</li> <li>0: PWM mode is not active.</li> <li>1: PWM mode is active, the OCMP1 pin outputs a programmable cyclic signal; the length of the pulse depends on the value of OC1R register; the period depends on the value of OC2R register.</li> </ul>                                  |  |  |  |  |

| 3:2   | CC[1:0]                                       | <i>Clock Control</i><br>The timer clock mode depends on these bits (see <i>Table 61</i> ).                                                                                                                                                                                                                           |  |  |  |  |

| 1     | IEDG2                                         | <ul> <li>Input Edge 2</li> <li>This bit determines which type of level transition on the ICAP2 pin will trigger the capture.</li> <li>0: A falling edge triggers the capture.</li> <li>1: A rising edge triggers the capture.</li> </ul>                                                                             |  |  |  |  |

| 0     | EXEDG                                         | <ul> <li>External Clock Edge</li> <li>This bit determines which type of level transition on the external clock pin EXTCLK will trigger the counter register.</li> <li>0: A falling edge triggers the counter register.</li> <li>1: A rising edge triggers the counter register.</li> </ul>                           |  |  |  |  |

| Table 60. | <b>CR2 register</b> | description ( | (continued) | ) |

|-----------|---------------------|---------------|-------------|---|

|-----------|---------------------|---------------|-------------|---|

## Table 61.Timer clock selection

| Timer clock                                     | CC1 | CC0 |

|-------------------------------------------------|-----|-----|

| f <sub>CPU</sub> / 4                            | 0   | 0   |

| f <sub>CPU</sub> / 2                            | 0   | 1   |

| f <sub>CPU</sub> / 8                            | 1   | 0   |

| External clock (where available) <sup>(1)</sup> | 1   | 1   |

1. If the external clock pin is not available, programming the external clock configuration stops the counter.

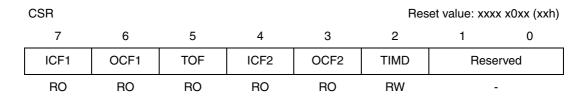

# 13.7.3 Control/status register (CSR)

When an overrun error occurs:

- The OR bit is set.

- The RDR content is not lost.

- The shift register is overwritten.

- An interrupt is generated if the RIE bit is set and the I bit is cleared in the CCR register.

The OR bit is reset by an access to the SCISR register followed by a SCIDR register read operation.

## Noise error

Oversampling techniques are used for data recovery by discriminating between valid incoming data and noise. Normal data bits are considered valid if three consecutive samples (8th, 9th, 10th) have the same bit value, otherwise the NF flag is set. In the case of start bit detection, the NF flag is set on the basis of an algorithm combining both valid edge detection and three samples (8th, 9th, 10th). Therefore, to prevent the NF flag getting set during start bit reception, there should be a valid edge detection as well as three valid samples.

When noise is detected in a frame:

- The NF flag is set at the rising edge of the RDRF bit.

- Data is transferred from the Shift register to the SCIDR register.

- No interrupt is generated. However this bit rises at the same time as the RDRF bit which itself generates an interrupt.

The NF flag is reset by a SCISR register read operation followed by a SCIDR register read operation.

During reception, if a false start bit is detected (for example, 8th, 9th, 10th samples are 011, 101, 110), the frame is discarded and the receiving sequence is not started for this frame. There is no RDRF bit set for this frame and the NF flag is set internally (not accessible to the user). This NF flag is accessible along with the RDRF bit when a next valid frame is received.

Note: If the application Start Bit is not long enough to match the above requirements, then the NF Flag may get set due to the short Start Bit. In this case, the NF flag may be ignored by the application software when the first valid byte is received.

See also Noise error causes on page 148.

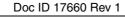

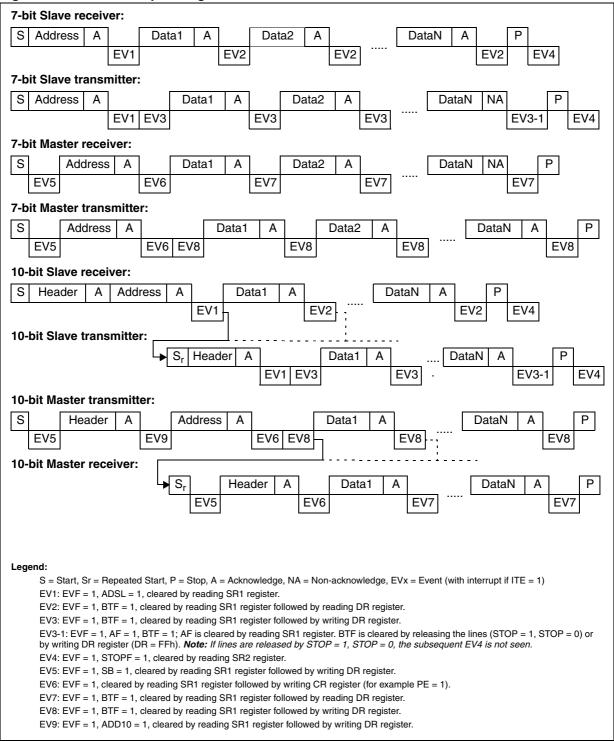

# 16.3 General description

In addition to receiving and transmitting data, this interface converts it from serial to parallel format and vice versa, using either an interrupt or polled handshake. The interrupts are enabled or disabled by software. The interface is connected to the  $I^2C$  bus by a data pin (SDAI) and by a clock pin (SCLI). It can be connected both with a standard  $I^2C$  bus and a fast  $I^2C$  bus. This selection is made by software.

# 16.3.1 Mode selection

The interface can operate in the four following modes:

- Slave transmitter/receiver

- Master transmitter/receiver

By default, it operates in slave mode.

The interface automatically switches from slave to master after it generates a START condition and from master to slave in case of arbitration loss or a STOP generation, allowing then Multimaster capability.

# 16.3.2 Communication flow

In Master mode, it initiates a data transfer and generates the clock signal. A serial data transfer always begins with a start condition and ends with a stop condition. Both start and stop conditions are generated in master mode by software.

In Slave mode, the interface is capable of recognizing its own address (7- or 10-bit), and the General Call address. The General Call address detection may be enabled or disabled by software.

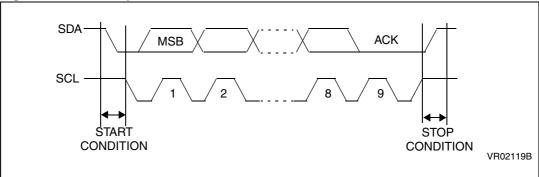

Data and addresses are transferred as 8-bit bytes, MSB first. The first byte(s) following the start condition contain the address (one in 7-bit mode, two in 10-bit mode). The address is always transmitted in Master mode.

A 9th clock pulse follows the 8 clock cycles of a byte transfer, during which the receiver must send an acknowledge bit to the transmitter. Refer to *Figure 66*.

Figure 66. I<sup>2</sup>C bus protocol

Acknowledge may be enabled and disabled by software.

The I<sup>2</sup>C interface address and/or general call address can be selected by software.

The speed of the  $I^2C$  interface may be selected between standard (up to 100 kHz) and fast  $I^2C$  (up to 400 kHz).

# 16.3.3 SDA/SCL line control

## Transmitter mode

The interface holds the clock line low before transmission to wait for the microcontroller to write the byte in the data register.

## **Receiver mode**

The interface holds the clock line low after reception to wait for the microcontroller to read the byte in the data register.

The SCL frequency ( $f_{SCL}$ ) is controlled by a programmable clock divider which depends on the  $I^2C$  bus mode.

When the I<sup>2</sup>C cell is enabled, the SDA and SCL ports must be configured as floating inputs. In this case, the value of the external pull-up resistor used depends on the application.

When the I<sup>2</sup>C cell is disabled, the SDA and SCL ports revert to being standard I/O port pins.

Figure 67. I<sup>2</sup>C interface block diagram

## Figure 68. Transfer sequencing

# 16.5 Low power modes

Table 81.

Effect of low power modes on I<sup>2</sup>C

| Mode | Effect                                                                                                                                                                                                                                          |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Wait | No effect on I <sup>2</sup> C interface.<br>I <sup>2</sup> C interrupts cause the device to exit from Wait mode.                                                                                                                                |

| Halt | $I^2C$ registers are frozen.<br>In Halt mode, the $I^2C$ interface is inactive and does not acknowledge data on the bus. The $I^2C$ interface resumes operation when the MCU is woken up by an interrupt with "exit from Halt mode" capability. |

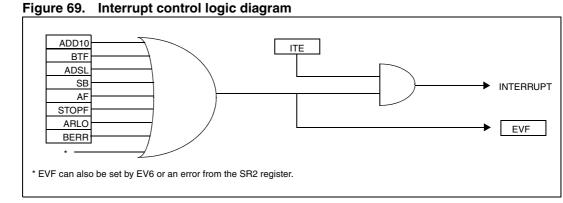

# 16.6 Interrupts

# Table 82. I<sup>2</sup>C interrupt control/wake-up capability

| Interrupt event                                    | Event flag | Enable<br>control bit | Exit from<br>Wait | Exit from<br>Halt |

|----------------------------------------------------|------------|-----------------------|-------------------|-------------------|

| 10-bit Address Sent Event (Master mode)            | ADD10      |                       |                   |                   |

| End of Byte Transfer Event                         | BTF        |                       |                   |                   |

| Address Matched Event (Slave mode)                 | ADSEL      |                       |                   |                   |

| Start Bit Generation Event (Master mode)           | SB         | ITE                   | Yes               | No                |

| Acknowledge Failure Event                          | AF         | 110                   | 162               | NO                |

| Stop Detection Event (Slave mode)                  | STOPF      |                       |                   |                   |

| Arbitration Lost Event (Multimaster configuration) | ARLO       | ]                     |                   |                   |

| Bus Error Event                                    | BERR       | ]                     |                   |                   |

Note:

The I<sup>2</sup>C interrupt events are connected to the same interrupt vector (see Interrupts chapter). They generate an interrupt if the corresponding Enable Control bit is set and the I-bit in the CC register is reset (RIM instruction).

| Address<br>(Hex.) | Page   | Register<br>label       | 7          | 6          | 5          | 4         | 3          | 2          | 1          | 0          |

|-------------------|--------|-------------------------|------------|------------|------------|-----------|------------|------------|------------|------------|

| 5A                |        | CANISR<br>Reset value   | RXIF3<br>0 | RXIF2<br>0 | RXIF1<br>0 | TXIF<br>0 | SCIF<br>0  | ORIF<br>0  | TEIF<br>0  | EPND<br>0  |

| 5B                |        | CANICR<br>Reset value   | 0          | ESCI<br>0  | RXIE<br>0  | TXIE<br>0 | SCIE<br>0  | ORIE<br>0  | TEIE<br>0  | ETX<br>0   |

| 5C                |        | CANCSR<br>Reset value   | 0          | BOFF<br>0  | EPSV<br>0  | SRTE<br>0 | NRTX<br>0  | FSYN<br>0  | WKPS<br>0  | RUN<br>0   |

| 5D                |        | CANBRPR<br>Reset value  | RJW1<br>0  | RJW0<br>0  | BRP5<br>0  | BRP4<br>0 | BRP3<br>0  | BRP2<br>0  | BRP1<br>0  | BRP0<br>0  |

| 5E                |        | CANBTR<br>Reset value   | 0          | BS22<br>0  | BS21<br>1  | BS20<br>0 | BS13<br>0  | BS12<br>0  | BS11<br>1  | BS10<br>1  |

| 5F                | / \    | CANPSR<br>Reset value   | 0          | 0          | 0          | 0         | 0          | PAGE2<br>0 | PAGE1<br>0 | PAGE0<br>0 |

| 60                | 0      | CANLIDHR<br>Reset value | LID10<br>x | LID9<br>x  | LID8<br>x  | LID7<br>x | LID6<br>x  | LID5<br>x  | LID4<br>x  | LID3<br>x  |

| 00                | 1 to 3 | CANIDHRx<br>Reset value | ID10<br>x  | ID9<br>x   | ID8<br>x   | ID7<br>x  | ID6<br>x   | ID5<br>x   | ID4<br>x   | ID3<br>x   |

| 60, 64            | 4      | CANFHRx<br>Reset value  | FIL11<br>x | FIL10<br>x | FIL9<br>x  | FIL8<br>x | FIL7<br>x  | FIL6<br>x  | FIL5<br>x  | FIL4<br>x  |

| 61                | 0      | CANLIDLR<br>Reset value | LID2<br>x  | LID1<br>x  | LID0<br>x  | LRTR<br>x | LDLC3<br>x | LDLC2<br>x | LDLC1<br>x | LDLC0<br>x |

| 01                | 1 to 3 | CANIDLRx<br>Reset value | ID2<br>x   | ID1<br>x   | ID0<br>x   | RTR<br>x  | DLC3<br>x  | DLC2<br>x  | DLC1<br>x  | DLC0<br>x  |

| 61, 65            | 4      | CANFLRx<br>Reset value  | FIL3<br>x  | FIL2<br>x  | FIL1<br>x  | FIL0<br>x | 0          | 0          | 0          | 0          |

| 62 to 69          | 1 to 3 | CANDRx<br>Reset value   | MSB<br>x   | x          | x          | x         | x          | x          | x          | LSB<br>x   |

| 62, 66            | 4      | CANMHRx<br>Reset value  | MSK11<br>x | MSK10<br>x | MSK9<br>x  | MSK8<br>x | MSK7<br>x  | MSK6<br>x  | MSK5<br>x  | MSK4<br>x  |

| 63, 67            | 4      | CANMLRx<br>Reset value  | MSK3<br>x  | MSK2<br>x  | MSK1<br>x  | MSK0<br>x | 0          | 0          | 0          | 0          |

| 6E                | 0      | CANTECR<br>Reset value  | MSB<br>0   | 0          | 0          | 0         | 0          | 0          | 0          | LSB<br>0   |

| 6F                |        | CANRECR<br>Reset value  | MSB<br>0   | 0          | 0          | 0         | 0          | 0          | 0          | LSB<br>0   |

| UL                | 1 to 3 | CANBCSRx<br>Reset value | 0          | 0          | 0          | 0         | ACC<br>0   | RDY<br>0   | BUSY<br>0  | LOCK<br>0  |

# Table 109. CAN register map and reset values

### Supply current characteristics 20.4

The following current consumption specified for the ST7 functional operating modes over temperature range does not take into account the clock source current consumption. To obtain the total device consumption, the two current values must be added (except for Halt mode, for which the clock is stopped).

#### 20.4.1 Current consumption

Table 131. Current consumption

| Symbol          | Parameter                                          | Conditions                                                                                                                                                                                                                                                    | Flash<br>devices          |                              | ROM<br>devices            |                              | Unit     |

|-----------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------------------------------|---------------------------|------------------------------|----------|

|                 |                                                    |                                                                                                                                                                                                                                                               | Тур                       | Max <sup>(1)</sup>           | Тур                       | Max <sup>(1)</sup>           |          |

|                 | Supply current in<br>Run mode <sup>(2)</sup>       |                                                                                                                                                                                                                                                               | 1.3<br>2.0<br>3.6<br>7.1  | 3.0<br>5.0<br>8.0<br>15.0    | 1.3<br>2.0<br>3.6<br>7.1  | 2.0<br>3.0<br>5.0<br>10.0    | mA       |

|                 | Supply current in Slow mode <sup>(2)</sup>         | $      f_{OSC} = 2 \text{ MHz}, \  f_{CPU} = 62.5 \text{ kHz} \\       f_{OSC} = 4 \text{ MHz}, \  f_{CPU} = 125 \text{ kHz} \\       f_{OSC} = 8 \text{ MHz}, \  f_{CPU} = 250 \text{ kHz} \\       f_{OSC} = 16 \text{ MHz}, \  f_{CPU} = 500 \text{ kHz} $ | 600<br>700<br>800<br>1100 | 2700<br>3000<br>3600<br>4000 | 600<br>700<br>800<br>1100 | 1800<br>2100<br>2400<br>3000 | μΑ       |

| I <sub>DD</sub> | Supply current in<br>Wait mode <sup>(2)</sup>      |                                                                                                                                                                                                                                                               | 1.0<br>1.5<br>2.5<br>4.5  | 3.0<br>4.0<br>5.0<br>7.0     | 1.0<br>1.5<br>2.5<br>4.5  | 1.3<br>2.0<br>3.3<br>6.0     | mA       |

|                 | Supply current in<br>Slow Wait mode <sup>(2)</sup> | $      f_{OSC} = 2 \text{ MHz}, \  f_{CPU} = 62.5 \text{ kHz} \\       f_{OSC} = 4 \text{ MHz}, \  f_{CPU} = 125 \text{ kHz} \\       f_{OSC} = 8 \text{ MHz}, \  f_{CPU} = 250 \text{ kHz} \\       f_{OSC} = 16 \text{ MHz}, \  f_{CPU} = 500 \text{ kHz} $ | 580<br>650<br>770<br>1050 | 1200<br>1300<br>1800<br>2000 | 70<br>100<br>200<br>350   | 200<br>300<br>600<br>1200    | μΑ       |

|                 | Supply current in                                  | $-40^{\circ}C \le T_A \le +85^{\circ}C$                                                                                                                                                                                                                       | <1                        | 10                           | <1                        | 10                           | μA       |

|                 | Halt mode <sup>(3)</sup>                           | -40°C <u>≤</u> T <sub>A</sub> <u>≤</u> +125°C                                                                                                                                                                                                                 | <1                        | 50                           | <1                        | 50                           | <u> </u> |

| I <sub>DD</sub> | Supply current in Active Halt mode <sup>(4)</sup>  | $f_{OSC} = 2 \text{ MHz}$<br>$f_{OSC} = 4 \text{ MHz}$<br>$f_{OSC} = 8 \text{ MHz}$<br>$f_{OSC} = 16 \text{ MHz}$                                                                                                                                             | 80<br>160<br>325<br>650   | No max.<br>guaran-<br>teed   | 15<br>30<br>60<br>120     | 25<br>50<br>100<br>200       | μΑ       |

1. Data based on characterization results, tested in production at V<sub>DD</sub> max. and f<sub>CPU</sub> max.

2.

Measurements are done in the following conditions: - Program executed from RAM, CPU running with RAM access. The increase in consumption when executing from Flash is 50%

- All I/O pins in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load)

- All peripherals in reset state.

- LVD disabled.

- Clock input (OSC1) driven by external square wave.

- In Slow and Slow Wait mode, f<sub>CPU</sub> is based on f<sub>OSC</sub> divided by 32.

- To obtain the total current consumption of the device, add the clock source (*Section 20.4.2*) and the peripheral power

consumption (Section 20.4.3)

- 3. All I/O pins in push-pull 0 mode (when applicable) with a static value at V<sub>DD</sub> or VSS (no load), LVD disabled. Data based on characterization results, tested in production at V<sub>DD</sub> max. and f<sub>CPU</sub> max.

- Data based on characterization results, not tested in production. All I/O pins in push-pull 0 mode (when applicable) with a static value at  $V_{DD}$  or  $V_{SS}$  (no load); clock input (OSC1) driven by external square wave, LVD disabled. To obtain the total current consumption of the device, add the clock source consumption (*Section 20.4.2*). 4.

# 20.6 Memory characteristics

# 20.6.1 RAM and hardware registers

## Table 140. RAM supply voltage

| Symbol          | Parameter                          | Conditions           | Min | Тур | Max | Unit |

|-----------------|------------------------------------|----------------------|-----|-----|-----|------|

| V <sub>RM</sub> | Data retention mode <sup>(1)</sup> | Halt mode (or RESET) | 1.6 |     |     | V    |

1. Minimum V<sub>DD</sub> supply voltage without losing data stored in RAM (in Halt mode or under RESET) or in hardware registers (only in Halt mode). Not tested in production.

# 20.6.2 Flash memory

## Table 141. Dual voltage HDFlash memory

| Symbol                                  | Parameter                                   | Conditions                          | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit   |  |

|-----------------------------------------|---------------------------------------------|-------------------------------------|--------------------|-----|--------------------|--------|--|

| f <sub>CPU</sub>                        | Operating frequency                         | Read mode                           | 0                  |     | 8                  | MHz    |  |

|                                         |                                             | Write / Erase mode                  | 1                  |     | 8                  | IVILIZ |  |

| V <sub>PP</sub>                         | Programming voltage <sup>(2)</sup>          | $4.5V \le V_{DD} \le 5.5V$          | 11.4               |     | 12.6               | V      |  |

| I <sub>DD</sub>                         | Supply current <sup>(3)</sup>               | Run mode (f <sub>CPU</sub> = 4 MHz) |                    |     | 3                  | mA     |  |

|                                         |                                             | Write / Erase                       |                    | 0   |                    |        |  |

|                                         |                                             | Power down mode / HALT              |                    | 1   | 10                 |        |  |

| I <sub>PP</sub>                         | V <sub>PP</sub> current <sup>(3)</sup>      | Read (V <sub>PP</sub> = 12V)        |                    |     | 200                | μA     |  |

|                                         |                                             | Write / Erase                       |                    |     | 30                 | mA     |  |

| t <sub>VPP</sub>                        | Internal V <sub>PP</sub> stabilization time |                                     |                    | 10  |                    | μs     |  |

| t <sub>RET</sub>                        | Data retention                              | $T_A = 55^{\circ}C$                 | 20                 |     |                    | years  |  |

| N <sub>RW</sub>                         | Write erase cycles                          | $T_A = 85^{\circ}C$                 | 100                |     |                    | cycles |  |

| T <sub>PROG</sub><br>T <sub>ERASE</sub> | Programming or erasing temperature range    |                                     | -40                | 25  | 85                 | °C     |  |

1. Data based on characterization results, not tested in production

2.  $V_{PP}$  must be applied only during the programming or erasing operation and not permanently for reliability reasons.

3. Data based on simulation results, not tested in production

# Warning: Do not connect 12V to $V_{PP}$ before $V_{DD}$ is powered on, as this may damage the device.

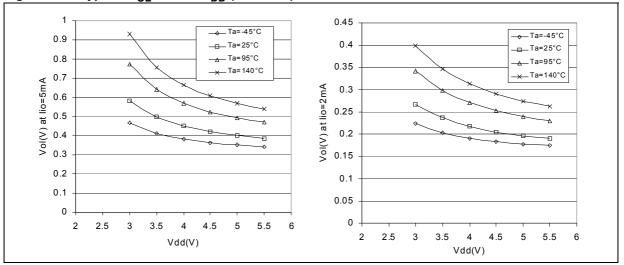

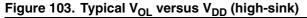

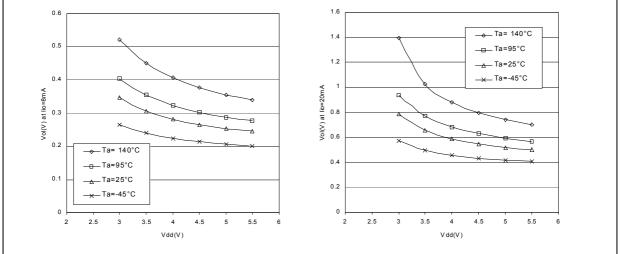

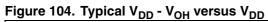

## Figure 102. Typical $V_{OL}$ versus $V_{DD}$ (standard)

Doc ID 17660 Rev 1

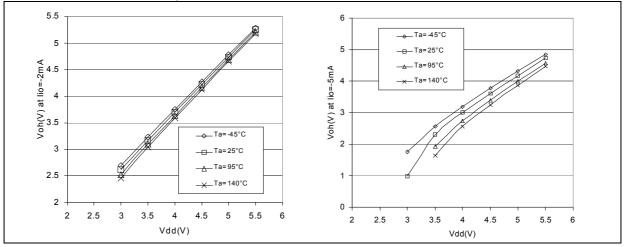

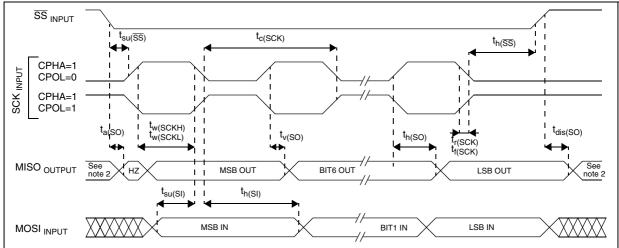

## Figure 108. SPI slave timing diagram with CPHA = $0^{(1)}$

1. Measurement points are done at CMOS levels:  $0.3xV_{DD}$  and  $0.7xV_{DD}$ .

2. When no communication is on-going the data output line of the SPI (MOSI in master mode, MISO in slave mode) has its alternate function capability released. In this case, the pin status depends on the I/O port configuration.

# Figure 109. SPI slave timing diagram with CPHA = $1^{(1)}$

1. Measurement points are done at CMOS levels:  $0.3xV_{DD}$  and  $0.7xV_{DD}$ .

2. When no communication is on-going the data output line of the SPI (MOSI in master mode, MISO in slave mode) has its alternate function capability released. In this case, the pin status depends of the I/O port configuration.

# 20.11.2 I<sup>2</sup>C - inter IC control interface

Subject to general operating conditions for  $V_{\text{DD}},\,f_{\text{CPU}},$  and  $T_{\text{A}}$  unless otherwise specified.

Refer to *Section 20.8: I/O port pin characteristics* for more details on the input/output alternate function characteristics (SDAI and SCLI). The ST7 I2C interface meets the requirements of the standard I2C communication protocol described in the following table.

| Table 153. | I <sup>2</sup> C control | interface | characteristics |

|------------|--------------------------|-----------|-----------------|

|------------|--------------------------|-----------|-----------------|

| Symbol                                     | Parameter                               | Standard mode I <sup>2</sup> C |                    | Fast mode I <sup>2</sup> C <sup>(1)</sup> |                    | 11   |

|--------------------------------------------|-----------------------------------------|--------------------------------|--------------------|-------------------------------------------|--------------------|------|

|                                            | Parameter                               | Min <sup>(2)</sup>             | Max <sup>(2)</sup> | Min <sup>(2)</sup>                        | Max <sup>(2)</sup> | Unit |

| t <sub>w(SCLL)</sub>                       | SCL clock low time                      | 4.7                            |                    | 1.3                                       |                    | μs   |

| t <sub>w(SCLH)</sub>                       | SCL clock high time                     | 4.0                            |                    | 0.6                                       |                    |      |

| t <sub>su(SDA)</sub>                       | SDA setup time                          | 250                            |                    | 100                                       |                    |      |

| t <sub>h(SDA)</sub>                        | SDA data hold time                      | 0 <sup>(3)</sup>               |                    | 0 <sup>(4)</sup>                          | 900 <sup>(3)</sup> |      |

| t <sub>r(SDA)</sub><br>t <sub>r(SCL)</sub> | SDA and SCL rise time                   |                                | 1000               | 20+0.1C <sub>b</sub>                      | 300                | ns   |

| t <sub>f(SDA)</sub><br>t <sub>f(SCL)</sub> | SDA and SCL fall time                   |                                | 300                | 20+0.10b                                  |                    |      |

| t <sub>h(STA)</sub>                        | START condition hold time               | 4.0                            |                    |                                           |                    |      |

| t <sub>su(STA)</sub>                       | Repeated START condition setup time     | 4.7                            |                    | 0.6                                       |                    | μs   |

| t <sub>su(STO)</sub>                       | STOP condition setup time               | 4.0                            |                    |                                           |                    |      |

| t <sub>w(STO:STA)</sub>                    | STOP to START condition time (bus free) | 4.7                            |                    | 1.3                                       |                    |      |

| Cb                                         | Capacitive load for each bus line       |                                | 400                |                                           | 400                | pF   |

1. At 4 MHz f<sub>CPU</sub>, maximum I<sup>2</sup>C speed (400 kHz) is not achievable. In this case, maximum I<sup>2</sup>C speed will be approximately 260 kHz.

2. Data based on standard I<sup>2</sup>C protocol requirement, not tested in production.

3. The maximum hold time of the START condition has only to be met if the interface does not stretch the low period of SCL signal.

4. The device must internally provide a hold time of at least 300ns for the SDA signal in order to bridge the undefined region of the falling edge of SCL.

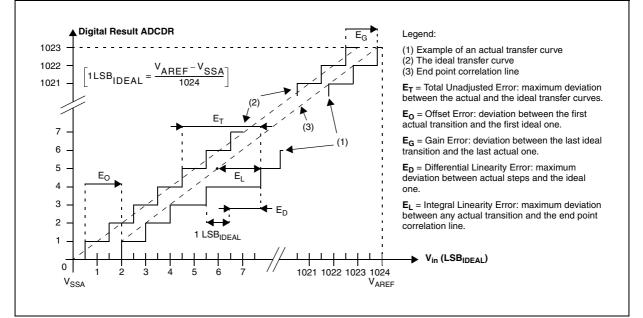

### 20.12.3 **ADC** accuracy

Conditions:  $V_{DD} = 5V^{(1)}$

| Table 101. Abb decutacy |                              |                                          |     |                    |      |

|-------------------------|------------------------------|------------------------------------------|-----|--------------------|------|

| Symbol                  | Parameter <sup>(1)</sup>     | Conditions                               | Тур | Max <sup>(2)</sup> | Unit |

| IE <sub>T</sub> I       | Total unadjusted error       |                                          | 3   | 4                  |      |

| IE <sub>O</sub> I       | Offset error                 |                                          | 2   | 3                  |      |

| IE <sub>G</sub> I       | Gain error                   | CPU in run mode @ f <sub>ADC</sub> 2 MHz | 0.5 | 3                  | LSB  |

| IE <sub>D</sub> I       | Differential linearity error |                                          | 4   | 2                  |      |

| ΙΕ <sub>L</sub> Ι       | Integral linearity error     |                                          | I   | 2                  |      |

## Table 157. ADC accuracy

ADC Accuracy versus Negative Injection Current: Injecting negative current may reduce the accuracy of the conversion being performed on another analog input. The effect of negative injection current on robust pins is specified in *Section 20.12*. Any positive injection current within the limits specified for I<sub>INJ(PIN)</sub> and ΣI<sub>INJ(PIN)</sub> in *Section 20.8* does not affect the ADC accuracy.

- Data based on characterization results, monitored in production to guarantee 99.73% within  $\pm$  max value from -40°C to 125°C ( $\pm$  3 $\sigma$  distribution limits). 2.

## Figure 116. ADC error classification

### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2010 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

Doc ID 17660 Rev 1