# E·XFL

#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Details                            |                                                                                                                     |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Product Status                     | Active                                                                                                              |

| Core Processor                     | ARM® Cortex®-A9                                                                                                     |

| Number of Cores/Bus<br>Width       | 2 Core, 32-Bit                                                                                                      |

| Speed                              | 1.0GHz                                                                                                              |

| Co-Processors/DSP                  | Multimedia; NEON <sup>™</sup> SIMD                                                                                  |

| RAM Controllers                    | LPDDR2, LVDDR3, DDR3                                                                                                |

| Graphics Acceleration              | Yes                                                                                                                 |

| Display & Interface<br>Controllers | Keypad, LCD                                                                                                         |

| Ethernet                           | 10/100/1000Mbps (1)                                                                                                 |

| SATA                               | SATA 3Gbps (1)                                                                                                      |

| USB                                | USB 2.0 + PHY (4)                                                                                                   |

| Voltage - I/O                      | 1.8V, 2.5V, 2.8V, 3.3V                                                                                              |

| Operating Temperature              | -40°C ~ 125°C (TJ)                                                                                                  |

| Security Features                  | ARM TZ, Boot Security, Cryptography, RTIC, Secure Fusebox, Secure JTAG, Secure Memory, Secure RTC, Tamper Detection |

| Package / Case                     | 624-FBGA, FCBGA                                                                                                     |

| Supplier Device Package            | 624-FCBGA (21x21)                                                                                                   |

| Purchase URL                       | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcimx6d4avt10ae                                             |

|                                    |                                                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Introduction

- Graphics rendering for Human Machine Interfaces (HMI)

- High-performance speech processing with large databases

- Audio playback

The i.MX 6Dual/6Quad processors offers numerous advanced features, such as:

- Multilevel memory system—The multilevel memory system of each processor is based on the L1 instruction and data caches, L2 cache, and internal and external memory. The processors support many types of external memory devices, including DDR3, DDR3L, LPDDR2, NOR Flash, PSRAM, cellular RAM, NAND Flash (MLC and SLC), OneNAND<sup>™</sup>, and managed NAND, including eMMC up to rev 4.4/4.41.

- Smart speed technology—The processors have power management throughout the device that enables the rich suite of multimedia features and peripherals to consume minimum power in both active and various low power modes. Smart speed technology enables the designer to deliver a feature-rich product, requiring levels of power far lower than industry expectations.

- Dynamic voltage and frequency scaling—The processors improve the power efficiency of devices by scaling the voltage and frequency to optimize performance.

- Multimedia powerhouse—The multimedia performance of each processor is enhanced by a multilevel cache system, Neon<sup>®</sup> MPE (Media Processor Engine) co-processor, a multi-standard hardware video codec, 2 autonomous and independent image processing units (IPU), and a programmable smart DMA (SDMA) controller.

- Powerful graphics acceleration—Each processor provides three independent, integrated graphics processing units: an OpenGL<sup>®</sup> ES 2.0 3D graphics accelerator with four shaders (up to 200 MTri/s and OpenCL support), 2D graphics accelerator, and dedicated OpenVG<sup>TM</sup> 1.1 accelerator.

- Interface flexibility—Each processor supports connections to a variety of interfaces: LCD controller for up to four displays (including parallel display, HDMI1.4, MIPI display, and LVDS display), dual CMOS sensor interface (parallel or through MIPI), high-speed USB on-the-go with PHY, high-speed USB host with PHY, multiple expansion card ports (high-speed MMC/SDIO host and other), 10/100/1000 Mbps Gigabit Ethernet controller, and a variety of other popular interfaces (such as UART, I<sup>2</sup>C, and I<sup>2</sup>S serial audio, SATA-II, and PCIe-II).

- Automotive environment support—Each processor includes interfaces, such as two CAN ports, an MLB150/50 port, an ESAI audio interface, and an asynchronous sample rate converter for multichannel/multisource audio.

- Advanced security—The processors deliver hardware-enabled security features that enable secure e-commerce, digital rights management (DRM), information encryption, secure boot, and secure software downloads. The security features are discussed in detail in the i.MX 6Dual/6Quad security reference manual (IMX6DQ6SDLSRM).

- Integrated power management—The processors integrate linear regulators and internally generate voltage levels for different domains. This significantly simplifies system power management structure.

- 1-bit or 4-bit transfer mode specifications for SD and SDIO cards up to UHS-I SDR-104 mode (104 MB/s max)

- 1-bit, 4-bit, or 8-bit transfer mode specifications for MMC cards up to 52 MHz in both SDR and DDR modes (104 MB/s max)

- USB:

- One High Speed (HS) USB 2.0 OTG (Up to 480 Mbps), with integrated HS USB PHY

- Three USB 2.0 (480 Mbps) hosts:

- One HS host with integrated High Speed PHY

- Two HS hosts with integrated High Speed Inter-Chip (HS-IC) USB PHY

- Expansion PCI Express port (PCIe) v2.0 one lane

- PCI Express (Gen 2.0) dual mode complex, supporting Root complex operations and Endpoint operations. Uses x1 PHY configuration.

- Miscellaneous IPs and interfaces:

- SSI block capable of supporting audio sample frequencies up to 192 kHz stereo inputs and outputs with I<sup>2</sup>S mode

- ESAI is capable of supporting audio sample frequencies up to 260 kHz in I2S mode with 7.1 multi channel outputs

- Five UARTs, up to 5.0 Mbps each:

- Providing RS232 interface

- Supporting 9-bit RS485 multidrop mode

- One of the five UARTs (UART1) supports 8-wire while the other four support 4-wire. This is due to the SoC IOMUX limitation, because all UART IPs are identical.

- Five eCSPI (Enhanced CSPI)

- Three I2C, supporting 400 kbps

- Gigabit Ethernet Controller (IEEE1588 compliant),  $10/100/1000^1$  Mbps

- Four Pulse Width Modulators (PWM)

- System JTAG Controller (SJC)

- GPIO with interrupt capabilities

- 8x8 Key Pad Port (KPP)

- Sony Philips Digital Interconnect Format (SPDIF), Rx and Tx

- Two Controller Area Network (FlexCAN), 1 Mbps each

- Two Watchdog timers (WDOG)

- Audio MUX (AUDMUX)

- MLB (MediaLB) provides interface to MOST Networks (150 Mbps) with the option of DTCP cipher accelerator

1. The theoretical maximum performance of 1 Gbps ENET is limited to 470 Mbps (total for Tx and Rx) due to internal bus throughput limitations. The actual measured performance in optimized environment is up to 400 Mbps. For details, see the ERR004512 erratum in the i.MX 6Dual/6Quad errata document (IMX6DQCE).

# 3 Modules List

The i.MX 6Dual/6Quad processors contain a variety of digital and analog modules. Table 2 describes these modules in alphabetical order.

| Block<br>Mnemonic   | Block Name                                                                          | Subsystem                               | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------|-------------------------------------------------------------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 512 x 8 Fuse<br>Box | Electrical Fuse Array                                                               | Security                                | Electrical Fuse Array. Enables to setup Boot Modes, Security Levels,<br>Security Keys, and many other system parameters.<br>The i.MX 6Dual/6Quad processors consist of 512x8-bit fuse box<br>accessible through OCOTP_CTRL interface.                                                                                                                                                                                                                                                                                                                                                |

| APBH-DMA            | NAND Flash and<br>BCH ECC DMA<br>Controller                                         | System<br>Control<br>Peripherals        | DMA controller used for GPMI2 operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ARM                 | ARM Platform                                                                        | ARM                                     | The ARM Cortex-A9 platform consists of 4x (four) Cortex-A9 cores<br>version r2p10 and associated sub-blocks, including Level 2 Cache<br>Controller, SCU (Snoop Control Unit), GIC (General Interrupt Controller),<br>private timers, Watchdog, and CoreSight debug modules.                                                                                                                                                                                                                                                                                                          |

| ASRC                | Asynchronous<br>Sample Rate<br>Converter                                            | Multimedia<br>Peripherals               | The Asynchronous Sample Rate Converter (ASRC) converts the sampling rate of a signal associated to an input clock into a signal associated to a different output clock. The ASRC supports concurrent sample rate conversion of up to 10 channels of about -120dB THD+N. The sample rate conversion of each channel is associated to a pair of incoming and outgoing sampling rates. The ASRC supports up to three sampling rate pairs.                                                                                                                                               |

| AUDMUX              | Digital Audio Mux                                                                   | Multimedia<br>Peripherals               | The AUDMUX is a programmable interconnect for voice, audio, and<br>synchronous data routing between host serial interfaces (for example,<br>SSI1, SSI2, and SSI3) and peripheral serial interfaces (audio and voice<br>codecs). The AUDMUX has seven ports with identical functionality and<br>programming models. A desired connectivity is achieved by configuring<br>two or more AUDMUX ports.                                                                                                                                                                                    |

| BCH40               | Binary-BCH ECC<br>Processor                                                         | System<br>Control<br>Peripherals        | The BCH40 module provides up to 40-bit ECC error correction for NAND Flash controller (GPMI).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CAAM                | Cryptographic<br>Accelerator and<br>Assurance Module                                | Security                                | CAAM is a cryptographic accelerator and assurance module. CAAM<br>implements several encryption and hashing functions, a run-time integrity<br>checker, and a Pseudo Random Number Generator (PRNG). The pseudo<br>random number generator is certified by Cryptographic Algorithm<br>Validation Program (CAVP) of National Institute of Standards and<br>Technology (NIST). Its DRBG validation number is 94 and its SHS<br>validation number is 1455.<br>CAAM also implements a Secure Memory mechanism. In i.MX<br>6Dual/6Quad processors, the security memory provided is 16 KB. |

| CCM<br>GPC<br>SRC   | Clock Control<br>Module, General<br>Power Controller,<br>System Reset<br>Controller | Clocks,<br>Resets, and<br>Power Control | These modules are responsible for clock and reset distribution in the system, and also for the system power management.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Table 2. i.MX 6Dual/6Quad Mod | dules List |

|-------------------------------|------------|

|-------------------------------|------------|

| Table 2. i.MX 6Dual/6Quad | Modules List | (continued) |

|---------------------------|--------------|-------------|

|---------------------------|--------------|-------------|

| Block<br>Mnemonic                | Block Name                    | Subsystem                                   | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------------------|-------------------------------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LDB                              | LVDS Display Bridge           | Connectivity<br>Peripherals                 | <ul> <li>LVDS Display Bridge is used to connect the IPU (Image Processing Unit) to External LVDS Display Interface. LDB supports two channels; each channel has following signals:</li> <li>One clock pair</li> <li>Four data pairs</li> <li>Each signal pair contains LVDS special differential pad (PadP, PadM).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                  |

| MLB150                           | MediaLB                       | Connectivity /<br>Multimedia<br>Peripherals | The MLB interface module provides a link to a MOST <sup>®</sup> data network, using the standardized MediaLB protocol (up to 150 Mbps). The module is backward compatible to MLB-50.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| MMDC                             | Multi-Mode DDR<br>Controller  | Connectivity<br>Peripherals                 | <ul> <li>DDR Controller has the following features:</li> <li>Supports 16/32/64-bit DDR3 / DDR3L or LPDDR2</li> <li>Supports both dual x32 for LPDDR2 and x64 DDR3 / LPDDR2 configurations (including 2x32 interleaved mode)</li> <li>Supports up to 4 GByte DDR memory space</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| OCOTP_CTRL                       | OTP Controller                | Security                                    | The On-Chip OTP controller (OCOTP_CTRL) provides an interface for reading, programming, and/or overriding identification and control information stored in on-chip fuse elements. The module supports electrically-programmable poly fuses (eFUSEs). The OCOTP_CTRL also provides a set of volatile software-accessible signals that can be used for software control of hardware elements, not requiring non-volatility. The OCOTP_CTRL provides the primary user-visible mechanism for interfacing with on-chip fuse elements. Among the uses for the fuses are unique chip identifiers, mask revision numbers, cryptographic keys, JTAG secure mode, boot characteristics, and various control signals, requiring permanent non-volatility. |

| OCRAM                            | On-Chip Memory<br>Controller  | Data Path                                   | The On-Chip Memory controller (OCRAM) module is designed as an interface between system's AXI bus and internal (on-chip) SRAM memory module.<br>In i.MX 6Dual/6Quad processors, the OCRAM is used for controlling the 256 KB multimedia RAM through a 64-bit AXI bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| OSC 32 kHz                       | OSC 32 kHz                    | Clocking                                    | Generates 32.768 kHz clock from an external crystal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PCle                             | PCI Express 2.0               | Connectivity<br>Peripherals                 | The PCIe IP provides PCI Express Gen 2.0 functionality.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PMU                              | Power-Management<br>Functions | Data Path                                   | Integrated power management unit. Used to provide power to various SoC domains.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| PWM-1<br>PWM-2<br>PWM-3<br>PWM-4 | Pulse Width<br>Modulation     | Connectivity<br>Peripherals                 | The pulse-width modulator (PWM) has a 16-bit counter and is optimized to generate sound from stored sample audio images and it can also generate tones. It uses 16-bit resolution and a 4x16 data FIFO to generate sound.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RAM<br>16 KB                     | Secure/non-secure<br>RAM      | Secured<br>Internal<br>Memory               | Secure/non-secure Internal RAM, interfaced through the CAAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| RAM<br>256 KB                    | Internal RAM                  | Internal<br>Memory                          | Internal RAM, which is accessed through OCRAM memory controllers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Table 2. i.MX 6Dual/6Quad Modules List (continued) |

|----------------------------------------------------|

|----------------------------------------------------|

| Block<br>Mnemonic                              | Block Name                                   | Subsystem                        | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------------------------------------|----------------------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SSI-1<br>SSI-2<br>SSI-3                        | I2S/SSI/AC97<br>Interface                    | Connectivity<br>Peripherals      | The SSI is a full-duplex synchronous interface, which is used on the processor to provide connectivity with off-chip audio peripherals. The SSI supports a wide variety of protocols (SSI normal, SSI network, I2S, and AC-97), bit depths (up to 24 bits per word), and clock / frame sync options. The SSI has two pairs of 8x24 FIFOs and hardware support for an external DMA controller to minimize its impact on system performance. The second pair of FIFOs provides hardware interleaving of a second audio stream that reduces CPU overhead in use cases where two time slots are being used simultaneously. |

| TEMPMON                                        | Temperature Monitor                          | System<br>Control<br>Peripherals | The temperature monitor/sensor IP module for detecting high temperature conditions. The temperature read out does not reflect case or ambient temperature. It reflects the temperature in proximity of the sensor location on the die. Temperature distribution may not be uniformly distributed; therefore, the read out value may not be the reflection of the temperature value for the entire die.                                                                                                                                                                                                                 |

| TZASC                                          | Trust-Zone Address<br>Space Controller       | Security                         | The TZASC (TZC-380 by ARM) provides security address region control functions required for intended application. It is used on the path to the DRAM controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| UART-1<br>UART-2<br>UART-3<br>UART-4<br>UART-5 | UART Interface                               | Connectivity<br>Peripherals      | <ul> <li>Each of the UARTv2 modules support the following serial data transmit/receive protocols and configurations:</li> <li>7- or 8-bit data words, 1 or 2 stop bits, programmable parity (even, odd or none)</li> <li>Programmable baud rates up to 5 MHz</li> <li>32-byte FIFO on Tx and 32 half-word FIFO on Rx supporting auto-baud</li> <li>IrDA 1.0 support (up to SIR speed of 115200 bps)</li> <li>Option to operate as 8-pins full UART, DCE, or DTE</li> </ul>                                                                                                                                             |

| USBOH3A                                        | USB 2.0 High Speed<br>OTG and 3x HS<br>Hosts | Connectivity<br>Peripherals      | <ul> <li>USBOH3 contains:</li> <li>One high-speed OTG module with integrated HS USB PHY</li> <li>One high-speed Host module with integrated HS USB PHY</li> <li>Two identical high-speed Host modules connected to HSIC USB ports.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                          |

### **Modules List**

| Block<br>Mnemonic             | Block Name                                                                             | Subsystem                   | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------------|----------------------------------------------------------------------------------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| uSDHC-1<br>uSDHC-2<br>uSDHC-4 | SD/MMC and SDXC<br>Enhanced<br>Multi-Media Card /<br>Secure Digital Host<br>Controller | Connectivity<br>Peripherals | <ul> <li>i.MX 6Dual/6Quad specific SoC characteristics:</li> <li>All four MMC/SD/SDIO controller IPs are identical and are based on the uSDHC IP. They are:</li> <li>Conforms to the SD Host Controller Standard Specification version 3.0</li> <li>Fully compliant with MMC command/response sets and Physical Layer as defined in the Multimedia Card System Specification, v4.2/4.3/4.4/4.41 including high-capacity (size &gt; 2 GB) cards HC MMC. Hardware reset as specified for eMMC cards is supported at ports #3 and #4 only.</li> <li>Fully compliant with SD command/response sets and Physical Layer as defined in the SD Memory Card Specifications, v3.0 including high-capacity SDHC cards up to 32 GB and SDXC cards up to 2TB.</li> <li>Fully compliant with SDIO command/response sets and interrupt/read-wait mode as defined in the SDIO Card Specification, Part E1, v1.10</li> <li>Fully compliant with SD Card Specification, Part A2, SD Host Controller Standard Specification, v2.00</li> <li>All four ports support:</li> <li>1-bit or 4-bit transfer mode specifications for SD and SDIO cards up to UHS-I SDR104 mode (104 MB/s max)</li> <li>1-bit, 4-bit, or 8-bit transfer mode specifications for MMC cards up to 52 MHz in both SDR and DDR modes (104 MB/s max)</li> <li>However, the SoC-level integration and I/O muxing logic restrict the functionality to the following:</li> <li>Instances #1 and #2 are primarily intended to serve as external slots or interfaces to on-board SDIO devices. These ports are equipped with "Card Detection" and "Write Protection" pads and do support hardware reset.</li> <li>Instances #3 and #4 are primarily intended to serve interfaces to embedded MMC memory or interfaces to on-board SDIO devices. These ports do not have "Card detection" and "Write Protection" pads and do support hardware reset.</li> <li>All ports can work with 1.8 V and 3.3 V cards. There are two completely independent I/O power domains for Ports #1 and #2 in four bit configuration (SD interface). Port #3 is placed in his own independent power domain</li></ul> |

| VDOA                          | VDOA                                                                                   | Multimedia<br>Peripherals   | The Video Data Order Adapter (VDOA) is used to re-order video data from the "tiled" order used by the VPU to the conventional raster-scan order needed by the IPU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| VPU                           | Video Processing<br>Unit                                                               | Multimedia<br>Peripherals   | A high-performing video processing unit (VPU), which covers many<br>SD-level and HD-level video decoders and SD-level encoders as a<br>multi-standard video codec engine as well as several important video<br>processing, such as rotation and mirroring.<br>See the i.MX 6Dual/6Quad reference manual (IMX6DQRM) for complete<br>list of VPU's decoding/encoding capabilities.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| WDOG-1                        | Watchdog                                                                               | Timer<br>Peripherals        | The Watchdog Timer supports two comparison points during each counting period. Each of the comparison points is configurable to evoke an interrupt to the ARM core, and a second point evokes an external event on the WDOG line.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

# 4.1.2 Thermal Resistance

### NOTE

Per JEDEC JESD51-2, the intent of thermal resistance measurements is solely for a thermal performance comparison of one package to another in a standardized environment. This methodology is not meant to and will not predict the performance of a package in an application-specific environment.

### 4.1.2.1 FCPBGA Package Thermal Resistance

Table 5 provides the FCPBGA package thermal resistance data for the *lidded* package type.

| Thermal Parameter                     | Test Conditions                                           | Symbol              | Value | Unit |

|---------------------------------------|-----------------------------------------------------------|---------------------|-------|------|

| Junction to Ambient <sup>1</sup>      | Single-layer board (1s); natural convection <sup>2</sup>  | R <sub>θJA</sub>    | 24    | °C/W |

|                                       | Four-layer board (2s2p); natural convection <sup>2</sup>  | R <sub>θJA</sub>    | 15    | °C/W |

| Junction to Ambient <sup>1</sup>      | Single-layer board (1s); air flow 200 ft/min <sup>3</sup> | R <sub>0JMA</sub>   | 17    | °C/W |

|                                       | Four-layer board (2s2p); air flow 200 ft/min <sup>4</sup> | R <sub>0JMA</sub>   | 12    | °C/W |

| Junction to Board <sup>1,4</sup>      | _                                                         | R <sub>θJB</sub>    | 5     | °C/W |

| Junction to Case (top) <sup>1,5</sup> | _                                                         | R <sub>0JCtop</sub> | 1     | °C/W |

Table 5. FCPBGA Package Thermal Resistance Data (Lidded)

<sup>1</sup> Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

<sup>2</sup> Per JEDEC JESD51-3 with the single layer board horizontal. Thermal test board meets JEDEC specification for the specified package.

- <sup>3</sup> Per JEDEC JESD51-6 with the board horizontal.

- <sup>4</sup> Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- <sup>5</sup> Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1). The cold plate temperature is used for the case temperature. Reported value includes the thermal resistance of the interface layer.

| Table 8. Maximum Supply | Currents | (continued) |

|-------------------------|----------|-------------|

|-------------------------|----------|-------------|

| Dower Supply | Conditions | Maximum C                                                                                                                                          | Unit     |      |  |  |

|--------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|--|--|

| Power Supply | Conditions | Power Virus                                                                                                                                        | CoreMark | Unit |  |  |

| NVCC_LVDS2P5 | _          | NVCC_LVDS2P5 is connected to<br>VDD_HIGH_CAP at the board<br>level. VDD_HIGH_CAP is capable<br>of handing the current required by<br>NVCC_LVDS2P5. |          |      |  |  |

| MISC         |            |                                                                                                                                                    |          |      |  |  |

| DRAM_VREF    | _          | 1                                                                                                                                                  |          | mA   |  |  |

<sup>1</sup> The actual maximum current drawn from VDD\_HIGH\_IN will be as shown plus any additional current drawn from the VDD\_HIGH\_CAP outputs, depending upon actual application configuration (for example, NVCC\_LVDS\_2P5, NVCC\_MIPI, or HDMI, PCIe, and SATA VPH supplies).

- <sup>2</sup> Under normal operating conditions, the maximum current on VDD\_SNVS\_IN is shown Table 8. The maximum VDD\_SNVS\_IN current may be higher depending on specific operating configurations, such as BOOT\_MODE[1:0] not equal to 00, or use of the Tamper feature. During initial power on, VDD\_SNVS\_IN can draw up to 1 mA if the supply is capable of sourcing that current. If less than 1 mA is available, the VDD\_SNVS\_CAP charge time will increase.

- <sup>3</sup> This is the maximum current per active USB physical interface.

- <sup>4</sup> The DRAM power consumption is dependent on several factors such as external signal termination. DRAM power calculators are typically available from memory vendors which take into account factors such as signal termination. See the *i.MX 6Dual/6Quad Power Consumption Measurement Application Note* (AN4509) for examples of DRAM power consumption during specific use case scenarios.

- <sup>5</sup> General equation for estimated, maximum power consumption of an IO power supply: Imax = N x C x V x (0.5 x F)

- Where:

N-Number of IO pins supplied by the power line

C-Equivalent external capacitive load

V—IO voltage

(0.5 xF)—Data change rate. Up to 0.5 of the clock rate (F)

In this equation, Imax is in Amps, C in Farads, V in Volts, and F in Hertz.

# 4.1.6 Low Power Mode Supply Currents

Table 9 shows the current core consumption (not including I/O) of the i.MX 6Dual/6Quad processors in selected low power modes.

| Mode | Test Conditions                                                                        | Supply              | Typical <sup>1</sup> | Unit |

|------|----------------------------------------------------------------------------------------|---------------------|----------------------|------|

| WAIT | • ARM, SoC, and PU LDOs are set to 1.225 V                                             | VDD_ARM_IN (1.4 V)  | 6                    | mA   |

|      | HIGH LDO set to 2.5 V     Clocks are gated                                             | VDD_SOC_IN (1.4 V)  | 23                   | mA   |

|      | <ul> <li>DDR is in self refresh</li> <li>PLLs are active in bypass (24 MHz)</li> </ul> | VDD_HIGH_IN (3.0 V) | 3.7                  | mA   |

|      | Supply voltages remain ON                                                              | Total               | 52                   | mW   |

| Table 9. | Stop Mode | <b>Current and</b> | Power | Consumption |

|----------|-----------|--------------------|-------|-------------|

|----------|-----------|--------------------|-------|-------------|

• When the PCIE interface is not used, the PCIE\_VP, PCIE\_VPH, and PCIE\_VPTX supplies should be grounded. The input and output supplies for rest of the ports (PCIE\_REXT, PCIE\_RX\_N, PCIE\_RX\_P, PCIE\_TX\_N, and PCIE\_TX\_P) can remain unconnected. It is recommended not to turn the PCIE\_VPH supply OFF while the PCIE\_VP supply is ON, as it may lead to excessive power consumption. If boundary scan test is used, PCIE\_VP, PCIE\_VPH, and PCIE\_VPTX must remain powered.

# 4.3 Integrated LDO Voltage Regulator Parameters

Various internal supplies can be powered ON from internal LDO voltage regulators. All the supply pins named \*\_CAP must be connected to external capacitors. The onboard LDOs are intended for internal use only and should not be used to power any external circuitry. See the i.MX 6Dual/6Quad reference manual (IMX6DQRM) for details on the power tree scheme recommended operation.

### NOTE

The \*\_CAP signals should not be powered externally. These signals are intended for internal LDO or LDO bypass operation only.

# 4.3.1 Digital Regulators (LDO\_ARM, LDO\_PU, LDO\_SOC)

There are three digital LDO regulators ("Digital", because of the logic loads that they drive, not because of their construction). The advantages of the regulators are to reduce the input supply variation because of their input supply ripple rejection and their on die trimming. This translates into more voltage for the die producing higher operating frequencies. These regulators have three basic modes.

- Bypass. The regulation FET is switched fully on passing the external voltage, DCDC\_LOW, to the load unaltered. The analog part of the regulator is powered down in this state, removing any loss other than the IR drop through the power grid and FET.

- Power Gate. The regulation FET is switched fully off limiting the current draw from the supply. The analog part of the regulator is powered down here limiting the power consumption.

- Analog regulation mode. The regulation FET is controlled such that the output voltage of the regulator equals the programmed target voltage. The target voltage is fully programmable in 25 mV steps.

Optionally LDO\_SOC/VDD\_SOC\_CAP can be used to power the HDMI, PCIe, and SATA PHY's through external connections.

For additional information, see the i.MX 6Dual/6Quad reference manual (IMX6DQRM).

# 4.3.2 Regulators for Analog Modules

# 4.3.2.1 LDO\_1P1 / NVCC\_PLL\_OUT

The LDO\_1P1 regulator implements a programmable linear-regulator function from VDD\_HIGH\_IN (see Table 6 for minimum and maximum input requirements). Typical Programming Operating Range is 1.0 V to 1.2 V with the nominal default setting as 1.1 V. The LDO\_1P1 supplies the 24 MHz oscillator, PLLs, and USB PHY. A programmable brown-out detector is included in the regulator that can be used by the

# 4.9 System Modules Timing

This section contains the timing and electrical parameters for the modules in each i.MX 6Dual/6Quad processor.

# 4.9.1 Reset Timing Parameters

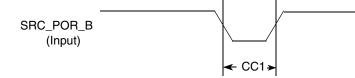

Figure 10 shows the reset timing and Table 38 lists the timing parameters.

Figure 10. Reset Timing Diagram

Table 38. Reset Timing Parameters

| ID  | Parameter                                      | Min | Мах | Unit                     |

|-----|------------------------------------------------|-----|-----|--------------------------|

| CC1 | Duration of SRC_POR_B to be qualified as valid | 1   |     | XTALOSC_RTC_ XTALI cycle |

# 4.9.2 WDOG Reset Timing Parameters

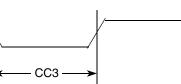

Figure 11 shows the WDOG reset timing and Table 39 lists the timing parameters.

WDOG1\_B (Output)

Figure 11. WDOG1\_B Timing Diagram

### Table 39. WDOG1\_B Timing Parameters

| ID  | Parameter                     | Min | Мах | Unit                     |

|-----|-------------------------------|-----|-----|--------------------------|

| CC3 | Duration of WDOG1_B Assertion | 1   | _   | XTALOSC_RTC_ XTALI cycle |

### NOTE

XTALOSC\_RTC\_XTALI is approximately 32 kHz. XTALOSC\_RTC\_XTALI cycle is one period or approximately 30 µs.

### NOTE

WDOG1\_B output signals (for each one of the Watchdog modules) do not have dedicated pins, but are muxed out through the IOMUX. See the IOMUX manual for detailed information.

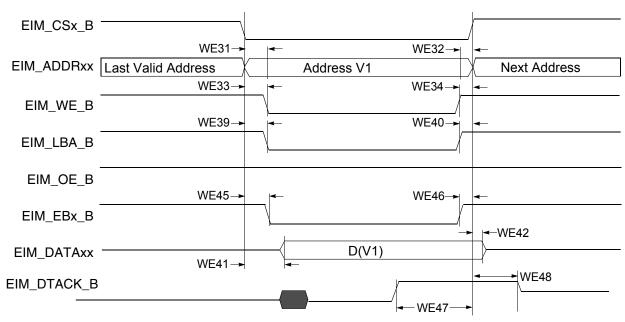

Figure 23. DTACK Mode Write Access (DAP=0)

| Ref No.                 | Parameter                                               | Determination by Synchronous<br>measured parameters | Min                             | Мах                                    | Unit |

|-------------------------|---------------------------------------------------------|-----------------------------------------------------|---------------------------------|----------------------------------------|------|

| WE31                    | EIM_CSx_B valid to Address Valid                        | WE4-WE6-CSA×t                                       | -3.5-CSA×t                      | 3.5-CSA×t                              | ns   |

| WE32                    | Address Invalid to EIM_CSx_B<br>Invalid                 | WE7-WE5-CSN×t                                       | -3.5-CSN×t                      | 3.5-CSN×t                              | ns   |

| WE32A<br>(muxed<br>A/D) | EIM_CSx_B valid to Address<br>Invalid                   | t+WE4-WE7+<br>(ADVN+ADVA+1-CSA)×t                   | t - 3.5+(ADVN+A<br>DVA+1-CSA)×t | t + 3.5+(ADVN+ADVA+<br>1-CSA)×t        | ns   |

| WE33                    | EIM_CSx_B Valid to EIM_WE_B<br>Valid                    | WE8-WE6+(WEA-WCSA)×t                                | -3.5+(WEA-WCS<br>A)×t           | 3.5+(WEA-WCSA)×t                       | ns   |

| WE34                    | EIM_WE_B Invalid to EIM_CSx_B<br>Invalid                | WE7-WE9+(WEN-WCSN)×t                                | -3.5+(WEN-WCS<br>N)×t           | 3.5+(WEN-WCSN)×t                       | ns   |

| WE35                    | EIM_CSx_B Valid to EIM_OE_B<br>Valid                    | WE10- WE6+(OEA-RCSA)×t                              | -3.5+(OEA-RCS<br>A)×t           | 3.5+(OEA-RCSA)×t                       | ns   |

| WE35A<br>(muxed<br>A/D) | EIM_CSx_B Valid to EIM_OE_B<br>Valid                    | WE10-WE6+(OEA+RADVN+R<br>ADVA+ADH+1-RCSA)×t         |                                 | 3.5+(OEA+RADVN+RA<br>DVA+ADH+1-RCSA)×t | ns   |

| WE36                    | EIM_OE_B Invalid to EIM_CSx_B<br>Invalid                | WE7-WE11+(OEN-RCSN)×t                               | -3.5+(OEN-RCS<br>N)×t           | 3.5+(OEN-RCSN)×t                       | ns   |

| WE37                    | EIM_CSx_B Valid to EIM_EBx_B<br>Valid (Read access)     | WE12-WE6+(RBEA-RCSA)×t                              | -3.5+(RBEA- RC<br>SA)×t         | 3.5+(RBEA - RCSA)×t                    | ns   |

| WE38                    | EIM_EBx_B Invalid to<br>EIM_CSx_B Invalid (Read access) | WE7-WE13+(RBEN-RCSN)×t                              | -3.5+<br>(RBEN-RCSN)×t          | 3.5+(RBEN-RCSN)×t                      | ns   |

| WE39                    | EIM_CSx_B Valid to EIM_LBA_B<br>Valid                   | WE14-WE6+(ADVA-CSA)×t                               | -3.5+<br>(ADVA-CSA)×t           | 3.5+(ADVA-CSA)×t                       | ns   |

|  | Table 42. EIM | Asynchronous | <b>Timing Parameters</b> | <b>Relative to</b> | Chip Select <sup>1, 2</sup> |

|--|---------------|--------------|--------------------------|--------------------|-----------------------------|

|--|---------------|--------------|--------------------------|--------------------|-----------------------------|

Figure 28. Read Data Latch Cycle Timing Diagram (EDO Mode)

| ID   | Parameter                | Symbol           |                                            | Timing<br>T = GPMI Clock Cycle |    |

|------|--------------------------|------------------|--------------------------------------------|--------------------------------|----|

|      |                          |                  | Min                                        | Мах                            |    |

| NF1  | NAND_CLE setup time      | tCLS             | $(AS + DS) \times T$ ·                     | - 0.12 [see <sup>2,3</sup> ]   | ns |

| NF2  | NAND_CLE hold time       | tCLH             | DH $	imes$ T - 0.72 [see <sup>2</sup> ]    |                                | ns |

| NF3  | NAND_CEx_B setup time    | tCS              | (AS + DS + 1)                              | ) × T [see <sup>3,2</sup> ]    | ns |

| NF4  | NAND_CEx_B hold time     | tCH              | (DH+1) × T - 1 [see <sup>2</sup> ]         |                                | ns |

| NF5  | NAND_WE_B pulse width    | tWP              | $DS 	imes T$ [see $^2$ ]                   |                                | ns |

| NF6  | NAND_ALE setup time      | tALS             | (AS + DS) × T - 0.49 [see <sup>3,2</sup> ] |                                | ns |

| NF7  | NAND_ALE hold time       | tALH             | (DH × T - 0.42 [see <sup>2</sup> ]         |                                | ns |

| NF8  | Data setup time          | tDS              | DS × T - 0.                                | 26 [see <sup>2</sup> ]         | ns |

| NF9  | Data hold time           | tDH              | DH × T - 1.                                | .37 [see <sup>2</sup> ]        | ns |

| NF10 | Write cycle time         | tWC              | (DS + DH)                                  | × T [see <sup>2</sup> ]        | ns |

| NF11 | NAND_WE_B hold time      | tWH              | DH 	imes T                                 | [see <sup>2</sup> ]            | ns |

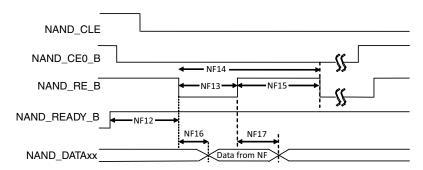

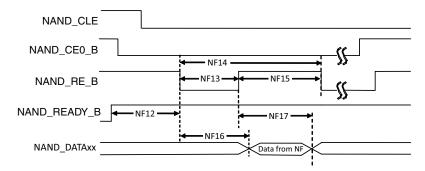

| NF12 | Ready to NAND_RE_B low   | tRR <sup>4</sup> | (AS + 2) × T [see <sup>3,2</sup> ] —       |                                | ns |

| NF13 | NAND_RE_B pulse width    | tRP              | $DS 	imes T$ [see $^2$ ]                   |                                | ns |

| NF14 | READ cycle time          | tRC              | (DS + DH) $	imes$ T [see <sup>2</sup> ]    |                                | ns |

| NF15 | NAND_RE_B high hold time | tREH             | DH × T                                     | [see <sup>2</sup> ]            | ns |

| Table 44. As | synchronous | Mode | Timing | Parameters <sup>1</sup> | l |

|--------------|-------------|------|--------|-------------------------|---|

|--------------|-------------|------|--------|-------------------------|---|

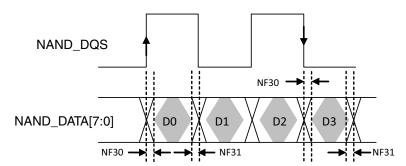

Figure 32. NAND\_DQS/NAND\_DQ Read Valid Window

| ID   | Parameter                                      | Symbol | Timing<br>T = GPMI Clock Cycle            |                          | Unit |  |

|------|------------------------------------------------|--------|-------------------------------------------|--------------------------|------|--|

|      |                                                |        | Min                                       | Max                      |      |  |

| NF18 | NAND_CEx_B access time                         | tCE    | CE_DELAY × T -                            | 0.79 [see <sup>2</sup> ] | ns   |  |

| NF19 | NAND_CEx_B hold time                           | tCH    | 0.5 × tCK - 0.6                           | 63 [see <sup>2</sup> ]   | ns   |  |

| NF20 | Command/address NAND_DATAxx setup time         | tCAS   | $0.5 	imes tCK \cdot$                     | 0.05                     | ns   |  |

| NF21 | Command/address NAND_DATAxx hold time          | tCAH   | 0.5 × tCK - 1.23                          |                          | ns   |  |

| NF22 | clock period                                   | tCK    | —                                         |                          | ns   |  |

| NF23 | preamble delay                                 | tPRE   | PRE_DELAY × T - 0.29 [see <sup>2</sup> ]  |                          | ns   |  |

| NF24 | postamble delay                                | tPOST  | POST_DELAY × T - 0.78 [see <sup>2</sup> ] |                          | ns   |  |

| NF25 | NAND_CLE and NAND_ALE setup time               | tCALS  | 0.5 × tCK - 0.86                          |                          | ns   |  |

| NF26 | NAND_CLE and NAND_ALE hold time                | tCALH  | 0.5 × tCK - 0.37                          |                          | ns   |  |

| NF27 | NAND_CLK to first NAND_DQS latching transition | tDQSS  | T - 0.41 [see <sup>2</sup> ]              |                          | ns   |  |

| NF28 | Data write setup                               | tDS    | 0.25 × tCK - 0.35                         |                          | —    |  |

| NF29 | Data write hold                                | tDH    | 0.25 × tCK - 0.85                         |                          | —    |  |

| NF30 | NAND_DQS/NAND_DQ read setup skew               | tDQSQ  | — 2.06                                    |                          | —    |  |

| NF31 | NAND_DQS/NAND_DQ read hold skew                | tQHS   | _                                         | 1.95                     | —    |  |

Table 45. Source Synchronous Mode Timing Parameters<sup>1</sup>

<sup>1</sup> The GPMI source synchronous mode output timing can be controlled by the module's internal registers GPMI\_TIMING2\_CE\_DELAY, GPMI\_TIMING\_PREAMBLE\_DELAY, GPMI\_TIMING2\_POST\_DELAY. This AC timing depends on these registers settings. In the table, CE\_DELAY/PRE\_DELAY/POST\_DELAY represents each of these settings.

<sup>2</sup> T = tCK (GPMI clock period) -0.075ns (half of maximum p-p jitter).

Figure 32 shows the timing diagram of NAND\_DQS/NAND\_DATAxx read valid window. For Source Synchronous mode, the typical value of tDQSQ is 0.85 ns (max) and 1 ns (max) for tQHS at 200MB/s. GPMI will sample NAND\_DATA[7:0] at both rising and falling edge of a delayed NAND\_DQS signal, which can be provided by an internal DPLL. The delay value can be controlled by GPMI register GPMI\_READ\_DDR\_DLL\_CTRL.SLV\_DLY\_TARGET (see the GPMI chapter of the i.MX 6Dual/6Quad reference manual (IMX6DQRM)). Generally, the typical delay value of this register is equal to 0x7 which means 1/4 clock cycle delay expected. However, if the board delay is large enough and cannot be ignored, the delay value should be made larger to compensate the board delay.

# 4.11.3 Samsung Toggle Mode AC Timing

### 4.11.3.1 Command and Address Timing

Samsung Toggle mode command and address timing is the same as ONFI 1.0 compatible Async mode AC timing. See Section 4.11.1, "Asynchronous Mode AC Timing (ONFI 1.0 Compatible)" for details.

### 4.11.3.2 Read and Write Timing

| dev_clk    |             |

|------------|-------------|

| NAND_CEx_F | 3 0         |

| NAND_CLE   | 0           |

| NAND_ALE   | 0           |

| NAND_WE_B  | . 1         |

| NAND_RE_B  | 1 NF23 NF24 |

| NAND_DQS   |             |

| NAND_DATA[ |             |

Figure 33. Samsung Toggle Mode Data Write Timing

# 4.12.4 Ultra High Speed SD/SDIO/MMC Host Interface (uSDHC) AC Timing

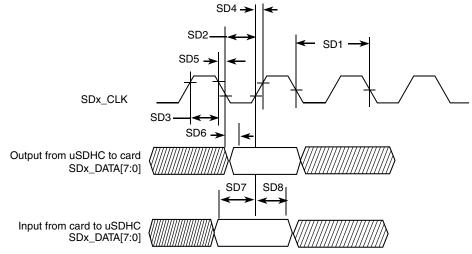

This section describes the electrical information of the uSDHC, which includes SD/eMMC4.3 (Single Data Rate) timing and eMMC4.4/4.1 (Dual Date Rate) timing.

# 4.12.4.1 SD/eMMC4.3 (Single Data Rate) AC Timing

Figure 39 depicts the timing of SD/eMMC4.3, and Table 50 lists the SD/eMMC4.3 timing characteristics.

Figure 39. SD/eMMC4.3 Timing

| ID  | Parameter                                                        | Symbols                      | Min  | Max   | Unit |  |  |

|-----|------------------------------------------------------------------|------------------------------|------|-------|------|--|--|

|     | Card Input Cloc                                                  | ĸ                            |      |       |      |  |  |

| SD1 | Clock Frequency (Low Speed)                                      | f <sub>PP</sub> <sup>1</sup> | 0    | 400   | kHz  |  |  |

|     | Clock Frequency (SD/SDIO Full Speed/High Speed)                  | f <sub>PP</sub> <sup>2</sup> | 0    | 25/50 | MHz  |  |  |

|     | Clock Frequency (MMC Full Speed/High Speed)                      | f <sub>PP</sub> <sup>3</sup> | 0    | 20/52 | MHz  |  |  |

|     | Clock Frequency (Identification Mode)                            | f <sub>OD</sub>              | 100  | 400   | kHz  |  |  |

| SD2 | Clock Low Time                                                   | t <sub>WL</sub>              | 7    | —     | ns   |  |  |

| SD3 | Clock High Time                                                  | t <sub>WH</sub>              | 7    | —     | ns   |  |  |

| SD4 | Clock Rise Time                                                  | t <sub>TLH</sub>             | —    | 3     | ns   |  |  |

| SD5 | Clock Fall Time                                                  | t <sub>THL</sub>             | —    | 3     | ns   |  |  |

|     | eSDHC Output/Card Inputs SD_CMD, SD_DATAx (Reference to SDx_CLK) |                              |      |       |      |  |  |

| SD6 | eSDHC Output Delay                                               | t <sub>OD</sub>              | -6.6 | 3.6   | ns   |  |  |

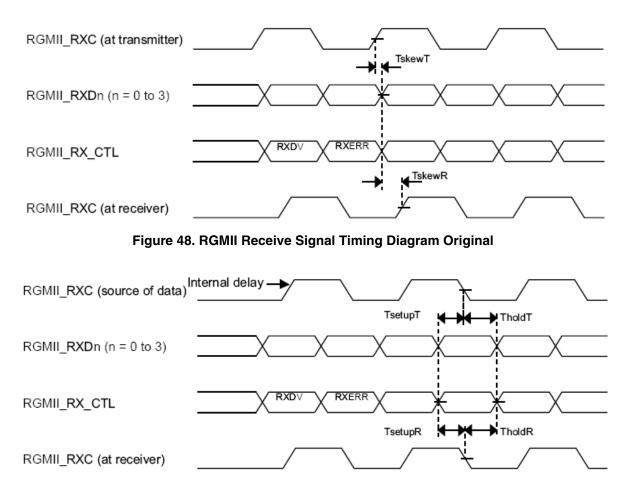

Figure 49. RGMII Receive Signal Timing Diagram with Internal Delay

# 4.12.6 Flexible Controller Area Network (FlexCAN) AC Electrical Specifications

The Flexible Controller Area Network (FlexCAN) module is a communication controller implementing the CAN protocol according to the CAN 2.0B protocol specification. The processor has two CAN modules available for systems design. Tx and Rx ports for both modules are multiplexed with other I/O pins. See the IOMUXC chapter of the i.MX 6Dual/6Quad reference manual (IMX6DQRM) to see which pins expose Tx and Rx pins; these ports are named FLEXCAN\_TX and FLEXCAN\_RX, respectively.

# 4.12.7 HDMI Module Timing Parameters

### 4.12.7.1 Latencies and Timing Information

Power-up time (time between TX\_PWRON assertion and TX\_READY assertion) for the HDMI 3D Tx PHY while operating with the slowest input reference clock supported (13.5 MHz) is 3.35 ms.

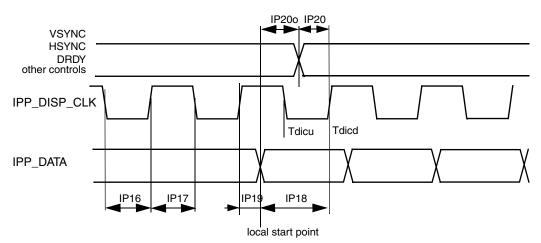

Figure 65 depicts the synchronous display interface timing for access level. The DISP\_CLK\_DOWN and DISP\_CLK\_UP parameters are register-controlled. Table 66 lists the synchronous display interface timing characteristics.

Figure 65. Synchronous Display Interface Timing Diagram—Access Level

| ID    | Parameter                                                                          | Symbol | Min                    | Typ <sup>1</sup>                       | Мах                   | Unit |

|-------|------------------------------------------------------------------------------------|--------|------------------------|----------------------------------------|-----------------------|------|

| IP16  | Display interface clock low time                                                   | Tckl   | Tdicd-Tdicu-1.24       | Tdicd <sup>2</sup> -Tdicu <sup>3</sup> | Tdicd-Tdicu+1.24      | ns   |

| IP17  | Display interface clock<br>high time                                               | Tckh   | Tdicp-Tdicd+Tdicu-1.24 | Tdicp-Tdicd+Tdicu                      | Tdicp-Tdicd+Tdicu+1.2 | ns   |

| IP18  | Data setup time                                                                    | Tdsu   | Tdicd-1.24             | Tdicu                                  | —                     | ns   |

| IP19  | Data holdup time                                                                   | Tdhd   | Tdicp-Tdicd-1.24       | Tdicp-Tdicu                            | —                     | ns   |

| IP20o | Control signals offset<br>times (defined for each<br>pin)                          | Tocsu  | Tocsu-1.24             | Tocsu                                  | Tocsu+1.24            | ns   |

| IP20  | Control signals setup time<br>to display interface clock<br>(defined for each pin) | Tcsu   | Tdicd-1.24-Tocsu%Tdicp | Tdicu                                  | _                     | ns   |

| Table 66. Synchronous Display Interface | e Timing Characteristics (Access Level) |

|-----------------------------------------|-----------------------------------------|

|-----------------------------------------|-----------------------------------------|

<sup>1</sup>The exact conditions have not been finalized, but will likely match the current customer requirement for their specific display. These conditions may be chip specific.

<sup>2</sup> Display interface clock down time

$$Tdicd = \frac{1}{2} \left( T_{diclk} \times ceil \left[ \frac{2 \times DISP_{CLK} DOWN}{DI_{CLK} PERIOD} \right] \right)$$

<sup>3</sup> Display interface clock up time where CEIL(X) rounds the elements of X to the nearest integers towards infinity.

$$\Gamma \text{dicu} = \frac{1}{2} \left( T_{\text{diclk}} \times \text{ceil} \left[ \frac{2 \times \text{DISP} \text{-} \text{CLK} \text{-} \text{UP}}{\text{DI} \text{-} \text{CLK} \text{-} \text{PERIOD}} \right] \right)$$

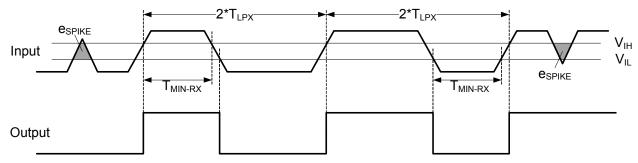

4.12.12.9 Low-Power Receiver Timing

Figure 72. Input Glitch Rejection of Low-Power Receivers

# 4.12.13 HSI Host Controller Timing Parameters

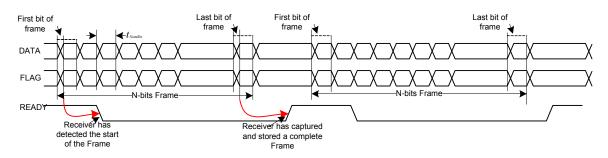

This section describes the timing parameters of the HSI Host Controller which are compliant with High-Speed Synchronous Serial Interface (HSI) Physical Layer specification version 1.01.

# 4.12.13.1 Synchronous Data Flow

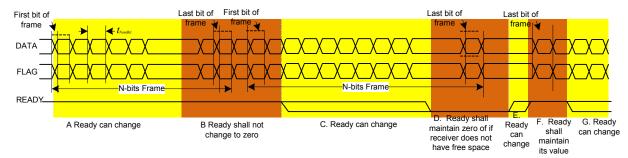

Figure 73. Synchronized Data Flow READY Signal Timing (Frame and Stream Transmission)

# 4.12.13.2 Pipelined Data Flow

Figure 74. Pipelined Data Flow READY Signal Timing (Frame Transmission Mode)

# 4.12.21 UART I/O Configuration and Timing Parameters

# 4.12.21.1 UART RS-232 I/O Configuration in Different Modes

The i.MX 6Dual/6Quad UART interfaces can serve both as DTE or DCE device. This can be configured by the DCEDTE control bit (default 0 - DCE mode). Table 86 shows the UART I/O configuration based on the enabled mode.

| Port                 |           | DTE Mode                    | DCE Mode  |                             |  |  |  |  |  |

|----------------------|-----------|-----------------------------|-----------|-----------------------------|--|--|--|--|--|

|                      | Direction | Description                 | Direction | Description                 |  |  |  |  |  |

| UARTx_RTS_B          | Output    | RTS from DTE to DCE         | Input     | RTS from DTE to DCE         |  |  |  |  |  |

| UARTx_CTS_B          | Input     | CTS from DCE to DTE         | Output    | CTS from DCE to DTE         |  |  |  |  |  |

| UARTx_DTR_B          | Output    | DTR from DTE to DCE         | Input     | DTR from DTE to DCE         |  |  |  |  |  |

| UARTx_DSR_B          | Input     | DSR from DCE to DTE         | Output    | DSR from DCE to DTE         |  |  |  |  |  |

| UARTx_DCD_B          | Input     | DCD from DCE to DTE         | Output    | DCD from DCE to DTE         |  |  |  |  |  |

| UARTx_RI_B           | Input     | RING from DCE to DTE        | Output    | RING from DCE to DTE        |  |  |  |  |  |

| UARTx_TX_DATA        | Input     | Serial data from DCE to DTE | Output    | Serial data from DCE to DTE |  |  |  |  |  |

| UARTx_RX_DATA Output |           | Serial data from DTE to DCE | Input     | Serial data from DTE to DCE |  |  |  |  |  |

### Table 86. UART I/O Configuration vs. Mode

### Package Information and Contact Assignments

|   | -           | 2           | e            | 4          | 5          | 9          | 7               | 8   | 6           | 10          | 11                        | 12            | 13         | 14        | 15  | 16        | 17        | 18  | 19           | 20         | 21         | 22         | 23         | 24         | 25       |

|---|-------------|-------------|--------------|------------|------------|------------|-----------------|-----|-------------|-------------|---------------------------|---------------|------------|-----------|-----|-----------|-----------|-----|--------------|------------|------------|------------|------------|------------|----------|

| н | DSI_D1P     | M10_ISU     | DSI_CLK0M    | DSI_CLK0P  | JTAG_TCK   | JTAG_MOD   | PCIE_VP         | GND |             | VDDHIGH_CAP | VDDARM23_CAP              | GND           | VDDARM_CAP | VDDARM_IN | GND | VDDSOC_IN | VDDPU_CAP | GND | EIM_A25      | EIM_D21    | EIM_D31    | EIM_A20    | EIM_A21    | EIM_CS0    | EIM_A16  |

| ſ | HDMI_REF    | GNÐ         | HDMI_D1M     | HDMI_D1P   | HDMI_CLKM  | HDMI_CLKP  | NVCC_JTAG       | GND | VDDHIGH_IN  | VDDHIGH_CAP | VDDARM23_CAP VDDARM23_CAP | GND           | VDDARM_CAP | VDDARM_IN | GND | VDDSOC_IN | VDDPU_CAP | GND | EIM_D29      | EIM_D30    | EIM_A23    | EIM_A18    | EIM_CS1    | EIM_OE     | EIM_DA1  |

| К |             | HDMI_DDCCEC | HDMI_D2M     | HDMI_D2P   | HDMI_D0M   | HDMI_D0P   | NVCC_MIPI       | GND | VDDARM23_IN | GND         | VDDARM23_CAP              | GND           | VDDARM_CAP | VDDARM_IN | GND | VDDSOC_IN | VDDPU_CAP | GND | NVCC_EIMO    | EIM_RW     | EIM_EB0    | EIM_LBA    | EIM_EB1    | EIM_DA3    | EIM_DA6  |

| Г | CSI0_DAT13  | GNÐ         | CSI0_DAT17   | CSI0_DAT16 | GND        | CSI0_DAT19 | <b>d</b> V_IMDH | GND | VDDARM23_IN | GND         | VDDARM23_CAP              | GND           | VDDARM_CAP | VDDARM_IN | GND | VDDSOC_IN | VDDPU_CAP | GND |              | EIM_DAO    | EIM_DA2    | EIM_DA4    | EIM_DA5    | EIM_DA8    | EIM_DA7  |