#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                     | Active                                                                                                              |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Core Processor                     | ARM® Cortex®-A9                                                                                                     |

| Number of Cores/Bus<br>Width       | 2 Core, 32-Bit                                                                                                      |

| Speed                              | 1.0GHz                                                                                                              |

| Co-Processors/DSP                  | Multimedia; NEON™ SIMD                                                                                              |

| RAM Controllers                    | LPDDR2, LVDDR3, DDR3                                                                                                |

| Graphics Acceleration              | Yes                                                                                                                 |

| Display & Interface<br>Controllers | Keypad, LCD                                                                                                         |

| Ethernet                           | 10/100/1000Mbps (1)                                                                                                 |

| SATA                               | SATA 3Gbps (1)                                                                                                      |

| USB                                | USB 2.0 + PHY (4)                                                                                                   |

| Voltage - I/O                      | 1.8V, 2.5V, 2.8V, 3.3V                                                                                              |

| Operating Temperature              | -40°C ~ 125°C (TJ)                                                                                                  |

| Security Features                  | ARM TZ, Boot Security, Cryptography, RTIC, Secure Fusebox, Secure JTAG, Secure Memory, Secure RTC, Tamper Detection |

| Package / Case                     | 624-FBGA, FCBGA                                                                                                     |

| Supplier Device Package            | 624-FCBGA (21x21)                                                                                                   |

| Purchase URL                       | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcimx6d6avt10ae                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 2. i.MX 6Dual/6Quad Modules List (continued) |

|----------------------------------------------------|

|----------------------------------------------------|

| Block<br>Mnemonic                              | Block Name                                   | Subsystem                        | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------------------------------------|----------------------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SSI-1<br>SSI-2<br>SSI-3                        | I2S/SSI/AC97<br>Interface                    | Connectivity<br>Peripherals      | The SSI is a full-duplex synchronous interface, which is used on the processor to provide connectivity with off-chip audio peripherals. The SSI supports a wide variety of protocols (SSI normal, SSI network, I2S, and AC-97), bit depths (up to 24 bits per word), and clock / frame sync options. The SSI has two pairs of 8x24 FIFOs and hardware support for an external DMA controller to minimize its impact on system performance. The second pair of FIFOs provides hardware interleaving of a second audio stream that reduces CPU overhead in use cases where two time slots are being used simultaneously. |

| TEMPMON                                        | Temperature Monitor                          | System<br>Control<br>Peripherals | The temperature monitor/sensor IP module for detecting high temperature conditions. The temperature read out does not reflect case or ambient temperature. It reflects the temperature in proximity of the sensor location on the die. Temperature distribution may not be uniformly distributed; therefore, the read out value may not be the reflection of the temperature value for the entire die.                                                                                                                                                                                                                 |

| TZASC                                          | Trust-Zone Address<br>Space Controller       | Security                         | The TZASC (TZC-380 by ARM) provides security address region control functions required for intended application. It is used on the path to the DRAM controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| UART-1<br>UART-2<br>UART-3<br>UART-4<br>UART-5 | UART Interface                               | Connectivity<br>Peripherals      | <ul> <li>Each of the UARTv2 modules support the following serial data transmit/receive protocols and configurations:</li> <li>7- or 8-bit data words, 1 or 2 stop bits, programmable parity (even, odd or none)</li> <li>Programmable baud rates up to 5 MHz</li> <li>32-byte FIFO on Tx and 32 half-word FIFO on Rx supporting auto-baud</li> <li>IrDA 1.0 support (up to SIR speed of 115200 bps)</li> <li>Option to operate as 8-pins full UART, DCE, or DTE</li> </ul>                                                                                                                                             |

| USBOH3A                                        | USB 2.0 High Speed<br>OTG and 3x HS<br>Hosts | Connectivity<br>Peripherals      | <ul> <li>USBOH3 contains:</li> <li>One high-speed OTG module with integrated HS USB PHY</li> <li>One high-speed Host module with integrated HS USB PHY</li> <li>Two identical high-speed Host modules connected to HSIC USB ports.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                          |

system to determine when the load capability of the regulator is being exceeded to take the necessary steps. Current-limiting can be enabled to allow for in-rush current requirements during start-up, if needed. Active-pull-down can also be enabled for systems requiring this feature.

For information on external capacitor requirements for this regulator, see the Hardware Development Guide for i.MX 6Quad, 6Dual, 6DualLite, 6Solo Families of Applications Processors (IMX6DQ6SDLHDG).

For additional information, see the i.MX 6Dual/6Quad reference manual (IMX6DQRM).

## 4.3.2.2 LDO\_2P5

The LDO\_2P5 module implements a programmable linear-regulator function from VDD\_HIGH\_IN (see Table 6 for min and max input requirements). Typical Programming Operating Range is 2.25 V to 2.75 V with the nominal default setting as 2.5 V. The LDO\_2P5 supplies the SATA PHY, USB PHY, LVDS PHY, HDMI PHY, MIPI PHY, E-fuse module and PLLs. A programmable brown-out detector is included in the regulator that can be used by the system to determine when the load capability of the regulator is being exceeded, to take the necessary steps. Current-limiting can be enabled to allow for in-rush current requirements during start-up, if needed. Active-pull-down can also be enabled for systems requiring this feature. An alternate self-biased low-precision weak-regulator is included that can be enabled for applications needing to keep the output voltage alive during low-power modes where the main regulator driver and its associated global bandgap reference module are disabled. The output of the weak-regulator is not programmable and is a function of the input supply as well as the load current. Typically, with a 3 V input supply the weak-regulator output is 2.525 V and its output impedance is approximately  $40 \, \Omega$ .

For information on external capacitor requirements for this regulator, see the Hardware Development Guide for i.MX 6Quad, 6Dual, 6DualLite, 6Solo Families of Applications Processors (IMX6DQ6SDLHDG).

For additional information, see the i.MX 6Dual/6Quad reference manual (IMX6DQRM).

## 4.3.2.3 LDO\_USB

The LDO\_USB module implements a programmable linear-regulator function from the USB\_OTG\_VBUS and USB\_H1\_VBUS voltages (4.4 V–5.25 V) to produce a nominal 3.0 V output voltage. A programmable brown-out detector is included in the regulator that can be used by the system to determine when the load capability of the regulator is being exceeded, to take the necessary steps. This regulator has a built in power-mux that allows the user to select to run the regulator from either VBUS supply, when both are present. If only one of the VBUS voltages is present, then the regulator automatically selects this supply. Current limit is also included to help the system meet in-rush current targets. If no VBUS voltage is present, then the VBUSVALID threshold setting will prevent the regulator from being enabled.

For information on external capacitor requirements for this regulator, see the Hardware Development Guide for i.MX 6Quad, 6Dual, 6DualLite, 6Solo Families of Applications Processors (IMX6DQ6SDLHDG).

For additional information, see the i.MX 6Dual/6Quad reference manual (IMX6DQRM).

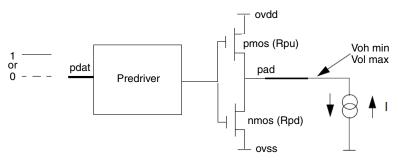

Figure 3. Circuit for Parameters Voh and Vol for I/O Cells

## 4.6.1 XTALI and RTC\_XTALI (Clock Inputs) DC Parameters

Table 21 shows the DC parameters for the clock inputs.

| Table 21. XTALI and RTC_ | XTALI DC Parameters |

|--------------------------|---------------------|

|--------------------------|---------------------|

| Parameter                              | Symbol                     | Test Conditions                                                                              | Min                | Тур | Max                         | Unit |

|----------------------------------------|----------------------------|----------------------------------------------------------------------------------------------|--------------------|-----|-----------------------------|------|

| XTALI high-level DC input voltage      | Vih                        | _                                                                                            | 0.8 x NVCC_PLL_OUT | —   | NVCC_PLL_ OUT               | V    |

| XTALI low-level DC input voltage       | Vil                        | —                                                                                            | 0                  | —   | 0.2                         | V    |

| RTC_XTALI high-level DC input voltage  | Vih                        | —                                                                                            | 0.8                | _   | 1.1 <sup>(See note 1)</sup> | V    |

| RTC_XTALI low-level DC input voltage   | Vil                        | —                                                                                            | 0                  | _   | 0.2                         | V    |

| Input capacitance                      | C <sub>IN</sub>            | Simulated data                                                                               | —                  | 5   | —                           | pF   |

| XTALI input leakage current at startup | I <sub>XTALI_STARTUP</sub> | Power-on startup for<br>0.15 msec with a driven<br>32 KHz RTC clock<br>@ 1.1 V. <sup>2</sup> | _                  | —   | 600                         | μA   |

| DC input current                       | I <sub>XTALI_DC</sub>      | —                                                                                            | —                  | —   | 2.5                         | μΑ   |

<sup>1</sup> This voltage specification must not be exceeded and, as such, is an absolute maximum specification.

<sup>2</sup> This current draw is present even if an external clock source directly drives XTALI.

### NOTE

The Vil and Vih specifications only apply when an external clock source is used. If a crystal is used, Vil and Vih do not apply.

## 4.6.2 General Purpose I/O (GPIO) DC Parameters

Table 22 shows DC parameters for GPIO pads. The parameters in Table 22 are guaranteed per the operating ranges in Table 6, unless otherwise noted.

| Parameter                                              | Symbol           | Test Conditions                           | Min  | Max  | Unit |

|--------------------------------------------------------|------------------|-------------------------------------------|------|------|------|

| Output Differential Voltage                            | V <sub>OD</sub>  | Rload = 50 $\Omega$ between padP and padN | 300  | 500  | mV   |

| Output High Voltage                                    | V <sub>OH</sub>  |                                           | 1.15 | 1.75 | V    |

| Output Low Voltage                                     | V <sub>OL</sub>  |                                           | 0.75 | 1.35 | V    |

| Common-mode Output Voltage<br>((Vpad_P + Vpad_N) / 2)) | V <sub>OCM</sub> |                                           | 1    | 1.5  | V    |

| Differential Output Impedance                          | Z <sub>O</sub>   | —                                         | 1.6  | _    | kΩ   |

### Table 27. MLB I/O DC Parameters

## 4.7 I/O AC Parameters

This section includes the AC parameters of the following I/O types:

- General Purpose I/O (GPIO)

- Double Data Rate I/O (DDR) for LPDDR2 and DDR3/DDR3L modes

- LVDS I/O

- MLB I/O

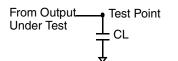

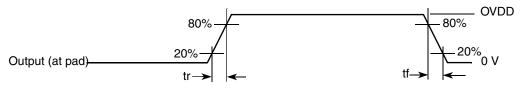

The GPIO and DDR I/O load circuit and output transition time waveforms are shown in Figure 4 and Figure 5.

CL includes package, probe and fixture capacitance

### Figure 4. Load Circuit for Output

Figure 5. Output Transition Time Waveform

### 4.9.3.2 General EIM Timing-Synchronous Mode

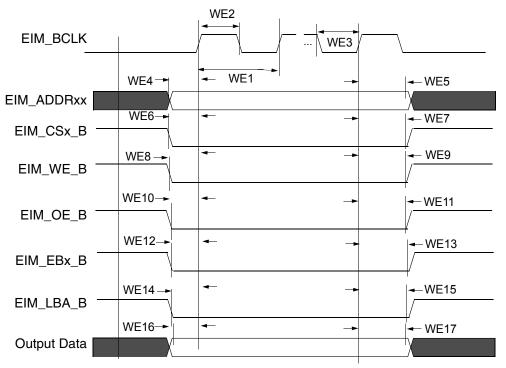

Figure 12, Figure 13, and Table 41 specify the timings related to the EIM module. All EIM output control signals may be asserted and deasserted by an internal clock synchronized to the EIM\_BCLK rising edge according to corresponding assertion/negation control fields.

Figure 12. EIM Output Timing Diagram

Figure 13. EIM Input Timing Diagram

### 4.9.3.3 Examples of EIM Synchronous Accesses

Table 41. EIM Bus Timing Parameters

| ID  | Parameter                        | Min <sup>1</sup>            | Max <sup>1</sup> | Unit |

|-----|----------------------------------|-----------------------------|------------------|------|

| WE1 | EIM_BCLK cycle time <sup>2</sup> | t × (k+1)                   | _                | ns   |

| WE2 | EIM_BCLK high level width        | $0.4 \times t \times (k+1)$ | —                | ns   |

| WE3 | EIM_BCLK low level width         | $0.4 \times t \times (k+1)$ | _                | ns   |

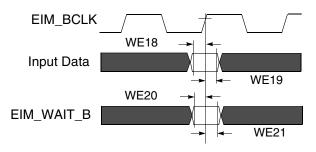

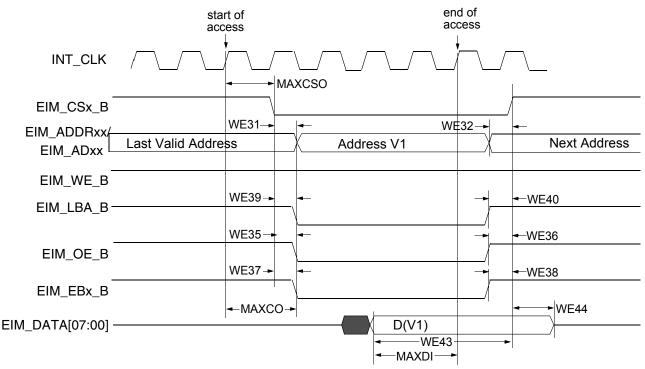

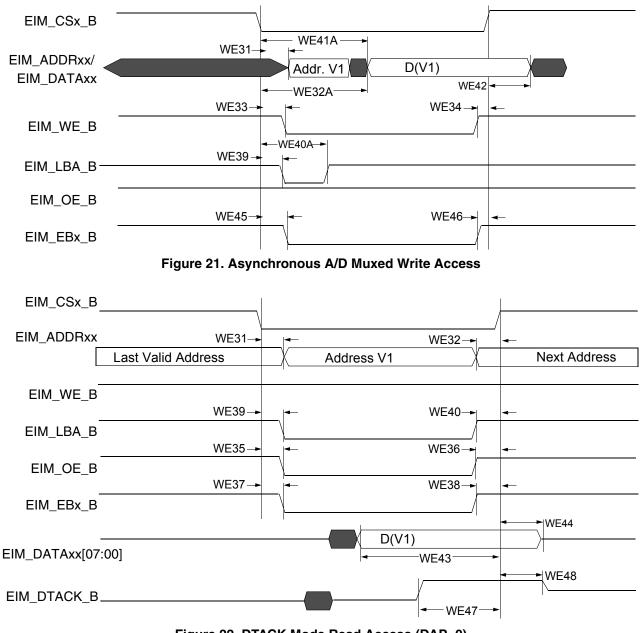

### 4.9.3.4 General EIM Timing-Asynchronous Mode

Figure 18 through Figure 22 and Table 42 provide timing parameters relative to the chip select (CS) state for asynchronous and DTACK EIM accesses with corresponding EIM bit fields and the timing parameters mentioned above.

Asynchronous read and write access length in cycles may vary from what is shown in Figure 18 through Figure 21 as RWSC, OEN & CSN is configured differently. See the i.MX 6Dual/6Quad reference manual (IMX6DQRM) for the EIM programming model.

Figure 18. Asynchronous Memory Read Access (RWSC = 5)

Figure 22. DTACK Mode Read Access (DAP=0)

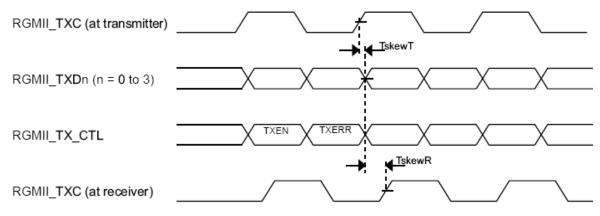

### 4.12.5.3 RGMII Signal Switching Specifications

The following timing specifications meet the requirements for RGMII interfaces for a range of transceiver devices.

| Symbol                          | Description                              | Min  | Max  | Unit |

|---------------------------------|------------------------------------------|------|------|------|

| T <sub>cyc</sub> <sup>2</sup>   | Clock cycle duration                     | 7.2  | 8.8  | ns   |

| T <sub>skewT</sub> <sup>3</sup> | Data to clock output skew at transmitter | -100 | 900  | ps   |

| T <sub>skewR</sub> <sup>3</sup> | Data to clock input skew at receiver     | 1    | 2.6  | ns   |

| Duty_G <sup>4</sup>             | Duty cycle for Gigabit                   | 45   | 55   | %    |

| Duty_T <sup>4</sup>             | Duty cycle for 10/100T                   | 40   | 60   | %    |

| Tr/Tf                           | Rise/fall time (20–80%)                  | _    | 0.75 | ns   |

| Table 58. RGMII Signal | I Switching Specifications |

|------------------------|----------------------------|

|------------------------|----------------------------|

<sup>1</sup> The timings assume the following configuration: DDR\_SEL = (11)b

DSE (drive-strength) = (111)b

$^2~$  For 10 Mbps and 100 Mbps,  $T_{cyc}$  will scale to 400 ns ±40 ns and 40 ns ±4 ns respectively.

<sup>3</sup> For all versions of RGMII prior to 2.0; This implies that PC board design will require clocks to be routed such that an additional delay of greater than 1.2 ns and less than 1.7 ns will be added to the associated clock signal. For 10/100, the max value is unspecified.

<sup>4</sup> Duty cycle may be stretched/shrunk during speed changes or while transitioning to a received packet's clock domain as long as minimum duty cycle is not violated and stretching occurs for no more than three Tcyc of the lowest speed transitioned between.

Figure 47. RGMII Transmit Signal Timing Diagram Original

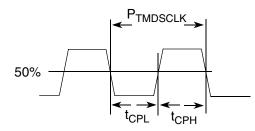

Figure 53. TMDS Clock Signal Definitions

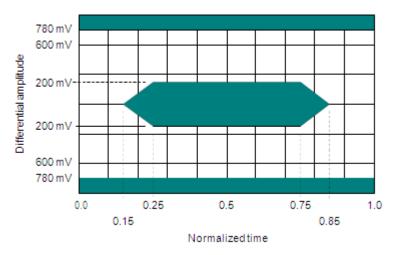

Figure 54. Eye Diagram Mask Definition for HDMI Driver Signal Specification at TP1

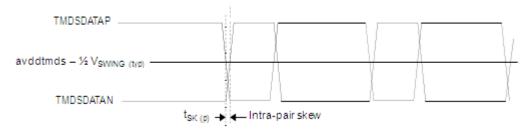

Figure 55. Intra-Pair Skew Definition

| i.MX 6Dual/6Quad        |                             |                           |               |               |                             |                                    |                                                                    |                                              |

|-------------------------|-----------------------------|---------------------------|---------------|---------------|-----------------------------|------------------------------------|--------------------------------------------------------------------|----------------------------------------------|

|                         | RGB,                        | R                         | GB/TV         | Signal /      | Allocatior                  | n (Examp                           | ole)                                                               | Comment <sup>1,2</sup>                       |

| Port Name<br>(x = 0, 1) | Signal<br>Name<br>(General) | 16-bit<br>RGB             | 18-bit<br>RGB | 24 Bit<br>RGB | 8-bit<br>YCrCb <sup>3</sup> | 16-bit<br>YCrCb                    | 20-bit<br>YCrCb                                                    |                                              |

| IPUx_DIx_PIN04          |                             | / _ / _ / _ / _ / _ / _ / |               |               |                             |                                    | 1                                                                  | Additional frame/row synchronous             |

| IPUx_DIx_PIN05          |                             |                           |               |               |                             |                                    |                                                                    | signals with programmable timing             |

| IPUx_DIx_PIN06          |                             |                           |               |               |                             |                                    |                                                                    |                                              |

| IPUx_DIx_PIN07          |                             |                           |               |               |                             |                                    |                                                                    |                                              |

| IPUx_DIx_PIN08          |                             | _                         |               |               |                             |                                    |                                                                    |                                              |

| IPUx_DIx_D0_CS          |                             |                           |               | _             |                             |                                    |                                                                    | —                                            |

| IPUx_DIx_D1_CS          |                             | _                         |               |               |                             |                                    | Alternate mode of PWM output for<br>contrast or brightness control |                                              |

| IPUx_DIx_PIN11          |                             |                           |               | _             |                             |                                    |                                                                    |                                              |

| IPUx_DIx_PIN12          |                             |                           |               | _             |                             |                                    |                                                                    |                                              |

| IPUx_DIx_PIN13          |                             |                           |               | _             |                             |                                    |                                                                    | Register select signal                       |

| IPUx_DIx_PIN14          |                             | _                         |               |               |                             | Optional RS2                       |                                                                    |                                              |

| IPUx_DIx_PIN15          |                             | DRDY/DV                   |               |               |                             | Data validation/blank, data enable |                                                                    |                                              |

| IPUx_DIx_PIN16          |                             |                           |               |               |                             |                                    | Additional data synchronous                                        |                                              |

| IPUx_DIx_PIN17          |                             |                           |               | Q             |                             |                                    |                                                                    | signals with programmable<br>features/timing |

#### Table 64. Video Signal Cross-Reference (continued)

<sup>1</sup> Signal mapping (both data and control/synchronization) is flexible. The table provides examples.

<sup>2</sup> Restrictions for ports IPUx\_DISPx\_DAT00 through IPUx\_DISPx\_DAT23 are as follows:

• A maximum of three continuous groups of bits can be independently mapped to the external bus. Groups must not overlap.

• The bit order is expressed in each of the bit groups, for example, B[0] = least significant blue pixel bit.

<sup>3</sup> This mode works in compliance with recommendation ITU-R BT.656. The timing reference signals (frame start, frame end, line start, and line end) are embedded in the 8-bit data bus. Only video data is supported, transmission of non-video related data during blanking intervals is not supported.

### NOTE

Table 64 provides information for both the DISP0 and DISP1 ports. However, DISP1 port has reduced pinout depending on IOMUXC configuration and therefore may not support all configurations. See the IOMUXC table for details.

### 4.12.10.5 IPU Display Interface Timing

The IPU Display Interface supports two kinds of display accesses: synchronous and asynchronous. There are two groups of external interface pins to provide synchronous and asynchronous controls.

### 4.12.10.5.1 Synchronous Controls

The synchronous control changes its value as a function of a system or of an external clock. This control has a permanent period and a permanent waveform.

## 4.12.11 LVDS Display Bridge (LDB) Module Parameters

The LVDS interface complies with TIA/EIA 644-A standard. For more details, see TIA/EIA STANDARD 644-A, "Electrical Characteristics of Low Voltage Differential Signaling (LVDS) Interface Circuits."

| Parameter                           | Symbol              | Test Condition                                                                                                                                     |      | Max   | Units |

|-------------------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-------|

| Differential Voltage Output Voltage | V <sub>OD</sub>     | 100 $\Omega$ Differential load                                                                                                                     | 250  | 450   | mV    |

| Output Voltage High                 | Voh                 | 100 $\Omega$ differential load<br>(0 V Diff—Output High Voltage static)                                                                            | 1.25 | 1.6   | V     |

| Output Voltage Low                  | Vol                 | 00 Ω differential load<br>0 V Diff—Output Low Voltage static)                                                                                      |      | 1.25  | V     |

| Offset Static Voltage               | V <sub>OS</sub>     | Two 49.9 $\Omega$ resistors in series between N-P terminal, with output in either Zero or One state, the voltage measured between the 2 resistors. | 1.15 | 1.375 | V     |

| VOS Differential                    | V <sub>OSDIFF</sub> | Difference in $V_{\mbox{\scriptsize OS}}$ between a One and a Zero state                                                                           | -50  | 50    | mV    |

| Output short-circuited to GND       | ISA ISB             | With the output common shorted to GND                                                                                                              | -24  | 24    | mA    |

| VT Full Load Test                   | VTLoad              | 100 $\Omega$ Differential load with a 3.74 k $\Omega$ load between GND and I/O supply voltage                                                      | 247  | 454   | mV    |

Table 67. LVDS Display Bridge (LDB) Electrical Specification

## 4.12.12 MIPI D-PHY Timing Parameters

This section describes MIPI D-PHY electrical specifications, compliant with MIPI CSI-2 version 1.0, D-PHY specification Rev. 1.0 (for MIPI sensor port x4 lanes) and MIPI DSI Version 1.01, and D-PHY specification Rev. 1.0 (and also DPI version 2.0, DBI version 2.0, DSC version 1.0a at protocol layer) (for MIPI display port x2 lanes).

### 4.12.12.1 Electrical and Timing Information

| Symbol                                                                                               | Parameters                                                             | Test Conditions                                                                   | Min | Тур | Max  | Unit |  |  |  |  |

|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----|-----|------|------|--|--|--|--|

|                                                                                                      | Input DC Specifications—Apply to DSI_CLK_P/_N and DSI_DATA_P/_N Inputs |                                                                                   |     |     |      |      |  |  |  |  |

| V <sub>1</sub> Input signal voltage range Transient voltage range is limited from -300 mV to 1600 mV |                                                                        |                                                                                   |     | —   | 1350 | mV   |  |  |  |  |

| V <sub>LEAK</sub>                                                                                    | Input leakage current                                                  | VGNDSH(min) = VI = VGNDSH(max) +<br>VOH(absmax)<br>Lane module in LP Receive Mode | -10 |     | 10   | mA   |  |  |  |  |

| V <sub>GNDSH</sub>                                                                                   | Ground Shift                                                           | _                                                                                 | -50 |     | 50   | mV   |  |  |  |  |

| V <sub>OH(absmax)</sub>                                                                              | Maximum transient output voltage level                                 | _                                                                                 | _   | _   | 1.45 | V    |  |  |  |  |

| t <sub>voh(absmax)</sub>                                                                             | Maximum transient time<br>above VOH(absmax)                            | _                                                                                 | _   |     | 20   | ns   |  |  |  |  |

Table 68. Electrical and Timing Information

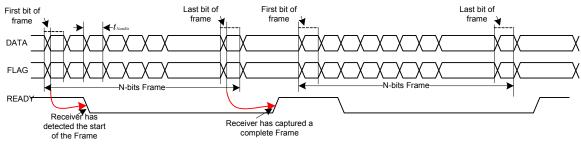

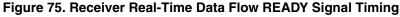

### 4.12.13.3 Receiver Real-Time Data Flow

Figure 76. Synchronized Data Flow Transmission with WAKE

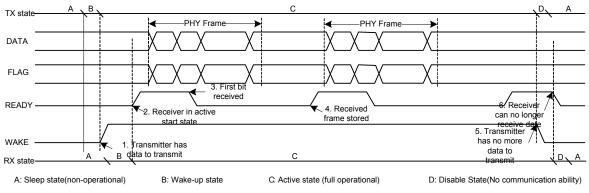

### 4.12.13.5 Stream Transmission Mode Frame Transfer

| Parameter                                                                                                                   | Symbol                                                   | Test Conditions       | Min        | Max        | Unit           |

|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-----------------------|------------|------------|----------------|

| Common-mode output voltage:<br>(V <sub>O+</sub> - V <sub>O-</sub> ) / 2                                                     | V <sub>OCM</sub>                                         | _                     | 1.0        | 1.5        | V              |

| Difference in common-mode output between<br>(high/low) steady-states:<br>I V <sub>OCM, high</sub> - V <sub>OCM, low</sub> I | ΔV <sub>OCM</sub>                                        | _                     | -50        | 50         | mV             |

| Variations on common-mode output during a logic state transitions                                                           | V <sub>CMV</sub>                                         | See Note <sup>2</sup> | —          | 150        | mVpp           |

| Short circuit current                                                                                                       | ll <sub>os</sub> l                                       | See Note <sup>3</sup> | —          | 43         | mA             |

| Differential output impedance                                                                                               | Z <sub>O</sub>                                           | _                     | 1.6        | _          | kΩ             |

|                                                                                                                             | Receiver                                                 | Characteristics       |            |            |                |

| Differential clock input:<br>• logic low steady-state<br>• logic high steady-state<br>• hysteresis                          | V <sub>ILC</sub><br>V <sub>IHC</sub><br>V <sub>HSC</sub> | See Note <sup>4</sup> | 50<br>-25  | -50<br>25  | mV<br>mV<br>mV |

| Differential signal/data input:<br>• logic low steady-state<br>• logic high steady-state                                    | V <sub>ILS</sub><br>V <sub>IHS</sub>                     | _                     | <br>50     | -50<br>—   | mV<br>mV       |

| Signal-ended input voltage (steady-state):<br>• MLB_SIG_P, MLB_DATA_P<br>• MLB_SIG_N, MLB_DATA_N                            | V <sub>IN+</sub><br>V <sub>IN-</sub>                     | _                     | 0.5<br>0.5 | 2.0<br>2.0 | v<br>v         |

Table 72. MediaLB 6-Pin Interface Electrical DC Specifications (continued)

The signal-ended output voltage of a driver is defined as  $V_{O+}$  on MLB\_CLK\_P, MLB\_SIG\_P, and MLB\_DATA\_P. The signal-ended output voltage of a driver is defined as  $V_{O-}$  on MLB\_CLK\_N, MLB\_SIG\_N, and MLB\_DATA\_N.

<sup>2</sup> Variations in the common-mode voltage can occur between logic states (for example, during state transitions) as a result of differences in the transition rate of V<sub>O+</sub> and V<sub>O-</sub>.

$^3\,$  Short circuit current is applicable when V\_{O\_{+}} and V\_{O\_{-}} are shorted together and/or shorted to ground.

$^4\,$  The logic state of the receiver is undefined when -50 mV < V\_{ID} < 50 mV.

| Parameter                                                                                                              | Symbol              | Min  | Max | Unit | Comment |

|------------------------------------------------------------------------------------------------------------------------|---------------------|------|-----|------|---------|

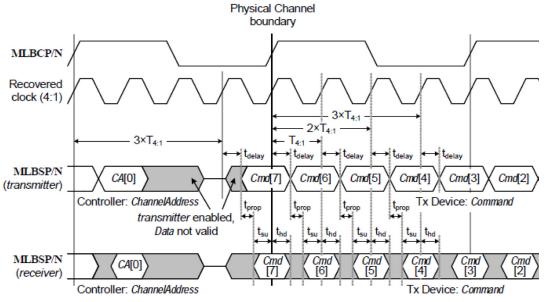

| Cycle-to-cycle system jitter                                                                                           | t <sub>jitter</sub> | _    | 600 | ps   | —       |

| Transmitter MLB_SIG_P/_N<br>(MLB_DATA_P/_N) output valid from transition<br>of MLB_CLK_P/_N (low-to-high) <sup>1</sup> | t <sub>delay</sub>  | 0.6  | 1.3 | ns   | _       |

| Disable turnaround time from transition of MLB_CLK_P/_N (low-to-high)                                                  | t <sub>phz</sub>    | 0.6  | 3.5 | ns   | _       |

| Enable turnaround time from transition of MLB_CLK_P/_N (low-to-high)                                                   | t <sub>plz</sub>    | 0.6  | 5.6 | ns   | _       |

| MLB_SIG_P/_N (MLB_DATA_P/_N) valid to transition of MLB_CLK_P/_N (low-to-high)                                         | t <sub>su</sub>     | 0.05 | —   | ns   | _       |

| MLB_SIG_P/_N (MLB_DATA_P/_N) hold from transition of MLB_CLK_P/_N (low-to-high) <sup>2</sup>                           | t <sub>hd</sub>     | 0.6  | —   | ns   | _       |

Table 75. MLB 6-Pin Interface Timing Parameters

t<sub>delay</sub>, t<sub>phz</sub>, t<sub>plz</sub>, t<sub>su</sub>, and t<sub>hd</sub> may also be referenced from a low-to-high transition of the recovered clock for 2:1 and 4:1 recovered-to-external clock ratios.

<sup>2</sup> The transmitting device must ensure valid data on MLB\_SIG\_P/\_N (MLB\_DATA\_P/\_N) for at least t<sub>hd(min)</sub> following the rising edge of MLBCP/N; receivers must latch MLB\_SIG\_P/\_N (MLB\_DATA\_P/\_N) data within t<sub>hd(min)</sub> of the rising edge of MLB\_CLK\_P/\_N.

Figure 82. MLB 6-Pin Delay, Setup, and Hold Times

### 4.12.15 PCIe PHY Parameters

The PCIe interface complies with PCIe specification Gen2 x1 lane and supports the PCI Express 1.1/2.0 standard.

1

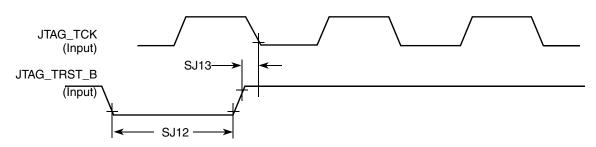

Figure 87. JTAG\_TRST\_B Timing Diagram

| ID   | Parameter <sup>1,2</sup>                                            | All Freq | uencies | Unit |

|------|---------------------------------------------------------------------|----------|---------|------|

|      |                                                                     | Min      | Max     |      |

| SJ0  | JTAG_TCK frequency of operation 1/(3xT <sub>DC</sub> ) <sup>1</sup> | 0.001    | 22      | MHz  |

| SJ1  | JTAG_TCK cycle time in crystal mode                                 | 45       | _       | ns   |

| SJ2  | JTAG_TCK clock pulse width measured at $V_M^2$                      | 22.5     | _       | ns   |

| SJ3  | JTAG_TCK rise and fall times                                        | —        | 3       | ns   |

| SJ4  | Boundary scan input data set-up time                                | 5        | —       | ns   |

| SJ5  | Boundary scan input data hold time                                  | 24       | _       | ns   |

| SJ6  | JTAG_TCK low to output data valid                                   | —        | 40      | ns   |

| SJ7  | JTAG_TCK low to output high impedance                               | —        | 40      | ns   |

| SJ8  | JTAG_TMS, JTAG_TDI data set-up time                                 | 5        | —       | ns   |

| SJ9  | JTAG_TMS, JTAG_TDI data hold time                                   | 25       | _       | ns   |

| SJ10 | JTAG_TCK low to JTAG_TDO data valid                                 | —        | 44      | ns   |

| SJ11 | JTAG_TCK low to JTAG_TDO high impedance                             | —        | 44      | ns   |

| SJ12 | JTAG_TRST_B assert time                                             | 100      | —       | ns   |

| SJ13 | JTAG_TRST_B set-up time to JTAG_TCK low                             | 40       | —       | ns   |

| Table | 79. | <b>JTAG</b> | Timing |

|-------|-----|-------------|--------|

| 14010 |     |             |        |

<sup>1</sup>  $T_{DC}$  = target frequency of SJC

<sup>2</sup>  $V_{M}$  = mid-point voltage

## 4.12.19 SPDIF Timing Parameters

The Sony/Philips Digital Interconnect Format (SPDIF) data is sent using the bi-phase marking code. When encoding, the SPDIF data signal is modulated by a clock that is twice the bit rate of the data signal.

Table 80 and Figure 88 and Figure 89 show SPDIF timing parameters for the Sony/Philips Digital Interconnect Format (SPDIF), including the timing of the modulating Rx clock (SPDIF\_SR\_CLK) for SPDIF in Rx mode and the timing of the modulating Tx clock (SPDIF\_ST\_CLK) for SPDIF in Tx mode.

| ID   | Parameter                                           | Min    | Max  | Unit |  |  |  |  |

|------|-----------------------------------------------------|--------|------|------|--|--|--|--|

|      | Internal Clock Operation                            |        |      |      |  |  |  |  |

| SS1  | AUDx_TXC/AUDx_RXC clock period                      | 81.4   | _    | ns   |  |  |  |  |

| SS2  | AUDx_TXC/AUDx_RXC clock high period                 | 36.0   | —    | ns   |  |  |  |  |

| SS4  | AUDx_TXC/AUDx_RXC clock low period                  | 36.0   | —    | ns   |  |  |  |  |

| SS6  | AUDx_TXC high to AUDx_TXFS (bl) high                | —      | 15.0 | ns   |  |  |  |  |

| SS8  | AUDx_TXC high to AUDx_TXFS (bl) low                 | —      | 15.0 | ns   |  |  |  |  |

| SS10 | AUDx_TXC high to AUDx_TXFS (wl) high                | —      | 15.0 | ns   |  |  |  |  |

| SS12 | AUDx_TXC high to AUDx_TXFS (wl) low                 | _      | 15.0 | ns   |  |  |  |  |

| SS14 | AUDx_TXC/AUDx_RXC Internal AUDx_TXFS rise time      | —      | 6.0  | ns   |  |  |  |  |

| SS15 | AUDx_TXC/AUDx_RXC Internal AUDx_TXFS fall time      | —      | 6.0  | ns   |  |  |  |  |

| SS16 | AUDx_TXC high to AUDx_TXD valid from high impedance | —      | 15.0 | ns   |  |  |  |  |

| SS17 | AUDx_TXC high to AUDx_TXD high/low                  | —      | 15.0 | ns   |  |  |  |  |

| SS18 | AUDx_TXC high to AUDx_TXD high impedance            | —      | 15.0 | ns   |  |  |  |  |

|      | Synchronous Internal Clock Oper                     | ration |      |      |  |  |  |  |

| SS42 | AUDx_RXD setup before AUDx_TXC falling              | 10.0   | _    | ns   |  |  |  |  |

| SS43 | AUDx_RXD hold after AUDx_TXC falling                | 0.0    | —    | ns   |  |  |  |  |

#### Table 82. SSI Transmitter Timing with Internal Clock

### NOTE

- All the timings for the SSI are given for a non-inverted serial clock polarity (TSCKP/RSCKP = 0) and a non-inverted frame sync (TFSI/RFSI = 0). If the polarity of the clock and/or the frame sync have been inverted, all the timing remains valid by inverting the clock signal AUDx\_TXC/AUDx\_RXC and/or the frame sync AUDx\_TXFS/AUDx\_RXFS shown in the tables and in the figures.

- All timings are on Audiomux Pads when SSI is being used for data transfer.

- The terms, WL and BL, refer to Word Length (WL) and Bit Length (BL).

- For internal Frame Sync operation using external clock, the frame sync timing is the same as that of transmit data (for example, during AC97 mode of operation).

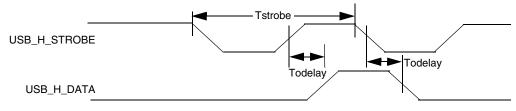

## 4.12.22 USB HSIC Timings

This section describes the electrical information of the USB HSIC port.

### NOTE

HSIC is a DDR signal. The following timing specification is for both rising and falling edges.

### 4.12.22.1 Transmit Timing

Figure 98. USB HSIC Transmit Waveform

#### Table 91. USB HSIC Transmit Parameters

| Name    | Parameter                       | Min   | Max   | Unit | Comment                        |

|---------|---------------------------------|-------|-------|------|--------------------------------|

| Tstrobe | strobe period                   | 4.166 | 4.167 | ns   | _                              |

| Todelay | data output delay time          | 550   | 1350  | ps   | Measured at 50% point          |

| Tslew   | strobe/data rising/falling time | 0.7   | 2     | V/ns | Averaged from 30% – 70% points |

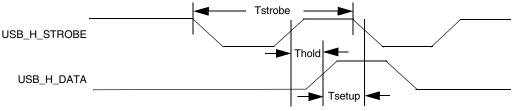

### 4.12.22.2 Receive Timing

Figure 99. USB HSIC Receive Waveform

### Table 92. USB HSIC Receive Parameters<sup>1</sup>

| Name    | Parameter                       | Min   | Max   | Unit | Comment                        |

|---------|---------------------------------|-------|-------|------|--------------------------------|

| Tstrobe | strobe period                   | 4.166 | 4.167 | ns   | —                              |

| Thold   | data hold time                  | 300   | —     | ps   | Measured at 50% point          |

| Tsetup  | data setup time                 | 365   | —     | ps   | Measured at 50% point          |

| Tslew   | strobe/data rising/falling time | 0.7   | 2     | V/ns | Averaged from 30% – 70% points |

<sup>1</sup> The timings in the table are guaranteed when:

-AC I/O voltage is between 0.9x to 1x of the I/O supply

-DDR\_SEL configuration bits of the I/O are set to (10)b

# 6 Package Information and Contact Assignments

This section includes the contact assignment information and mechanical package drawing.

## 6.1 Signal Naming Convention

The signal names of the i.MX6 series of products are standardized to align the signal names within the family and across the documentation. Benefits of this standardization are as follows:

- Signal names are unique within the scope of an SoC and within the series of products

- Searches will return all occurrences of the named signal

- Signal names are consistent between i.MX 6 series products implementing the same modules

- The module instance is incorporated into the signal name

This standardization applies only to signal names. The ball names are preserved to prevent the need to change schematics, BSDL models, IBIS models, and so on.

Throughout this document, the signal names are used except where referenced as a ball name (such as the Functional Contact Assignments table, Ball Map table, and so on). A master list of signal names is in the document, *IMX 6 Series Standardized Signal Name Map* (EB792). This list can be used to map the signal names used in older documentation to the standardized naming conventions.

## 6.2 21 x 21 mm Package Information

## 6.2.1 Case FCPBGA, 21 x 21 mm, 0.8 mm Pitch, 25 x 25 Ball Matrix

#### Package Information and Contact Assignments

| Supply Rail Name | Ball(s) Position(s)                              | Remark                                                                                                                              |

|------------------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| VDDHIGH_CAP      | H10, J10                                         | Secondary supply for the 2.5 V domain<br>(internal regulator output—requires<br>capacitor if internal regulator is used)            |

| VDDHIGH_IN       | H9, J9                                           | Primary supply for the 2.5 V regulator                                                                                              |

| VDDPU_CAP        | H17, J17, K17, L17, M17, N17, P17                | Secondary supply for the VPU and<br>GPU (internal regulator output—<br>requires capacitor if internal regulator<br>is used)         |

| VDDSOC_CAP       | R10, T10, T13, T14, U10, U13, U14                | Secondary supply for the SoC and PU<br>(internal regulator output—requires<br>capacitor if internal regulator is used)              |

| VDDSOC_IN        | H16, J16, K16, L16, M16, N16, P16, R16, T16, U16 | Primary supply for the SoC and PU regulators                                                                                        |

| VDDUSB_CAP       | F9                                               | Secondary supply for the 3 V domain<br>(internal regulator output—requires<br>capacitor if internal regulator is used)              |

| ZQPAD            | AE17                                             | Connect ZQPAD to an external $240\Omega$ 1% resistor to GND. This is a reference used during DRAM output buffer driver calibration. |

### Table 95. 21 x 21 mm Supplies Contact Assignment (continued)

### 6.2.3 21 x 21 mm Functional Contact Assignments

Table 96 displays an alpha-sorted list of the signal assignments including power rails. The table also includes out of reset pad state.

|            |      |              |           |                                    | Out of Reset Con                  | dition <sup>1</sup> |                    |

|------------|------|--------------|-----------|------------------------------------|-----------------------------------|---------------------|--------------------|

| Ball Name  | Ball | Power Group  | Ball Type | Default<br>Mode<br>(Reset<br>Mode) | Default Function<br>(Signal Name) | Input/Output        | Value <sup>2</sup> |

| BOOT_MODE0 | C12  | VDD_SNVS_IN  | GPIO      | ALT0                               | SRC_BOOT_MODE0                    | Input               | PD (100K)          |

| BOOT_MODE1 | F12  | VDD_SNVS_IN  | GPIO      | ALT0                               | SRC_BOOT_MODE1                    | Input               | PD (100K)          |

| CLK1_N     | C7   | VDD_HIGH_CAP | —         | —                                  | CLK1_N                            | —                   | —                  |

| CLK1_P     | D7   | VDD_HIGH_CAP | —         | —                                  | CLK1_P                            | —                   | —                  |

| CLK2_N     | C5   | VDD_HIGH_CAP | —         |                                    | CLK2_N                            | —                   | —                  |

| CLK2_P     | D5   | VDD_HIGH_CAP | —         | —                                  | CLK2_P                            | —                   | —                  |

| CSI_CLK0M  | F4   | NVCC_MIPI    | —         | —                                  | CSI_CLK_N                         | —                   | —                  |

| CSI_CLK0P  | F3   | NVCC_MIPI    | —         | —                                  | CSI_CLK_P                         | —                   | —                  |

| CSI_D0M    | E4   | NVCC_MIPI    | —         | —                                  | CSI_DATA0_N                       | —                   | —                  |

| CSI_D0P    | E3   | NVCC_MIPI    | —         | —                                  | CSI_DATA0_P                       | —                   | —                  |

| CSI_D1M    | D1   | NVCC_MIPI    | _         |                                    | CSI_DATA1_N                       | _                   | —                  |

Table 96. 21 x 21 mm Functional Contact Assignments

### Package Information and Contact Assignments

| Dell Neme | Before Reset State |                         |  |  |  |

|-----------|--------------------|-------------------------|--|--|--|

| Ball Name | Input/Output       | Value                   |  |  |  |

| EIM_DA14  | Input              | PD (100K)               |  |  |  |

| EIM_DA15  | Input              | PD (100K)               |  |  |  |

| EIM_EB0   | Input              | PD (100K)               |  |  |  |

| EIM_EB1   | Input              | PD (100K)               |  |  |  |

| EIM_EB2   | Input              | PD (100K)               |  |  |  |

| EIM_EB3   | Input              | PD (100K)               |  |  |  |

| EIM_LBA   | Input              | PD (100K)               |  |  |  |

| EIM_RW    | Input              | PD (100K)               |  |  |  |

| EIM_WAIT  | Input              | PD (100K)               |  |  |  |

| GPIO_17   | Output             | Drive state unknown (x) |  |  |  |

| GPIO_19   | Output             | Drive state unknown (x) |  |  |  |

| KEY_COL0  | Output             | Drive state unknown (x) |  |  |  |