# E·XFL

#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Details                            |                                                                                                                     |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Product Status                     | Active                                                                                                              |

| Core Processor                     | ARM® Cortex®-A9                                                                                                     |

| Number of Cores/Bus<br>Width       | 4 Core, 32-Bit                                                                                                      |

| Speed                              | 852MHz                                                                                                              |

| Co-Processors/DSP                  | Multimedia; NEON <sup>™</sup> SIMD                                                                                  |

| RAM Controllers                    | LPDDR2, LVDDR3, DDR3                                                                                                |

| Graphics Acceleration              | Yes                                                                                                                 |

| Display & Interface<br>Controllers | Keypad, LCD                                                                                                         |

| Ethernet                           | 10/100/1000Mbps (1)                                                                                                 |

| SATA                               | SATA 3Gbps (1)                                                                                                      |

| USB                                | USB 2.0 + PHY (4)                                                                                                   |

| Voltage - I/O                      | 1.8V, 2.5V, 2.8V, 3.3V                                                                                              |

| Operating Temperature              | -40°C ~ 125°C (TJ)                                                                                                  |

| Security Features                  | ARM TZ, Boot Security, Cryptography, RTIC, Secure Fusebox, Secure JTAG, Secure Memory, Secure RTC, Tamper Detection |

| Package / Case                     | 624-FBGA, FCBGA                                                                                                     |

| Supplier Device Package            | 624-FCBGA (21x21)                                                                                                   |

| Purchase URL                       | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcimx6q4avt08ae                                             |

|                                    |                                                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- 1-bit or 4-bit transfer mode specifications for SD and SDIO cards up to UHS-I SDR-104 mode (104 MB/s max)

- 1-bit, 4-bit, or 8-bit transfer mode specifications for MMC cards up to 52 MHz in both SDR and DDR modes (104 MB/s max)

- USB:

- One High Speed (HS) USB 2.0 OTG (Up to 480 Mbps), with integrated HS USB PHY

- Three USB 2.0 (480 Mbps) hosts:

- One HS host with integrated High Speed PHY

- Two HS hosts with integrated High Speed Inter-Chip (HS-IC) USB PHY

- Expansion PCI Express port (PCIe) v2.0 one lane

- PCI Express (Gen 2.0) dual mode complex, supporting Root complex operations and Endpoint operations. Uses x1 PHY configuration.

- Miscellaneous IPs and interfaces:

- SSI block capable of supporting audio sample frequencies up to 192 kHz stereo inputs and outputs with I<sup>2</sup>S mode

- ESAI is capable of supporting audio sample frequencies up to 260 kHz in I2S mode with 7.1 multi channel outputs

- Five UARTs, up to 5.0 Mbps each:

- Providing RS232 interface

- Supporting 9-bit RS485 multidrop mode

- One of the five UARTs (UART1) supports 8-wire while the other four support 4-wire. This is due to the SoC IOMUX limitation, because all UART IPs are identical.

- Five eCSPI (Enhanced CSPI)

- Three I2C, supporting 400 kbps

- Gigabit Ethernet Controller (IEEE1588 compliant), 10/100/1000<sup>1</sup> Mbps

- Four Pulse Width Modulators (PWM)

- System JTAG Controller (SJC)

- GPIO with interrupt capabilities

- 8x8 Key Pad Port (KPP)

- Sony Philips Digital Interconnect Format (SPDIF), Rx and Tx

- Two Controller Area Network (FlexCAN), 1 Mbps each

- Two Watchdog timers (WDOG)

- Audio MUX (AUDMUX)

- MLB (MediaLB) provides interface to MOST Networks (150 Mbps) with the option of DTCP cipher accelerator

1. The theoretical maximum performance of 1 Gbps ENET is limited to 470 Mbps (total for Tx and Rx) due to internal bus throughput limitations. The actual measured performance in optimized environment is up to 400 Mbps. For details, see the ERR004512 erratum in the i.MX 6Dual/6Quad errata document (IMX6DQCE).

| Block<br>Mnemonic                                                  | Block Name                           | Subsystem                        | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------------------------------------------|--------------------------------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EPIT-1<br>EPIT-2                                                   | Enhanced Periodic<br>Interrupt Timer | Timer<br>Peripherals             | Each EPIT is a 32-bit "set and forget" timer that starts counting after the EPIT is enabled by software. It is capable of providing precise interrupts at regular intervals with minimal processor intervention. It has a 12-bit prescaler for division of input clock frequency to get the required time setting for the interrupts to occur, and counter value can be programmed on the fly.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ESAI                                                               | Enhanced Serial<br>Audio Interface   | Connectivity<br>Peripherals      | The Enhanced Serial Audio Interface (ESAI) provides a full-duplex serial port for serial communication with a variety of serial devices, including industry-standard codecs, SPDIF transceivers, and other processors. The ESAI consists of independent transmitter and receiver sections, each section with its own clock generator. All serial transfers are synchronized to a clock. Additional synchronization signals are used to delineate the word frames. The normal mode of operation is used to transfer data at a periodic rate, one word per period. The network mode is also intended for periodic transfers; however, it supports up to 32 words (time slots) per period. This mode can be used to build time division multiplexed (TDM) networks. In contrast, the on-demand mode is intended for non-periodic transfers of data and to transfer data serially at high speed when the data becomes available. The ESAI has 12 pins for data and clocking connection to external devices. |

| FlexCAN-1<br>FlexCAN-2                                             | Flexible Controller<br>Area Network  | Connectivity<br>Peripherals      | The CAN protocol was primarily, but not only, designed to be used as a vehicle serial data bus, meeting the specific requirements of this field: real-time processing, reliable operation in the Electromagnetic interference (EMI) environment of a vehicle, cost-effectiveness and required bandwidth. The FlexCAN module is a full implementation of the CAN protocol specification, Version 2.0 B, which supports both standard and extended message frames.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| GPIO-1<br>GPIO-2<br>GPIO-3<br>GPIO-4<br>GPIO-5<br>GPIO-6<br>GPIO-7 | General Purpose I/O<br>Modules       | System<br>Control<br>Peripherals | Used for general purpose input/output to external devices. Each GPIO module supports 32 bits of I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| GPMI                                                               | General Purpose<br>Media Interface   | Connectivity<br>Peripherals      | The GPMI module supports up to 8x NAND devices. 40-bit ECC error correction for NAND Flash controller (GPMI2). The GPMI supports separate DMA channels per NAND device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| GPT                                                                | General Purpose<br>Timer             | Timer<br>Peripherals             | Each GPT is a 32-bit "free-running" or "set and forget" mode timer with programmable prescaler and compare and capture register. A timer counter value can be captured using an external event and can be configured to trigger a capture event on either the leading or trailing edges of an input pulse. When the timer is configured to operate in "set and forget" mode, it is capable of providing precise interrupts at regular intervals with minimal processor intervention. The counter has output compare logic to provide the status and interrupt at comparison. This timer can be configured to run either on an external clock or on an internal clock.                                                                                                                                                                                                                                                                                                                                   |

#### **Modules List**

| Block<br>Mnemonic             | Block Name                                                                             | Subsystem                   | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------------|----------------------------------------------------------------------------------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| uSDHC-1<br>uSDHC-2<br>uSDHC-4 | SD/MMC and SDXC<br>Enhanced<br>Multi-Media Card /<br>Secure Digital Host<br>Controller | Connectivity<br>Peripherals | <ul> <li>i.MX 6Dual/6Quad specific SoC characteristics:</li> <li>All four MMC/SD/SDIO controller IPs are identical and are based on the uSDHC IP. They are:</li> <li>Conforms to the SD Host Controller Standard Specification version 3.0</li> <li>Fully compliant with MMC command/response sets and Physical Layer as defined in the Multimedia Card System Specification, v4.2/4.3/4.4/4.41 including high-capacity (size &gt; 2 GB) cards HC MMC. Hardware reset as specified for eMMC cards is supported at ports #3 and #4 only.</li> <li>Fully compliant with SD command/response sets and Physical Layer as defined in the SD Memory Card Specifications, v3.0 including high-capacity SDHC cards up to 32 GB and SDXC cards up to 2TB.</li> <li>Fully compliant with SDIO command/response sets and interrupt/read-wait mode as defined in the SDIO Card Specification, Part E1, v1.10</li> <li>Fully compliant with SD Card Specification, Part A2, SD Host Controller Standard Specification, v2.00</li> <li>All four ports support:</li> <li>1-bit or 4-bit transfer mode specifications for SD and SDIO cards up to UHS-I SDR104 mode (104 MB/s max)</li> <li>1-bit, 4-bit, or 8-bit transfer mode specifications for MMC cards up to 52 MHz in both SDR and DDR modes (104 MB/s max)</li> <li>However, the SoC-level integration and I/O muxing logic restrict the functionality to the following:</li> <li>Instances #1 and #2 are primarily intended to serve as external slots or interfaces to on-board SDIO devices. These ports are equipped with "Card Detection" and "Write Protection" pads and do support hardware reset.</li> <li>Instances #3 and #4 are primarily intended to serve interfaces to embedded MMC memory or interfaces to on-board SDIO devices. These ports do not have "Card detection" and "Write Protection" pads and do support hardware reset.</li> <li>All ports can work with 1.8 V and 3.3 V cards. There are two completely independent I/O power domains for Ports #1 and #2 in four bit configuration (SD interface). Port #3 is placed in his own independent power domain</li></ul> |

| VDOA                          | VDOA                                                                                   | Multimedia<br>Peripherals   | The Video Data Order Adapter (VDOA) is used to re-order video data from the "tiled" order used by the VPU to the conventional raster-scan order needed by the IPU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| VPU                           | Video Processing<br>Unit                                                               | Multimedia<br>Peripherals   | A high-performing video processing unit (VPU), which covers many<br>SD-level and HD-level video decoders and SD-level encoders as a<br>multi-standard video codec engine as well as several important video<br>processing, such as rotation and mirroring.<br>See the i.MX 6Dual/6Quad reference manual (IMX6DQRM) for complete<br>list of VPU's decoding/encoding capabilities.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| WDOG-1                        | Watchdog                                                                               | Timer<br>Peripherals        | The Watchdog Timer supports two comparison points during each counting period. Each of the comparison points is configurable to evoke an interrupt to the ARM core, and a second point evokes an external event on the WDOG line.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Dennen Ormerka                           | O an althic ma                                                                                           | Maximum (                                 | Maximum Current         |      |  |

|------------------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------|-------------------------|------|--|

| Power Supply                             | Conditions                                                                                               | Power Virus                               | CoreMark                | Unit |  |

| i.MX 6Quad:<br>VDD_ARM_IN + VDD_ARM23_IN | <ul> <li>ARM frequency = 996 MHz</li> <li>ARM LDOs set to 1.3V</li> <li>T<sub>j</sub> = 125°C</li> </ul> |                                           |                         | mA   |  |

|                                          | <ul> <li>ARM frequency = 852 MHz</li> <li>ARM LDOs set to 1.3V</li> <li>T<sub>j</sub> = 125°C</li> </ul> | 3630                                      | 2260                    | mA   |  |

| i.MX 6Dual: VDD_ARM_IN                   | <ul> <li>ARM frequency = 996 MHz</li> <li>ARM LDOs set to 1.3V</li> <li>T<sub>j</sub> = 125°C</li> </ul> | 2350                                      | 1500                    | mA   |  |

|                                          | <ul> <li>ARM frequency = 852 MHz</li> <li>ARM LDOs set to 1.3V</li> <li>T<sub>j</sub> = 125°C</li> </ul> | 2110                                      | 1360                    | mA   |  |

| i.MX 6Dual: or i.MX 6Quad:<br>VDD_SOC_IN | • Running 3DMark<br>• GPU frequency = 600 MHz<br>• SOC LDO set to 1.3V<br>• $T_j = 125^{\circ}C$         | 2500                                      |                         | mA   |  |

| VDD_HIGH_IN                              | —                                                                                                        | 125 <sup>1</sup>                          |                         | mA   |  |

| VDD_SNVS_IN                              | —                                                                                                        | 275 <sup>2</sup>                          |                         | μA   |  |

| USB_OTG_VBUS/<br>USB_H1_VBUS (LDO 3P0)   | _                                                                                                        | 25 <sup>3</sup>                           | 25 <sup>3</sup>         |      |  |

|                                          | Primary Interface (IO) Suppl                                                                             | ies                                       |                         |      |  |

| NVCC_DRAM                                | _                                                                                                        | (see no                                   | te <sup>4</sup> )       |      |  |

| NVCC_ENET                                | N=10                                                                                                     | Use maximum I                             | D equation <sup>5</sup> |      |  |

| NVCC_LCD                                 | N=29                                                                                                     | Use maximum IC                            | D equation <sup>5</sup> |      |  |

| NVCC_GPIO                                | N=24                                                                                                     | Use maximum I                             | D equation <sup>5</sup> |      |  |

| NVCC_CSI                                 | N=20                                                                                                     | Use maximum I                             | D equation <sup>5</sup> |      |  |

| NVCC_EIM0                                | N=19                                                                                                     | Use maximum I                             | D equation <sup>5</sup> |      |  |

| NVCC_EIM1                                | N=14                                                                                                     | Use maximum IC                            | D equation <sup>5</sup> |      |  |

| NVCC_EIM2                                | N=20                                                                                                     | Use maximum IC                            | D equation <sup>5</sup> |      |  |

| NVCC_JTAG                                | N=6                                                                                                      | Use maximum I                             | D equation <sup>5</sup> |      |  |

| NVCC_RGMII                               | N=6                                                                                                      | Use maximum I                             | D equation <sup>5</sup> |      |  |

| NVCC_SD1                                 | N=6                                                                                                      | Use maximum I                             | D equation <sup>5</sup> |      |  |

| NVCC_SD2                                 | N=6                                                                                                      | Use maximum I                             | D equation <sup>5</sup> |      |  |

| NVCC_SD3                                 | N=11                                                                                                     | Use maximum I                             | D equation <sup>5</sup> |      |  |

| NVCC_NANDF                               | N=26                                                                                                     | N=26 Use maximum IO equation <sup>5</sup> |                         |      |  |

| NVCC_MIPI                                | —                                                                                                        | 25.5                                      |                         | mA   |  |

### Table 8. Maximum Supply Currents

| Table 8. Maximum Supply | Currents | (continued) |

|-------------------------|----------|-------------|

|-------------------------|----------|-------------|

| Dower Supply | Conditions | Maximum C                                                                                        | Unit     |      |  |  |  |

|--------------|------------|--------------------------------------------------------------------------------------------------|----------|------|--|--|--|

| Power Supply | Conditions | Power Virus                                                                                      | CoreMark | onit |  |  |  |

| NVCC_LVDS2P5 | _          | NVCC_LVDS2P5 is<br>VDD_HIGH_CAP at<br>level. VDD_HIGH_C<br>of handing the curre<br>NVCC_LVDS2P5. |          |      |  |  |  |

| MISC         |            |                                                                                                  |          |      |  |  |  |

| DRAM_VREF    | _          | 1                                                                                                |          | mA   |  |  |  |

<sup>1</sup> The actual maximum current drawn from VDD\_HIGH\_IN will be as shown plus any additional current drawn from the VDD\_HIGH\_CAP outputs, depending upon actual application configuration (for example, NVCC\_LVDS\_2P5, NVCC\_MIPI, or HDMI, PCIe, and SATA VPH supplies).

- <sup>2</sup> Under normal operating conditions, the maximum current on VDD\_SNVS\_IN is shown Table 8. The maximum VDD\_SNVS\_IN current may be higher depending on specific operating configurations, such as BOOT\_MODE[1:0] not equal to 00, or use of the Tamper feature. During initial power on, VDD\_SNVS\_IN can draw up to 1 mA if the supply is capable of sourcing that current. If less than 1 mA is available, the VDD\_SNVS\_CAP charge time will increase.

- <sup>3</sup> This is the maximum current per active USB physical interface.

- <sup>4</sup> The DRAM power consumption is dependent on several factors such as external signal termination. DRAM power calculators are typically available from memory vendors which take into account factors such as signal termination. See the *i.MX 6Dual/6Quad Power Consumption Measurement Application Note* (AN4509) for examples of DRAM power consumption during specific use case scenarios.

- <sup>5</sup> General equation for estimated, maximum power consumption of an IO power supply: Imax = N x C x V x (0.5 x F)

- Where:

N-Number of IO pins supplied by the power line

C-Equivalent external capacitive load

V—IO voltage

(0.5 xF)—Data change rate. Up to 0.5 of the clock rate (F)

In this equation, Imax is in Amps, C in Farads, V in Volts, and F in Hertz.

# 4.1.6 Low Power Mode Supply Currents

Table 9 shows the current core consumption (not including I/O) of the i.MX 6Dual/6Quad processors in selected low power modes.

| Mode | Test Conditions                                                                                                                                                                                                                                    | Supply              | Typical <sup>1</sup> | Unit |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------------|------|

| WAIT | <ul> <li>WAIT</li> <li>ARM, SoC, and PU LDOs are set to 1.225 V</li> <li>HIGH LDO set to 2.5 V</li> <li>Clocks are gated</li> <li>DDR is in self refresh</li> <li>PLLs are active in bypass (24 MHz)</li> <li>Supply voltages remain ON</li> </ul> | VDD_ARM_IN (1.4 V)  | 6                    | mA   |

|      |                                                                                                                                                                                                                                                    | VDD_SOC_IN (1.4 V)  | 23                   | mA   |

|      |                                                                                                                                                                                                                                                    | VDD_HIGH_IN (3.0 V) | 3.7                  | mA   |

|      |                                                                                                                                                                                                                                                    | Total               | 52                   | mW   |

| Table 9. | Stop Mode | <b>Current and</b> | Power | Consumption |

|----------|-----------|--------------------|-------|-------------|

|----------|-----------|--------------------|-------|-------------|

• When the PCIE interface is not used, the PCIE\_VP, PCIE\_VPH, and PCIE\_VPTX supplies should be grounded. The input and output supplies for rest of the ports (PCIE\_REXT, PCIE\_RX\_N, PCIE\_RX\_P, PCIE\_TX\_N, and PCIE\_TX\_P) can remain unconnected. It is recommended not to turn the PCIE\_VPH supply OFF while the PCIE\_VP supply is ON, as it may lead to excessive power consumption. If boundary scan test is used, PCIE\_VP, PCIE\_VPH, and PCIE\_VPTX must remain powered.

# 4.3 Integrated LDO Voltage Regulator Parameters

Various internal supplies can be powered ON from internal LDO voltage regulators. All the supply pins named \*\_CAP must be connected to external capacitors. The onboard LDOs are intended for internal use only and should not be used to power any external circuitry. See the i.MX 6Dual/6Quad reference manual (IMX6DQRM) for details on the power tree scheme recommended operation.

### NOTE

The \*\_CAP signals should not be powered externally. These signals are intended for internal LDO or LDO bypass operation only.

# 4.3.1 Digital Regulators (LDO\_ARM, LDO\_PU, LDO\_SOC)

There are three digital LDO regulators ("Digital", because of the logic loads that they drive, not because of their construction). The advantages of the regulators are to reduce the input supply variation because of their input supply ripple rejection and their on die trimming. This translates into more voltage for the die producing higher operating frequencies. These regulators have three basic modes.

- Bypass. The regulation FET is switched fully on passing the external voltage, DCDC\_LOW, to the load unaltered. The analog part of the regulator is powered down in this state, removing any loss other than the IR drop through the power grid and FET.

- Power Gate. The regulation FET is switched fully off limiting the current draw from the supply. The analog part of the regulator is powered down here limiting the power consumption.

- Analog regulation mode. The regulation FET is controlled such that the output voltage of the regulator equals the programmed target voltage. The target voltage is fully programmable in 25 mV steps.

Optionally LDO\_SOC/VDD\_SOC\_CAP can be used to power the HDMI, PCIe, and SATA PHY's through external connections.

For additional information, see the i.MX 6Dual/6Quad reference manual (IMX6DQRM).

# 4.3.2 Regulators for Analog Modules

# 4.3.2.1 LDO\_1P1 / NVCC\_PLL\_OUT

The LDO\_1P1 regulator implements a programmable linear-regulator function from VDD\_HIGH\_IN (see Table 6 for minimum and maximum input requirements). Typical Programming Operating Range is 1.0 V to 1.2 V with the nominal default setting as 1.1 V. The LDO\_1P1 supplies the 24 MHz oscillator, PLLs, and USB PHY. A programmable brown-out detector is included in the regulator that can be used by the

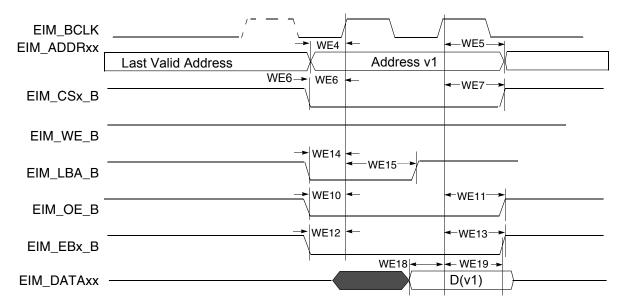

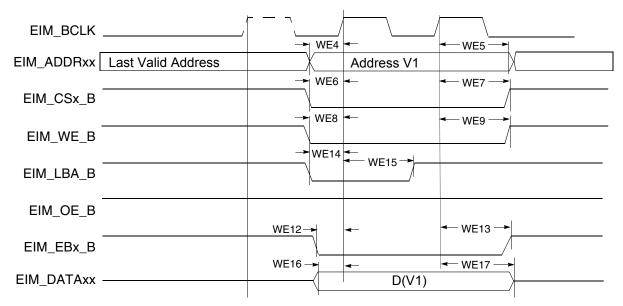

Figure 14 to Figure 17 provide few examples of basic EIM accesses to external memory devices with the timing parameters mentioned previously for specific control parameters settings.

Figure 14. Synchronous Memory Read Access, WSC=1

Figure 15. Synchronous Memory, Write Access, WSC=1, WBEA=0 and WADVN=0

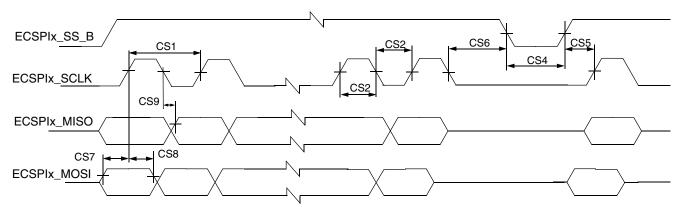

### 4.12.2.2 ECSPI Slave Mode Timing

Figure 36 depicts the timing of ECSPI in slave mode and Table 48 lists the ECSPI slave mode timing characteristics.

Note: ECSPIx\_MISO is always driven (not tri-stated) between actual data transmissions. This limits the ECSPI to be connected between a single master and a single slave.

#### Figure 36. ECSPI Slave Mode Timing Diagram

| ID  | Parameter                                                                                                                         | Symbol              | Min                     | Max      | Unit |

|-----|-----------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------------------|----------|------|

| CS1 | ECSPIx_SCLK Cycle Time-Read<br>• Slow group <sup>1</sup><br>• Fast group <sup>2</sup><br>ECSPIx_SCLK Cycle Time-Write             | t <sub>clk</sub>    | 55<br>40<br>15          | _        | ns   |

| CS2 | ECSPIx_SCLK High or Low Time-Read<br>• Slow group <sup>1</sup><br>• Fast group <sup>2</sup><br>ECSPIx_SCLK High or Low Time-Write | t <sub>SW</sub>     | 26<br>20<br>7           | _        | ns   |

| CS4 | ECSPIx_SSx pulse width                                                                                                            | t <sub>CSLH</sub>   | Half ECSPIx_SCLK period | _        | ns   |

| CS5 | ECSPIx_SSx Lead Time (CS setup time)                                                                                              | t <sub>SCS</sub>    | 5                       | _        | ns   |

| CS6 | ECSPIx_SSx Lag Time (CS hold time)                                                                                                | t <sub>HCS</sub>    | 5                       | —        | ns   |

| CS7 | ECSPIx_MOSI Setup Time                                                                                                            | t <sub>Smosi</sub>  | 4                       | —        | ns   |

| CS8 | ECSPIx_MOSI Hold Time                                                                                                             | t <sub>Hmosi</sub>  | 4                       | —        | ns   |

| CS9 | ECSPIx_MISO Propagation Delay (C <sub>LOAD</sub> = 20 pF)<br>• Slow group <sup>1</sup><br>• Fast group <sup>2</sup>               | t <sub>PDmiso</sub> | 4                       | 25<br>17 | ns   |

### Table 48. ECSPI Slave Mode Timing Parameters

<sup>1</sup> ECSPI slow includes:

ECSPI1/DISP0\_DAT22, ECSPI1/KEY\_COL1, ECSPI1/CSI0\_DAT6, ECSPI2/EIM\_OE, ECSPI2/DISP0\_DAT17, ECSPI2/CSI0\_DAT10, ECSPI3/DISP0\_DAT2

<sup>2</sup> ECSPI fast includes:

ECSPI1/EIM\_D17, ECSPI4/EIM\_D22, ECSPI5/SD2\_DAT0, ECSPI5/SD1\_DAT0

| ID | Parameter <sup>1,2</sup>                                                             | Symbol | Expression <sup>2</sup> | Min         | Мах          | Condition <sup>3</sup> | Unit |  |  |

|----|--------------------------------------------------------------------------------------|--------|-------------------------|-------------|--------------|------------------------|------|--|--|

| 81 | ESAI_TX_CLK rising edge to ESAI_TX_FS out (wr) low <sup>5</sup>                      |        | _                       |             | 22.0<br>12.0 | x ck<br>i ck           | ns   |  |  |

| 82 | ESAI_TX_CLK rising edge to ESAI_TX_FS out (wl) high                                  |        |                         |             | 19.0<br>9.0  | x ck<br>i ck           | ns   |  |  |

| 83 | ESAI_TX_CLK rising edge to ESAI_TX_FS out (wl) low                                   |        |                         |             | 20.0<br>10.0 | x ck<br>i ck           | ns   |  |  |

| 84 | ESAI_TX_CLK rising edge to data out enable from high impedance                       | _      |                         |             | 22.0<br>17.0 | x ck<br>i ck           | ns   |  |  |

| 86 | ESAI_TX_CLK rising edge to data out valid                                            | _      |                         |             | 19.0<br>13.0 | x ck<br>i ck           | ns   |  |  |

| 87 | ESAI_TX_CLK rising edge to data out high impedance <sup>67</sup>                     | _      | _                       |             | 21.0<br>16.0 | x ck<br>i ck           | ns   |  |  |

| 89 | ESAI_TX_FS input (bl, wr) setup time before<br>ESAI_TX_CLK falling edge <sup>5</sup> | _      |                         | 2.0<br>18.0 |              | x ck<br>i ck           | ns   |  |  |

| 90 | ESAI_TX_FS input (wI) setup time before ESAI_TX_CLK falling edge                     | _      | _                       | 2.0<br>18.0 | _            | x ck<br>i ck           | ns   |  |  |

| 91 | ESAI_TX_FS input hold time after ESAI_TX_CLK falling edge                            |        |                         | 4.0<br>5.0  | _            | x ck<br>i ck           | ns   |  |  |

| 95 | ESAI_RX_HF_CLK/ESAI_TX_HF_CLK clock cycle                                            | —      | 2 x T <sub>C</sub>      | 15          | —            | —                      | ns   |  |  |

| 96 | ESAI_TX_HF_CLK input rising edge to ESAI_TX_CLK output                               | _      | —                       |             | 18.0         | _                      | ns   |  |  |

| 97 | ESAI_RX_HF_CLK input rising edge to ESAI_RX_CLK output                               | _      | —                       |             | 18.0         | _                      | ns   |  |  |

| 1  |                                                                                      |        |                         |             |              |                        |      |  |  |

#### Table 49. Enhanced Serial Audio Interface (ESAI) Timing (continued)

<sup>1</sup> i ck = internal clock

x ck = external clock

i ck a = internal clock, asynchronous mode

(asynchronous implies that ESAI\_TX\_CLK and ESAI\_RX\_CLK are two different clocks)

i ck s = internal clock, synchronous mode

(synchronous implies that ESAI\_TX\_CLK and ESAI\_RX\_CLK are the same clock)

<sup>2</sup> bl = bit length

- wl = word length

- wr = word length relative

- <sup>3</sup> ESAI\_TX\_CLK(ESAI\_TX\_CLK pin) = transmit clock

ESAI\_RX\_CLK(ESAI\_RX\_CLK pin) = receive clock

ESAI\_TX\_FS(ESAI\_TX\_FS pin) = transmit frame sync

ESAI\_RX\_FS(ESAI\_RX\_FS pin) = receive frame sync

ESAI\_TX\_HF\_CLK(ESAI\_TX\_HF\_CLK pin) = transmit high frequency clock

ESAI\_RX\_HF\_CLK(ESAI\_RX\_HF\_CLK pin) = receive high frequency clock

<sup>4</sup> For the internal clock, the external clock cycle is defined by lcyc and the ESAI control register.

- <sup>5</sup> The word-relative frame sync signal waveform relative to the clock operates in the same manner as the bit-length frame sync signal waveform, but it spreads from one serial clock before the first bit clock (like the bit length frame sync signal), until the second-to-last bit clock of the first word in the frame.

- <sup>6</sup> Periodically sampled and not 100% tested.

| Symbol             | Parameter                                                                                                                                                                                                                                                                                                                                                              | Condition                                                                                                                                                                           | Min                  | Тур     | Мах                  | Unit |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------|----------------------|------|

| R <sub>T</sub>     | Termination resistance                                                                                                                                                                                                                                                                                                                                                 | —                                                                                                                                                                                   | 45                   | 50      | 55                   | Ω    |

|                    | T                                                                                                                                                                                                                                                                                                                                                                      | MDS drivers DC specifications                                                                                                                                                       |                      |         |                      |      |

| $V_{OFF}$          | Single-ended standby voltage                                                                                                                                                                                                                                                                                                                                           | $RT = 50 \Omega$                                                                                                                                                                    | avddt                | mV      |                      |      |

| V <sub>SWING</sub> | Single-ended output swing voltage                                                                                                                                                                                                                                                                                                                                      | For measurement conditions and<br>definitions, see the first two figures<br>above.<br>Compliance point TP1 as defined in<br>the HDMI specification, version 1.3a,<br>section 4.2.4. | 400                  | _       | 600                  | mV   |

| V <sub>H</sub>     | Single-ended output high voltage<br>For definition, see the second                                                                                                                                                                                                                                                                                                     | If attached sink supports TMDSCLK < or = 165 MHz                                                                                                                                    | avddti               | mds ± ' | 10 mV                | mV   |

|                    | figure above.                                                                                                                                                                                                                                                                                                                                                          | If attached sink supports TMDSCLK > 165 MHz                                                                                                                                         | avddtmds<br>– 200 mV | —       | avddtmds<br>+ 10 mV  | mV   |

| VL                 | For definition, see the second                                                                                                                                                                                                                                                                                                                                         | If attached sink supports TMDSCLK < or = 165 MHz                                                                                                                                    | avddtmds<br>– 600 mV | —       | avddtmds<br>– 400mV  | mV   |

|                    | figure above.                                                                                                                                                                                                                                                                                                                                                          | If attached sink supports TMDSCLK > 165 MHz                                                                                                                                         | avddtmds<br>– 700 mV | —       | avddtmds<br>- 400 mV | mV   |

| R <sub>TERM</sub>  | Differential source termination load<br>(inside HDMI 3D Tx PHY)<br>Although the HDMI 3D Tx PHY<br>includes differential source<br>termination, the user-defined value<br>is set for each single line (for<br>illustration, see the third figure<br>above).<br><b>Note:</b> R <sub>TERM</sub> can also be<br>configured to be open and not<br>present on TMDS channels. |                                                                                                                                                                                     | 50                   |         | 200                  | Ω    |

|                    |                                                                                                                                                                                                                                                                                                                                                                        | Hot plug detect specifications                                                                                                                                                      |                      |         |                      |      |

| HPD <sup>VH</sup>  | Hot plug detect high range                                                                                                                                                                                                                                                                                                                                             | _                                                                                                                                                                                   | 2.0                  |         | 5.3                  | V    |

|                    | Hot plug detect low range                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                     | 0                    | _       | 0.8                  | V    |

| HPD                | Hot plug detect input impedance                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                     | 10                   | —       |                      | kΩ   |

| HPD<br>t           | Hot plug detect time delay                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                     |                      | —       | 100                  | μs   |

#### Table 59. Electrical Characteristics (continued)

# 4.12.8 Switching Characteristics

Table 60 describes switching characteristics for the HDMI 3D Tx PHY. Figure 53 to Figure 57 illustrate various parameters specified in table.

### NOTE

All dynamic parameters related to the TMDS line drivers' performance imply the use of assembly guidelines.

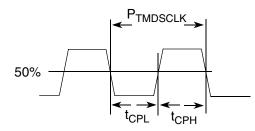

Figure 53. TMDS Clock Signal Definitions

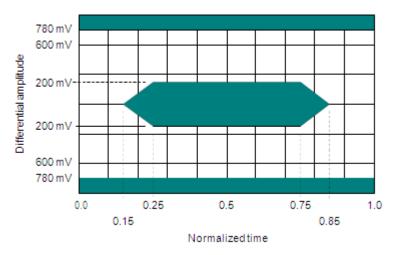

Figure 54. Eye Diagram Mask Definition for HDMI Driver Signal Specification at TP1

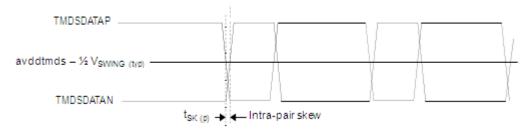

Figure 55. Intra-Pair Skew Definition

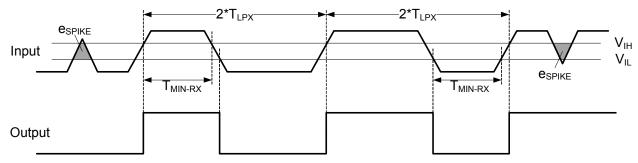

4.12.12.9 Low-Power Receiver Timing

Figure 72. Input Glitch Rejection of Low-Power Receivers

# 4.12.13 HSI Host Controller Timing Parameters

This section describes the timing parameters of the HSI Host Controller which are compliant with High-Speed Synchronous Serial Interface (HSI) Physical Layer specification version 1.01.

### 4.12.13.1 Synchronous Data Flow

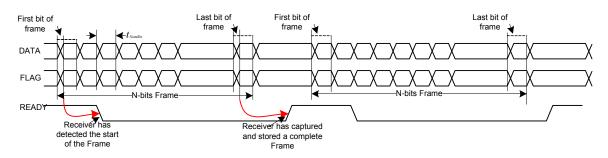

Figure 73. Synchronized Data Flow READY Signal Timing (Frame and Stream Transmission)

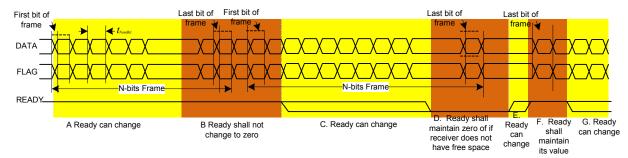

# 4.12.13.2 Pipelined Data Flow

Figure 74. Pipelined Data Flow READY Signal Timing (Frame Transmission Mode)

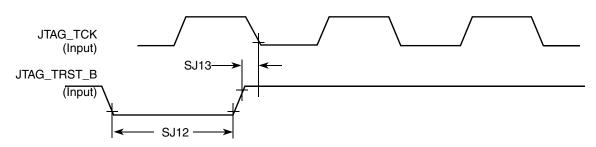

Figure 87. JTAG\_TRST\_B Timing Diagram

| ID   | Parameter <sup>1,2</sup>                                            | All Freq | All Frequencies |        |  |

|------|---------------------------------------------------------------------|----------|-----------------|--------|--|

|      |                                                                     | Min      | Max             | – Unit |  |

| SJ0  | JTAG_TCK frequency of operation 1/(3xT <sub>DC</sub> ) <sup>1</sup> | 0.001    | 22              | MHz    |  |

| SJ1  | JTAG_TCK cycle time in crystal mode                                 | 45       | —               | ns     |  |

| SJ2  | JTAG_TCK clock pulse width measured at $V_M^2$                      | 22.5     | —               | ns     |  |

| SJ3  | JTAG_TCK rise and fall times                                        | —        | 3               | ns     |  |

| SJ4  | Boundary scan input data set-up time                                | 5        | —               | ns     |  |

| SJ5  | Boundary scan input data hold time                                  | 24       | _               | ns     |  |

| SJ6  | JTAG_TCK low to output data valid                                   | —        | 40              | ns     |  |

| SJ7  | JTAG_TCK low to output high impedance                               | —        | 40              | ns     |  |

| SJ8  | JTAG_TMS, JTAG_TDI data set-up time                                 | 5        | —               | ns     |  |

| SJ9  | JTAG_TMS, JTAG_TDI data hold time                                   | 25       | _               | ns     |  |

| SJ10 | JTAG_TCK low to JTAG_TDO data valid                                 | —        | 44              | ns     |  |

| SJ11 | JTAG_TCK low to JTAG_TDO high impedance                             | —        | 44              | ns     |  |

| SJ12 | JTAG_TRST_B assert time                                             | 100      | —               | ns     |  |

| SJ13 | JTAG_TRST_B set-up time to JTAG_TCK low                             | 40       | —               | ns     |  |

| Table | 79. | <b>JTAG</b> | Timing |

|-------|-----|-------------|--------|

| 14010 |     |             |        |

<sup>1</sup>  $T_{DC}$  = target frequency of SJC

<sup>2</sup>  $V_{M}$  = mid-point voltage

# 4.12.19 SPDIF Timing Parameters

The Sony/Philips Digital Interconnect Format (SPDIF) data is sent using the bi-phase marking code. When encoding, the SPDIF data signal is modulated by a clock that is twice the bit rate of the data signal.

Table 80 and Figure 88 and Figure 89 show SPDIF timing parameters for the Sony/Philips Digital Interconnect Format (SPDIF), including the timing of the modulating Rx clock (SPDIF\_SR\_CLK) for SPDIF in Rx mode and the timing of the modulating Tx clock (SPDIF\_ST\_CLK) for SPDIF in Tx mode.

# 4.12.20 SSI Timing Parameters

This section describes the timing parameters of the SSI module. The connectivity of the serial synchronous interfaces are summarized in Table 81.

| Port          | Signal Nomenclature | Type and Access                            |

|---------------|---------------------|--------------------------------------------|

| AUDMUX port 1 | SSI 1               | Internal                                   |

| AUDMUX port 2 | SSI 2               | Internal                                   |

| AUDMUX port 3 | AUD3                | External – AUD3 I/O                        |

| AUDMUX port 4 | AUD4                | External – EIM or CSPI1 I/O through IOMUXC |

| AUDMUX port 5 | AUD5                | External – EIM or SD1 I/O through IOMUXC   |

| AUDMUX port 6 | AUD6                | External – EIM or DISP2 through IOMUXC     |

| AUDMUX port 7 | SSI 3               | Internal                                   |

Table 81. AUDMUX Port Allocation

### NOTE

The terms WL and BL used in the timing diagrams and tables refer to Word Length (WL) and Bit Length (BL).

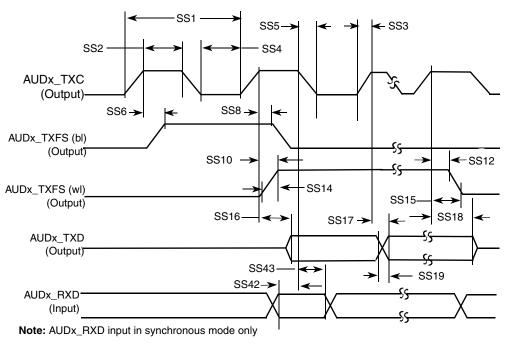

### 4.12.20.1 SSI Transmitter Timing with Internal Clock

Figure 90 depicts the SSI transmitter internal clock timing and Table 82 lists the timing parameters for the SSI transmitter internal clock.

Figure 90. SSI Transmitter Internal Clock Timing Diagram

| Supply Rail Name | Ball(s) Position(s)                              | Remark                                                                                                                              |

|------------------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| VDDHIGH_CAP      | H10, J10                                         | Secondary supply for the 2.5 V domain<br>(internal regulator output—requires<br>capacitor if internal regulator is used)            |

| VDDHIGH_IN       | H9, J9                                           | Primary supply for the 2.5 V regulator                                                                                              |

| VDDPU_CAP        | H17, J17, K17, L17, M17, N17, P17                | Secondary supply for the VPU and<br>GPU (internal regulator output—<br>requires capacitor if internal regulator<br>is used)         |

| VDDSOC_CAP       | R10, T10, T13, T14, U10, U13, U14                | Secondary supply for the SoC and PU<br>(internal regulator output—requires<br>capacitor if internal regulator is used)              |

| VDDSOC_IN        | H16, J16, K16, L16, M16, N16, P16, R16, T16, U16 | Primary supply for the SoC and PU regulators                                                                                        |

| VDDUSB_CAP       | F9                                               | Secondary supply for the 3 V domain<br>(internal regulator output—requires<br>capacitor if internal regulator is used)              |

| ZQPAD            | AE17                                             | Connect ZQPAD to an external $240\Omega$ 1% resistor to GND. This is a reference used during DRAM output buffer driver calibration. |

#### Table 95. 21 x 21 mm Supplies Contact Assignment (continued)

### 6.2.3 21 x 21 mm Functional Contact Assignments

Table 96 displays an alpha-sorted list of the signal assignments including power rails. The table also includes out of reset pad state.

|            |      |              |           | Out of Reset Condition <sup>1</sup> |                                   |              |                    |  |

|------------|------|--------------|-----------|-------------------------------------|-----------------------------------|--------------|--------------------|--|

| Ball Name  | Ball | Power Group  | Ball Type | Default<br>Mode<br>(Reset<br>Mode)  | Default Function<br>(Signal Name) | Input/Output | Value <sup>2</sup> |  |

| BOOT_MODE0 | C12  | VDD_SNVS_IN  | GPIO      | ALT0                                | SRC_BOOT_MODE0                    | Input        | PD (100K)          |  |

| BOOT_MODE1 | F12  | VDD_SNVS_IN  | GPIO      | ALT0                                | SRC_BOOT_MODE1                    | Input        | PD (100K)          |  |

| CLK1_N     | C7   | VDD_HIGH_CAP | —         | —                                   | CLK1_N                            | —            | —                  |  |

| CLK1_P     | D7   | VDD_HIGH_CAP | —         | —                                   | CLK1_P                            | —            | —                  |  |

| CLK2_N     | C5   | VDD_HIGH_CAP | —         |                                     | CLK2_N                            | —            | —                  |  |

| CLK2_P     | D5   | VDD_HIGH_CAP | —         | —                                   | CLK2_P                            | —            | —                  |  |

| CSI_CLK0M  | F4   | NVCC_MIPI    | —         | —                                   | CSI_CLK_N                         | —            | —                  |  |

| CSI_CLK0P  | F3   | NVCC_MIPI    | —         | —                                   | CSI_CLK_P                         | —            | —                  |  |

| CSI_D0M    | E4   | NVCC_MIPI    | —         | —                                   | CSI_DATA0_N                       | —            | —                  |  |

| CSI_D0P    | E3   | NVCC_MIPI    | —         | —                                   | CSI_DATA0_P                       | —            | —                  |  |

| CSI_D1M    | D1   | NVCC_MIPI    | _         |                                     | CSI_DATA1_N                       | _            | —                  |  |

Table 96. 21 x 21 mm Functional Contact Assignments

|                |                  |           |           |                                    | Out of Reset Condition <sup>1</sup> |              |                    |  |  |

|----------------|------------------|-----------|-----------|------------------------------------|-------------------------------------|--------------|--------------------|--|--|

| Ball Name      | Ball Power Group |           | Ball Type | Default<br>Mode<br>(Reset<br>Mode) | Default Function<br>(Signal Name)   | Input/Output | Value <sup>2</sup> |  |  |

| DRAM_DQM7      | Y21              | NVCC_DRAM | DDR       | ALT0                               | DRAM_DQM7                           | Output       | 0                  |  |  |

| DRAM_RAS       | AB15             | NVCC_DRAM | DDR       | ALT0                               | DRAM_RAS_B                          | Output       | 0                  |  |  |

| DRAM_RESET     | Y6               | NVCC_DRAM | DDR       | ALT0                               | DRAM_RESET                          | Output       | 0                  |  |  |

| DRAM_SDBA0     | AC15             | NVCC_DRAM | DDR       | ALT0                               | DRAM_SDBA0                          | Output       | 0                  |  |  |

| DRAM_SDBA1     | Y15              | NVCC_DRAM | DDR       | ALT0                               | DRAM_SDBA1                          | Output       | 0                  |  |  |

| DRAM_SDBA2     | AB12             | NVCC_DRAM | DDR       | ALT0                               | DRAM_SDBA2                          | Output       | 0                  |  |  |

| DRAM_SDCKE0    | Y11              | NVCC_DRAM | DDR       | ALT0                               | DRAM_SDCKE0                         | Output       | 0                  |  |  |

| DRAM_SDCKE1    | AA11             | NVCC_DRAM | DDR       | ALT0                               | DRAM_SDCKE1                         | Output       | 0                  |  |  |

| DRAM_SDCLK_0   | AD15             | NVCC_DRAM | DDRCLK    | ALT0                               | DRAM_SDCLK0_P                       | Output       | 0                  |  |  |

| DRAM_SDCLK_0_B | AE15             | NVCC_DRAM | DDRCLK    | —                                  | DRAM_SDCLK0_N                       | —            | _                  |  |  |

| DRAM_SDCLK_1   | AD14             | NVCC_DRAM | DDRCLK    | ALT0                               | DRAM_SDCLK1_P                       | Output       | 0                  |  |  |

| DRAM_SDCLK_1_B | AE14             | NVCC_DRAM | DDRCLK    | _                                  | DRAM_SDCLK1_N                       | —            | _                  |  |  |

| DRAM_SDODT0    | AC16             | NVCC_DRAM | DDR       | ALT0                               | DRAM_ODT0                           | Output       | 0                  |  |  |

| DRAM_SDODT1    | AB17             | NVCC_DRAM | DDR       | ALT0                               | DRAM_ODT1                           | Output       | 0                  |  |  |

| DRAM_SDQS0     | AE3              | NVCC_DRAM | DDRCLK    | ALT0                               | DRAM_SDQS0_P                        | Input        | Hi-Z               |  |  |

| DRAM_SDQS0_B   | AD3              | NVCC_DRAM | DDRCLK    | —                                  | DRAM_SDQS0_N                        |              | _                  |  |  |

| DRAM_SDQS1     | AD6              | NVCC_DRAM | DDRCLK    | ALT0                               | DRAM_SDQS1_P                        | Input        | Hi-Z               |  |  |

| DRAM_SDQS1_B   | AE6              | NVCC_DRAM | DDRCLK    | —                                  | DRAM_SDQS1_N                        |              | _                  |  |  |

| DRAM_SDQS2     | AD8              | NVCC_DRAM | DDRCLK    | ALT0                               | DRAM_SDQS2_P                        | Input        | Hi-Z               |  |  |

| DRAM_SDQS2_B   | AE8              | NVCC_DRAM | DDRCLK    | —                                  | DRAM_SDQS2_N                        | —            | _                  |  |  |

| DRAM_SDQS3     | AC10             | NVCC_DRAM | DDRCLK    | ALT0                               | DRAM_SDQS3_P                        | Input        | Hi-Z               |  |  |

| DRAM_SDQS3_B   | AB10             | NVCC_DRAM | DDRCLK    | —                                  | DRAM_SDQS3_N                        | —            | _                  |  |  |

| DRAM_SDQS4     | AD18             | NVCC_DRAM | DDRCLK    | ALT0                               | DRAM_SDQS4_P                        | Input        | Hi-Z               |  |  |

| DRAM_SDQS4_B   | AE18             | NVCC_DRAM | DDRCLK    | —                                  | DRAM_SDQS4_N                        | —            | _                  |  |  |

| DRAM_SDQS5     | AD20             | NVCC_DRAM | DDRCLK    | ALT0                               | DRAM_SDQS5_P                        | Input        | Hi-Z               |  |  |

| DRAM_SDQS5_B   | AE20             | NVCC_DRAM | DDRCLK    | —                                  | DRAM_SDQS5_N                        | —            | _                  |  |  |

| DRAM_SDQS6     | AD23             | NVCC_DRAM | DDRCLK    | ALT0                               | DRAM_SDQS6_P                        | Input        | Hi-Z               |  |  |

| DRAM_SDQS6_B   | AE23             | NVCC_DRAM | DDRCLK    | _                                  | DRAM_SDQS6_N                        |              | _                  |  |  |

| DRAM_SDQS7     | AA25             | NVCC_DRAM | DDRCLK    | ALT0                               | DRAM_SDQS7_P                        | Input        | Hi-Z               |  |  |

| DRAM_SDQS7_B   | AA24             | NVCC_DRAM | DDRCLK    | _                                  | DRAM_SDQS7_N                        |              |                    |  |  |

| DRAM_SDWE      | AB16             | NVCC_DRAM | DDR       | ALT0                               | DRAM_SDWE_B                         | Output       | 0                  |  |  |

| DSI_CLK0M      | H3               | NVCC_MIPI |           | _                                  | DSI_CLK_N                           |              |                    |  |  |

| DSI_CLK0P      | H4               | NVCC_MIPI |           | _                                  | DSI_CLK_P                           |              | _                  |  |  |

| DSI_D0M        | G2               | NVCC_MIPI |           | _                                  | DSI_DATA0_N                         |              |                    |  |  |

| DSI_D0P        | G1               | NVCC_MIPI |           | _                                  | DSI_DATA0_P                         |              | _                  |  |  |

| DSI_D1M        | H2               | NVCC_MIPI |           | —                                  | DSI_DATA1_N                         |              | _                  |  |  |

Table 96. 21 x 21 mm Functional Contact Assignments (continued)

|             |      |               |           | Out of Reset Condition <sup>1</sup> |                                   |              |                    |  |

|-------------|------|---------------|-----------|-------------------------------------|-----------------------------------|--------------|--------------------|--|

| Ball Name   | Ball | Power Group   | Ball Type | Default<br>Mode<br>(Reset<br>Mode)  | Default Function<br>(Signal Name) | Input/Output | Value <sup>2</sup> |  |

| GPIO_4      | R6   | NVCC_GPIO     | GPIO      | ALT5                                | GPIO1_IO04                        | Input        | PU (100K)          |  |

| GPIO_5      | R4   | NVCC_GPIO     | GPIO      | ALT5                                | GPIO1_IO05                        | Input        | PU (100K)          |  |

| GPIO_6      | Т3   | NVCC_GPIO     | GPIO      | ALT5                                | GPIO1_IO06                        | Input        | PU (100K)          |  |

| GPIO_7      | R3   | NVCC_GPIO     | GPIO      | ALT5                                | GPIO1_IO07                        | Input        | PU (100K)          |  |

| GPIO_8      | R5   | NVCC_GPIO     | GPIO      | ALT5                                | GPIO1_IO08                        | Input        | PU (100K)          |  |

| GPIO_9      | T2   | NVCC_GPIO     | GPIO      | ALT5                                | GPIO1_IO09                        | Input        | PU (100K)          |  |