Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | e200z4                                                                   |

| Core Size                  | 32-Bit Dual-Core                                                         |

| Speed                      | 120MHz                                                                   |

| Connectivity               | CANbus, FlexRay, LINbus, SPI, UART/USART                                 |

| Peripherals                | DMA, POR, PWM, WDT                                                       |

| Number of I/O              | -                                                                        |

| Program Memory Size        | 1MB (1M x 8)                                                             |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 128K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                |

| Data Converters            | A/D 32x12b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 144-LQFP                                                                 |

| Supplier Device Package    | 144-LQFP (20x20)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5643lff0mlq1r |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.5.2 Crossbar switch (XBAR)

The XBAR multi-port crossbar switch supports simultaneous connections between four master ports and three slave ports. The crossbar supports a 32-bit address bus width and a 64-bit data bus width.

The crossbar allows four concurrent transactions to occur from any master port to any slave port, although one of those transfers must be an instruction fetch from internal flash memory. If a slave port is simultaneously requested by more than one master port, arbitration logic selects the higher priority master and grants it ownership of the slave port. All other masters requesting that slave port are stalled until the higher priority master completes its transactions.

The crossbar provides the following features:

- 4 masters and 3 slaves supported per each replicated crossbar

- Masters allocation for each crossbar: e200z4d core with two independent bus interface units (BIU) for I and D access (2 masters), one eDMA, one FlexRay

- Slaves allocation for each crossbar: a redundant flash-memory controller with 2 slave ports to guarantee maximum flexibility to handle Instruction and Data array, one redundant SRAM controller with 1 slave port each and 1 redundant peripheral bus bridge

- 32-bit address bus and 64-bit data bus

- Programmable arbitration priority

- Requesting masters can be treated with equal priority and are granted access to a slave port in round-robin method, based upon the ID of the last master to be granted access or a priority order can be assigned by software at application run time

- Temporary dynamic priority elevation of masters

The XBAR is replicated for each processing channel.

### 1.5.3 Memory Protection Unit (MPU)

The Memory Protection Unit splits the physical memory into 16 different regions. Each master (eDMA, FlexRay, CPU) can be assigned different access rights to each region.

- 16-region MPU with concurrent checks against each master access

- 32-byte granularity for protected address region

The memory protection unit is replicated for each processing channel.

# 1.5.4 Enhanced Direct Memory Access (eDMA)

The enhanced direct memory access (eDMA) controller is a second-generation module capable of performing complex data movements via 16 programmable channels, with minimal intervention from the host processor. The hardware microarchitecture includes a DMA engine which performs source and destination address calculations, and the actual data movement operations, along with an SRAM-based memory containing the transfer control descriptors (TCD) for the channels. This implementation is used to minimize the overall block size.

The eDMA module provides the following features:

- 16 channels supporting 8-, 16-, and 32-bit value single or block transfers

- Support variable sized queues and circular buffered queue

- Source and destination address registers independently configured to post-increment or stay constant

- Support major and minor loop offset

- Support minor and major loop done signals

- DMA task initiated either by hardware requestor or by software

- Each DMA task can optionally generate an interrupt at completion and retirement of the task

- Signal to indicate closure of last minor loop

#### MPC5643L Microcontroller Data Sheet, Rev. 9

#### Introduction

- EXTEST

- SAMPLE

- SAMPLE/PRELOAD

- 3 test data registers: a bypass register, a boundary scan register, and a device identification register. The size of the boundary scan register is parameterized to support a variety of boundary scan chain lengths.

- TAP controller state machine that controls the operation of the data registers, instruction register and associated circuitry

### 1.5.40 Voltage regulator / Power Management Unit (PMU)

The on-chip voltage regulator module provides the following features:

- Single external rail required

- Single high supply required: nominal 3.3 V both for packaged and Known Good Die option

- Packaged option requires external ballast transistor due to reduced dissipation capacity at high temperature but can use embedded transistor if power dissipation is maintained within package dissipation capacity (lower frequency of operation)

- Known Good Die option uses embedded ballast transistor as dissipation capacity is increased to reduce system cost

- All I/Os are at same voltage as external supply (3.3 V nominal)

- Duplicated Low-Voltage Detectors (LVD) to guarantee proper operation at all stages (reset, configuration, normal operation) and, to maximize safety coverage, one LVD can be tested while the other operates (on-line self-testing feature)

# 1.5.41 Built-In Self-Test (BIST) capability

This device includes the following protection against latent faults:

- Boot-time Memory Built-In Self-Test (MBIST)

- Boot-time scan-based Logic Built-In Self-Test (LBIST)

- Run-time ADC Built-In Self-Test (BIST)

- Run-time Built-In Self Test of LVDs

#### Package pinouts and signal descriptions

| Pin # | Port/function            | Peripheral | Output function | Input function |  |  |  |

|-------|--------------------------|------------|-----------------|----------------|--|--|--|

| 14    | A[5]                     | SIUL       | GPIO[5]         | GPIO[5]        |  |  |  |

|       | -                        | DSPI_1     | CS0             | CS0            |  |  |  |

|       | -                        | eTimer_1   | ETC[5]          | ETC[5]         |  |  |  |

|       | -                        | DSPI_0     | CS7             | —              |  |  |  |

|       | -                        | SIUL       | —               | EIRQ[5]        |  |  |  |

| 15    | C[7]                     | SIUL       | GPIO[39]        | GPIO[39]       |  |  |  |

|       | -                        | FlexPWM_0  | A[1]            | A[1]           |  |  |  |

|       | -                        | SSCM       | DEBUG[7]        | _              |  |  |  |

|       | -                        | DSPI_0     | —               | SIN            |  |  |  |

| 16    | V <sub>DD_HV_REG_0</sub> |            |                 |                |  |  |  |

| 17    | V <sub>SS_LV_COR</sub>   |            | _               |                |  |  |  |

| 18    | V <sub>DD_LV_COR</sub>   | _          |                 |                |  |  |  |

| 19    | F[7]                     | SIUL       | GPIO[87]        | GPIO[87]       |  |  |  |

|       | -                        | NPC        | МСКО            | _              |  |  |  |

| 20    | F[8]                     | SIUL       | GPIO[88]        | GPIO[88]       |  |  |  |

|       | -                        | NPC        | MSEO[1]         | —              |  |  |  |

| 21    | V <sub>DD_HV_IO</sub>    |            | —               |                |  |  |  |

| 22    | V <sub>SS_HV_IO</sub>    |            |                 |                |  |  |  |

| 23    | F[9]                     | SIUL       | GPIO[89]        | GPIO[89]       |  |  |  |

|       | -                        | NPC        | MSEO[0]         | —              |  |  |  |

| 24    | F[10]                    | SIUL       | GPIO[90]        | GPIO[90]       |  |  |  |

|       | -                        | NPC        | EVTO            | _              |  |  |  |

| 25    | F[11]                    | SIUL       | GPIO[91]        | GPIO[91]       |  |  |  |

|       | -                        | NPC        | —               | EVTI           |  |  |  |

| 26    | D[9]                     | SIUL       | GPIO[57]        | GPIO[57]       |  |  |  |

|       | -                        | FlexPWM_0  | X[0]            | X[0]           |  |  |  |

|       | -                        | LINFlexD_1 | TXD             |                |  |  |  |

| 27    | V <sub>DD_HV_OSC</sub>   |            | <u> </u>        |                |  |  |  |

| 28    | V <sub>SS_HV_OSC</sub>   |            | —               |                |  |  |  |

| 29    | XTAL                     |            | —               |                |  |  |  |

| 30    | EXTAL                    |            | —               |                |  |  |  |

| 31    | RESET                    |            | _               |                |  |  |  |

Table 3. 144 LQFP pin function summary (continued)

| Pin #                        | Port/function                | Peripheral | Output function | Input function |  |  |

|------------------------------|------------------------------|------------|-----------------|----------------|--|--|

| 32                           | D[8]                         | SIUL       | GPIO[56]        | GPIO[56]       |  |  |

|                              |                              | DSPI_1     | CS2             | —              |  |  |

|                              |                              | eTimer_1   | ETC[4]          | ETC[4]         |  |  |

|                              |                              | DSPI_0     | CS5             | _              |  |  |

|                              |                              | FlexPWM_0  | —               | FAULT[3]       |  |  |

| 33                           | D[5]                         | SIUL       | GPIO[53]        | GPIO[53]       |  |  |

|                              |                              | DSPI_0     | CS3             | _              |  |  |

|                              |                              | FlexPWM_0  | —               | FAULT[2]       |  |  |

| 34                           | D[6]                         | SIUL       | GPIO[54]        | GPIO[54]       |  |  |

|                              |                              | DSPI_0     | CS2             | _              |  |  |

| 32<br>33<br>33<br>34<br>35 \ |                              | FlexPWM_0  | X[3]            | X[3]           |  |  |

|                              |                              | FlexPWM_0  |                 |                |  |  |

| 35                           | V <sub>SS_LV_PLL0_PLL1</sub> |            | —               |                |  |  |

| 36                           | V <sub>DD_LV_PLL0_PLL1</sub> |            | —               |                |  |  |

| 37                           | D[7]                         | SIUL       | GPIO[55]        | GPIO[55]       |  |  |

|                              |                              | DSPI_1     | CS3             | _              |  |  |

|                              |                              | DSPI_0     | CS4             | _              |  |  |

|                              |                              | SWG        | analog output   | —              |  |  |

| 38                           | FCCU_F[0]                    | FCCU       | F[0]            | F[0]           |  |  |

| 39                           | V <sub>DD_LV_COR</sub>       |            | _               |                |  |  |

| 40                           | V <sub>SS_LV_COR</sub>       |            | _               |                |  |  |

| 41                           | C[1]                         | SIUL       | —               | GPIO[33]       |  |  |

|                              |                              | ADC_0      | —               | AN[2]          |  |  |

| 42                           | E[4]                         | SIUL       | —               | GPIO[68]       |  |  |

|                              |                              | ADC_0      | —               | AN[7]          |  |  |

| 43                           | B[7]                         | SIUL       | —               | GPIO[23]       |  |  |

|                              |                              | LINFlexD_0 | —               | RXD            |  |  |

|                              |                              | ADC_0      | —               | AN[0]          |  |  |

| 44                           | E[5]                         | SIUL       | —               | GPIO[69]       |  |  |

|                              |                              | ADC_0      | —               | AN[8]          |  |  |

| 45                           | C[2]                         | SIUL       | —               | GPIO[34]       |  |  |

|                              |                              | ADC_0      | —               | AN[3]          |  |  |

| 46                           | E[6]                         | SIUL       | —               | GPIO[70]       |  |  |

|                              |                              | ADC_0      | —               | AN[4]          |  |  |

| Table 3. 144 LQFP pin fun | ction summary (continued) |

|---------------------------|---------------------------|

#### Package pinouts and signal descriptions

| Pin # | Port/function                | Peripheral                                                                                                                                                                                                                                                                                                                                                                                                        | Output function | Input function |  |

|-------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------|--|

| C16   | A[4]                         | SIUL                                                                                                                                                                                                                                                                                                                                                                                                              | GPIO[4]         | GPIO[4]        |  |

|       |                              | eTimer_1                                                                                                                                                                                                                                                                                                                                                                                                          | ETC[0]          | ETC[0]         |  |

|       |                              | DSPI_2                                                                                                                                                                                                                                                                                                                                                                                                            | CS1             |                |  |

|       |                              | eTimer_0                                                                                                                                                                                                                                                                                                                                                                                                          | ETC[4]          | ETC[4]         |  |

|       |                              | MC_RGM                                                                                                                                                                                                                                                                                                                                                                                                            | —               | FAB            |  |

|       |                              | SIUL                                                                                                                                                                                                                                                                                                                                                                                                              | _               | EIRQ[4]        |  |

| C17   | F[12]                        | SIUL                                                                                                                                                                                                                                                                                                                                                                                                              | GPIO[92]        | GPIO[92]       |  |

|       |                              | eTimer_1                                                                                                                                                                                                                                                                                                                                                                                                          | ETC[3]          | ETC[3]         |  |

|       |                              | SIUL                                                                                                                                                                                                                                                                                                                                                                                                              | —               | EIRQ[30]       |  |

| D1    | F[5]                         | NPC                                                                                                                                                                                                                                                                                                                                                                                                               |                 | GPIO[85]       |  |

|       |                              | SIUL         GPIO[4]         GPIO[4]           eTimer_1         ETC[0]         ETC[0]           DSPI_2         CS1         —           eTimer_0         ETC[4]         ETC[4]           MC_RGM         —         FAB           SIUL         GPI0[92]         GPI0[92]           eTimer_1         ETC[3]         ETC[3]           SIUL         —         EIRQ[30]           SIUL         GPI0[85]         GPI0[85] |                 |                |  |

| D2    | F[4]                         | SIUL                                                                                                                                                                                                                                                                                                                                                                                                              |                 |                |  |

|       |                              | NPC                                                                                                                                                                                                                                                                                                                                                                                                               | MDO[3]          | _              |  |

| D3    | A[15]                        | SIUL                                                                                                                                                                                                                                                                                                                                                                                                              | GPIO[15]        | GPIO[15]       |  |

|       |                              | eTimer_1                                                                                                                                                                                                                                                                                                                                                                                                          | ETC[5]          | ETC[5]         |  |

|       |                              | FlexCAN_1                                                                                                                                                                                                                                                                                                                                                                                                         | _               | RXD            |  |

|       |                              | FlexCAN_0                                                                                                                                                                                                                                                                                                                                                                                                         | —               | RXD            |  |

|       |                              | SIUL                                                                                                                                                                                                                                                                                                                                                                                                              | _               | EIRQ[14]       |  |

| D4    | C[6]                         | SIUL                                                                                                                                                                                                                                                                                                                                                                                                              | GPIO[38]        | GPIO[38]       |  |

|       |                              | DSPI_0                                                                                                                                                                                                                                                                                                                                                                                                            | SOUT            | _              |  |

|       |                              | FlexPWM_0                                                                                                                                                                                                                                                                                                                                                                                                         | B[1]            | B[1]           |  |

|       |                              | SSCM                                                                                                                                                                                                                                                                                                                                                                                                              | DEBUG[6]        | _              |  |

|       |                              | SIUL                                                                                                                                                                                                                                                                                                                                                                                                              | —               | EIRQ[24]       |  |

| D5    | V <sub>SS_LV_CORE_RING</sub> |                                                                                                                                                                                                                                                                                                                                                                                                                   |                 |                |  |

| D6    | V <sub>DD_LV_CORE_RING</sub> |                                                                                                                                                                                                                                                                                                                                                                                                                   | _               |                |  |

| D7    | F[0]                         | SIUL                                                                                                                                                                                                                                                                                                                                                                                                              | GPIO[80]        | GPIO[80]       |  |

|       |                              | FlexPWM_0                                                                                                                                                                                                                                                                                                                                                                                                         | A[1]            | A[1]           |  |

|       |                              | eTimer_0                                                                                                                                                                                                                                                                                                                                                                                                          | —               | ETC[2]         |  |

|       |                              | SIUL                                                                                                                                                                                                                                                                                                                                                                                                              | -               | EIRQ[28]       |  |

| D8    | V <sub>DD_HV_IO_RING</sub>   |                                                                                                                                                                                                                                                                                                                                                                                                                   | _               |                |  |

| D9    | V <sub>SS_HV_IO_RING</sub>   |                                                                                                                                                                                                                                                                                                                                                                                                                   | —               |                |  |

| D10   | Not connected                |                                                                                                                                                                                                                                                                                                                                                                                                                   | _               |                |  |

Table 4. 257 MAPBGA pin function summary (continued)

|                        | Supply                                                                                                                                                                                | Pin #      |                     |  |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------------|--|

| Symbol                 | Description                                                                                                                                                                           | 144<br>pkg | 257<br>pkg          |  |

| V <sub>SS_LV_COR</sub> | $\label{eq:VSS_LV_COR} \begin{tabular}{lllllllllllllllllllllllllllllllllll$                                                                                                           | 17         | VSS_HV <sup>2</sup> |  |

| V <sub>DD_LV_COR</sub> | $\label{eq:VDD_LV_COR} \begin{tabular}{lllllllllllllllllllllllllllllllllll$                                                                                                           | 18         | VDD_LV <sup>1</sup> |  |

| V <sub>SS</sub> 1V2    | VSS_LV_PLL0_PLL1 / 1.2 V Decoupling pins for on-chip FMPLL modules. Decoupling capacitor must be connected between this pin and $V_{DD_LV_PLL}$ .                                     | 35         | N4                  |  |

| V <sub>DD</sub> 1V2    | VDD_LV_PLL0_PLL1<br>Decoupling pins for on-chip FMPLL modules. Decoupling capacitor must be connected between this pin and $V_{SS_LV_PLL}$ .                                          | 36         | P4                  |  |

| V <sub>DD_LV_COR</sub> | $\label{eq:VDD_LV_COR} \begin{tabular}{lllllllllllllllllllllllllllllllllll$                                                                                                           | 39         | VDD_LV <sup>1</sup> |  |

| V <sub>SS_LV_COR</sub> | $\label{eq:VSS_LV_COR} \begin{tabular}{lllllllllllllllllllllllllllllllllll$                                                                                                           | 40         | VSS_LV <sup>2</sup> |  |

| V <sub>DD_LV_COR</sub> | VDD_LV_COR<br>Decoupling pins for core logic and Regulator feedback. Decoupling<br>capacitor must be connected between this pins and V <sub>SS_LV_REGCOR</sub> .                      | 70         | VDD_LV <sup>1</sup> |  |

| V <sub>SS_LV_COR</sub> | VSS_LV_REGCOR0<br>Decoupling pins for core logic and Regulator feedback. Decoupling<br>capacitor must be connected between this pins and V <sub>DD_LV_REGCOR</sub> .                  | 71         | VSS_LV <sup>2</sup> |  |

| V <sub>DD_LV_COR</sub> | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$                                                                                                                                 | 93         | VDD_LV <sup>1</sup> |  |

| V <sub>SS_LV_COR</sub> | VSS_LV_COR<br>/ 1.2 V Decoupling pins for core logic. Decoupling capacitor must be<br>connected between these pins and the nearest V <sub>DD_LV_COR pin</sub> .                       | 94         | VSS_LV <sup>2</sup> |  |

| V <sub>DD</sub> 1V2    | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$                                                                                                                                 | 131        | VDD_LV <sup>1</sup> |  |

| V <sub>SS</sub> 1V2    | $\label{eq:VSS_LV_COR} \begin{tabular}{lllllllllllllllllllllllllllllllllll$                                                                                                           | 132        | VSS_LV <sup>2</sup> |  |

| V <sub>DD</sub> 1V2    | $\label{eq:VD_LV_COR} VDD_LV_COR / \\ Decoupling pins for core logic. Decoupling capacitor must be connected \\ between these pins and the nearest V_{DD_LV_COR} pin. \\ \end{array}$ | 135        | VDD_LV <sup>1</sup> |  |

| V <sub>SS</sub> 1V2    | VSS_LV_COR /<br>Decoupling pins for core logic. Decoupling capacitor must be connected<br>between these pins and the nearest V <sub>DD_LV_COR</sub> pin.                              | 137        | VSS_LV <sup>2</sup> |  |

| Table 5. Supply | pins | (continued) |

|-----------------|------|-------------|

|-----------------|------|-------------|

<sup>1</sup> VDD\_LV balls are tied together on the 257 MAPBGA substrate.

| MPC5643L        |

|-----------------|

| Microcontroller |

| Data            |

| Sheet,          |

| Rev. 9          |

### Table 7. Pin muxing (continued)

| Port |        |            | Alternate          | Output  | Input     | Input mux             | Weak pull              | Pad s | peed <sup>1</sup> |            | Pin # |     |  |  |  |  |  |  |  |  |

|------|--------|------------|--------------------|---------|-----------|-----------------------|------------------------|-------|-------------------|------------|-------|-----|--|--|--|--|--|--|--|--|

| name | PCR    | Peripheral | output<br>function | mux sel | functions | select                | config during<br>reset |       | 144<br>pkg        | 257<br>pkg |       |     |  |  |  |  |  |  |  |  |

| A[2] | PCR[2] | SIUL       | GPIO[2]            | ALT0    | GPIO[2]   | —                     | Pull down              | М     | S                 |            | 84    | N16 |  |  |  |  |  |  |  |  |

|      |        | eTimer_0   | ETC[2]             | ALT1    | ETC[2]    | PSMI[37];<br>PADSEL=0 |                        |       |                   |            |       |     |  |  |  |  |  |  |  |  |

|      |        | FlexPWM_0  | A[3]               | ALT3    | A[3]      | PSMI[23];<br>PADSEL=0 | -                      |       |                   |            |       |     |  |  |  |  |  |  |  |  |

|      |        | DSPI_2     | _                  | —       | SIN       | PSMI[2];<br>PADSEL=0  |                        | -     |                   |            |       |     |  |  |  |  |  |  |  |  |

|      |        | MC_RGM     | _                  |         | ABS[0]    | —                     |                        |       |                   |            |       |     |  |  |  |  |  |  |  |  |

|      |        | SIUL       | _                  | —       | EIRQ[2]   | —                     |                        |       |                   |            |       |     |  |  |  |  |  |  |  |  |

| A[3] | PCR[3] | SIUL       | GPIO[3]            | ALT0    | GPIO[3]   | —                     | Pull down              | М     | S                 |            | 92    | K17 |  |  |  |  |  |  |  |  |

|      |        | eTimer_0   | ETC[3]             | ALT1    | ETC[3]    | PSMI[38];<br>PADSEL=0 |                        |       |                   |            |       |     |  |  |  |  |  |  |  |  |

|      |        | DSPI_2     | CS0                | ALT2    | CS0       | PSMI[3];<br>PADSEL=0  |                        |       |                   |            |       |     |  |  |  |  |  |  |  |  |

|      |        | FlexPWM_0  | B[3]               | ALT3    | B[3]      | PSMI[27];<br>PADSEL=0 |                        | -     |                   |            |       |     |  |  |  |  |  |  |  |  |

|      |        | MC_RGM     | _                  | _       | ABS[2]    | —                     |                        |       |                   |            |       |     |  |  |  |  |  |  |  |  |

|      |        | SIUL       |                    | —       | EIRQ[3]   | —                     | •                      |       |                   |            |       |     |  |  |  |  |  |  |  |  |

| A[4] | PCR[4] | SIUL       | GPIO[4]            | ALT0    | GPIO[4]   | —                     | Pull down              | М     | S                 |            | 108   | C16 |  |  |  |  |  |  |  |  |

|      |        | eTimer_1   | ETC[0]             | ALT1    | ETC[0]    | PSMI[9];<br>PADSEL=0  |                        |       |                   |            |       |     |  |  |  |  |  |  |  |  |

|      |        | DSPI_2     | CS1                | ALT2    | —         | —                     | •                      |       |                   |            |       |     |  |  |  |  |  |  |  |  |

|      |        | eTimer_0   | ETC[4]             | ALT3    | ETC[4]    | PSMI[7];<br>PADSEL=0  |                        |       |                   |            |       |     |  |  |  |  |  |  |  |  |

|      |        | MC_RGM     | —                  | —       | FAB       | —                     |                        |       |                   |            |       |     |  |  |  |  |  |  |  |  |

|      |        | SIUL       | _                  | —       | EIRQ[4]   | —                     |                        |       |                   |            |       |     |  |  |  |  |  |  |  |  |

| Port |             |            | Alternate          | Output  | Input     | Input mux             | Weak pull              | Pad s      | peed <sup>1</sup> | Pin #      |            |

|------|-------------|------------|--------------------|---------|-----------|-----------------------|------------------------|------------|-------------------|------------|------------|

| name | PCR         | Peripheral | output<br>function | mux sel | functions | select                | config during<br>reset | SRC<br>= 1 | SRC<br>= 0        | 144<br>pkg | 257<br>pkg |

| D[4] | PCR[52]     | SIUL       | GPIO[52]           | ALT0    | GPIO[52]  | _                     | _                      | SYM        | S                 | 129        | B7         |

|      |             | FlexRay    | CB_TR_EN           | ALT1    | —         | —                     |                        |            |                   |            |            |

|      |             | eTimer_1   | ETC[5]             | ALT2    | ETC[5]    | PSMI[14];<br>PADSEL=2 |                        |            |                   |            |            |

|      |             | FlexPWM_0  | B[3]               | ALT3    | B[3]      | PSMI[27];<br>PADSEL=2 |                        |            |                   |            |            |

| D[5] | PCR[53]     | SIUL       | GPIO[53]           | ALT0    | GPIO[53]  | _                     | —                      | М          | S                 | 33         | N3         |

|      |             | DSPI_0     | CS3                | ALT1    | —         | —                     |                        |            |                   |            |            |

|      |             | FlexPWM_0  | —                  | _       | FAULT[2]  | PSMI[18];<br>PADSEL=0 |                        |            |                   |            |            |

| D[6] | [6] PCR[54] | SIUL       | GPIO[54]           | ALT0    | GPIO[54]  | —                     | — N                    | М          | S                 | 34         | P3         |

|      |             | DSPI_0     | CS2                | ALT1    | —         | —                     |                        |            |                   |            |            |

|      |             | FlexPWM_0  | X[3]               | ALT3    | X[3]      | PSMI[30];<br>PADSEL=1 |                        |            |                   |            |            |

|      |             | FlexPWM_0  | —                  | _       | FAULT[1]  | PSMI[17];<br>PADSEL=1 |                        |            |                   |            |            |

| D[7] | PCR[55]     | SIUL       | GPIO[55]           | ALT0    | GPIO[55]  | _                     | —                      | М          | M S               | 37         | R4         |

|      |             | DSPI_1     | CS3                | ALT1    | —         | —                     |                        |            |                   |            |            |

|      |             | DSPI_0     | CS4                | ALT3    | —         | —                     |                        |            |                   |            |            |

|      |             | SWG        | analog output      |         | —         | —                     |                        |            |                   |            |            |

| D[8] | PCR[56]     | SIUL       | GPIO[56]           | ALT0    | GPIO[56]  | —                     | —                      | М          | S                 | 32         | M3         |

|      |             | DSPI_1     | CS2                | ALT1    | —         | —                     |                        |            |                   |            |            |

|      |             | eTimer_1   | ETC[4]             | ALT2    | ETC[4]    | PSMI[13];<br>PADSEL=2 |                        |            |                   |            |            |

|      |             | DSPI_0     | CS5                | ALT3    | _         | —                     |                        |            |                   |            |            |

|      |             | FlexPWM_0  | —                  | _       | FAULT[3]  | PSMI[19];<br>PADSEL=1 | 1                      |            |                   |            |            |

| Table 7. Pin | muxing (continued) |

|--------------|--------------------|

|--------------|--------------------|

| Port PCR |                                   |            | Alternate | Outrout             | Input                  |                       | Weak pull  | Pad s      | peed <sup>1</sup> | Pin # |    |     |     |   |    |     |   |     |     |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |  |  |  |  |  |  |  |  |  |

|----------|-----------------------------------|------------|-----------|---------------------|------------------------|-----------------------|------------|------------|-------------------|-------|----|-----|-----|---|----|-----|---|-----|-----|--|--|--|--|--|--|--|--|--|--|--|--|--|--|---|--|--|--|--|--|--|--|--|--|

|          | PCR Peripheral Output<br>function | mux sel    |           | Input mux<br>select | config during<br>reset | SRC<br>= 1            | SRC<br>= 0 | 144<br>pkg | 257<br>pkg        |       |    |     |     |   |    |     |   |     |     |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |  |  |  |  |  |  |  |  |  |

| D[9]     | PCR[57]                           | SIUL       | GPIO[57]  | ALT0                | GPIO[57]               | —                     | _          | М          | S                 | 26    | L3 |     |     |   |    |     |   |     |     |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |  |  |  |  |  |  |  |  |  |

|          |                                   | FlexPWM_0  | X[0]      | ALT1                | X[0]                   | —                     | -          | -          | -                 | -     |    |     |     |   |    |     |   |     |     |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |  |  |  |  |  |  |  |  |  |

|          |                                   | LINFlexD_1 | TXD       | ALT2                | —                      | —                     |            |            |                   |       |    |     |     |   |    |     |   |     |     |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |  |  |  |  |  |  |  |  |  |

| D[10]    | PCR[58]                           | SIUL       | GPIO[58]  | ALT0                | GPIO[58]               | _                     | .1<br>;    |            |                   | —     |    | _   | М   | S | 76 | T15 |   |     |     |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |  |  |  |  |  |  |  |  |  |

|          |                                   | FlexPWM_0  | A[0]      | ALT1                | A[0]                   | PSMI[20];<br>PADSEL=1 |            |            |                   |       |    |     |     |   |    |     |   |     |     |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |  |  |  |  |  |  |  |  |  |

|          |                                   | eTimer_0   | _         | —                   | ETC[0]                 | PSMI[35];<br>PADSEL=1 |            |            |                   |       |    |     |     |   |    |     |   |     |     |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |  |  |  |  |  |  |  |  |  |

| D[11]    | PCR[59]                           | SIUL       | GPIO[59]  | ALT0                | GPIO[59]               | —                     | _          | —          |                   | —     |    | —   | М   | S | 78 | R16 |   |     |     |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |  |  |  |  |  |  |  |  |  |

|          |                                   | FlexPWM_0  | B[0]      | ALT1                | B[0]                   | PSMI[24];<br>PADSEL=1 |            |            |                   |       |    |     |     |   |    |     |   |     | -   |  |  |  |  |  |  |  |  |  |  |  |  |  |  | • |  |  |  |  |  |  |  |  |  |

|          |                                   | eTimer_0   | _         | —                   | ETC[1]                 | PSMI[36];<br>PADSEL=1 |            |            |                   |       |    |     |     |   |    |     |   |     |     |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |  |  |  |  |  |  |  |  |  |

| D[12]    | PCR[60]                           | SIUL       | GPIO[60]  | ALT0                | GPIO[60]               |                       | 1          | — M        | —                 | М     | S  | 99  | G14 |   |    |     |   |     |     |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |  |  |  |  |  |  |  |  |  |

|          |                                   | FlexPWM_0  | X[1]      | ALT1                | X[1]                   | PSMI[28];<br>PADSEL=1 |            |            |                   |       |    |     |     |   |    |     |   |     |     |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |  |  |  |  |  |  |  |  |  |

|          |                                   | LINFlexD_1 | _         | —                   | RXD                    | PSMI[32];<br>PADSEL=1 |            |            |                   |       |    |     |     |   |    |     |   |     |     |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |  |  |  |  |  |  |  |  |  |

| D[14]    | PCR[62]                           | SIUL       | GPIO[62]  | ALT0                | GPIO[62]               | —                     |            |            | M                 | —     | —  | —   | M   | - | N  | М   | S | 105 | D16 |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |  |  |  |  |  |  |  |  |  |

|          |                                   | FlexPWM_0  | B[1]      | ALT1                | B[1]                   | PSMI[25];<br>PADSEL=2 |            |            |                   |       |    |     |     |   |    |     |   |     |     |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |  |  |  |  |  |  |  |  |  |

|          |                                   | eTimer_0   | _         | —                   | ETC[3]                 | PSMI[38];<br>PADSEL=1 |            |            |                   |       |    |     |     |   |    |     |   |     |     |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |  |  |  |  |  |  |  |  |  |

|          |                                   |            |           |                     | Port E                 |                       |            |            |                   |       |    |     |     |   |    |     |   |     |     |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |  |  |  |  |  |  |  |  |  |

| E[0]     | PCR[64]                           | SIUL       |           | ALT0                | GPI[64]                |                       | _          | —          |                   | —     | 68 | T13 |     |   |    |     |   |     |     |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |  |  |  |  |  |  |  |  |  |

|          |                                   | ADC_1      |           | —                   | AN[5] <sup>3</sup>     | —                     | ]          |            |                   |       |    |     |     |   |    |     |   |     |     |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |  |  |  |  |  |  |  |  |  |

| E[2]     | PCR[66]                           | SIUL       | _         | ALT0                | GPI[66]                | _                     | —          | —          | —                 | 49    | U6 |     |     |   |    |     |   |     |     |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |  |  |  |  |  |  |  |  |  |

|          |                                   | ADC_0      |           | —                   | AN[5] <sup>3</sup>     | _                     |            |            |                   |       |    |     |     |   |    |     |   |     |     |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |  |  |  |  |  |  |  |  |  |

67

### <sup>2</sup> Adjust resistor at bipolar transistor collector for 3.3V to avoid VCE<VCE<sub>SAT</sub>

The recommended external ballast transistor is the bipolar transistor BCP68 with the gain range of 85 up to 375 (for IC=500mA, VCE=1V) provided by several suppliers. This includes the gain variations BCP68-10, BCP68-16 and BCP68-25. The most important parameters for the interoperability with the integrated voltage regulator are the DC current gain (hFE) and the temperature coefficient of the gain (XTB). While the specified gain range of most BCP68 vendors is the same, there are slight variations in the temperature coefficient parameter. MPC5643L Voltage regulator operation was simulated against the typical variation on temperature coefficient and against the specified gain range to have a robust design.

| Symb              | ool              | Parameter                                                              | Conditions                                                                                                          | Min   | Тур | Max   | Unit |

|-------------------|------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------|-----|-------|------|

|                   | C <sub>ext</sub> | External decoupling/<br>stability capacitor                            | Min, max values shall be<br>granted with respect to<br>tolerance, voltage,<br>temperature, and aging<br>variations. | 12    | _   | 40    | μF   |

|                   | SR               | Combined ESR of external capacitor                                     | _                                                                                                                   | 1     | —   | 100   | mΩ   |

|                   | SR               | Number of pins for<br>external decoupling/<br>stability capacitor      | _                                                                                                                   | 5     | _   | _     |      |

| C <sub>V1V2</sub> | SR               | Total capacitance on 1.2 V pins                                        | Ceramic capacitors,<br>taking into account<br>tolerance, aging, voltage<br>and temperature variation                | 300   | _   | 900   | nF   |

| t <sub>SU</sub>   |                  | Start-up time after main<br>supply stabilization                       | $C_{load} = 10 \ \mu F \times 4$                                                                                    | —     | —   | 2.5   | ms   |

| —                 |                  | Main High Voltage Power -<br>Low Voltage Detection,<br>upper threshold | _                                                                                                                   | _     | _   | 2.93  | V    |

| _                 | D                | Main supply low voltage detector, lower threshold                      | _                                                                                                                   | 2.6   | —   | —     | V    |

| _                 | D                | Digital supply high voltage detector upper threshold                   | Before a destructive reset<br>initialization phase<br>completion                                                    | 1.355 | _   | 1.495 | V    |

|                   |                  |                                                                        | After a destructive reset<br>initialization phase<br>completion                                                     | 1.39  | _   | 1.47  |      |

| _                 | D                | Digital supply high voltage detector lower threshold                   | Before a destructive reset<br>initialization phase<br>completion                                                    | 1.315 | _   | 1.455 | V    |

|                   |                  |                                                                        | After a destructive reset<br>initialization phase<br>completion                                                     | 1.35  | _   | 1.38  |      |

| Table 18. | Voltage regulator | electrical s | specifications |

|-----------|-------------------|--------------|----------------|

|-----------|-------------------|--------------|----------------|

| r    |     |                                                         |                                                                 |       | 1   | 1        | 1    |

|------|-----|---------------------------------------------------------|-----------------------------------------------------------------|-------|-----|----------|------|

| Symb | ool | Parameter                                               | Conditions                                                      | Min   | Тур | Max      | Unit |

| _    | D   | Digital supply low voltage detector lower threshold     | After a destructive reset<br>initialization phase<br>completion | 1.080 | _   | 1.140    | V    |

| _    | D   | Digital supply low voltage detector upper threshold     | After a destructive reset<br>initialization phase<br>completion | 1.16  | _   | 1.22     | V    |

| —    | D   | Digital supply low voltage detector lower threshold     | Before a destructive reset initialization phase                 | 1.080 | _   | 1.226    | V    |

| _    | D   | Digital supply low voltage detector upper threshold     | Before a destructive reset initialization phase                 | 1.160 | —   | 1.306    | V    |

| _    | D   | POR rising/ falling supply threshold voltage            | _                                                               | 1.6   | —   | 2.6      | V    |

| —    | SR  | Supply ramp rate                                        | _                                                               | 3 V/s | _   | 0.5 V/µs | —    |

| —    | D   | LVD_MAIN: Time<br>constant of RC filter at<br>LVD input | 3.3V noise rejection at the<br>input of<br>LVD comparator       | 1.1   | _   | -        | μs   |

| _    | D   | HVD_DIG: Time constant<br>of RC filter at LVD input     | 1.2V noise rejection at the<br>input of<br>LVD comparator       | 0.1   | _   | _        | μs   |

| _    | D   | LVD_DIG: Time constant<br>of RC filter at LVD input     | 1.2V noise rejection at the<br>input of<br>LVD comparator       | 0.1   | _   | _        | μs   |

Table 18. Voltage regulator electrical specifications (continued)

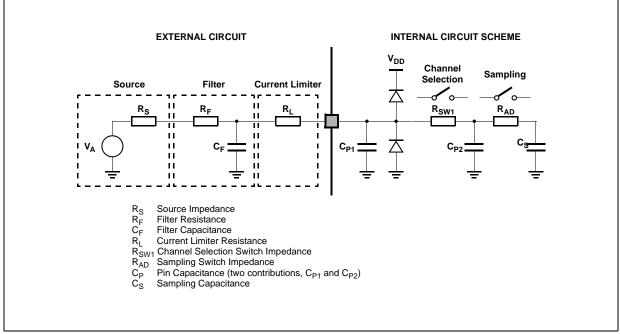

A real filter can typically be obtained by using a series resistance with a capacitor on the input pin (simple RC filter). The RC filtering may be limited according to the value of source impedance of the transducer or circuit supplying the analog signal to be measured. The filter at the input pins must be designed taking into account the dynamic characteristics of the input signal (bandwidth) and the equivalent input impedance of the ADC itself.

In fact a current sink contributor is represented by the charge sharing effects with the sampling capacitance:  $C_S$  and  $C_{p2}$  being substantially a switched capacitance, with a frequency equal to the conversion rate of the ADC, it can be seen as a resistive path to ground. For instance, assuming a conversion rate of 1 MHz, with  $C_{p2} + CS$  equal to 7.5 pF, a resistance of 133 k $\Omega$  is obtained ( $R_{EQ} = 1 / (fS^*(C_{p2}+C_S))$ ), where fS represents the conversion rate at the considered channel). To minimize the error induced by the voltage partitioning between this resistance (sampled voltage on  $C_s$ ) and the sum of  $R_S + R_F$ , the external circuit must be designed to respect the Equation 4:

$$V_A \bullet \frac{R_S + R_F}{R_{EO}} < \frac{1}{2}LSB$$

Eqn. 4

Equation 4 generates a constraint for external network design, in particular on resistive path. Internal switch resistances ( $R_{SW}$  and  $R_{AD}$ ) can be neglected with respect to external resistances.

Figure 8. Input Equivalent Circuit

A second aspect involving the capacitance network shall be considered. Assuming the three capacitances  $C_{F}$ ,  $C_{P1}$  and  $C_{P2}$  are initially charged at the source voltage  $V_A$  (refer to the equivalent circuit reported in Figure 8): A charge sharing phenomenon is installed when the sampling phase is started (A/D switch close).

- <sup>4</sup> During the sample time the input capacitance CS can be charged/discharged by the external source. The internal resistance of the analog source must allow the capacitance to reach its final voltage level within t<sub>sample</sub>. After the end of the sample time t<sub>sample</sub>, changes of the analog input voltage have no effect on the conversion result. Values for the sample clock t<sub>sample</sub> depend on programming.

- <sup>5</sup> This parameter does not include the sample time Tsample, but only the time for determining the digital result.

- <sup>6</sup> See Figure 8.

- <sup>7</sup> For the 144-pin package

- <sup>8</sup> No missing codes

# 3.16 Flash memory electrical characteristics

| No. | Symbol                   |    | Parameter                                       | Typ <sup>1</sup> | Initial<br>Max <sup>2</sup> | Lifetime<br>Max <sup>3</sup> | Unit |

|-----|--------------------------|----|-------------------------------------------------|------------------|-----------------------------|------------------------------|------|

| 1   | T <sub>DWPROGRAM</sub>   | *4 | Double word (64 bits) program time <sup>4</sup> | 30               | —                           | 500                          | μs   |

| 2   | T <sub>PPROGRAM</sub>    | *4 | Page(128 bits) program time <sup>4</sup>        | 40               | 160                         | 500                          | μs   |

| 3   | T <sub>16KPPERASE</sub>  | *4 | 16 KB block pre-program and erase time          | 250              | 1000                        | 5000                         | ms   |

| 4   | T <sub>48KPPERASE</sub>  | *4 | 48 KB block pre-program and erase time          | 400              | 1500                        | 5000                         | ms   |

| 5   | T <sub>64KPPERASE</sub>  | *4 | 64 KB block pre-program and erase time          | 450              | 1800                        | 5000                         | ms   |

| 6   | T <sub>128KPPERASE</sub> | *4 | 128 KB block pre-program and erase time         | 800              | 2600                        | 7500                         | ms   |

| 7   | T <sub>256KPPERASE</sub> | *4 | 256 KB block pre-program and erase time         | 1400             | 5200                        | 15000                        | ms   |

#### Table 26. Flash memory program and erase electrical specifications

<sup>1</sup> Typical program and erase times represent the median performance and assume nominal supply values and operation at 25C. These values are characterized, but not tested.I

<sup>2</sup> Initial Max program and erase times provide guidance for time-out limits used in the factory and apply for <100 program/erase cycles, nominal supply values and operation at 25C. These values are verified at production test.

<sup>3</sup> Lifetime Max program and erase times apply across the voltage, temperature, and cycling range of product life. These values are characterized, but not tested.

<sup>4</sup> Program times are actual hardware programming times and do not include software overhead.

#### Table 27. Flash memory timing

| Symbol            |   | Parameter                                                                                                   |     | Unit |     |      |

|-------------------|---|-------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

|                   |   | i didineter                                                                                                 | Min | Тур  | Max | Onic |

| T <sub>RES</sub>  | D | Time from clearing the MCR-ESUS or PSUS bit with EHV = 1<br>until DONE goes low                             | —   | _    | 100 | ns   |

| T <sub>DONE</sub> |   | Time from 0 to 1 transition on the MCR-EHV bit initiating a program/erase until the MCR-DONE bit is cleared | _   | _    | 5   | ns   |

| T <sub>PSRT</sub> | D | Time between program suspend resume and the next program suspend request. <sup>1</sup>                      | 100 | _    |     | μS   |

| T <sub>ESRT</sub> | D | Time between erase suspend resume and the next erase suspend request. <sup>2</sup>                          | 10  |      |     | ms   |

The reset sequences shown in Figure 15 and Figure 16 are triggered by functional reset events. RESET is driven low during these two reset sequences *only if* the corresponding functional reset source (which triggered the reset sequence) was enabled to drive RESET low for the duration of the internal reset sequence<sup>1</sup>.

# 3.19.3 Reset sequence trigger mapping

The following table shows the possible trigger events for the different reset sequences. It specifies the reset sequence start conditions as well as the reset sequence end indications that are the basis for the timing data provided in Table 31.

|                                                                                                                         |                                                         |                                        |                                                                    | Re                                                                  | set Sequenc                                                | set Sequence                              |                                            |  |  |

|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|----------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------|------------------------------------------------------------|-------------------------------------------|--------------------------------------------|--|--|

| Reset<br>Sequence<br>Trigger                                                                                            | Reset<br>Sequence<br>Start<br>Condition                 | Reset<br>Sequence<br>End<br>Indication | Destructiv<br>e Reset<br>Sequence,<br>BIST<br>enabled <sup>1</sup> | Destructiv<br>e Reset<br>Sequence,<br>BIST<br>disabled <sup>1</sup> | External<br>Reset<br>Sequenc<br>e Long,<br>BIST<br>enabled | Functiona<br>I Reset<br>Sequenc<br>e Long | Functiona<br>I Reset<br>Sequenc<br>e Short |  |  |

| All internal<br>destructive reset<br>sources<br>(LVDs or internal<br>HVD during<br>power-up and<br>during<br>operation) | Section 3.1<br>9.4.1,<br>Destructive<br>reset           | Release of<br>RESET <sup>2</sup>       | triggers                                                           |                                                                     | cannot<br>trigger                                          | cannot<br>trigger                         | cannot<br>trigger                          |  |  |

| Assertion of RESET <sup>3</sup>                                                                                         | Section 3.1<br>9.4.2,<br>External<br>reset via<br>RESET |                                        | cannot trigger                                                     |                                                                     | triggers <sup>4</sup>                                      | triggers <sup>5</sup>                     | triggers <sup>6</sup>                      |  |  |

| All internal<br>functional reset<br>sources<br>configured for<br>long reset                                             | Sequence<br>starts with<br>internal<br>reset<br>trigger | Release of RESET <sup>7</sup>          | cannot trigger                                                     |                                                                     | cannot<br>trigger                                          | triggers                                  | cannot<br>trigger                          |  |  |

| All internal<br>functional reset<br>sources<br>configured for<br>short reset                                            |                                                         |                                        | cannot                                                             | trigger                                                             | cannot<br>trigger                                          | cannot<br>trigger                         | triggers                                   |  |  |

| Table 32 | . Reset sequenc | e trigger — rese | et sequence |

|----------|-----------------|------------------|-------------|

|          | . Reset sequene | cungger rest     | , sequence  |

<sup>1</sup> Whether BIST is executed or not depends on the chip configuration data stored in the shadow sector of the NVM.

<sup>2</sup> End of the internal reset sequence (as specified in Table 31) can only be observed by release of RESET if it is not held low externally beyond the end of the internal sequence which would prolong the internal reset PHASE3 till RESET is released externally.

<sup>3</sup> The assertion of RESET can only trigger a reset sequence if the device was running (RESET released) before. RESET does not gate a *Destructive Reset Sequence*, *BIST enabled* or a *Destructive Reset Sequence*, *BIST disabled*. However, it can prolong these sequences if RESET is held low externally beyond the end of the internal sequence (beyond PHASE3).

1.See RGM\_FBRE register for more details.

- <sup>4</sup> If RESET is configured for long reset (default) and if BIST is enabled via chip configuration data stored in the shadow sector of the NVM.

- <sup>5</sup> If RESET is configured for long reset (default) and if BIST is disabled via chip configuration data stored in the shadow sector of the NVM.

- <sup>6</sup> If RESET is configured for short reset

- <sup>7</sup> Internal reset sequence can only be observed by state of RESET if bidirectional RESET functionality is enabled for the functional reset source which triggered the reset sequence.

### 3.19.4 Reset sequence — start condition

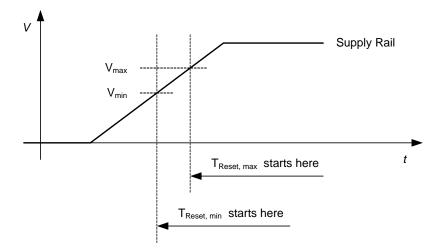

The impact of the voltage thresholds on the starting point of the internal reset sequence are becoming important if the voltage rails / signals ramp up with a very slow slew rate compared to the overall reset sequence duration.

### 3.19.4.1 Destructive reset

Figure 17 shows the voltage threshold that determines the start of the *Destructive Reset Sequence*, *BIST enabled* and the start for the *Destructive Reset Sequence*, *BIST disabled*.

Figure 17. Reset sequence start for Destructive Resets

Table 33. Voltage Thresholds

| Variable name    | Value             |

|------------------|-------------------|

| V <sub>min</sub> | Refer to Table 18 |

| V <sub>max</sub> | Refer to Table 18 |

| Supply Rail      | VDD_HV_PMU        |

### 3.19.4.2 External reset via RESET

Figure 18 shows the voltage thresholds that determine the start of the reset sequences initiated by the assertion of RESET as specified in Table 32.

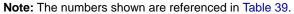

**Note:** The numbers shown are referenced in Table 39.

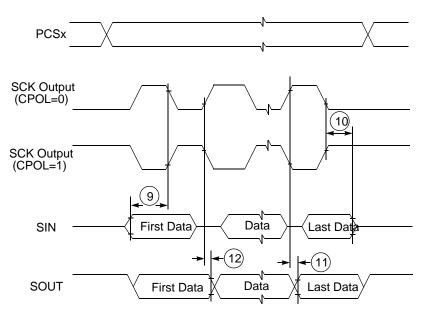

Figure 32. DSPI classic SPI timing — slave, CPHA = 0

MPC5643L Microcontroller Data Sheet, Rev. 9

#### Package characteristics

NOTES:

1. ALL DIMENSIONS IN MILLIMETERS.

2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

3. MAXIMUM SOLDER BALL DIAMETER MEASURED PARALLEL TO DATUM A.

4. DATUM A, THE SEATING PLANE, IS DETERMINED BY THE SPHERICAL CROWNS OF THE SOLDER BALLS.

5. PARALLELISM MEASUREMENT SHALL EXCLUDE ANY EFFECT OF MARK ON TOP SURFACE OF PACKAGE.

| TITLE: PBGA, LOW PROFILE,       | CASE NUMBER: 2082-01            |

|---------------------------------|---------------------------------|

| FINE PITCH, 257 I/O,            | STANDARD: JEDEC MO-275A-JJAC-1  |

| 14 X 14 PKG, 0.8 MM PITCH (MAP) | PACKAGE CODE: IN AGILE SHEET: 2 |

#### Figure 42. 257 MAPBGA package mechanical drawing (2 of 2)

S = Fully spec. qualified, automotive flow

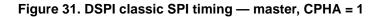

# 5 Ordering information

**Note:** Not all options are available on all devices. See Table 40.

#### Figure 43. Commercial product code structure

| Part number <sup>1</sup> | Flash/SRAM  | Package              | Speed<br>(MHz) <sup>2</sup> | Other features           |

|--------------------------|-------------|----------------------|-----------------------------|--------------------------|

| SPC5643LFF2MLQ1          | 1 MB/128 KB | 144 LQFP (Pb free)   | 120                         | FlexRay<br>-40-125 °C    |

| SPC5643LFF2MMM1          | 1 MB/128 KB | 257 MAPBGA (Pb free) | 120                         | FlexRay<br>-40-125 °C    |

| SPC5643LF2MLQ1           | 1 MB/128 KB | 144 LQFP (Pb free)   | 120                         | No FlexRay<br>-40-125 °C |

| SPC5643LF2MMM1           | 1 MB/128 KB | 257 MAPBGA (Pb free) | 120                         | No FlexRay<br>-40-125 °C |

| SPC5643LFF2VLQ1          | 1 MB/128 KB | 144 LQFP (Pb free)   | 120                         | FlexRay<br>-40-105 °C    |

| SPC5643LFF2VMM1          | 1 MB/128 KB | 257 MAPBGA (Pb free) | 120                         | FlexRay<br>-40-105 °C    |

| SPC5643LF2VLQ1           | 1 MB/128 KB | 144 LQFP (Pb free)   | 120                         | No FlexRay<br>-40-105 °C |

| SPC5643LF2VMM1           | 1 MB/128 KB | 257 MAPBGA (Pb free) | 120                         | No FlexRay<br>-40-105 °C |

| SPC5643LFF2MLQ8          | 1 MB/128 KB | 144 LQFP (Pb free)   | 80                          | FlexRay<br>-40-125 °C    |

| SPC5643LFF2MMM8          | 1 MB/128 KB | 257 MAPBGA (Pb free) | 80                          | FlexRay<br>–40–125 °C    |

#### Table 40. Orderable part number summary

#### **Document revision history**

| Revision | Date        | Description of changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision | Dale        | Description of changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 6        | 11 Mar 2011 | In the "ADC conversion characteristics" table:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| (cont.)  | (cont.)     | Changed DNL min from -2 to -1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |