Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                              |

|----------------------------|--------------------------------------------------------------|

| Product Status             | Active                                                       |

| Core Processor             | e200z4                                                       |

| Core Size                  | 32-Bit Dual-Core                                             |

| Speed                      | 64MHz                                                        |

| Connectivity               | CANbus, FlexRay, LINbus, SPI, UART/USART                     |

| Peripherals                | DMA, POR, PWM, WDT                                           |

| Number of I/O              | -                                                            |

| Program Memory Size        | 1MB (1M x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | -                                                            |

| RAM Size                   | 128K x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                    |

| Data Converters            | A/D 32x12b                                                   |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                           |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 100-LQFP                                                     |

| Supplier Device Package    | 100-LQFP (14x14)                                             |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=spc5643lff2mll6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Table 1. MPC5643L device summary (continued)

|             | Feature                                                            | MPC5643L      |  |  |  |

|-------------|--------------------------------------------------------------------|---------------|--|--|--|

| Packages    | LQFP                                                               | 144 pins      |  |  |  |

|             | MAPBGA                                                             | 257 MAPBGA    |  |  |  |

| Temperature | Temperature range (junction)                                       | −40 to 150 °C |  |  |  |

|             | Ambient temperature range using external ballast transistor (LQFP) | -40 to 125 °C |  |  |  |

|             | Ambient temperature range using external ballast transistor (BGA)  | –40 to 125 °C |  |  |  |

The third eTimer (eTimer\_2) is available with external I/O access only in the BGA package, on the LQFP package eTimer\_2 is available internally only without any external I/O access.

# 1.4 Block diagram

Figure 1 shows a top-level block diagram of the MPC5643L device.

<sup>&</sup>lt;sup>2</sup> The second FlexPWM module is available only in the BGA package.

#### Introduction

- Single-cycle read responses (0 AHB data-phase wait states) for hits in the buffers. The buffers implement a least-recently-used replacement algorithm to maximize performance.

- Programmable response for read-while-write sequences including support for stall-while-write, optional stall notification interrupt, optional flash operation abort, and optional abort notification interrupt.

- Separate and independent configurable access timing (on a per bank basis) to support use across a wide range of

platforms and frequencies.

- Support of address-based read access timing for emulation of other memory types.

- Support for reporting of single- and multi-bit error events.

- Typical operating configuration loaded into programming model by system reset.

The platform flash controller is replicated for each processor.

### 1.5.8 Platform Static RAM Controller (SRAMC)

The SRAMC module is the platform SRAM array controller, with integrated error detection and correction.

The main features of the SRAMC provide connectivity for the following interfaces:

- XBAR Slave Port (64-bit data path)

- ECSM (ECC Error Reporting, error injection and configuration)

- SRAM array

The following functions are implemented:

- ECC encoding (32-bit boundary for data and complete address bus)

- ECC decoding (32-bit boundary and entire address)

- Address translation from the AHB protocol on the XBAR to the SRAM array

The platform SRAM controller is replicated for each processor.

### 1.5.9 Memory subsystem access time

Every memory access the CPU performs requires at least one system clock cycle for the data phase of the access. Slower memories or peripherals may require additional data phase wait states. Additional data phase wait states may also occur if the slave being accessed is not parked on the requesting master in the crossbar.

Table 2 shows the number of additional data phase wait states required for a range of memory accesses.

Table 2. Platform memory access time summary

| AHB transfer              | Data phase wait states | Description                                                                         |

|---------------------------|------------------------|-------------------------------------------------------------------------------------|

| e200z4d instruction fetch | 0                      | Flash memory prefetch buffer hit (page hit)                                         |

| e200z4d instruction fetch | 3                      | Flash memory prefetch buffer miss (based on 4-cycle random flash array access time) |

| e200z4d data read         | 0–1                    | SRAM read                                                                           |

| e200z4d data write        | 0                      | SRAM 32-bit write                                                                   |

| Table 2. Platform | memory access | time summary | (continued) |

|-------------------|---------------|--------------|-------------|

|                   |               |              |             |

| AHB transfer              | Data phase wait states | Description                                                                                                     |

|---------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------|

| e200z4d data write        | 0                      | SRAM 64-bit write (executed as 2 x 32-bit writes)                                                               |

| e200z4d data write        | 0–2                    | SRAM 8-,16-bit write (Read-modify-Write for ECC)                                                                |

| e200z4d flash memory read | 0                      | Flash memory prefetch buffer hit (page hit)                                                                     |

| e200z4d flash memory read | 3                      | Flash memory prefetch buffer miss (at 120 MHz; includes 1 cycle of program flash memory controller arbitration) |

### 1.5.10 Error Correction Status Module (ECSM)

The ECSM on this device manages the ECC configuration and reporting for the platform memories (flash memory and SRAM). It does not implement the actual ECC calculation. A detected error (double error for flash memory or SRAM) is also reported to the FCCU. The following errors and indications are reported into the ECSM dedicated registers:

- ECC error status and configuration for flash memory and SRAM

- ECC error reporting for flash memory

- ECC error reporting for SRAM

- ECC error injection for SRAM

### 1.5.11 Peripheral bridge (PBRIDGE)

The PBRIDGE implements the following features:

- · Duplicated periphery

- Master access privilege level per peripheral (per master: read access enable; write access enable)

- Checker applied on PBRIDGE output toward periphery

- Byte endianess swap capability

## 1.5.12 Interrupt Controller (INTC)

The INTC provides priority-based preemptive scheduling of interrupt requests, suitable for statically scheduled hard real-time systems.

For high-priority interrupt requests, the time from the assertion of the interrupt request from the peripheral to when the processor is executing the interrupt service routine (ISR) has been minimized. The INTC provides a unique vector for each interrupt request source for quick determination of which ISR needs to be executed. It also provides an ample number of priorities so that lower priority ISRs do not delay the execution of higher priority ISRs. To allow the appropriate priorities for each source of interrupt request, the priority of each interrupt request is software configurable.

The INTC supports the priority ceiling protocol for coherent accesses. By providing a modifiable priority mask, the priority can be raised temporarily so that all tasks which share the resource can not preempt each other.

The INTC provides the following features:

- Duplicated periphery

- Unique 9-bit vector per interrupt source

- 16 priority levels with fixed hardware arbitration within priority levels for each interrupt source

- Priority elevation for shared resource

The INTC is replicated for each processor.

MPC5643L Microcontroller Data Sheet, Rev. 9

### Package pinouts and signal descriptions

Table 4. 257 MAPBGA pin function summary (continued)

| Pin# | Port/function              | Peripheral | Output function | Input function |

|------|----------------------------|------------|-----------------|----------------|

| D11  | A[11]                      | SIUL       | GPIO[11]        | GPIO[11]       |

|      |                            | DSPI_2     | SCK             | SCK            |

|      |                            | FlexPWM_0  | A[0]            | A[0]           |

|      |                            | FlexPWM_0  | A[2]            | A[2]           |

|      |                            | SIUL       | _               | EIRQ[10]       |

| D12  | E[13]                      | SIUL       | GPIO[77]        | GPIO[77]       |

|      |                            | eTimer_0   | ETC[5]          | ETC[5]         |

|      |                            | DSPI_2     | CS3             | _              |

|      |                            | SIUL       | _               | EIRQ[25]       |

| D13  | F[15]                      | SIUL       | GPIO[95]        | GPIO[95]       |

|      |                            | LINFlexD_1 | _               | RXD            |

| D14  | V <sub>DD_HV_IO_RING</sub> |            | _               |                |

| D15  | V <sub>PP_TEST</sub> 1     |            | _               |                |

| D16  | D[14]                      | SIUL       | GPIO[62]        | GPIO[62]       |

|      |                            | FlexPWM_0  | B[1]            | B[1]           |

|      |                            | eTimer_0   | eTimer_0 —      |                |

| D17  | G[3]                       | SIUL       | GPIO[99]        | GPIO[99]       |

|      |                            | FlexPWM_0  | A[2]            | A[2]           |

|      |                            | eTimer_0   | _               | ETC[4]         |

| E1   | MDO0                       |            | _               |                |

| E2   | F[6]                       | SIUL       | GPIO[86]        | GPIO[86]       |

|      |                            | NPC        | MDO[1]          | _              |

| E3   | D[1]                       | SIUL       | GPIO[49]        | GPIO[49]       |

|      |                            | eTimer_1   | ETC[2]          | ETC[2]         |

|      |                            | CTU_0      | EXT_TGR         | _              |

|      |                            | FlexRay    | _               | CA_RX          |

| E4   | NMI                        |            | _               |                |

| E14  | Not connected              |            | _               |                |

| E15  | C[14]                      | SIUL       | GPIO[46]        | GPIO[46]       |

|      |                            | eTimer_1   | ETC[2]          | ETC[2]         |

|      |                            | CTU_0      | EXT_TGR         | _              |

| E16  | G[2]                       | SIUL       | GPIO[98]        | GPIO[98]       |

|      |                            | FlexPWM_0  | X[2]            | X[2]           |

|      |                            | DSPI_1     | CS1             | _              |

### Package pinouts and signal descriptions

Table 4. 257 MAPBGA pin function summary (continued)

| Pin # | Port/function              | Peripheral | Output function | Input function |

|-------|----------------------------|------------|-----------------|----------------|

| K17   | A[3]                       | SIUL       | GPIO[3]         | GPIO[3]        |

|       |                            | eTimer_0   | ETC[3]          | ETC[3]         |

|       |                            | DSPI_2     | CS0             | CS0            |

|       |                            | FlexPWM_0  | B[3]            | B[3]           |

|       |                            | MC_RGM     | _               | ABS[2]         |

|       |                            | SIUL       | _               | EIRQ[3]        |

| L1    | F[10]                      | SIUL       | GPIO[90]        | GPIO[90]       |

|       |                            | NPC        | EVTO            | _              |

| L2    | F[11]                      | SIUL       | GPIO[91]        | GPIO[91]       |

|       |                            | NPC        | _               | EVTI           |

| L3    | D[9]                       | SIUL       | GPIO[57]        | GPIO[57]       |

|       |                            | FlexPWM_0  | X[0]            | X[0]           |

|       |                            | LINFlexD_1 | TXD             | _              |

| L4    | Not connected              |            | _               |                |

| L6    | V <sub>DD_LV</sub>         |            | _               |                |

| L7    | V <sub>SS_LV</sub>         |            | _               |                |

| L8    | V <sub>SS_LV</sub>         |            | _               |                |

| L9    | V <sub>SS_LV</sub>         |            | _               |                |

| L10   | V <sub>SS_LV</sub>         |            | _               |                |

| L11   | V <sub>SS_LV</sub>         |            | _               |                |

| L12   | V <sub>DD_LV</sub>         |            | _               |                |

| L14   | Not connected              |            | _               |                |

| L15   | TCK                        |            | _               |                |

| L16   | H[4]                       | SIUL       | GPIO[116]       | GPIO[116]      |

|       |                            | FlexPWM_1  | X[0]            | X[0]           |

|       |                            | eTimer_2   | ETC[0]          | ETC[0]         |

| L17   | B[4]                       | SIUL       | GPIO[20]        | GPIO[20]       |

|       |                            | JTAGC      | TDO             | _              |

| M1    | V <sub>DD_HV_OSC</sub>     |            | _               |                |

| M2    | V <sub>DD_HV_IO_RING</sub> |            | _               |                |

| М3    | D[8]                       | SIUL       | GPIO[56]        | GPIO[56]       |

|       |                            | DSPI_1     | CS2             | _              |

|       |                            | eTimer_1   | ETC[4]          | ETC[4]         |

|       |                            | DSPI_0     | CS5             | _              |

|       |                            | FlexPWM_0  | _               | FAULT[3]       |

MPC5643L Microcontroller Data Sheet, Rev. 9

Table 5. Supply pins (continued)

|                        | Supply                                                                                                                                                         | Pin        | #                   |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------------|

| Symbol                 | Description                                                                                                                                                    | 144<br>pkg | 257<br>pkg          |

| V <sub>SS_LV_COR</sub> | VSS_LV_COR Decoupling pins for core logic. Decoupling capacitor must be connected between these pins and the nearest V <sub>DD_LV_COR</sub> pin.               | 17         | VSS_HV <sup>2</sup> |

| V <sub>DD_LV_COR</sub> | VDD_LV_COR Decoupling pins for core logic. Decoupling capacitor must be connected between these pins and the nearest V <sub>SS_LV_COR</sub> pin.               | 18         | VDD_LV <sup>1</sup> |

| V <sub>SS</sub> 1V2    | VSS_LV_PLL0_PLL1 / 1.2 V Decoupling pins for on-chip FMPLL modules. Decoupling capacitor must be connected between this pin and V <sub>DD_LV_PLL</sub> .       | 35         | N4                  |

| V <sub>DD</sub> 1V2    | VDD_LV_PLL0_PLL1 Decoupling pins for on-chip FMPLL modules. Decoupling capacitor must be connected between this pin and V <sub>SS_LV_PLL</sub> .               | 36         | P4                  |

| V <sub>DD_LV_COR</sub> | VDD_LV_COR Decoupling pins for core logic. Decoupling capacitor must be connected between these pins and the nearest V <sub>SS_LV_COR</sub> pin.               | 39         | VDD_LV <sup>1</sup> |

| V <sub>SS_LV_COR</sub> | VSS_LV_COR Decoupling pins for core logic. Decoupling capacitor must be connected between these pins and the nearest V <sub>DD_LV_COR</sub> pin.               | 40         | VSS_LV <sup>2</sup> |

| V <sub>DD_LV_COR</sub> | VDD_LV_COR Decoupling pins for core logic and Regulator feedback. Decoupling capacitor must be connected between this pins and VSS_LV_REGCOR.                  | 70         | VDD_LV <sup>1</sup> |

| V <sub>SS_LV_COR</sub> | VSS_LV_REGCOR0 Decoupling pins for core logic and Regulator feedback. Decoupling capacitor must be connected between this pins and V <sub>DD_LV_REGCOR</sub> . | 71         | VSS_LV <sup>2</sup> |

| V <sub>DD_LV_COR</sub> | VDD_LV_COR Decoupling pins for core logic. Decoupling capacitor must be connected between these pins and the nearest V <sub>SS_LV_COR</sub> pin.               | 93         | VDD_LV <sup>1</sup> |

| V <sub>SS_LV_COR</sub> | VSS_LV_COR / 1.2 V Decoupling pins for core logic. Decoupling capacitor must be connected between these pins and the nearest V <sub>DD_LV_COR pin</sub> .      | 94         | VSS_LV <sup>2</sup> |

| V <sub>DD</sub> 1V2    | VDD_LV_COR Decoupling pins for core logic. Decoupling capacitor must be connected between these pins and the nearest V <sub>DD_LV_COR</sub> pin.               | 131        | VDD_LV <sup>1</sup> |

| V <sub>SS</sub> 1V2    | VSS_LV_COR Decoupling pins for core logic. Decoupling capacitor must be connected between these pins and the nearest V <sub>DD_LV_COR</sub> pin.               | 132        | VSS_LV <sup>2</sup> |

| V <sub>DD</sub> 1V2    | VDD_LV_COR / Decoupling pins for core logic. Decoupling capacitor must be connected between these pins and the nearest V <sub>DD_LV_COR</sub> pin.             | 135        | VDD_LV <sup>1</sup> |

| V <sub>SS</sub> 1V2    | VSS_LV_COR / Decoupling pins for core logic. Decoupling capacitor must be connected between these pins and the nearest V <sub>DD_LV_COR</sub> pin.             | 137        | VSS_LV <sup>2</sup> |

<sup>1</sup> VDD\_LV balls are tied together on the 257 MAPBGA substrate.

MPC5643L Microcontroller Data Sheet, Rev. 9

| Port  |         |                | Alternate          | Output  | Input               | Input mux             | Weak pull              | Pad s      | peed <sup>1</sup> | Piı      | Pin# |            |  |  |  |

|-------|---------|----------------|--------------------|---------|---------------------|-----------------------|------------------------|------------|-------------------|----------|------|------------|--|--|--|

| name  | PCR     | Peripheral     | output<br>function | mux sel | functions           | select                | config during<br>reset | SRC<br>= 1 | SRC<br>= 0        | 14<br>pl |      | 257<br>pkg |  |  |  |

| B[7]  | PCR[23] | SIUL           | _                  | ALT0    | GPI[23]             | _                     | _                      | _          | _                 | 4        | 3    | R5         |  |  |  |

|       |         | LINFlexD_0     | _                  | _       | RXD                 | PSMI[31];<br>PADSEL=1 |                        |            |                   |          |      |            |  |  |  |

|       |         | ADC_0          | _                  | _       | AN[0] <sup>3</sup>  | _                     |                        |            |                   |          |      |            |  |  |  |

| B[8]  | PCR[24] | SIUL           | _                  | ALT0    | GPI[24]             | _                     | _                      | _          | _                 | 4        | 7    | P7         |  |  |  |

|       |         | eTimer_0       | _                  | _       | ETC[5]              | PSMI[8];<br>PADSEL=2  | 2                      |            |                   |          |      |            |  |  |  |

|       |         | ADC_0          | _                  | _       | AN[1] <sup>3</sup>  | _                     |                        |            |                   |          |      |            |  |  |  |

| B[9]  | PCR[25] | SIUL           | _                  | ALT0    | GPI[25]             | _                     | _                      | _          | _                 | 52       | 2    | U7         |  |  |  |

|       |         | ADC_0<br>ADC_1 | _                  | _       | AN[11] <sup>3</sup> | _                     |                        |            |                   |          |      |            |  |  |  |

| B[10] | PCR[26] | SIUL           | _                  | ALT0    | GPI[26]             | _                     | _                      | _          | _                 | 5        | 3    | R8         |  |  |  |

|       |         | ADC_0<br>ADC_1 | _                  | _       | AN[12] <sup>3</sup> | _                     |                        |            |                   |          |      |            |  |  |  |

| B[11] | PCR[27] | SIUL           | _                  | ALT0    | GPI[27]             | _                     | _                      | _          | _                 | 5        | 4    | T8         |  |  |  |

|       |         | ADC_0<br>ADC_1 | _                  | _       | AN[13] <sup>3</sup> | _                     |                        |            |                   |          |      |            |  |  |  |

| B[12] | PCR[28] | SIUL           | _                  | ALT0    | GPI[28]             | _                     | _                      | _          | _                 | 5        | 5    | U8         |  |  |  |

|       |         | ADC_0<br>ADC_1 | _                  | _       | AN[14] <sup>3</sup> | _                     |                        |            |                   |          |      |            |  |  |  |

| B[13] | PCR[29] | SIUL           | _                  | ALT0    | GPI[29]             | _                     | _                      | _          | _                 | 6        | 0 1  | R10        |  |  |  |

|       |         | LINFlexD_1     | _                  | _       | RXD                 | PSMI[32];<br>PADSEL=0 |                        |            |                   |          |      |            |  |  |  |

|       |         | ADC_1          | _                  | _       | AN[0] <sup>3</sup>  | _                     | 1                      |            |                   |          |      |            |  |  |  |

| Port |          |            | Alternate          | Output            | Input     | Input mux             | Weak pull              | Pad s      | peed <sup>1</sup> | Pin #      |            |  |  |

|------|----------|------------|--------------------|-------------------|-----------|-----------------------|------------------------|------------|-------------------|------------|------------|--|--|

| name | PCR      | Peripheral | output<br>function | Output<br>mux sel | functions | select                | config during<br>reset | SRC<br>= 1 | SRC<br>= 0        | 144<br>pkg | 257<br>pkg |  |  |

| G[3] | PCR[99]  | SIUL       | GPIO[99]           | ALT0              | GPIO[99]  | _                     | _                      | М          | S                 | 104        | D17        |  |  |

|      |          | FlexPWM_0  | A[2]               | ALT1              | A[2]      | PSMI[22];<br>PADSEL=2 |                        |            |                   |            |            |  |  |

|      |          | eTimer_0   | _                  | _                 | ETC[4]    | PSMI[7];<br>PADSEL=3  |                        |            |                   |            |            |  |  |

| G[4] | PCR[100] | SIUL       | GPIO[100]          | ALT0              | GPIO[100] | _                     | _                      | М          | S                 | 100        | F17        |  |  |

|      |          | FlexPWM_0  | B[2]               | ALT1              | B[2]      | PSMI[26];<br>PADSEL=2 |                        |            |                   |            |            |  |  |

|      |          | eTimer_0   |                    | _                 | ETC[5]    | PSMI[8];<br>PADSEL=3  |                        |            |                   |            |            |  |  |

| G[5] | PCR[101] | SIUL       | GPIO[101]          | ALT0              | GPIO[101] | _                     | _                      | М          | S                 | 85         | N17        |  |  |

|      |          | FlexPWM_0  | X[3]               | ALT1              | X[3]      | PSMI[30];<br>PADSEL=2 |                        |            |                   |            |            |  |  |

|      |          | DSPI_2     | CS3                | ALT2              | _         | _                     | -                      |            |                   |            |            |  |  |

| G[6] | PCR[102] | SIUL       | GPIO[102]          | ALT0              | GPIO[102] | _                     | _                      | М          | S                 | 98         | G17        |  |  |

|      |          | FlexPWM_0  | A[3]               | ALT1              | A[3]      | PSMI[23];<br>PADSEL=3 |                        |            |                   |            |            |  |  |

| G[7] | PCR[103] | SIUL       | GPIO[103]          | ALT0              | GPIO[103] |                       | _                      | М          | S                 | 83         | P17        |  |  |

|      |          | FlexPWM_0  | B[3]               | ALT1              | B[3]      | PSMI[27];<br>PADSEL=3 |                        |            |                   |            |            |  |  |

| G[8] | PCR[104] | SIUL       | GPIO[104]          | ALT0              | GPIO[104] | _                     | _                      | М          | S                 | 81         | P16        |  |  |

|      |          | FlexRay    | DBG0               | ALT1              | _         | _                     |                        |            |                   |            |            |  |  |

|      |          | DSPI_0     | CS1                | ALT2              | _         | _                     |                        |            |                   |            |            |  |  |

|      |          | FlexPWM_0  | _                  | _                 | FAULT[0]  | PSMI[16];<br>PADSEL=2 |                        |            |                   |            |            |  |  |

|      |          | SIUL       | _                  | _                 | EIRQ[21]  | _                     | 1                      |            |                   |            |            |  |  |

| Dowt         |          |            | Alternate          | Outmut            | lmmut              | In most mosses        | Weak pull           | Pad s      | peed <sup>1</sup> |   | Pin #      |            |

|--------------|----------|------------|--------------------|-------------------|--------------------|-----------------------|---------------------|------------|-------------------|---|------------|------------|

| Port<br>name | PCR      | Peripheral | output<br>function | Output<br>mux sel | Input<br>functions | Input mux<br>select   | config during reset | SRC<br>= 1 | SRC<br>= 0        |   | 144<br>pkg | 257<br>pkg |

| H[1]         | PCR[113] | SIUL       | GPIO[113]          | ALT0              | GPIO[113]          | _                     | _                   | F          | S                 |   | _          | F1         |

|              |          | NPC        | MDO[6]             | ALT2              | _                  | _                     |                     |            |                   |   |            |            |

| H[2]         | PCR[114] | SIUL       | GPIO[114]          | ALT0              | GPIO[114]          | _                     | _                   | F          | S                 |   | _          | A4         |

|              |          | NPC        | MDO[5]             | ALT2              | _                  | _                     |                     |            |                   |   |            |            |

| H[3]         | PCR[115] | SIUL       | GPIO[115]          | ALT0              | GPIO[115]          | _                     | _                   | F          | S                 |   | _          | G1         |

|              |          | NPC        | MDO[4]             | ALT2              | _                  | _                     |                     |            |                   |   |            |            |

| H[4]         | PCR[116] | SIUL       | GPIO[116]          | ALT0              | GPIO[116]          | _                     | _                   | М          | S                 |   | _          | L16        |

|              |          | FlexPWM_1  | X[0]               | ALT1              | X[0]               | _                     |                     |            |                   |   |            |            |

|              |          | eTimer_2   | ETC[0]             | ALT2              | ETC[0]             | PSMI[39];<br>PADSEL=0 |                     |            |                   |   |            |            |

| H[5]         | PCR[117] | SIUL       | GPIO[117]          | ALT0              | GPIO[117]          | _                     | _                   | М          | S                 |   | _          | M17        |

|              |          | FlexPWM_1  | A[0]               | ALT1              | A[0]               | _                     |                     |            |                   |   |            |            |

|              |          | DSPI_0     | CS4                | ALT3              | _                  | _                     |                     |            |                   |   |            |            |

| H[6]         | PCR[118] | SIUL       | GPIO[118]          | ALT0              | GPIO[118]          | _                     | _                   | М          | S                 | _ | H17        |            |

|              |          | FlexPWM_1  | B[0]               | ALT1              | B[0]               | _                     |                     |            |                   |   |            |            |

|              |          | DSPI_0     | CS5                | ALT3              | _                  | _                     |                     |            |                   |   |            |            |

| H[7]         | PCR[119] | SIUL       | GPIO[119]          | ALT0              | GPIO[119]          | _                     | _                   | М          | S                 |   | _          | K16        |

|              |          | FlexPWM_1  | X[1]               | ALT1              | X[1]               | _                     |                     |            |                   |   |            |            |

|              |          | eTimer_2   | ETC[1]             | ALT2              | ETC[1]             | PSMI[40];<br>PADSEL=0 |                     |            |                   |   |            |            |

| H[8]         | PCR[120] | SIUL       | GPIO[120]          | ALT0              | GPIO[120]          | _                     | _                   | М          | S                 |   | _          | K15        |

|              |          | FlexPWM_1  | A[1]               | ALT1              | A[1]               | _                     | 1                   |            |                   |   |            |            |

|              |          | DSPI_0     | CS6                | ALT3              | _                  | _                     |                     |            |                   |   |            |            |

| H[9]         | PCR[121] | SIUL       | GPIO[121]          | ALT0              | GPIO[121]          | _                     | _                   | М          | S                 |   | _          | G16        |

|              |          | FlexPWM_1  | B[1]               | ALT1              | B[1]               | _                     |                     |            |                   |   |            |            |

|              |          | DSPI_0     | CS7                | ALT3              | _                  | _                     |                     |            |                   |   |            |            |

| Port |          |            | Alternate          | Output  | Input     | Input mux             | Weak pull              | Pad s      | peed <sup>1</sup> |  | Pin#       |            |  |  |  |  |

|------|----------|------------|--------------------|---------|-----------|-----------------------|------------------------|------------|-------------------|--|------------|------------|--|--|--|--|

| name | PCR      | Peripheral | output<br>function | mux sel | functions | select                | config during<br>reset | SRC<br>= 1 | SRC<br>= 0        |  | 144<br>pkg | 257<br>pkg |  |  |  |  |

| I[1] | PCR[129] | SIUL       | GPIO[129]          | ALT0    | GPIO[129] | _                     | _                      | М          | S                 |  |            | C12        |  |  |  |  |

|      |          | eTimer_2   | ETC[1]             | ALT1    | ETC[1]    | PSMI[40];<br>PADSEL=1 |                        |            |                   |  | 1          |            |  |  |  |  |

|      |          | DSPI_0     | CS5                | ALT2    | _         | _                     |                        |            |                   |  |            |            |  |  |  |  |

|      |          | FlexPWM_1  | _                  | _       | FAULT[1]  | _                     |                        |            |                   |  |            |            |  |  |  |  |

| I[2] | PCR[130] | SIUL       | GPIO[130]          | ALT0    | GPIO[130] | _                     | _                      | М          | S                 |  |            | F16        |  |  |  |  |

|      |          | eTimer_2   | ETC[2]             | ALT1    | ETC[2]    | PSMI[41];<br>PADSEL=1 |                        | _          |                   |  |            |            |  |  |  |  |

|      |          | DSPI_0     | CS6                | ALT2    | _         | _                     |                        |            |                   |  |            |            |  |  |  |  |

|      |          | FlexPWM_1  | _                  | _       | FAULT[2]  | _                     |                        |            |                   |  |            |            |  |  |  |  |

| I[3] | PCR[131] | SIUL       | GPIO[131]          | ALT0    | GPIO[131] | _                     | _                      | М          | S                 |  |            | E17        |  |  |  |  |

|      |          | eTimer_2   | ETC[3]             | ALT1    | ETC[3]    | PSMI[42];<br>PADSEL=1 |                        |            |                   |  |            |            |  |  |  |  |

|      |          | DSPI_0     | CS7                | ALT2    | _         | _                     |                        |            |                   |  |            |            |  |  |  |  |

|      |          | CTU_0      | EXT_TGR            | ALT3    | _         | _                     | =                      |            |                   |  |            |            |  |  |  |  |

|      |          | FlexPWM_1  | _                  | _       | FAULT[3]  | _                     |                        |            |                   |  |            |            |  |  |  |  |

| RDY  | PCR[132] | SIUL       | GPIO[132]          | ALT0    | GPIO[132] | _                     | _                      | F          | S                 |  | 1-         | K3         |  |  |  |  |

|      |          | NPC        | RDY                | ALT2    | _         | _                     |                        |            |                   |  |            |            |  |  |  |  |

<sup>1</sup> Programmable via the SRC (Slew Rate Control) bit in the respective Pad Configuration Register; S = Slow, M = Medium, F = Fast, SYM = Symmetric (for FlexRay)

### NOTE

Open Drain can be configured by the PCRn for all pins used as output (except FCCU\_F[0] and FCCU\_F[1]).

<sup>&</sup>lt;sup>2</sup> The default function of this pin out of reset is ALT1 (TDO).

<sup>&</sup>lt;sup>3</sup> Analog

| Table 8. Absolute maximum ra | atings <sup>1</sup> (continued | I) |

|------------------------------|--------------------------------|----|

|------------------------------|--------------------------------|----|

| Symbol              |    | Parameter                                                             | Conditions                  | Min                       | Max                  | Unit |

|---------------------|----|-----------------------------------------------------------------------|-----------------------------|---------------------------|----------------------|------|

| TV <sub>DD</sub>    | SR | Supply ramp rate                                                      | _                           | 3.0 × 10-6<br>(3.0 V/sec) | 0.5 V/μs             | V/µs |

| V <sub>IN</sub>     | SR | Voltage on any pin with respect to ground                             | _                           | -0.3                      | 6.0 <sup>5</sup>     | V    |

|                     |    | (Vss_hv_lo <sub>x</sub> )                                             | Relative to V <sub>DD</sub> | -0.3                      | $V_{DD} + 0.3^{5,6}$ |      |

| I <sub>INJPAD</sub> | SR | Injected input current on any pin during overload condition           | _                           | -10                       | 10                   | mA   |

| I <sub>INJSUM</sub> | SR | Absolute sum of all injected input currents during overload condition | _                           | -50                       | 50                   | mA   |

| T <sub>STG</sub>    | SR | Storage temperature                                                   | _                           | <b>-</b> 55               | 150                  | °C   |

<sup>&</sup>lt;sup>1</sup> Functional operating conditions are given in the DC electrical characteristics. Absolute maximum ratings are stress ratings only, and functional operation at the maxima is not guaranteed. Stress beyond the listed maxima may affect device reliability or cause permanent damage to the device.

## 3.3 Recommended operating conditions

Table 9. Recommended operating conditions (3.3 V)

| Symbol                                                            |    | Parameter                                                                                | Conditions | Min <sup>1</sup> | Max            | Unit |

|-------------------------------------------------------------------|----|------------------------------------------------------------------------------------------|------------|------------------|----------------|------|

| V <sub>DD_HV_REG</sub>                                            | SR | 3.3 V voltage regulator supply voltage —                                                 |            | 3.0              | 3.63           | V    |

| V <sub>DD_HV_IOx</sub>                                            | SR | 3.3 V input/output supply voltage                                                        | _          | 3.0              | 3.63           | V    |

| V <sub>SS_HV_IOx</sub>                                            | SR | Input/output ground voltage                                                              | _          | 0                | 0              | V    |

| $V_{DD\_HV\_FLA}$                                                 | SR | 3.3 V flash supply voltage                                                               | _          | 3.0              | 3.63           | V    |

| V <sub>SS_HV_FLA</sub>                                            | SR | Flash memory ground                                                                      | _          | 0                | 0              | V    |

| V <sub>DD_HV_OSC</sub>                                            | SR | 3.3 V crystal oscillator amplifier supply voltage                                        | _          | 3.0              | 3.63           | V    |

| V <sub>SS_HV_OSC</sub>                                            | SR | 3.3 V crystal oscillator amplifier reference voltage                                     | _          | 0                | 0              | V    |

| V <sub>DD_HV_ADR0</sub> <sup>2,3</sup><br>V <sub>DD_HV_ADR1</sub> | SR | 3.3 V / 5.0 V ADC_0 high reference voltage<br>3.3 V / 5.0 V ADC_1 high reference voltage | _          |                  | 5.5 or<br>3.63 | V    |

| V <sub>DD_HV_ADV</sub>                                            | SR | 3.3 V ADC supply voltage                                                                 | _          | 3.0              | 3.63           | V    |

| V <sub>SS_HV_AD0</sub><br>V <sub>SS_HV_AD1</sub>                  | SR | ADC_0 ground and low reference voltage ADC_1 ground and low reference voltage            | _          | 0                | 0              | V    |

| V <sub>SS_HV_ADV</sub>                                            | SR | 3.3 V ADC supply ground                                                                  | _          | 0                | 0              | V    |

| V <sub>DD_LV_REGCOR</sub> <sup>4</sup>                            | SR | Internal supply voltage                                                                  | _          | _                | _              | V    |

| V <sub>SS_LV_REGCOR</sub> <sup>5</sup>                            | SR | Internal reference voltage                                                               | _          | 0                | 0              | V    |

| V <sub>DD_LV_CORx</sub> <sup>2</sup>                              | SR | Internal supply voltage                                                                  | _          | _                | _              | V    |

$<sup>^2</sup>$  5.3 V for 10 hours cumulative over lifetime of device, 3.3 V +10% for time remaining.

<sup>&</sup>lt;sup>3</sup> Voltage overshoots during a high-to-low or low-to-high transition must not exceed 10 seconds per instance.

<sup>&</sup>lt;sup>4</sup> 6.4 V for 10 hours cumulative time, 6.0 V for time remaining.

Internal structures hold the input voltage less than the maximum voltage on all pads powered by VDDE supplies, if the maximum injection current specification is met and VDDE is within the operating voltage specifications.

$<sup>^{6}</sup>$  Only when  $V_{DD} < 5.2 \text{ V}$ .

83

<sup>3</sup> Data based on characterization results, not tested in production.

## 3.7 Static latch-up (LU)

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply overvoltage is applied to each power supply pin.

- A current injection is applied to each input, output and configurable I/O pin.

These tests are compliant with the EIA/JESD 78 IC latch-up standard.

Table 16. Latch-up results

| No. | Symbol |  | Parameter             | Conditions                                    | Class      |

|-----|--------|--|-----------------------|-----------------------------------------------|------------|

| 1   | LU SR  |  | Static latch-up class | T <sub>A</sub> = 125 °C conforming to JESD 78 | II level A |

## 3.8 Voltage regulator electrical characteristics

The voltage regulator is composed of the following blocks:

- High power regulator HPREG1 (internal ballast to support core current)

- High power regulator HPREG2 (external NPN to support core current)

- Low voltage detector (LVD\_MAIN\_1) for 3.3 V supply to IO (V<sub>DDIO</sub>)

- Low voltage detector (LVD\_MAIN\_2) for 3.3 V supply (V<sub>DDREG</sub>)

- Low voltage detector (LVD\_MAIN\_3) for 3.3 V flash supply (V<sub>DDFLASH</sub>)

- Low voltage detector (LVD\_DIG\_MAIN) for 1.2 V digital core supply (HPV<sub>DD</sub>)

- Low voltage detector (LVD\_DIG\_BKUP) for the self-test of LVD\_DIG\_MAIN

- High voltage detector (HVD\_DIG\_MAIN) for 1.2 V digital CORE supply (HPV $_{

m DD}$ )

- High voltage detector (HVD\_DIG\_BKUP) for the self-test of HVD\_DIG\_MAIN.

- Power on Reset (POR)

HPREG1 uses an internal ballast to support the core current. HPREG2 is used only when external NPN transistor is present on board to supply core current. The MPC5643L always powers up using HPREG1 if an external NPN transistor is present. Then the MPC5643L makes a transition from HPREG1 to HPREG2. This transition is dynamic. Once HPREG2 is fully operational, the controller part of HPREG1 is switched off.

The following bipolar transistors are supported:

- BCP68 from ON Semiconductor

- BCX68 from Infineon

Table 17. Recommended operating characteristics

| Symbol              | Parameter                                                     | Value            | Unit |

|---------------------|---------------------------------------------------------------|------------------|------|

| h <sub>FE</sub> (β) | DC current gain (Beta)                                        | 85 - 375         | _    |

| P <sub>D</sub>      | Maximum power dissipation @ T <sub>A</sub> =25°C <sup>1</sup> | 1.5              | W    |

| I <sub>CMaxDC</sub> | Maximum peak collector current                                | 1.0              | А    |

| VCE <sub>SAT</sub>  | Collector-to-emitter saturation voltage(Max)                  | 600 <sup>2</sup> | mV   |

| V <sub>BE</sub>     | Base-to-emitter voltage (Max)                                 | 1.0              | V    |

derating factor 12mW/degC

#### **Electrical characteristics**

Table 20. Current consumption characteristics

| Symbol                                                          |   | Parameter         | Conditions <sup>1</sup>                                                                                                    | Min | Тур | Max                                      | Unit |

|-----------------------------------------------------------------|---|-------------------|----------------------------------------------------------------------------------------------------------------------------|-----|-----|------------------------------------------|------|

| I <sub>DD_LV_FULL</sub><br>+ I <sub>DD_LV_PLL</sub>             | Т | Operating current | 1.2 V supplies T <sub>J</sub> = 25 °C V <sub>DD_LV_COR</sub> = 1.32 V                                                      | _   | _   | 50 mA+<br>2.18 mA*f <sub>CPU</sub> [MHz] | mA   |

|                                                                 |   |                   | 1.2 V supplies<br>T <sub>J</sub> = 150 °C<br>V <sub>DD_LV_COR</sub> = 1.32 V                                               | _   | _   | 80 mA+<br>2.50 mA*f <sub>CPU</sub> [MHz] |      |

| I <sub>DD_LV_TYP</sub><br>+ I <sub>DD_LV_PLL</sub> <sup>2</sup> | Т | Operating current | 1.2 V supplies<br>T <sub>J</sub> = 25 °C<br>V <sub>DD_LV_COR</sub> = 1.32 V                                                | _   | _   | 26 +<br>2.10 mA*f <sub>CPU</sub> [MHz]   | mA   |

|                                                                 |   |                   | 1.2 V supplies<br>$T_J = 150 ^{\circ}\text{C}$<br>$V_{DD\_LV\_COR} = 1.32 ^{\circ}\text{V}$                                | _   | _   | 41 mA+<br>2.30 mA*f <sub>CPU</sub> [MHz] |      |

| IDD_LV_BIST<br>+ IDD_LV_PLL                                     | Т | Operating current | 1.2 V supplies during LBIST (full LBIST configuration) T <sub>J</sub> = 25 °C V <sub>DD_LV_COR</sub> = 1.32 V              | _   | _   | 250                                      | mA   |

|                                                                 |   |                   | 1.2 V supplies during<br>LBIST (full LBIST<br>configuration)<br>T <sub>J</sub> = 150 °C<br>V <sub>DD_LV_COR</sub> = 1.32 V | _   | _   | 290                                      |      |

| I <sub>DD_LV_TYP</sub><br>+ I <sub>DD_LV_PLL</sub> <sup>2</sup> | Р | Operating current | 1.2 V supplies  T <sub>J</sub> = 25 °C  V <sub>DD_LV_COR</sub> = 1.32 V  LSM mode                                          | _   | _   | 279                                      | mA   |

|                                                                 |   |                   | $T_J$ = 150 °C $V_{DD\_LV\_COR}$ = 1.32 V LSM mode                                                                         | _   | _   | 318                                      | mA   |

| I <sub>DD_LV_TYP</sub> + I <sub>DD_LV_PLL</sub> <sup>2</sup>    | Т | Operating current | 1.2V supplies Tj=105°C V <sub>DD_LV_COR</sub> = 1.2V LSM mode                                                              | _   | _   | 275                                      | mA   |

|                                                                 |   |                   | 1.2V supplies Tj=125°C V <sub>DD_LV_COR</sub> = 1.2V LSM mode                                                              | _   | _   | 299                                      | mA   |

95

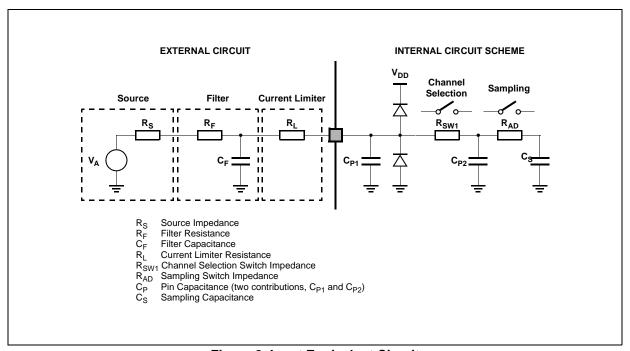

A real filter can typically be obtained by using a series resistance with a capacitor on the input pin (simple RC filter). The RC filtering may be limited according to the value of source impedance of the transducer or circuit supplying the analog signal to be measured. The filter at the input pins must be designed taking into account the dynamic characteristics of the input signal (bandwidth) and the equivalent input impedance of the ADC itself.

In fact a current sink contributor is represented by the charge sharing effects with the sampling capacitance:  $C_S$  and  $C_{p2}$  being substantially a switched capacitance, with a frequency equal to the conversion rate of the ADC, it can be seen as a resistive path to ground. For instance, assuming a conversion rate of 1 MHz, with  $C_{p2} + CS$  equal to 7.5 pF, a resistance of 133 k $\Omega$  is obtained ( $R_{EQ} = 1 / (fS*(C_{p2} + C_S))$ ), where fS represents the conversion rate at the considered channel). To minimize the error induced by the voltage partitioning between this resistance (sampled voltage on  $C_s$ ) and the sum of  $R_S + R_F$ , the external circuit must be designed to respect the Equation 4:

$$V_A \bullet \frac{R_S + R_F}{R_{EQ}} < \frac{1}{2}LSB$$

Eqn. 4

Equation 4 generates a constraint for external network design, in particular on resistive path. Internal switch resistances ( $R_{SW}$  and  $R_{AD}$ ) can be neglected with respect to external resistances.

Figure 8. Input Equivalent Circuit

A second aspect involving the capacitance network shall be considered. Assuming the three capacitances  $C_F$ ,  $C_{P1}$  and  $C_{P2}$  are initially charged at the source voltage  $V_A$  (refer to the equivalent circuit reported in Figure 8): A charge sharing phenomenon is installed when the sampling phase is started (A/D switch close).

Table 39. DSPI timing (continued)

| No. | Symbol          |   | Symbol                     |                             | Parameter | Conditions | Min | Max | Unit |

|-----|-----------------|---|----------------------------|-----------------------------|-----------|------------|-----|-----|------|

| 12  | t <sub>HO</sub> | D | Data hold time for outputs | Master (MTFE = 0)           | -2        | _          | ns  |     |      |

|     |                 |   |                            | Slave                       | 6         | _          |     |     |      |

|     |                 |   |                            | Master (MTFE = 1, CPHA = 0) | 6         | _          |     |     |      |

|     |                 |   |                            | Master (MTFE = 1, CPHA = 1) | -2        | _          |     |     |      |

Slave Receive Only Mode can operate at a maximum frequency of 60 MHz. In this mode, the DSPI can receive data on SIN, but no valid data is transmitted on SOUT.

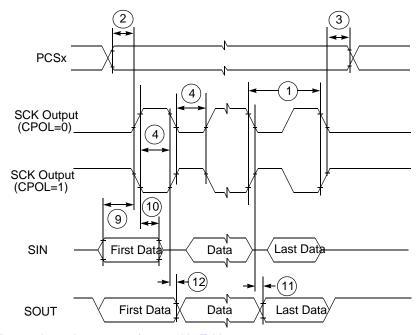

Note: The numbers shown are referenced in Table 39.

Figure 30. DSPI classic SPI timing — master, CPHA = 0

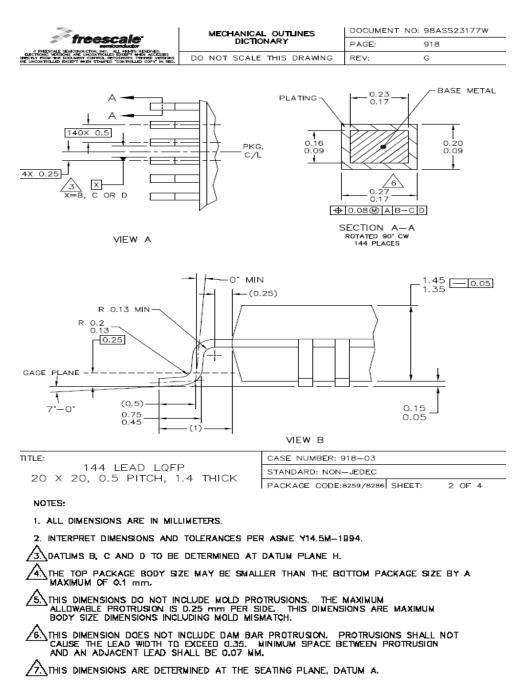

Figure 40. 144 LQFP package mechanical drawing (2 of 2)

#### **Document revision history**

Table 40. Orderable part number summary (continued)

| Part number <sup>1</sup> | Flash/SRAM  | Package              | Speed<br>(MHz) <sup>2</sup> | Other features           |

|--------------------------|-------------|----------------------|-----------------------------|--------------------------|

| SPC5643LF2MLQ8           | 1 MB/128 KB | 144 LQFP (Pb free)   | 80                          | No FlexRay<br>-40-125 °C |

| SPC5643LF2MMM8           | 1 MB/128 KB | 257 MAPBGA (Pb free) | 80                          | No FlexRay<br>-40-125 °C |

| SPC5643LFF2VLQ8          | 1 MB/128 KB | 144 LQFP (Pb free)   | 80                          | FlexRay<br>-40-105 °C    |

| SPC5643LFF2VMM8          | 1 MB/128 KB | 257 MAPBGA (Pb free) | 80                          | FlexRay<br>-40-105 °C    |

| SPC5643LF2VLQ8           | 1 MB/128 KB | 144 LQFP (Pb free)   | 80                          | No FlexRay<br>-40-105 °C |

| SPC5643LF2VMM8           | 1 MB/128 KB | 257 MAPBGA (Pb free) | 80                          | No FlexRay<br>-40-105 °C |

All packaged devices are SPC, rather than MPC or SPC, until product qualifications are complete. The unpackaged device prefix is PCC, rather than SCC, until product qualification is complete. Not all configurations are available in the SPC parts.

# 6 Document revision history

Table 41 summarizes revisions to this document.

Table 41. Revision history

| Revision | Date       | Description of changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | 2 Mar 2009 | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2        | 5 May 2009 | Updated, Advance Information.  —Revised SINAD/SNR specifications.  — Updated pinout and pin multiplexing information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3        | 5 Oct 2009 | Updated, Advance Information, Public release.  — Throughout this document, added information for 257 MAPBGA package.  — Updated Table 1, MPC5643L device summary.  — Updated Section 1.3, Feature Details.  — Updated pin-out and pin multiplexing tables.  — In Section 3, Electrical characteristics, added symbols for signal characterization methods.  — In Table 8, updated maximum ratings.  — In Table 10 and Table 11, removed moving-air thermal characteristics.  — Updated Section 3.8, Voltage regulator electrical characteristics.  — Updated Section 3.14, ADC electrical characteristics.  — Updated Section 3.15, Flash memory electrical characteristics.  — Updated Section 3.17.1, RESET pin characteristics.  — Removed External interrupt timing (IRQ pin) timing specifications.  — Updated Section 5, Ordering information. |

MPC5643L Microcontroller Data Sheet, Rev. 9

<sup>&</sup>lt;sup>2</sup> This speed rating does not include the  $\pm 2\%$  for frequency modulation.

Table 41. Revision history (continued)

| Revision     | Date                   | Description of changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6<br>(cont.) | 11 Mar 2011<br>(cont.) | In the "ADC conversion characteristics" table:  • Changed DNL min from -2 to -1.  • Changed OFS min from -2 to -6.  • Changed OFS max from 2 to 6.  • Changed GNE min from -2 to -6.  • Changed GNE max from 2 to 6.  • Changed SNR min from 69 to 67.  • Changed TUE min (without current injection) from -6 to -8.  • Changed TUE max (without current injection) from 6 to 8.  • Changed TUE min (with current injection) from -8 to -10.  • Changed TUE max (with current injection) from 8 to 10.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 7            | 25 Mar 2011            | In the "Description" section, changed the first paragraph and its bullets to paragraph form only.  In the "Voltage regulator electrical specifications" table, changed the C <sub>V1V2</sub> Min value from "—" to 300 nF, and changed the Max value from 300 nF to 900 nF.  In the "Supply current characteristics (cut2)" table, corrected the "I <sub>DD_LV_TYP</sub> + I <sub>DD_LV_PLL</sub> " values as follows:  • Changed the maximum value for "T <sub>J</sub> = ambient" from "279 mA+ 2.10 mA*f <sub>CPU</sub> " to "279 mA".  • Changed the maximum value for "T <sub>J</sub> = 150 °C" from "318 mA+ 2.30 mA*f <sub>CPU</sub> " to 318 mA.  • Changed the frequency multiplier "f <sub>CPU</sub> " in the max value to read "f <sub>CPU</sub> [MHz]" for "I <sub>DD_LV_FULL</sub> + I <sub>DD_LV_PLL</sub> " and "I <sub>DD_LV_TYP</sub> + I <sub>DD_LV_PLL</sub> ".  In the "JTAG pin AC electrical characteristics" table:  • Changed t <sub>JCYC</sub> min from 100ns to 62.5ns.  • Changed t <sub>JCYC</sub> min from 40ns to 62.5ns.  • Changed t <sub>TCYC</sub> min from 40ns to 62.5 ns.  • Changed t <sub>JCYC</sub> min from 40ns to 62.5 ns.  • Changed t <sub>JCYC</sub> min from 40ns to 62.5 ns.  • Changed t <sub>JCYC</sub> min from 40ns to 62.5 ns.  • Changed t <sub>JCYC</sub> min from 40ns to 62.5 ns.  • Changed t <sub>JCYC</sub> min from 40ns to 62.5 ns.  • Changed t <sub>JCYC</sub> min from 40ns to 62.5 ns.  • Changed t <sub>JCYC</sub> min from 40ns to 62.5 ns.  • Changed t <sub>JCYC</sub> min from 40ns to 62.5 ns.  • Changed t <sub>JCYC</sub> min from 40ns to 62.5 ns.  • Changed t <sub>JCYC</sub> min from 40ns to 62.5 ns.  • Changed t <sub>JCYC</sub> min from 40ns to 62.5 ns.  • Changed t <sub>JCYC</sub> min from 40ns to 62.5 ns.  • Changed t <sub>JCYC</sub> min from 40ns to 62.5 ns.  • Changed t <sub>JCYC</sub> min from 40ns to 62.5 ns.  • Changed t <sub>JCYC</sub> min from 40ns to 62.5 ns.  • Changed t <sub>JCYC</sub> min from 40ns to 62.5 ns.  • Changed t <sub>JCYC</sub> min from 40ns to 62.5 ns. |

MPC5643L Microcontroller Data Sheet, Rev. 9 Freescale Semiconductor 131

### **Document revision history**

Table 41. Revision history (continued)

| Revision | Date        | Description of changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision | Date        | <ul> <li>Added Table 29 (MPC5643L SWG Specifications)</li> <li>In Table 29 (MPC5643L SWG Specifications)</li> <li>Added table footnote for Common Mode.</li> <li>Changed text from "internal device pad resistance" to "internal device routing resistance".</li> <li>Added Figure 26 in Section 3.20.4, "Nexus timing".</li> <li>In Table 30 (Pad AC specifications (3.3 V , IPP_HVE = 0 )), removed the row of pad "Pull Up/Downc(3.6 V max)".</li> <li>In Table 40 (Orderable part number summary) and Figure 43, updated part numbers (changed 'PPC' to 'SPC' and 'F0' to 'F2').</li> <li>Replaced Figure 39, Figure 40, Figure 41, Figure 42 with the new versions.</li> <li>InTable 18 (Voltage regulator electrical specifications), changed the symbol of spec external decoupling capacitor from SR to C<sub>ext</sub>.</li> <li>In Figure 4, changed the ESR range in note text to 1 mW to 100 mW from 30 mW to 150 mW.</li> <li>In Section 1.5.32, "Sine Wave Generator (SWG)" removed the following text: Frequency range from 1kHz to 50kHz.</li> <li>Sine wave amplitude from 0.47 V to 2.26 V.</li> <li>In Table 20 (Current consumption characteristics)", changed symbol from 'C' to 'T', added "operating current" to the parameter and updated the maximum value for five additional RunIDD parameters.</li> <li>In Table 20 (Current consumption characteristics), changed "Conditions" from '1.2 V supplies' to '1.2 V supplies during LBIST (full LBIST configuration)" for all the parameters.</li> <li>Removed Table "SWG electrical characteristics".</li> <li>In Table 18 (Voltage regulator electrical specifications), changed the "Digital supply high voltage detector upper threshold low limit (After a destructive reset initialization phase completion)" from 1.43V to 1.38V.</li> <li>Added Table 17 (Recommended operating characteristics).</li> <li>Updated the IDD values in Table 20 (Current consumption characteristics). Changed conditions text from "1.2 supplies during LBIST (full LBIST configuration)" to "1.2 V supplies" for all the IDD parameters except I<sub>DD_LV_BIST</sub>+I<sub>DD_LV_PL</sub></li></ul> |

| 8.1      | 07 May 2012 | Deleted the Footer "Preliminary-Subject to Change Without Notice" label.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

#### How to Reach Us:

Home Page: freescale.com

Web Support:

freescale.com/support