Welcome to **E-XFL.COM**

<u>Embedded - Microcontrollers - Application</u>

<u>Specific</u>: Tailored Solutions for Precision and Performance

Embedded - Microcontrollers - Application Specific represents a category of microcontrollers designed with unique features and capabilities tailored to specific application needs. Unlike general-purpose microcontrollers, application-specific microcontrollers are optimized for particular tasks, offering enhanced performance, efficiency, and functionality to meet the demands of specialized applications.

What Are <u>Embedded - Microcontrollers - Application Specific</u>?

Annication anacific microcontrollars are anaineared to

| Details                 |                                                                           |

|-------------------------|---------------------------------------------------------------------------|

| Product Status          | Obsolete                                                                  |

| Applications            | Automotive                                                                |

| Core Processor          | XC800                                                                     |

| Program Memory Type     | FLASH (48kB)                                                              |

| Controller Series       | -                                                                         |

| RAM Size                | 3.25K x 8                                                                 |

| Interface               | LIN, SSI, UART                                                            |

| Number of I/O           | 11                                                                        |

| Voltage - Supply        | 3V ~ 27V                                                                  |

| Operating Temperature   | -40°C ~ 150°C (TJ)                                                        |

| Mounting Type           | Surface Mount                                                             |

| Package / Case          | 48-VFQFN Exposed Pad                                                      |

| Supplier Device Package | PG-VQFN-48-29                                                             |

| Purchase URL            | https://www.e-xfl.com/product-detail/infineon-technologies/tle9833qxxuma2 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Edition 2012-03-08

Published by Infineon Technologies AG 81726 Munich, Germany © 2012 Infineon Technologies AG All Rights Reserved.

#### **Legal Disclaimer**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

## **Table of Contents**

# **Table of Contents**

|                 | Table of Contents                        | . 3 |

|-----------------|------------------------------------------|-----|

| 1               | Summary of Features                      | . 5 |

| 1.1             | Device Types / Ordering Information      |     |

| 1.2             | Abbreviations                            | . 7 |

| 2               | General Device Information               | . 9 |

| _<br>2.1        | Pin Configuration                        |     |

| 2.2             | Pin Definitions and Functions            |     |

| 3               | Functional Description                   |     |

| <b>ა</b><br>3.1 | Power Management Unit (PMU)              |     |

| 3.1.1           | Voltage Regulator 5.0V (VDDP)            |     |

| 3.1.1           | Voltage Regulator 1.5V (VDDC)            |     |

| 3.1.2           | External Voltage Regulator 5.0V (VDDEXT) |     |

| 3.1.3           | System Control Unit                      |     |

| 3.2.1           | System Control Unit - Power Modules      |     |

| 3.2.2           | System Control Unit - Digital Part       |     |

| 3.3             | XC800 Core                               |     |

| 3.4             | Memory Architecture                      |     |

| 3.5             | Flash Memory                             |     |

| 3.6             | Watchdog Timer 1 (WDT1)                  |     |

| 3.7             | Watchdog Timer (WDT)                     |     |

| 3.8             | Interrupt System                         |     |

| 3.9             | Multiplication/Division Unit             |     |

| 3.10            | Parallel Ports                           |     |

| 3.11            | Timer 0 and Timer 1                      |     |

| 3.12            | Timer 2 and Timer 21                     |     |

| 3.13            | Timer 3                                  | 43  |

| 3.14            | Capture/Compare Unit 6 (CCU6)            | 44  |

| 3.15            | UART                                     | 46  |

| 3.16            | LIN Transceiver                          | 47  |

| 3.17            | High-Speed Synchronous Serial Interface  | 47  |

| 3.18            | Measurement Unit                         | 49  |

| 3.19            | Measurement Core Module (incl. ADC2)     | 51  |

| 3.20            | Analog Digital Converter (ADC1)          |     |

| 3.21            | High Voltage Monitor Input               | 53  |

| 3.22            | High Side Switches                       |     |

| 3.23            | Low Side Switches                        |     |

| 3.24            | PWM Generator                            |     |

| 3.25            | Debug System                             | 57  |

| 4               | Application Information                  | 58  |

| 4.1             | Electric Drive Application               | 58  |

| 4.2             | Connection of N.C. Pins                  | 59  |

| 4.3             | Connection of ADCGND Pin                 | 59  |

| 4.4             | Connection of Exposed Pad                | 59  |

| 4.5             | Voltage Regulators-Blocking Capacitors   | 59  |

| 4.6             | Additional External Components           |     |

| 4.7             | ESD Tests                                | 60  |

| 5               | Electrical Characteristics               | 61  |

|                 |                                          |     |

**General Device Information**

# 2 General Device Information

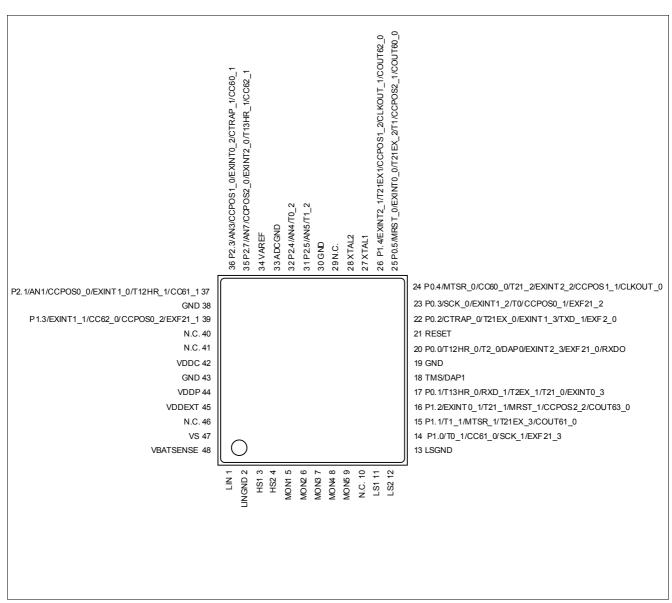

# 2.1 Pin Configuration

Figure 1 TLE9833QX pin configuration, VQFN-48-29 package (top view)

## **General Device Information**

Table 3 Pin Definitions and Functions (cont'd)

| Symbol     | Pin Number            | Туре | Reset<br>State | Function                                            |  |  |  |  |

|------------|-----------------------|------|----------------|-----------------------------------------------------|--|--|--|--|

| Others     |                       |      | ·              |                                                     |  |  |  |  |

| VAREF      | 34                    | I/O  | 0              | 5V ADC1 reference voltage                           |  |  |  |  |

| XTAL1      | 27                    | I    | I              | External oscillator input                           |  |  |  |  |

| XTAL2      | 28                    | 0    | Hi-Z           | External oscillator output                          |  |  |  |  |

| TMS        | 18                    | I    | I/PD           | TMS test mode select input DAP1 Debug Access Port 1 |  |  |  |  |

| RESET      | 21                    | I/O  | I/O/PU         | Reset input, not available during Sleep Mode        |  |  |  |  |

| VBAT_SENSE | 48                    | I    | I              | Battery supply voltage sense input                  |  |  |  |  |

| N.C.       | 10, 29, 40,<br>41, 46 | _    | _              | Not connected - can be connected to GND             |  |  |  |  |

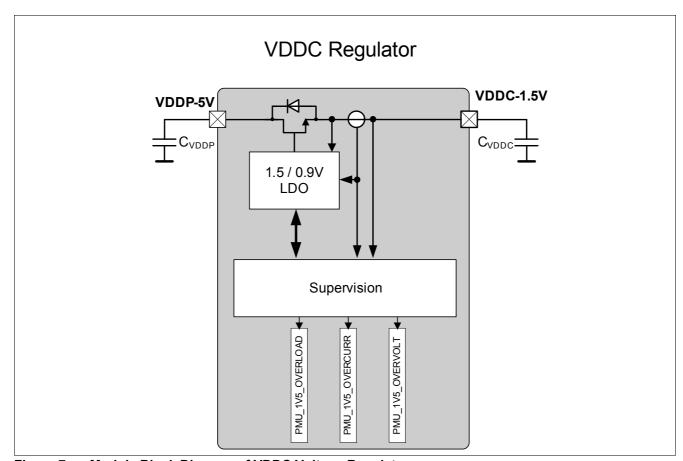

# 3.1.2 Voltage Regulator 1.5V (VDDC)

This module represents the 1.5 V voltage regulator, which serves as core supply for the 8-bit  $\mu$ C and other chip internal analog 1.5 V functions (e.g. 8 Bit ADC). To further reduce the current consumption of the 8-bit MCU during Stop Mode the output voltage is optionally reduced to 0.9 V.

#### **Features**

- 1.5 V low-drop voltage regulator

- Optional 0.9 V in Stop Mode

- · Current limitation

- · Overcurrent monitoring and shutdown with MCU signalling (interrupt)

- Overvoltage monitoring with MCU signalling (interrupt)

- Undervoltage monitoring with MCU signalling (interrupt)

- Pull-down current source at the output for Sleep Mode (100 μA)

The output capacitor  $C_{VDDC}$  is mandatory to ensure a proper regulator functionality.

Figure 7 Module Block Diagram of VDDC Voltage Regulator

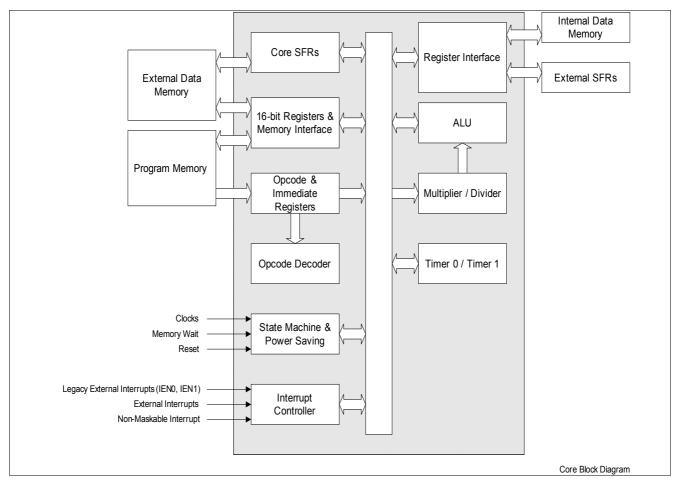

**Figure 10** shows the functional blocks of the XC800 Core. The XC800 Core consists mainly of the instruction decoder, the arithmetic section, the program control section, the access control section, and the interrupt controller.

The instruction decoder decodes each instruction and accordingly generates the internal signals required to control the functions of the individual units within the core. These internal signals have an effect on the source and destination of data transfers and control the ALU processing.

Figure 10 XC800 Core Block Diagram

The arithmetic section of the processor performs extensive data manipulation and consists of the arithmetic/logic unit (ALU), A register, B register and PSW register. The ALU accepts 8-Bit data words from one or two sources and generates an 8-Bit result under the control of the instruction decoder. The ALU performs both arithmetic and logic operations. Arithmetic operations include add, subtract, multiply, divide, increment, decrement, BCD-decimal-add-adjust and compare. Logic operations include AND, OR, Exclusive OR, complement and rotate (right, left or swap nibble (left four)). Also included is a Boolean unit performing the Bit operations as set, clear, complement, jump-if-set, jump-if-not-set, jump-if-set-and-clear and move to/from carry. The ALU can perform the Bit operations of logical AND or logical OR between any addressable Bit (or its complement) and the carry flag, and place the new result in the carry flag.

The program control section controls the sequence in which the instructions stored in program memory are executed. The 16-Bit program counter (PC) holds the address of the next instruction to be executed. The conditional branch logic enables internal and external events to the processor to cause a change in the program execution sequence.

The access control unit is responsible for the selection of the on-chip memory resources. The interrupt requests from the peripheral units are handled by the interrupt controller unit.

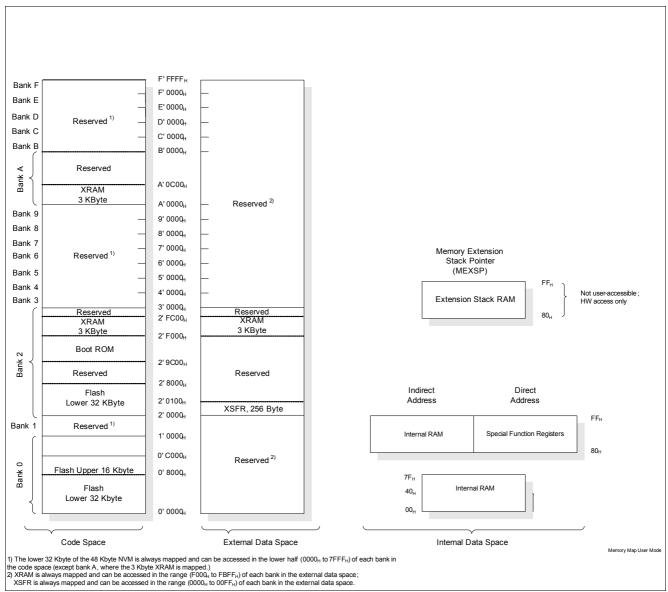

## 3.4 Memory Architecture

The TLE9833QX CPU manipulates operands in the following memory spaces:

- 48 kByte of Flash memory in code space

- BootROM memory in code space

- 256 Byte of internal RAM data memory in internal data space

- 3 kByte of XRAM memory in code space and external data space (XRAM can be read/written as program memory or external data memory)

- 128 Byte of special function registers SFR in internal data space

- 256 Byte of special function registers XSFR in external data space.

Figure 11 illustrates the memory address spaces of the TLE9833QX.

Figure 11 TLE9833QX Memory Map

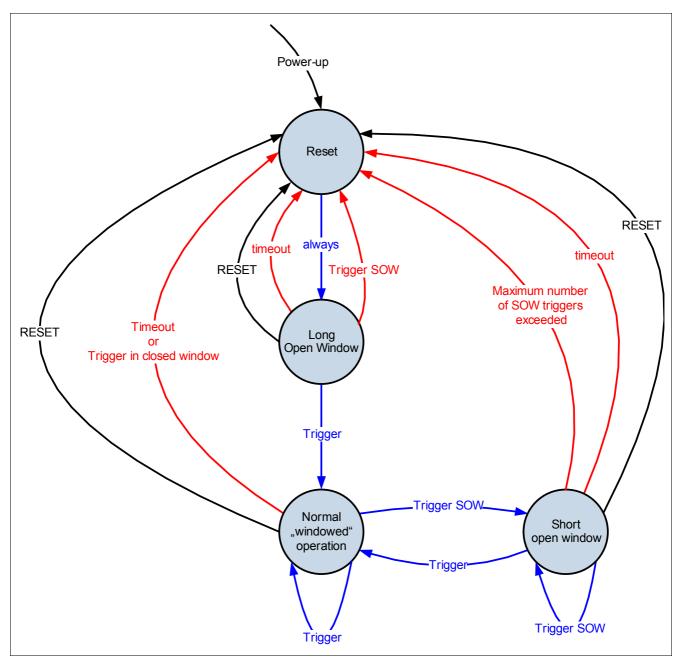

Figure 12 Watchdog Timer 1 Behavior

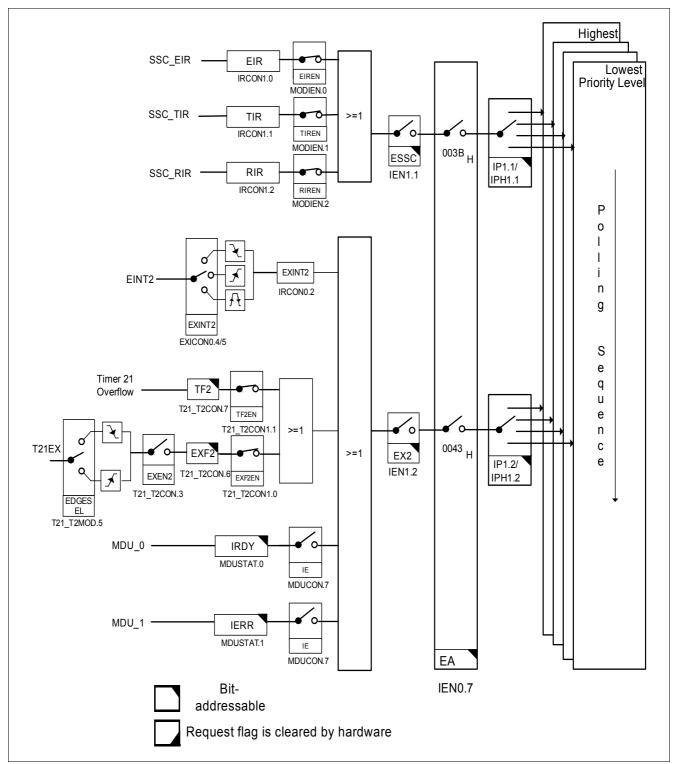

Figure 16 Interrupt Request Sources (Part 3)

## 3.15 **UART**

The UART provides a full-duplex asynchronous receiver/transmitter, i.e. it can transmit and receive simultaneously. It is also receive-buffered, i.e. it can commence reception of a second Byte before a previously received Byte has been read from the receive register. However, if the first Byte still has not been read by the time reception of the second Byte is complete, one of the Bytes will be lost. The serial port receive and transmit registers are both accessed at Special Function Register (SFR) SBUF. Writing to SBUF loads the transmit register, and reading SBUF accesses a physically separate receive register.

#### **UART Features**

- Full-duplex asynchronous modes

- 8-Bit or 9-Bit data frames, LSB first

- fixed or variable baud rate

- Receive buffered

- Multiprocessor communication

- Interrupt generation on the completion of a data transmission or reception

- · Baud-rate generator with fractional divider for generating a wide range of baud rates

- Hardware logic for break and synch Byte detection

#### **UART Modes**

The UART can be used in four different modes. In mode 0, it operates as an 8-Bit shift register. In mode 1, it operates as an 8-Bit serial port. In modes 2 and 3, it operates as a 9-Bit serial port. The only difference between mode 2 and mode 3 is the baud rate, which is fixed in mode 2 but variable in mode 3. The variable baud rate is set by the underflow rate on the dedicated baud-rate generator.

The different modes are selected by setting Bits SM0 and SM1 to their corresponding values, as shown in Table 9.

Table 9 UART Modes

| SM0 | SM1 | Operating Mode               | Baud Rate     |

|-----|-----|------------------------------|---------------|

| 0   | 0   | Mode 0: 8-Bit shift register | $f_{PCLK}$ /2 |

| 0   | 1   | Mode 1: 8-Bit shift UART     | Variable      |

| 1   | 0   | Mode 2: 9-Bit shift UART     | $f_{PCLK}/64$ |

| 1   | 1   | Mode 3: 9-Bit shift UART     | Variable      |

Data Sheet 46 Rev. 1.1, 2012-03-08

**Application Information**

# 4 Application Information

# 4.1 Electric Drive Application

**Figure 31** shows the TLE9833QX in an electric drive application setup controlling a DC-brush motor. The two Low Side Switches are controlling a relay each. An external FET allows to control the window lift motor with a PWM signal as generated with the CCU6 module of the microcontroller.

Note: The following information is given as a hint for the implementation of the device only and shall not be regarded as a description or warranty of a certain functionality, condition or quality of the device.

Figure 31 Simplified Application Diagram

**Application Information**

## 4.2 Connection of N.C. Pins

It is recommended to connect N.C. pins to GND unless otherwise specified. Since pins 10 and 46 are located next to high voltage pins (VS, MON5, LS1) these 2 N.C. pins can be also left unconnected in order to avoid huge current flow and damage of the system in case of short-circuit.

#### 4.3 Connection of ADCGND Pin

The ADCGND pin is chip-internal connected to reference ground. In order to provide full offset compensation and achieve full accuracy of ADC1 the ADCGND pin must not be connected to board ground. ADCGND pin should be connected with a capacitor (100 nF) to VAREF only.

## 4.4 Connection of Exposed Pad

It is recommended to connect the exposed pad to GND.

## 4.5 Voltage Regulators-Blocking Capacitors

Table 11 External Component Recommendation

| Symbol              | Function                         | Comment                                                |  |  |  |

|---------------------|----------------------------------|--------------------------------------------------------|--|--|--|

| C <sub>VS</sub>     | blocking capacitor at VS pin     | $>$ 20 $\mu$ F Elco + 100 nF Ceramic, ESR < 1 $\Omega$ |  |  |  |

| C <sub>VDDP</sub>   | blocking capacitor at VDDP pin   | 1 μF typ. + 100 nF Ceramic, ESR < 1 Ω                  |  |  |  |

| C <sub>VDDEXT</sub> | blocking capacitor at VDDEXT pin | 100 nF typ., ESR < 1 Ω                                 |  |  |  |

| C <sub>VDDC</sub>   | blocking capacitor at VDDC pin   | > 330 nF + 100 nF Ceramic, ESR < 1 Ω                   |  |  |  |

| C <sub>VAREF</sub>  | blocking capacitor at VAREF pin  | > 100 nF, ESR < 1 Ω                                    |  |  |  |

## 4.6 Additional External Components

Table 12 External Component Recommendation

| Symbol            | Function                         | Comment |

|-------------------|----------------------------------|---------|

| C <sub>HSx</sub>  | HF blocking capacitor at HSx pin | 6.8 nF  |

| $R_{MONx}$        | resistor at MONx pin             | 1 kΩ    |

| R <sub>VBAT</sub> | resistor at VBAT_SENSE pin       | 1 kΩ    |

# 5.5 Parallel Ports (GPIO)

# 5.5.1 Functional Range

## Table 25 Functional Range

$V_{\rm S}$  = 5.5 V to 27 V,  $T_{\rm j}$  = -40° C to +150 °C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                        | Symbol              | Values |      | Values |    | Note /         | Number  |

|----------------------------------|---------------------|--------|------|--------|----|----------------|---------|

|                                  |                     | Min.   | Тур. | Max.   |    | Test Condition |         |

| Output current on any pin        | $I_{OH}$ , $I_{OL}$ | _      | _    | 20     | mA | 1) 2)          | P_5.5.1 |

| Max output current for all GPIOs | $I_{max}$           | _      | _    | 60     | mA | 1) 2)          | P_5.5.2 |

<sup>1)</sup> One of these limits must be kept.

#### 5.5.2 DC Parameters

These parameters apply to the IO voltage range, 4.5 V  $\leq V_{DDP} \leq$  5.5 V.

Note: Operating Conditions apply.

Keeping signal levels within the limits specified in this table ensures operation without overload conditions. For signal levels outside these specifications, also refer to the specification of the overload current  $I_{\text{OV}}$ .

#### Table 26 DC Characteristics

$V_{\rm S}$  = 5.5 V to 27 V,  $T_{\rm j}$  = -40° C to +150 °C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                       | Symbol       |                          | Values | <b>;</b>               | Unit | Note /                                                                              | Number   |  |

|-------------------------------------------------|--------------|--------------------------|--------|------------------------|------|-------------------------------------------------------------------------------------|----------|--|

|                                                 |              | Min.                     | Тур.   | Max.                   |      | Test Condition                                                                      |          |  |

| Input low voltage (all except XTAL1)            | $V_{IL}$     | -0.3                     | _      | 0.3 x V <sub>DDP</sub> | V    | _                                                                                   | P_5.5.3  |  |

| Input high voltage (all except XTAL1)           | $V_{IH}$     | $0.7 \times V_{\rm DDP}$ | -      | V <sub>DDP</sub> + 0.3 | V    | _                                                                                   | P_5.5.4  |  |

| Input Hysteresis <sup>1)</sup>                  | HYS          | 0.11 x V <sub>DDP</sub>  | -      | _                      | V    | Series resistance<br>= 0 Ω                                                          | P_5.5.5  |  |

| Output low voltage                              | $V_{OL}$     | _                        | _      | 1.0                    | V    | $^{2)}I_{\rm OL} \leq I_{\rm OLmax}$                                                | P_5.5.6  |  |

| Output low voltage                              | $V_{OL}$     | _                        | _      | 0.4                    | V    | $^{2)}I_{\rm OL} \leq ^{3)}I_{\rm OLnom}$                                           | P_5.5.7  |  |

| Output high voltage <sup>4)</sup>               | $V_{OH}$     | V <sub>DDP</sub> - 1.0   | _      | _                      | V    | <sup>2)</sup> $I_{\text{OH}} \ge I_{\text{OHmax}}$                                  | P_5.5.8  |  |

| Output high voltage                             | $V_{OH}$     | V <sub>DDP</sub> - 0.4   | _      | _                      | V    | $^{2)3)}I_{\mathrm{OH}} \ge I_{\mathrm{OHnom}}$                                     | P_5.5.9  |  |

| Input leakage current (Port 2)                  | $I_{OZ1}$    | -400                     | _      | +400                   | nA   | $T_{\rm J} \le 85^{\circ}{\rm C},$<br>0 V < $V_{\rm IN} < V_{\rm DDP}$              | P_5.5.10 |  |

| Input leakage current (all other) <sup>5)</sup> | $I_{ m OZ2}$ | -5                       | _      | +5                     | μΑ   | $T_{\rm J} \leq 85^{\circ}{\rm C},$ $0.45 \ {\rm V} < \ V_{\rm IN}$ $< V_{\rm DDP}$ | P_5.5.11 |  |

<sup>2)</sup> Not subject to production test, specified by design

#### Table 26 DC Characteristics

$V_{\rm S}$  = 5.5 V to 27 V,  $T_{\rm j}$  = -40° C to +150 °C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                | Symbol           | Values |      |      |    | Note /                                                                                               | Number   |

|------------------------------------------|------------------|--------|------|------|----|------------------------------------------------------------------------------------------------------|----------|

|                                          |                  | Min.   | Тур. | Max. |    | Test Condition                                                                                       |          |

| Input leakage current (all other)        | I <sub>OZ2</sub> | -15    | -    | +15  | μА | $T_{\rm J} \le 150^{\circ}{\rm C},$<br>0.45 V < $V_{\rm IN}$<br>< $V_{\rm DDP}$                      | P_5.5.12 |

| Pull level keep current                  | $I_{PLK}$        | -240   | _    | +240 | μΑ | $V_{\text{PIN}} \ge V_{\text{IH}} \text{ (up)}$<br>$V_{\text{PIN}} \le V_{\text{IL}} \text{ (dn)}$   | P_5.5.13 |

| Pull level force current                 | $I_{PLF}$        | -1.5   | -    | +1.5 | mA | $V_{\text{PIN}} \leq V_{\text{IL}} \text{ (up)}$<br>$V_{\text{PIN}} \geq V_{\text{IH}} \text{ (dn)}$ | P_5.5.14 |

| Pin capacitance (digital inputs/outputs) | $C_{IO}$         | _      | -    | 10   | pF | _                                                                                                    | P_5.5.15 |

- 1) Not subject to production test, specified by design.

- 2) The maximum deliverable output current of a port driver depends on the selected output driver mode. The limit for pin groups must be respected.

- 3) As a rule, with decreasing output current the output levels approach the respective supply level ( $V_{OL} \rightarrow GND$ ,  $V_{OH} \rightarrow V_{DDP}$ ). However, only the levels for nominal output currents are verified.

- 4) This specification is not valid for outputs which are switched to open drain mode. In this case the respective output will float and the voltage is determined by the external circuit.

- 5) The given values are worst-case values. In production test, this leakage current is only tested at 125°C; other values are ensured by correlation. For derating, please refer to the following descriptions:

- Leakage derating depending on temperature ( $T_{\rm J}$  = junction temperature [°C]):  $I_{\rm OZ}$  = 0.05 × e<sup>(1.5 + 0.028×TJ)</sup> [ $\mu$ A]. For example, at a temperature of 95°C the resulting leakage current is 3.2  $\mu$ A. Leakage derating depending on voltage level ( $\Delta$ V =  $V_{\rm DDP}$   $V_{\rm PIN}$  [V]):

$I_{OZ} = I_{OZtempmax} - (1.6 \times \Delta V) [\mu A]$

- This voltage derating formula is an approximation which applies for maximum temperature.

- 6) Keep current: Limit the current through this pin to the indicated value so that the enabled pull device can keep the default pin level:  $V_{\text{PIN}} \ge V_{\text{IH}}$  for a pull-up;  $V_{\text{PIN}} \le V_{\text{IL}}$  for a pull-down.

- Force current: Drive the indicated minimum current through this pin to change the default pin level driven by the enabled pull device:  $V_{\text{PIN}} \leq V_{\text{IL}}$  for a pull-up;  $V_{\text{PIN}} \geq V_{\text{IH}}$  for a pull-down.

- These values apply to the fixed pull-devices in dedicated pins and to the user-selectable pull-devices in general purpose IO pins.

Data Sheet 72 Rev. 1.1, 2012-03-08

# 5.6 LIN Transceiver

## **5.6.1** Electrical Characteristics

Table 28 Electrical Characteristics LIN Transceiver

$V_{\rm s}$  = 5.5V - 18V,  $T_{\rm j}$  = -40° C to +150 °C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                              | Symbol                     | Values                    |                      |                           | Unit | Note / Test Condition                                                                                                                     | Number   |

|--------------------------------------------------------|----------------------------|---------------------------|----------------------|---------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                                        |                            | Min.                      | Тур.                 | Max.                      |      |                                                                                                                                           |          |

| Bus Receiver Interface                                 |                            | 1                         |                      | 1                         |      |                                                                                                                                           |          |

| Receiver threshold voltage, recessive to dominant edge | $V_{ m th\_dom}$           | 0.4 ×V <sub>S</sub>       | 0.45 ×V <sub>S</sub> | 0.53 x V <sub>S</sub>     | V    | SAE J2602                                                                                                                                 | P_5.6.1  |

| Receiver dominant state                                | $V_{\mathrm{BUSdom}}$      | -27                       | _                    | 0.4 ×V <sub>S</sub>       | V    | LIN Spec 2.1 (Par. 17)                                                                                                                    | P_5.6.2  |

| Receiver threshold voltage, dominant to recessive edge | $V_{th\_rec}$              | 0.47 x<br>V <sub>S</sub>  | 0.55 ×V <sub>S</sub> | 0.6 ×V <sub>S</sub>       | V    | SAE J2602                                                                                                                                 | P_5.6.3  |

| Receiver recessive state                               | $V_{BUSrec}$               | 0.6 ×V <sub>S</sub>       | _                    | 1.15 ×V <sub>S</sub>      | V    | 1) LIN Spec 2.1 (Par. 18)                                                                                                                 | P_5.6.4  |

| Receiver center voltage                                | $V_{ m BUS\_CN}$           | 0.475<br>× V <sub>S</sub> | 0.5 ×V <sub>S</sub>  | 0.525<br>× V <sub>S</sub> | V    | <sup>2)</sup> LIN Spec 2.1 (Par. 19)                                                                                                      | P_5.6.5  |

| Receiver hysteresis                                    | $V_{HYS}$                  | 0.07 V <sub>S</sub>       | 0.12 ×V <sub>S</sub> | 0.175<br>× V <sub>S</sub> | V    | <sup>3)</sup> LIN Spec 2.1 (Par. 20)                                                                                                      | P_5.6.6  |

| Wake-up threshold voltage                              | $V_{\mathrm{BUS,wk}}$      | 0.4 ×V <sub>S</sub>       | 0.5 ×V <sub>S</sub>  | 0.6 ×V <sub>S</sub>       | V    | _                                                                                                                                         | P_5.6.7  |

| Dominant time for bus wake-<br>up                      | <i>t</i> <sub>WK,bus</sub> | 3                         | _                    | 15                        | μs   | To achieve the required wake-up time from 30 µs to 150 µs according to LIN spec., an additional digital filter is added (see PMU chapter) | P_5.6.8  |

| Bus Transmitter Interface                              |                            |                           |                      |                           |      |                                                                                                                                           |          |

| Bus recessive output voltage                           | $V_{\rm BUS,ro}$           | $0.8 \times V_{\rm S}$    | _                    | $V_{S}$                   | V    | $V_{TxD}$ = high Level                                                                                                                    | P_5.6.9  |

| Bus short circuit current                              | $I_{\rm BUS,sc}$           | 40                        | 100                  | 150                       | mA   | $V_{\rm BUS}$ = 13.5 V                                                                                                                    | P_5.6.10 |

| Leakage current                                        | $I_{\rm BUS\_NO\_}$ gnd    | -1000                     | -70                  | _                         | μΑ   | $V_{\rm S}$ = 0 V; $V_{\rm BUS}$ = -12 V;<br>LIN Spec 2.1 (Par. 15)                                                                       | P_5.6.11 |

| Leakage current                                        | $I_{ m BUS\_NO\_}$         | _                         | 10                   | 20                        | μΑ   | $V_{\rm S}$ = 0 V; $V_{\rm BUS}$ = 18 V;<br>LIN Spec 2.1 (Par. 16)                                                                        | P_5.6.12 |

| Leakage current                                        | I <sub>BUS_PAS</sub>       | -1                        | _                    | _                         | mA   | $V_{\rm S}$ = 18 V; $V_{\rm BUS}$ = 0 V;<br>LIN Spec 2.1 (Par. 13)                                                                        | P_5.6.13 |

| Leakage current                                        | I <sub>BUS_PAS</sub>       | _                         | _                    | 20                        | μΑ   | $V_{\rm S}$ = 8 V; $V_{\rm BUS}$ = 18 V;<br>LIN Spec 2.1 (Par. 14)                                                                        | P_5.6.14 |

| Bus pull-up resistance                                 | $R_{BUS}$                  | 20                        | 30                   | 47                        | kΩ   | Normal mode LIN Spec 2.1 (Param. 26)                                                                                                      | P_5.6.15 |

| LIN input capacity                                     | $C_{LIN\ IN}$              | _                         | 15                   | 30                        | pF   | 4)                                                                                                                                        | P_5.6.80 |

# 5.7 High-Speed Synchronous Serial Interface

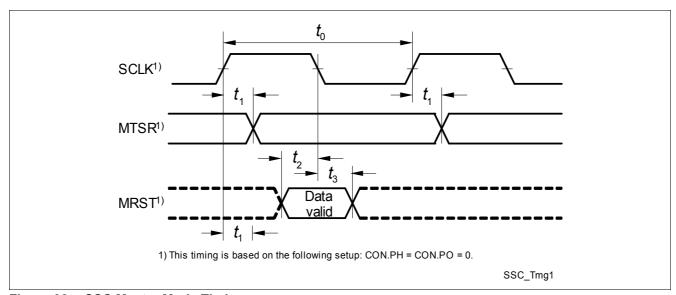

The table below provides the SSC timing in the TLE9833QX.

## Table 29 SSC Master Mode Timing (Operating Conditions apply; CL = 50 pF)

$V_{\rm S}$  = 5.5 V to 27 V,  $T_{\rm j}$  = -40° C to +150 °C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter            | Symbol |                         | Values | i    | Unit | Note /         | Number  |  |

|----------------------|--------|-------------------------|--------|------|------|----------------|---------|--|

|                      |        | Min.                    | Тур.   | Max. |      | Test Condition |         |  |

| SCLK clock period    | $t_0$  | 1) 2 * T <sub>SSC</sub> | _      | _    |      | _              | P_5.7.1 |  |

| MTSR delay from SCLK | $t_1$  | 10                      | _      | _    | ns   | _              | P_5.7.2 |  |

| MRST setup to SCLK   | $t_2$  | 10                      | _      | _    | ns   | _              | P_5.7.3 |  |

| MRST hold from SCLK  | $t_3$  | 15                      | _      | _    | ns   | _              | P_5.7.4 |  |

<sup>1)</sup>  $T_{\text{SSCmin}} = T_{\text{CPU}} = 1/f_{\text{CPU}}$ . When  $f_{\text{CPU}} = 24$  MHz,  $t_0 = 83.3$  ns.  $T_{\text{CPU}}$  is the CPU clock period.

Figure 32 SSC Master Mode Timing

## Table 31 Supply voltage signal conditioning

$V_{\rm S}$  = 5.5 V to 27 V,  $T_{\rm j}$  = -40° C to +150 °C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                | Symbol                          |      | Values |      | Values l |   | Unit     | Note / Test Condition | Number |

|--------------------------|---------------------------------|------|--------|------|----------|---|----------|-----------------------|--------|

|                          |                                 | Min. | Тур.   | Max. |          |   |          |                       |        |

| V <sub>DD5_SENSE</sub>   | $\Delta V_{DDP\_SENSE}$         | -150 | _      | 150  | mV       | _ | P_5.8.15 |                       |        |

| V <sub>DD1V5_SENSE</sub> | $\Delta V_{	extsf{DDC\_SENSE}}$ | -45  | _      | 45   | mV       | - | P_5.8.16 |                       |        |

<sup>1)</sup> This parameter is not subject to production test

# 5.8.3 Measurement Functions Monitoring Input Voltage Attenuator

#### Table 32 Monitoring input voltage attenuation

$V_{\rm S}$  = 5.5 V to 27 V,  $T_{\rm j}$  = -40° C to +150 °C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                           | Symbol                 | Values  |         |           | Unit    | Note / Test Condition                                                                                                                       | Number   |

|-------------------------------------|------------------------|---------|---------|-----------|---------|---------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                     |                        | Min.    | Тур.    | Гур. Мах. |         |                                                                                                                                             |          |

| Power Supply                        |                        | ·       |         |           | •       |                                                                                                                                             |          |

| Input resistance <sup>1)</sup>      | R <sub>IN</sub>        | 300     | 400     | 500       | kΩ      | PD_N=1 (on-state) V <sub>MON_X</sub> =0 P_<br>to 18V if<br>VMON_SEN_SEL_INRANGE<br>= 0                                                      |          |

| Input resistance                    | R <sub>IN</sub>        | 250     | _       | _         | kΩ      | $V_{MON_X}$ =0 to 28V if VMON_SEN_SEL_INRANGE = 1 >200 kΩ under all other conditions                                                        | P_5.8.18 |

| Timing Characteristics              |                        |         |         |           |         |                                                                                                                                             |          |

| Analog Multiplexer Settling<br>Time | $T_{ m MUXsettle}$     | _       | _       | 30        | μs      | This time frame is valid from writing the corresponding selection register to proper settling of the voltage at channel 7 of the 10-Bit ADC | P_5.8.19 |

| Overall (calibrated) meas           | urement ac             | ccuracy | after A | /D-con    | version | 1                                                                                                                                           | •        |

| V <sub>MONx</sub> 10-bit ADC        | $\Delta V_{ m MONxAD}$ | -200    | _       | 200       | mV      | $V_{\rm s}$ =5.5V to 18V,<br>$T_{\rm j}$ = 4085°C                                                                                           | P_5.8.20 |

<sup>1)</sup> Not subject to production test, specified by design.

<sup>2)</sup> The device is calibrated based on an external  $1k\Omega$  resistor

# 5.10 High-Voltage Monitor Input

**Table 37 Electrical Characteristics**

$V_{\rm S}$  = 5.5 V to 27 V,  $T_{\rm j}$  = -40° C to +150 °C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                                                     | Symbol              |                     | Values              |                     | Unit | Note / Test Condition                                                                              | Number   |

|-------------------------------------------------------------------------------|---------------------|---------------------|---------------------|---------------------|------|----------------------------------------------------------------------------------------------------|----------|

|                                                                               |                     | Min.                | Тур.                | Max.                |      |                                                                                                    |          |

| Input Pin characteristics                                                     |                     |                     |                     |                     |      |                                                                                                    |          |

| Wake-up/monitoring threshold voltage                                          | $V_{MONth}$         | 0.4*V <sub>s</sub>  | 0.5*V <sub>s</sub>  | 0.6*V <sub>s</sub>  | V    | without external serial resistor $R_s$ (with $R_s$ : $\Delta V = I_{PD/PU} * R_s$ );               | P_5.10.1 |

| Threshold hysteresis                                                          | $V_{MONth,hys}$     | 0.02*V <sub>s</sub> | 0.06*V <sub>s</sub> | 0.12*V <sub>s</sub> | V    | in all modes; without external serial resistor $R_s$ (with $R_s$ : $\Delta V = I_{PD/PU} * R_s$ ); | P_5.10.2 |

| Pull-up current MONx_CTRL_STS.MONx_PU = high MONx_CTRL_STS.MONx_PD = low      | $I_{PU,MONx}$       | -20                 | -10                 | -1                  | μΑ   | $0 V < V_{MON\_IN} < V_s - 2 V$                                                                    | P_5.10.3 |

| Pull-up current MONx_CTRL_STS.MONx_PU = high MONx_CTRL_STS.MONx_PD = high     | $I_{PU,MONx}$       | -20                 | -10                 | -1                  | μА   | 0.6*V <sub>s</sub> < V <sub>MON_IN</sub> < V <sub>s</sub> - 2 V                                    | P_5.10.4 |

| Pull-down current MONx_CTRL_STS.MONx_PU = low MONx_CTRL_STS.MONx_PD = high    | $I_{PD,\;MONx}$     | 4                   | 10                  | 18                  | μА   | 2 V < V <sub>MON_IN</sub> < V <sub>s</sub>                                                         | P_5.10.5 |

| Pull-down current MONx_CTRL_STS.MONx_PU = high MONx_CTRL_STS.MONx_PD = high   | $I_{\rm PD,\;MONx}$ | 4                   | 10                  | 18                  | μА   | 2 V < V <sub>MON_IN</sub> < 0.4*V <sub>s</sub>                                                     | P_5.10.6 |

| Input leakage current MONx_CTRL_STS.MONx_PU = low MONx_CTRL_STS.MONx_PD = low | $I_{LK,I}$          | -2                  | _                   | 2                   | μА   | 0 V < V <sub>MON_IN</sub> < 28 V                                                                   | P_5.10.7 |

The Parameters of the analog measurement are listed in the chapter Measurement Interface.

**Package Outlines**

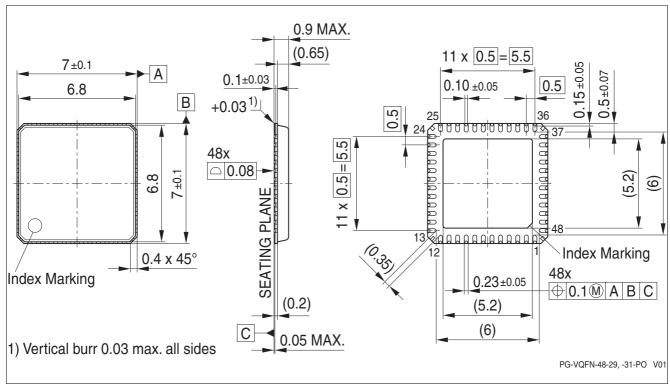

# 6 Package Outlines

Figure 33 Package outline VQFN-48-29

#### **Notes**

- 1. You can find all of our packages, sorts of packing and others in our Infineon Internet Page "Products": <a href="http://www.infineon.com/products">http://www.infineon.com/products</a>.

- 2. Dimensions in mm.

**Revision History**

# 7 Revision History

| Revision | Date       | Changes                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|----------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1.1      | 2012-03-08 | Editorial Changes                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 1.1      | 2012-03-08 | Added full package name (VQFN-48-29)                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 1.1      | 2012-03-08 | <b>Table 4</b> : VDD1V5P: Power Mode configurations: added comment: "Power Dow Supply"                                                                                                                                                                                                                                                                                                |  |  |  |

| 1.1      | 2012-03-08 | <b>Table 5</b> : Description of PMU Submodules: PMU-CYCMU description added and PMU-CMU changed from "cyclic" to "clock" management                                                                                                                                                                                                                                                   |  |  |  |

| 1.1      | 2012-03-08 | Table 30: Changed Value Max. from parameter "Common input voltage in differential mode" from $V_{\rm DD}$ to $V_{\rm DDP}$                                                                                                                                                                                                                                                            |  |  |  |

| 1.1      | 2012-03-08 | <b>Table 23</b> : Changed Value Min. from parameter "Input voltage (amplitude) on XTAL1" from $0.3xV_{\rm DDI}$ to $0.3xV_{\rm DDP}$                                                                                                                                                                                                                                                  |  |  |  |

| 1.1      | 2012-03-08 | <b>Table 41</b> : for "Turn ON, Turn OFF" Parameters changed Test condition from $R_L$ =1kΩ to $R_L$ =270Ω                                                                                                                                                                                                                                                                            |  |  |  |

| 1.1      | 2012-03-08 | Table 14: - Removed "max" from the symbol suffixes - Corrected Symbol of Parameter "Input voltage at LIN" from $V_{\rm MONx}$ to $V_{\rm LIN}$                                                                                                                                                                                                                                        |  |  |  |

| 1.1      | 2012-03-08 | Table 41: Parameter "Overcurrent Limitation": - Renamed Parameter from "Typical on-state current" to "Overcurrent Limitation" Added min. (175mA) and max (325mA) values - Removed Parameter "Overcurrent threshold accuracy". This information is added in the "Note/Test" Condition of the Parameter "Overcurrent Limitation"                                                        |  |  |  |

| 1.1      | 2012-03-08 | Table 19: - Renamed Parameter "Output Current" to "Specified Output Current" - Renamed Parameter "Output Capacitance" to "Required Output Capacitance"                                                                                                                                                                                                                                |  |  |  |

| 1.1      | 2012-03-08 | Table 20:  - Renamed Parameter "Output Current" to "Specified Output Current"  - Renamed Parameter "Output Capacitance" to "Required Output Capacitance"  - Parameter "Dynamic Line Regulation": Correct typo in "Note/Test Condition"  from $V_{\rm DDC}$ to $V_{\rm DDP}$ - Parameter "Output Voltage including line regulation @ Stop Mode": Value Max.  changed from 1.01 to 1.15 |  |  |  |

| 1.1      | 2012-03-08 | Figure 31: Application Diagram updated                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 1.1      | 2012-03-08 | Figure 29: Module Block Diagram updated (replaced 500mA by 250mA)                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 1.1      | 2012-03-08 | Table 27: Changed "Maximum Output Current" to "Nominal Output Current" in third row                                                                                                                                                                                                                                                                                                   |  |  |  |

| 1.1      | 2012-03-08 | <b>Table 14</b> : Added "Output voltage VDDP" for <i>t</i> < 100ms, in Stop Mode only                                                                                                                                                                                                                                                                                                 |  |  |  |

| 1.1      | 2012-03-08 | Chapter 4.1: Added disclaimer note                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| 1.1      | 2012-03-08 | <b>Table 11</b> : Changed value C <sub>VDDEXT</sub> of blocking capacitor at VDDEXT pin to100nF (from 10nF)                                                                                                                                                                                                                                                                           |  |  |  |

| 1.1      | 2012-03-08 | Table 11 and Table 12: Changed headline from "External Component Requirements" to "External Component Recommendation"                                                                                                                                                                                                                                                                 |  |  |  |