Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                              |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ST7                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               | SCI, SPI                                                              |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 32                                                                    |

| Program Memory Size        | 8KB (8K x 8)                                                          |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 384 x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                           |

| Data Converters            | A/D 12x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 44-LQFP                                                               |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f324bj2t6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

57

|    | 12.10               | Control                                                                                            | pin characteristics 166                                                                                                                                                                                                                                                                                                                                 | 6                                         |  |  |  |

|----|---------------------|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|--|--|--|

|    |                     | 12.10.1                                                                                            | Asynchronous RESET pin166                                                                                                                                                                                                                                                                                                                               | 6                                         |  |  |  |

|    |                     | 12.10.2                                                                                            | ICCSEL/VPP pin                                                                                                                                                                                                                                                                                                                                          | 8                                         |  |  |  |

|    | 12.11               | Timer p                                                                                            | eripheral characteristics 168                                                                                                                                                                                                                                                                                                                           | 8                                         |  |  |  |

|    |                     | 12.11.1                                                                                            | 16-bit timer                                                                                                                                                                                                                                                                                                                                            | 8                                         |  |  |  |

|    | 12.12               | Commu                                                                                              | inication interface characteristics 169                                                                                                                                                                                                                                                                                                                 | 9                                         |  |  |  |

|    |                     | 12.12.1                                                                                            | Serial peripheral interface (SPI) 169                                                                                                                                                                                                                                                                                                                   | 9                                         |  |  |  |

|    | 12.13               | 10-bit A                                                                                           | DC characteristics 17 <sup>-</sup>                                                                                                                                                                                                                                                                                                                      | 1                                         |  |  |  |

|    |                     | 12.13.1                                                                                            | Analog power supply and reference pins                                                                                                                                                                                                                                                                                                                  | 3                                         |  |  |  |

|    |                     | 12.13.2                                                                                            | General PCB design guidelines                                                                                                                                                                                                                                                                                                                           | 3                                         |  |  |  |

|    |                     | 12.13.3                                                                                            | ADC accuracy                                                                                                                                                                                                                                                                                                                                            | 4                                         |  |  |  |

| 13 | Packa               | age cha                                                                                            | racteristics                                                                                                                                                                                                                                                                                                                                            | 5                                         |  |  |  |

|    | 13.1                | LQFP4                                                                                              | 4 package characteristics 175                                                                                                                                                                                                                                                                                                                           | 5                                         |  |  |  |

|    | 13.2                | LQFP3                                                                                              | 2 package characteristics 176                                                                                                                                                                                                                                                                                                                           | 6                                         |  |  |  |

|    | 13.3                | Therma                                                                                             | Il characteristics                                                                                                                                                                                                                                                                                                                                      | 8                                         |  |  |  |

|    | 13.4                | Ecopac                                                                                             | k information                                                                                                                                                                                                                                                                                                                                           | 8                                         |  |  |  |

|    | 13.5                | Packag                                                                                             | ing for automatic handling 178                                                                                                                                                                                                                                                                                                                          | 8                                         |  |  |  |

| 14 | Devic               | e confi                                                                                            | guration and ordering information                                                                                                                                                                                                                                                                                                                       | 9                                         |  |  |  |

|    | 14.1                | Flash d                                                                                            | evices                                                                                                                                                                                                                                                                                                                                                  | 9                                         |  |  |  |

|    |                     | 14.1.1                                                                                             | Flash configuration                                                                                                                                                                                                                                                                                                                                     | 9                                         |  |  |  |

|    |                     | 14.1.2                                                                                             | Flash ordering information                                                                                                                                                                                                                                                                                                                              | 2                                         |  |  |  |

|    | 14.2                | ROM device ordering information and transfer of customer code                                      |                                                                                                                                                                                                                                                                                                                                                         |                                           |  |  |  |

|    |                     | ROM de                                                                                             | evice ordering information and transfer of customer code 18                                                                                                                                                                                                                                                                                             | 3                                         |  |  |  |

|    | 14.3                |                                                                                                    | evice ordering information and transfer of customer code 183                                                                                                                                                                                                                                                                                            |                                           |  |  |  |

|    | 14.3                |                                                                                                    |                                                                                                                                                                                                                                                                                                                                                         | 7                                         |  |  |  |

|    | 14.3                | Develop                                                                                            | oment tools                                                                                                                                                                                                                                                                                                                                             | 7<br>7                                    |  |  |  |

|    | 14.3                | Develop<br>14.3.1                                                                                  | oment tools                                                                                                                                                                                                                                                                                                                                             | 7<br>7<br>7                               |  |  |  |

|    | 14.3                | Develop<br>14.3.1<br>14.3.2                                                                        | oment tools       187         Introduction       187         Evaluation tools and starter kits       187                                                                                                                                                                                                                                                | 7<br>7<br>7<br>7                          |  |  |  |

|    | 14.3                | Develop<br>14.3.1<br>14.3.2<br>14.3.3                                                              | oment tools       187         Introduction       187         Evaluation tools and starter kits       187         Development and debugging tools       187                                                                                                                                                                                              | 7<br>7<br>7<br>7                          |  |  |  |

|    | 14.3                | Develop<br>14.3.1<br>14.3.2<br>14.3.3<br>14.3.4<br>14.3.5                                          | Dement tools       187         Introduction       187         Evaluation tools and starter kits       187         Development and debugging tools       187         Programming tools       187                                                                                                                                                         | 7<br>7<br>7<br>7<br>8                     |  |  |  |

| 15 | 14.4                | Develop<br>14.3.1<br>14.3.2<br>14.3.3<br>14.3.4<br>14.3.5<br>ST7 Ap                                | oment tools       187         Introduction       187         Evaluation tools and starter kits       187         Development and debugging tools       187         Programming tools       187         Socket and emulator adapter information       187                                                                                                | 7<br>7<br>7<br>7<br>8                     |  |  |  |

| 15 | 14.4                | Develop<br>14.3.1<br>14.3.2<br>14.3.3<br>14.3.4<br>14.3.5<br>ST7 Ap<br>m limita                    | oment tools       187         Introduction       187         Evaluation tools and starter kits       187         Development and debugging tools       187         Programming tools       187         Socket and emulator adapter information       188         plication notes       188                                                              | 7<br>7<br>7<br>7<br>8<br>8<br><b>9</b>    |  |  |  |

| 15 | 14.4<br><b>Know</b> | Develop<br>14.3.1<br>14.3.2<br>14.3.3<br>14.3.4<br>14.3.5<br>ST7 Ap<br>m limita                    | oment tools       187         Introduction       187         Evaluation tools and starter kits       187         Development and debugging tools       187         Programming tools       187         Socket and emulator adapter information       188         plication notes       188         Ntions       188                                     | 7<br>7<br>7<br>7<br>8<br>8<br>9<br>9      |  |  |  |

| 15 | 14.4<br><b>Know</b> | Develop<br>14.3.1<br>14.3.2<br>14.3.3<br>14.3.4<br>14.3.5<br>ST7 Ap<br><b>n limita</b><br>All Flas | oment tools       187         Introduction       187         Evaluation tools and starter kits       187         Development and debugging tools       187         Programming tools       187         Socket and emulator adapter information       188         plication notes       188         Ations       188         h and ROM devices       189 | 7<br>7<br>7<br>7<br>8<br>8<br>9<br>9<br>9 |  |  |  |

| Doc | ID13466 | Rev | 4 |

|-----|---------|-----|---|

|-----|---------|-----|---|

# List of figures

| Figure 1.   | Device block diagram                                                                | . 14       |

|-------------|-------------------------------------------------------------------------------------|------------|

| Figure 2.   | 44-pin LQFP package pinout                                                          | . 15       |

| Figure 3.   | 32-pin LQFP package pinout                                                          | . 15       |

| Figure 4.   | Memory map                                                                          | . 19       |

| Figure 5.   | Memory map and sector address                                                       | . 23       |

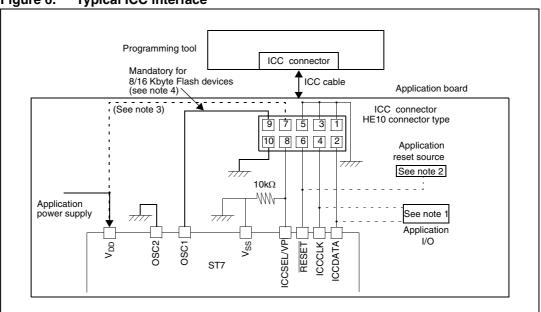

| Figure 6.   | Typical ICC interface                                                               |            |

| Figure 7.   | CPU registers                                                                       |            |

| Figure 8.   | Stack manipulation example                                                          |            |

| Figure 9.   | PLL block diagram                                                                   |            |

| Figure 10.  | Clock, reset and supply block diagram.                                              |            |

| Figure 11.  | Reset sequence phases                                                               |            |

| Figure 12.  | Reset block diagram                                                                 |            |

| Figure 13.  | RESET sequences                                                                     |            |

| Figure 14.  | Low voltage detector vs reset                                                       |            |

| Figure 15.  | Using the AVD to monitor $V_{DD}$                                                   |            |

| Figure 16.  | Interrupt processing flowchart                                                      |            |

| Figure 17.  | Priority decision process flowchart                                                 |            |

| Figure 18.  | Concurrent interrupt management                                                     |            |

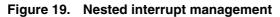

| -           | Nested interrupt management                                                         |            |

| Figure 19.  |                                                                                     |            |

| Figure 20.  | External interrupt control bits                                                     |            |

| Figure 21.  | Power saving mode transitions.                                                      |            |

| Figure 22.  | Slow mode clock transitions                                                         |            |

| Figure 23.  | Wait mode flowchart                                                                 |            |

| Figure 24.  | Active Halt timing overview.                                                        |            |

| Figure 25.  | Active Halt mode flowchart                                                          |            |

| Figure 26.  | HALT timing overview                                                                |            |

| Figure 27.  | Halt mode flowchart                                                                 |            |

| Figure 28.  | I/O port general block diagram                                                      |            |

| Figure 29.  | Interrupt I/O port state transitions                                                |            |

| Figure 30.  | Watchdog block diagram                                                              |            |

| Figure 31.  | Approximate timeout duration                                                        | . 66       |

| Figure 32.  | Exact timeout duration (t <sub>min</sub> and t <sub>max</sub> )                     | . 67       |

| Figure 33.  | Main clock controller (MCC/RTC) block diagram                                       | . 70       |

| Figure 34.  | Timer block diagram                                                                 | . 76       |

| Figure 35.  | 16-bit read sequence                                                                | . 77       |

| Figure 36.  | Counter timing diagram, internal clock divided by 2                                 | . 78       |

| Figure 37.  | Counter timing diagram, internal clock divided by 4                                 | . 78       |

| Figure 38.  | Counter timing diagram, internal clock divided by 8                                 | . 78       |

| Figure 39.  | Input capture block diagram                                                         |            |

| Figure 40.  | Input capture timing diagram                                                        |            |

| Figure 41.  | Output compare block diagram                                                        |            |

| Figure 42.  | Output compare timing diagram, $f_{TIMER} = f_{CPU}/2$                              |            |

| Figure 43.  | Output compare timing diagram, $f_{TIMER} = f_{CPU}/4$                              |            |

| Figure 44.  | One pulse mode cycle                                                                |            |

| Figure 45.  | One Pulse mode timing example(1)                                                    | . 85       |

| Figure 46.  | Pulse width modulation mode timing example with two output compare functions(1)(2). | 86         |

| Figure 47.  | Pulse width modulation cycle                                                        |            |

| Figure 48.  | Serial peripheral interface block diagram                                           | . 07<br>08 |

| . iguio 40. |                                                                                     |            |

### 4.3.1 Readout protection

Readout protection, when selected, provides a protection against program memory content extraction and against write access to Flash memory. Even if no protection can be considered as totally unbreakable, the feature provides a very high level of protection for a general purpose microcontroller.

In Flash devices, this protection is removed by reprogramming the option. In this case, the entire program memory is first automatically erased.

Readout protection selection depends on the device type:

- In Flash devices it is enabled and removed through the FMP\_R bit in the option byte.

- In ROM devices it is enabled by mask option specified in the option list.

#### Figure 5. Memory map and sector address

|        | 8K | 16K      | 32K       | <ul> <li>Flash<br/>memory size</li> </ul> |

|--------|----|----------|-----------|-------------------------------------------|

| 7FFFh  |    |          | · [       |                                           |

| BFFFh  |    |          | -         | <ul> <li>Sector 2</li> </ul>              |

| DFFFh  |    | 8 Kbytes | 24 Kbytes |                                           |

| EFFFh. |    | 4 Kbytes |           | Sector 1                                  |

| FFFFh  |    | 4 Kbytes |           | Sector 0                                  |

## 4.4 ICC interface

ICC needs a minimum of 4 and up to 6 pins to be connected to the programming tool (see *Figure 6*). These pins are:

- RESET: device reset

- V<sub>SS</sub>: device power supply ground

- ICCCLK: ICC output serial clock pin

- ICCDATA: ICC input/output serial data pin

- ICCSEL/V<sub>PP</sub>: programming voltage

- OSC1 (or OSCIN): main clock input for external source (optional)

- V<sub>DD</sub>: application board power supply (optional, see *Figure 6*, Note 3).

Figure 6. Typical ICC interface

- If the ICCCLK or ICCDATA pins are only used as outputs in the application, no signal isolation is necessary. As soon as the programming tool is plugged to the board, even if an ICC session is not in progress, the ICCCLK and ICCDATA pins are not available for the application. If they are used as inputs by the application, isolation such as a serial resistor has to be implemented in case another device forces the signal. Refer to the Programming Tool documentation for recommended resistor values.

- 2. During the ICC session, the programming tool must control the RESET pin. This can lead to conflicts between the programming tool and the application reset circuit if it drives more than 5mA at high level (PUSH-pull output or pull-up resistor <1K). A schottky diode can be used to isolate the application reset circuit in this case. When using a classical RC network with R>1K or a reset management IC with open drain output and pull-up resistor >1K, no additional components are needed. In all cases the user must ensure that no external reset is generated by the application during the ICC session.

- 3. The use of Pin 7 of the ICC connector depends on the programming tool architecture. This pin must be connected when using most ST programming tools (it is used to monitor the application power supply). Please refer to the programming tool manual.

- 4. Pin 9 has to be connected to the OSC1 (OSCIN) pin of the ST7 when the clock is not available in the application or if the selected clock option is not programmed in the option byte. ST7 devices with multi-oscillator capability need to have OSC2 grounded in this case.

- **Caution:** External clock ICC entry mode is mandatory in ST72F324B 8/16 Kbyte Flash devices. In this case pin 9 must be connected to the OSC1 (OSCIN) pin of the ST7 and OSC2 must be grounded. 32 Kbyte Flash devices may use external clock or application clock ICC entry mode.

## 4.5 ICP (in-circuit programming)

To perform ICP the microcontroller must be switched to ICC (in-circuit communication) mode by an external controller or programming tool.

Depending on the ICP code downloaded in RAM, Flash memory programming can be fully customized (number of bytes to program, program locations, or selection serial communication interface for downloading).

When using an STMicroelectronics or third-party programming tool that supports ICP and the specific microcontroller device, the user needs only to implement the ICP hardware interface on the application board (see *Figure 6*). For more details on the pin locations, refer to the device pinout description.

Doc ID13466 Rev 4

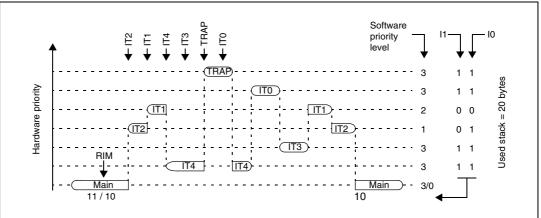

## 7.5 Interrupt registers

## 7.5.1 CPU CC register interrupt bits

#### Table 15. CPU CC register interrupt bits description

| Bit | Name | Function                      |

|-----|------|-------------------------------|

| 5   | 11   | Software Interrupt Priority 1 |

| 3   | 10   | Software Interrupt Priority 0 |

#### Table 16.Interrupt software priority levels

| Interrupt software priority                  | Level | 11 | 10 |

|----------------------------------------------|-------|----|----|

| Level 0 (main)                               | Low   | 1  | 0  |

| Level 1                                      |       | 0  | 1  |

| Level 2                                      | ↓     | 0  | 0  |

| Level 3 (= interrupt disable) <sup>(1)</sup> | High  | 1  | 1  |

1. TRAP and RESET events can interrupt a level 3 program.

These two bits indicate the current interrupt software priority (see *Table 16*) and are set/cleared by hardware when entering in interrupt. The loaded value is given by the corresponding bits in the interrupt software priority registers (ISPRx).

| No. | Source<br>block | Description                                  | Register<br>label | Priority<br>order  | Exit from<br>Halt/Active Halt | Address vector |             |

|-----|-----------------|----------------------------------------------|-------------------|--------------------|-------------------------------|----------------|-------------|

|     | Reset           | Reset                                        | N/A               |                    | yes                           | FFFEh-FFFFh    |             |

|     | TRAP            | Software interrupt                           | IN/A              |                    | no                            | FFFCh-FFFDh    |             |

| 0   |                 | Not used                                     |                   |                    |                               | FFFAh-FFFBh    |             |

| 1   | MCC/RTC         | Main clock controller time base<br>interrupt | MCCSR             | Higher<br>priority | yes                           | FFF8h-FFF9h    |             |

| 2   | ei0             | External interrupt port A30                  |                   |                    | yes                           | FFF6h-FFF7h    |             |

| 3   | ei1             | External interrupt port F20                  | N/A               |                    |                               | yes            | FFF4h-FFF5h |

| 4   | ei2             | External interrupt port B30                  |                   |                    | yes                           | FFF2h-FFF3h    |             |

| 5   | ei3             | External interrupt port B74                  |                   |                    | yes                           | FFF0h-FFF1h    |             |

| 6   |                 | Not used                                     |                   |                    |                               | FFEEh-FFEFh    |             |

| 7   | SPI             | SPI peripheral interrupts                    | SPICSR            |                    | yes                           | FFECh-FFEDh    |             |

| 8   | Timer A         | Timer A peripheral interrupts                | TASR              |                    | no                            | FFEAh-FFEBh    |             |

| 9   | Timer B         | Timer B peripheral interrupts                | TBSR              | ┥                  | no                            | FFE8h-FFE9h    |             |

| 10  | SCI             | SCI peripheral interrupts                    | SCISR             | Lower              | no                            | FFE6h-FFE7h    |             |

| 11  | AVD             | Auxiliary voltage detector interrupt         | SICSR             | priority           | no                            | FFE4h-FFE5h    |             |

#### Table 25. Interrupt mapping

#### Halt mode recommendations

- Make sure that an external event is available to wake up the microcontroller from Halt mode.

- When using an external interrupt to wake up the microcontroller, reinitialize the corresponding I/O as "Input Pull-up with Interrupt" before executing the HALT instruction. The main reason for this is that the I/O may be wrongly configured due to external interference or by an unforeseen logical condition.

- For the same reason, reinitialize the sensitivity level of each external interrupt as a precautionary measure.

- The opcode for the HALT instruction is 0x8E. To avoid an unexpected HALT instruction due to a program counter failure, it is advised to clear all occurrences of the data value 0x8E from memory. For example, avoid defining a constant in ROM with the value 0x8E.

- As the HALT instruction clears the interrupt mask in the CC register to allow interrupts, the user may choose to clear all pending interrupt bits before executing the HALT instruction. This avoids entering other peripheral interrupt routines after executing the external interrupt routine corresponding to the wake-up event (reset or external interrupt).

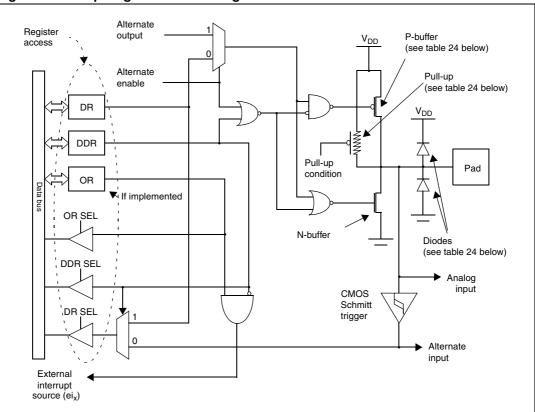

#### External interrupt function

When an I/O is configured as 'Input with Interrupt', an event on this I/O can generate an external interrupt request to the CPU.

Each pin can independently generate an interrupt request. The interrupt sensitivity is independently programmable using the sensitivity bits in the EICR register.

Each external interrupt vector is linked to a dedicated group of I/O port pins (see pinout description and interrupt section). If several input pins are selected simultaneously as interrupt sources, these are first detected according to the sensitivity bits in the EICR register and then logically ORed.

The external interrupts are hardware interrupts, which means that the request latch (not accessible directly by the application) is automatically cleared when the corresponding interrupt vector is fetched. To clear an unwanted pending interrupt by software, the sensitivity bits in the EICR register must be modified.

### 9.2.2 Output modes

The output configuration is selected by setting the corresponding DDR register bit. In this case, writing the DR register applies this digital value to the I/O pin through the latch. Then reading the DR register returns the previously stored value.

Two different output modes can be selected by software through the OR register: Output push-pull and open-drain.

| DR | Push-pull       | Open-drain      |

|----|-----------------|-----------------|

| 0  | V <sub>SS</sub> | V <sub>SS</sub> |

| 1  | V <sub>DD</sub> | Floating        |

#### Table 27. DR register value and output pin status

### 9.2.3 Alternate functions

When an on-chip peripheral is configured to use a pin, the alternate function is automatically selected. This alternate function takes priority over the standard I/O programming.

When the signal is coming from an on-chip peripheral, the I/O pin is automatically configured in output mode (push-pull or open drain according to the peripheral).

When the signal is going to an on-chip peripheral, the I/O pin must be configured in input mode. In this case, the pin state is also digitally readable by addressing the DR register.

Note: Input pull-up configuration can cause unexpected value at the input of the alternate peripheral input. When an on-chip peripheral use a pin as input and output, this pin has to be configured in input floating mode.

Figure 28. I/O port general block diagram

#### Table 28.I/O port mode options

|        | Configuration mode              |                    | Dhuffer  | Diodes                            |                                   |

|--------|---------------------------------|--------------------|----------|-----------------------------------|-----------------------------------|

|        |                                 |                    | P-buffer | to V <sub>DD</sub> <sup>(1)</sup> | to V <sub>SS</sub> <sup>(2)</sup> |

| Input  | Floating with/without Interrupt | Off <sup>(3)</sup> | Off      | On                                |                                   |

| Input  | Pull-up with/without Interrupt  | On <sup>(4)</sup>  | Oli      |                                   |                                   |

|        | Push-pull                       | Off                | On       | OII                               | On                                |

| Output | Open drain (logic level)        | Oli                | Off      |                                   |                                   |

|        | True open drain                 | NI                 | NI       | NI <sup>(5)</sup>                 |                                   |

1. The diode to  $V_{DD}$  is not implemented in the true open drain pads.

2. A local protection between the pad and  $V_{SS}$  is implemented to protect the device against positive stress.

3. Off = implemented not activated.

4. On = implemented and activated.

5. NI = not implemented

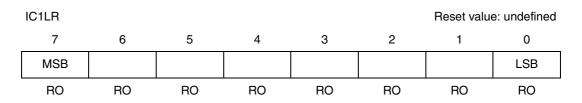

## Input Capture 1 Low Register (IC1LR)

This is an 8-bit register that contains the low part of the counter value (transferred by the input capture 1 event).

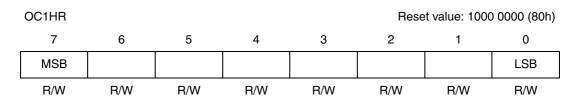

## Output Compare 1 High Register (OC1HR)

This is an 8-bit register that contains the high part of the value to be compared to the CHR register.

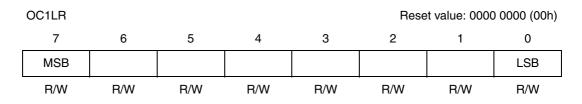

## Output Compare 1 Low Register (OC1LR)

This is an 8-bit register that contains the low part of the value to be compared to the CLR register.

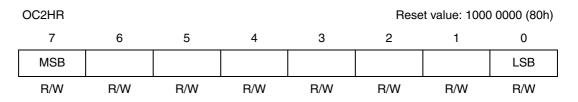

## Output Compare 2 High Register (OC2HR)

This is an 8-bit register that contains the high part of the value to be compared to the CHR register.

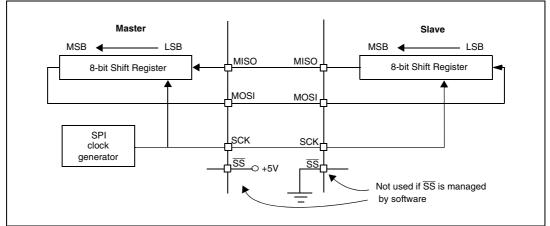

The MOSI pins are connected together and the MISO pins are connected together. In this way data is transferred serially between master and slave (most significant bit first).

The communication is always initiated by the master. When the master device transmits data to a slave device via MOSI pin, the slave device responds by sending data to the master device via the MISO pin. This implies full duplex communication with both data out and data in synchronized with the same clock signal (which is provided by the master device via the SCK pin).

To use a single data line, the MISO and MOSI pins must be connected at each node (in this case only simplex communication is possible).

Four possible data/clock timing relationships may be chosen (see *Figure 52*) but master and slave must be programmed with the same timing mode.

Figure 49. Single master/single slave application

#### Slave Select management

As an alternative to using the  $\overline{SS}$  pin to control the Slave Select signal, the application can choose to manage the Slave Select signal by software. This is configured by the SSM bit in the SPICSR register (see *Figure 51*).

In software management, the external  $\overline{SS}$  pin is free for other application uses and the internal  $\overline{SS}$  signal level is driven by writing to the SSI bit in the SPICSR register.

In Master mode:

• SS internal must be held high continuously

Depending on the data/clock timing relationship, there are two cases in Slave mode (see *Figure 50*):

If CPHA = 1 (data latched on second clock edge):

SS internal must be held low during the entire transmission. This implies that in single slave applications the SS pin either can be tied to V<sub>SS</sub>, or made free for standard I/O by managing the SS function by software (SSM = 1 and SSI = 0 in the in the SPICSR register)

If CPHA = 0 (data latched on first clock edge):

• SS internal must be held low during byte transmission and pulled high between each byte to allow the slave to write to the shift register. If SS is not pulled high, a Write

The SPIF bit can be cleared during a second transmission; however, it must be cleared before the second SPIF bit in order to prevent an Overrun condition (see *Overrun condition* (*OVR*) on page 103).

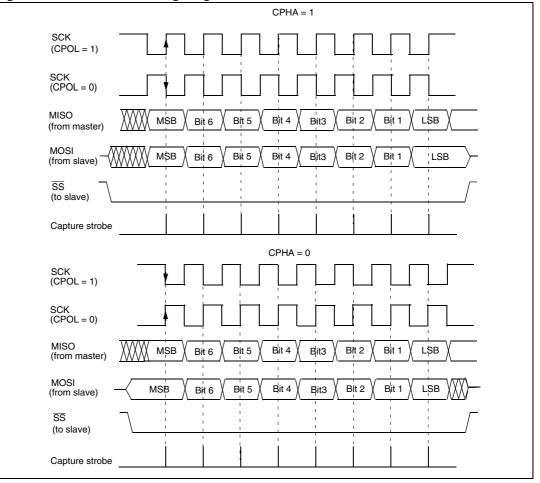

### 10.4.4 Clock phase and clock polarity

Four possible timing relationships may be chosen by software, using the CPOL and CPHA bits (see *Figure 52*).

Note: The idle state of SCK must correspond to the polarity selected in the SPICSR register (by pulling up SCK if CPOL = 1 or pulling down SCK if CPOL = 0).

The combination of the CPOL clock polarity and CPHA (clock phase) bits selects the data capture clock edge

*Figure 52* shows an SPI transfer with the four combinations of the CPHA and CPOL bits. The diagram may be interpreted as a master or slave timing diagram where the SCK, MISO and MOSI pins are directly connected between the master and the slave device.

*Note:* If CPOL is changed at the communication byte boundaries, the SPI must be disabled by resetting the SPE bit.

#### Figure 52. Data clock timing diagram<sup>(1)</sup>

1. This figure should not be used as a replacement for parametric information. Refer to the Electrical Characteristics chapter.

| Table 63. |      | SCICK I register description (continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|-----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Bit       | Name | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| 3         | WAKE | Wake-Up method<br>This bit determines the SCI Wake-Up method, it is set or cleared by software.<br>0: Idle line<br>1: Address mark                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| 2         | PCE  | <ul> <li>Parity Control Enable</li> <li>This bit selects the hardware parity control (generation and detection). When the parity control is enabled, the computed parity is inserted at the MSB position (9th bit if M = 1; 8th bit if M = 0) and parity is checked on the received data. This bit is set and cleared by software. Once it is set, PCE is active after the current byte (in reception and in transmission).</li> <li>0: Parity control disabled</li> <li>1: Parity control enabled</li> </ul> |  |  |  |  |

| 1         | PS   | <ul> <li>Parity Selection</li> <li>This bit selects the odd or even parity when the parity generation/detection is enabled (PCE bit set). It is set and cleared by software. The parity will be selected after the current byte.</li> <li>0: Even parity</li> <li>1: Odd parity</li> </ul>                                                                                                                                                                                                                    |  |  |  |  |

| 0         | PIE  | <ul> <li>Parity Interrupt Enable</li> <li>This bit enables the interrupt capability of the hardware parity control when a parity error is detected (PE bit set). It is set and cleared by software.</li> <li>0: Parity error interrupt disabled</li> <li>1: Parity error interrupt enabled</li> </ul>                                                                                                                                                                                                         |  |  |  |  |

| Table 63. | SCICR1 | register descri | ption (continued) |

|-----------|--------|-----------------|-------------------|

|-----------|--------|-----------------|-------------------|

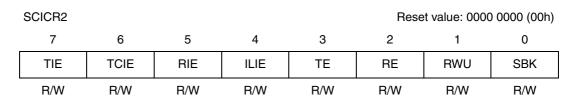

## SCI Control Register 2 (SCICR2)

Table 64. SCICR2 register description

| Bit | Name | Function                                                                                                                                                                                                                 |  |  |  |

|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7   | TIE  | <ul> <li>Transmitter Interrupt Enable</li> <li>This bit is set and cleared by software.</li> <li>0: Interrupt is inhibited</li> <li>1: An SCI interrupt is generated whenever TDRE = 1 in the SCISR register.</li> </ul> |  |  |  |

| 6   | TCIE | TCIE       Transmission Complete Interrupt Enable         This bit is set and cleared by software.         0: Interrupt is inhibited         1: An SCI interrupt is generated whenever TC = 1 in the SCISR register.     |  |  |  |

| Table 64. SCICR2 register description (continued) |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|---------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Bit                                               | Name | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 5                                                 | RIE  | Receiver interrupt Enable<br>This bit is set and cleared by software.<br>0: Interrupt is inhibited<br>1: An SCI interrupt is generated whenever OR = 1 or RDRF = 1 in the SCISR<br>register.                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 4                                                 | ILIE | Idle Line Interrupt Enable<br>This bit is set and cleared by software.<br>0: Interrupt is inhibited<br>1: An SCI interrupt is generated whenever IDLE = 1 in the SCISR register.                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 3                                                 | TE   | <ul> <li>Transmitter Enable</li> <li>This bit enables the transmitter. It is set and cleared by software.</li> <li>0: Transmitter is disabled</li> <li>1: Transmitter is enabled</li> <li>Notes: <ul> <li>During transmission, a '0' pulse on the TE bit ('0' followed by '1') sends a preamble (Idle line) after the current word.</li> <li>When TE is set there is a 1 bit-time delay before the transmission starts.</li> </ul> </li> <li>Caution: The TDO pin is free for general purpose I/O only when the TE and RE bits are both cleared (or if TE is never set).</li> </ul> |  |

| 2                                                 | RE   | Receiver Enable<br>This bit enables the receiver. It is set and cleared by software.<br>0: Receiver is disabled<br>1: Receiver is enabled and begins searching for a start bit<br>Note: Before selecting Mute mode (setting the RWU bit), the SCI must first receive<br>some data, otherwise it cannot function in Mute mode with Wake-Up by Idle line<br>detection.                                                                                                                                                                                                                |  |

| 1                                                 | RWU  | Receiver Wake-Up<br>This bit determines if the SCI is in mute mode or not. It is set and cleared by<br>software and can be cleared by hardware when a wake-up sequence is recognized.<br>0: Receiver in Active mode<br>1: Receiver in Mute mode                                                                                                                                                                                                                                                                                                                                     |  |

| 0                                                 | SBK  | <ul> <li>Send Break</li> <li>This bit set is used to send break characters. It is set and cleared by software.</li> <li>0: No break character is transmitted.</li> <li>1: Break characters are transmitted.</li> <li>Note: If the SBK bit is set to '1' and then to '0', the transmitter will send a Break word at the end of the current word.</li> </ul>                                                                                                                                                                                                                          |  |

Table 64.

SCICR2 register description (continued)

| Address (Hex.) | Register label          | 7        | 6    | 5    | 4    | 3    | 2    | 1    | 0        |

|----------------|-------------------------|----------|------|------|------|------|------|------|----------|

| 0050h          | SCISR                   | TDRE     | TC   | RDRF | IDLE | OR   | NF   | FE   | PE       |

|                | Reset value             | 1        | 1    | 0    | 0    | 0    | 0    | 0    | 0        |

| 0051h          | SCIDR<br>Reset value    | MSB<br>x | x    | x    | x    | x    | x    | x    | LSB<br>x |

| 0052h          | SCIBRR                  | SCP1     | SCP0 | SCT2 | SCT1 | SCT0 | SCR2 | SCR1 | SCR0     |

|                | Reset value             | 0        | 0    | 0    | 0    | 0    | 0    | 0    | 0        |

| 0053h          | SCICR1                  | R8       | Т8   | SCID | M    | WAKE | PCE  | PS   | PIE      |

|                | Reset value             | x        | 0    | 0    | 0    | 0    | 0    | 0    | 0        |

| 0054h          | SCICR2                  | TIE      | TCIE | RIE  | ILIE | TE   | RE   | RWU  | SBK      |

|                | Reset value             | 0        | 0    | 0    | 0    | 0    | 0    | 0    | 0        |

| 0055h          | SCIERPR<br>Reset value  | MSB<br>0 | 0    | 0    | 0    | 0    | 0    | 0    | LSB<br>0 |

| 0057h          | SCIPETPR<br>Reset value | MSB<br>0 | 0    | 0    | 0    | 0    | 0    | 0    | LSB<br>0 |

## Table 69. SCI register map and reset values

## 12.2.2 Current characteristics

| Table 84. Current characteristics | Table 84. | Current characteristics |

|-----------------------------------|-----------|-------------------------|

|-----------------------------------|-----------|-------------------------|

| Symbol                                  | Ratings                                                                 | Max value            | Unit |  |

|-----------------------------------------|-------------------------------------------------------------------------|----------------------|------|--|

| 1                                       | Total current into V <sub>DD</sub> power lines (source) <sup>(1)</sup>  | 75                   |      |  |

| IVDD                                    | Total current into V <sub>DD</sub> power lines (source)                 | 44-pin devices       | 150  |  |

| I                                       | Total current out of V <sub>SS</sub> ground lines (sink) <sup>(1)</sup> | 32-pin devices       | 75   |  |

| I <sub>VSS</sub>                        | Total current out of $v_{SS}$ ground lines (sink).                      | 44-pin devices       | 150  |  |

|                                         | Output current sunk by any standard I/O and co                          | ntrol pin            | 20   |  |

| I <sub>IO</sub>                         | Output current sunk by any high sink I/O pin                            | 40                   |      |  |

|                                         | Output current source by any I/Os and control p                         | - 25                 | mA   |  |

|                                         | Injected current on V <sub>PP</sub> pin                                 | ± 5                  | IIIA |  |

|                                         | Injected current on RESET pin                                           | ± 5                  |      |  |

| ı (2)(3)                                | Injected current on OSC1 and OSC2 pins                                  | ± 5                  |      |  |

| I <sub>INJ(PIN)</sub> <sup>(2)(3)</sup> | Injected current on ROM and 32 Kbyte Flash de                           | ± 5                  |      |  |

|                                         | Injected current on 8/16 Kbyte Flash devices PE                         | + 5                  |      |  |

|                                         | Injected current on any other $pin^{(4)(5)}$                            | ± 5                  |      |  |

| $\Sigma I_{\rm INJ(PIN)}^{(2)}$         | Total injected current (sum of all I/O and control                      | pins) <sup>(4)</sup> | ± 25 |  |

1. All power (V\_{DD}) and ground (V\_{SS}) lines must always be connected to the external supply.

- I<sub>INJ(PIN)</sub> must never be exceeded. This is implicitly insured if V<sub>IN</sub> maximum is respected. If V<sub>IN</sub> maximum cannot be respected, the injection current must be limited externally to the I<sub>INJ(PIN)</sub> value. A positive injection is induced by V<sub>IN</sub> > V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub> < V<sub>SS</sub>. For true open-drain pads, there is no positive injection current, and the corresponding V<sub>IN</sub> maximum must always be respected.

- 3. Negative injection degrades the analog performance of the device. See note in *Section 12.13.3: ADC* accuracy on page 174. If the current injection limits given in *Section Table 105.: General characteristics on* page 162 are exceeded, general device malfunction may result.

- 4. When several inputs are submitted to a current injection, the maximum SI<sub>INJ(PIN)</sub> is the absolute sum of the positive and negative injected currents (instantaneous values). These results are based on characterization with SI<sub>INJ(PIN)</sub> maximum current injection on four I/O port pins of the device.

- 5. True open drain I/O port pins do not accept positive injection.

## 12.2.3 Thermal characteristics

#### Table 85.Thermal characteristics

| Symbol                                                                                          | Ratings                   | Value       | Unit |

|-------------------------------------------------------------------------------------------------|---------------------------|-------------|------|

| T <sub>STG</sub>                                                                                | Storage temperature range | -65 to +150 | °C   |

| T <sub>J</sub> Maximum junction temperature (see <i>Section 13.3: Thermal characteristics</i> ) |                           |             |      |

## 12.7.2 Flash memory

Table 100.

Dual voltage HDFlash memory

| Symbol                                  | Parameter                                | Conditions                   | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit   |  |

|-----------------------------------------|------------------------------------------|------------------------------|--------------------|-----|--------------------|--------|--|

| famili                                  | Operating frequency                      | Read mode                    | 0                  |     | 8                  | MHz    |  |

| f <sub>CPU</sub>                        | Operating frequency                      | Write/Erase mode             | 1                  |     | 8                  |        |  |

| V <sub>PP</sub>                         | Programming voltage <sup>(2)</sup>       | $4.5V \le V_{DD} \le 5.5V$   | 11.4               |     | 12.6               | V      |  |

| I <sub>DD</sub>                         | Supply current <sup>(3)</sup>            | Write/Erase                  |                    | <10 |                    | μA     |  |

|                                         | V <sub>PP</sub> current <sup>(3)</sup>   | Read (V <sub>PP</sub> = 12V) |                    |     | 200                | μA     |  |

| I <sub>PP</sub>                         | vpp current; /                           | Write/Erase                  |                    |     | 30                 | mA     |  |

| t <sub>VPP</sub>                        | Internal $V_{PP}$ stabilization time     |                              |                    | 10  |                    | μs     |  |

| t <sub>RET</sub>                        | Data retention                           | $T_A = 55^{\circ}C$          | 20                 |     |                    | years  |  |

| N <sub>RW</sub>                         | Write/Erase cycles                       | $T_A = 85^{\circ}C$          | 100                |     |                    | cycles |  |

| T <sub>PROG</sub><br>T <sub>ERASE</sub> | Programming or erasing temperature range |                              | -40                | 25  | 85                 | °C     |  |

1. Data based on characterization results, not tested in production.

2.  $V_{PP}$  must be applied only during the programming or erasing operation and not permanently for reliability reasons.

3. Data based on simulation results, not tested in production.

| Dim.           |     | mm   |     |     | inches |     |

|----------------|-----|------|-----|-----|--------|-----|

|                | Min | Тур  | Max | Min | Тур    | Мах |

| L1             |     | 1.00 |     |     | 0.039  |     |

| Number of pins |     |      |     |     |        |     |

| Ν              |     |      | 3   | 2   |        |     |

Table 114.

32-pin low profile quad flat package mechanical data (continued)

## 13.3 Thermal characteristics

| Table 115. Thermal characte |

|-----------------------------|

|-----------------------------|

| Symbol            | Ratings                                                                        | Value    | Unit |

|-------------------|--------------------------------------------------------------------------------|----------|------|

| R <sub>thJA</sub> | Package thermal resistance (junction to ambient):<br>LQFP44 10x10<br>LQFP327x7 | 52<br>70 | °C/W |

| PD                | Power dissipation <sup>(1)</sup>                                               | 500      | mW   |

| T <sub>Jmax</sub> | Maximum junction temperature <sup>(2)</sup>                                    | 150      | °C   |

1. The maximum power dissipation is obtained from the formula  $P_D = (T_J - T_A) / R_{thJA}$ . The power dissipation of an application can be defined by the user with the formula:  $P_D = P_{INT} + P_{PORT}$  where  $P_{INT}$  is the chip internal power ( $I_{DD} \times V_{DD}$ ) and  $P_{PORT}$  is the port power dissipation depending on the ports used in the application.

2. The maximum chip-junction temperature is based on technology characteristics.

## 13.4 Ecopack information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

## 13.5 Packaging for automatic handling

The devices can be supplied in trays or with tape and reel conditioning.

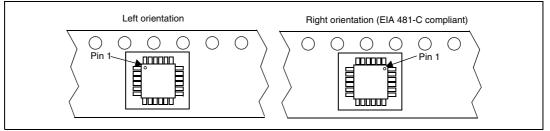

Tape and reel conditioning can be ordered with pin 1 left-oriented or right-oriented when facing the tape sprocket holes as shown in *Figure 89*.

#### Figure 89. pin 1 orientation in tape and reel conditioning

See also Figure 90: ST72F324Bxx-Auto Flash commercial product structure on page 182 and Figure 91: ST72P324Bxx-Auto FastROM commercial product structure on page 184.

# 16 Revision history

| Table 123. | Document revision history |

|------------|---------------------------|

|------------|---------------------------|

| Date                       | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23-May-2007                | 1        | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 23-May-2007<br>23-Jul-2007 | 2        | Replaced ST72324B-Auto with ST72324Bxx-Auto in document title on cover page.<br><i>1 analog peripheral (low current coupling) on page 1</i> : Replaced '12 robust input ports' with '12 input ports'<br><i>Table 1: Device summary on page 1</i> : Corrected order of listed packages Added Section 1.2: Differences between ST72324B-Auto and ST72324B datasheets on page 16<br><i>Figure 2: 44-pin LQFP package pinout on page 17</i> : Displayed port numbers for pins 18 and 20 (port numbers were hidden due to formatting error)<br><i>Table 2: Device pin description on page 18</i> :<br>- replaced V <sub>DDA</sub> with V <sub>REF</sub> in <i>Note 1</i><br>- modified <i>Note 2</i><br>Section <i>5.3.4</i> : Condition Code register (CC) on page 29: Replaced IxSPR with ISPRx<br>Section <i>5.3.4</i> : Condition Code register (CC) on page 29: Replaced IxSPR with ISPRx<br>Section <i>9.5.1</i> : <i>I/O port implementation on page 65</i> : Removed following tables:<br>- Standard ports PA5:4, PC7:0, PD5:0, PE1:0, PF7:6, 4<br>- Interrupt ports PA3, PB3 (without pull-up)<br>- True open drain ports PA7:6 (configurations in these four tables already exist in Table 32: Port configuration)<br>Section <i>12.6.3</i> : Crystal and ceramic resonator oscillators: Replaced two tables Crystal and ceramic resonator oscillators (32 Kbyte Flash and ROM devices) with single Table 95: Crystal and ceramic resonator oscillators on page 157: Deleted footnote detailing SMD and LEAD which was linked to 'Reference' column header<br><i>Table 102</i> : EMI emissions on page 161:<br>- added LQFP32 package to all listed devices<br>- changed values for 32 Kbyte ROM devices<br>Table 105: General characteristics on page 163:<br>- modified Note 6<br><i>Figure 76</i> : RESET pin protection when LVD is enabled(1)(2)(3)(4)(5)(6) on page 168: Replaced 'NW' with 'M ohm' in footnotes to correct formatting error<br>Table 111: 10-bit ADC characteristics on page 172: Modified input current leakage parameter and added Note 2<br>Table 112: ADC accuracy on page 175:<br>- added conditions to total unadjusted error, to offset error and to gain |

|                            |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |