Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                              |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ST7                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               | SCI, SPI                                                              |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 32                                                                    |

| Program Memory Size        | 16KB (16K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 512 x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                           |

| Data Converters            | A/D 12x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 44-LQFP                                                               |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f324bj4t3 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 101. | EMS test results                                     |

|------------|------------------------------------------------------|

| Table 102. | EMI emissions                                        |

| Table 103. | Absolute maximum ratings                             |

| Table 104. | Electrical sensitivities                             |

| Table 105. | General characteristics                              |

| Table 106. | Output driving current                               |

| Table 107. | Asynchronous RESET pin                               |

| Table 108. | ICĆSEL/V <sub>PP</sub> pin                           |

| Table 109. | 16-bit timer                                         |

| Table 110. | SPI characteristics                                  |

| Table 111. | 10-bit ADC characteristics                           |

| Table 112. | ADC accuracy                                         |

| Table 113. | 44-pin low profile quad flat package mechanical data |

| Table 114. | 32-pin low profile quad flat package mechanical data |

| Table 115. | Thermal characteristics                              |

| Table 116. | Flash option bytes                                   |

| Table 117. | Option byte 0 bit description                        |

| Table 118. | Option byte 1 bit description                        |

| Table 119. | Package selection (OPT7)                             |

| Table 120. | STMicroelectronics development tools                 |

| Table 121. | Suggested list of socket types                       |

| Table 122. | Port A and F configuration                           |

| Table 123. | Document revision history                            |

| Figure 49.        | Single master/single slave application                                    |     |

|-------------------|---------------------------------------------------------------------------|-----|

| Figure 50.        | Generic SS timing diagram                                                 |     |

| Figure 51.        | Hardware/software slave select management                                 |     |

| Figure 52.        | Data clock timing diagram(1)                                              | 102 |

| Figure 53.        | Clearing the WCOL bit (Write Collision flag) software sequence            |     |

| Figure 54.        | Single master/multiple slave configuration                                |     |

| Figure 55.        | SCI block diagram                                                         | 112 |

| Figure 56.        | Word length programming                                                   |     |

| Figure 57.        | SCI baud rate and extended prescaler block diagram                        |     |

| Figure 58.        | Bit sampling in Reception mode                                            | 121 |

| Figure 59.        | ADC block diagram                                                         | 131 |

| Figure 60.        | Pin loading conditions                                                    | 145 |

| Figure 61.        | Pin input voltage                                                         | 146 |

| Figure 62.        | f <sub>CPU</sub> max versus V <sub>DD</sub>                               | 148 |

| Figure 63.        | Typical application with an external clock source                         | 153 |

| Figure 64.        | Typical application with a crystal or ceramic resonator (8/16 Kbyte Flash |     |

| -                 | and ROM devices)                                                          | 154 |

| Figure 65.        | Typical application with a crystal or ceramic resonator (32 Kbyte Flash   |     |

| -                 | and ROM devices)                                                          | 155 |

| Figure 66.        | Typical f <sub>OSC(RCINT)</sub> vs T <sub>A</sub>                         | 155 |

| Figure 67.        | Integrated PLL jitter vs signal frequency(1)                              |     |

| Figure 68.        | Unused I/O pins configured as input(1)                                    |     |

| Figure 69.        | Typical I <sub>PU</sub> vs. V <sub>DD</sub> with $V_{IN} = V_{SS}$        |     |

| Figure 70.        | Typical $V_{OL}$ at $V_{DD}$ = 5V (standard ports)                        |     |

| Figure 71.        | Typical $V_{OL}$ at $V_{DD}$ = 5V (high-sink ports).                      |     |

| Figure 72.        | Typical $V_{OH}$ at $V_{DD} = 5V$ .                                       |     |

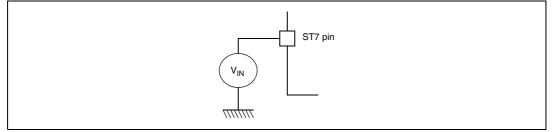

| Figure 73.        | Typical V <sub>OL</sub> vs. V <sub>DD</sub> (standard ports)              |     |

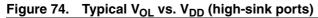

| Figure 74.        | Typical V <sub>OL</sub> vs. V <sub>DD</sub> (high-sink ports)             |     |

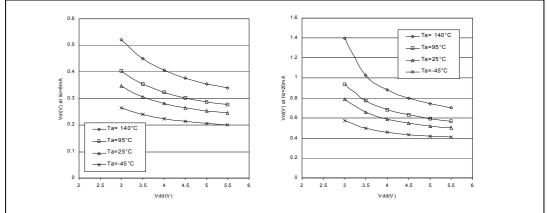

| Figure 75.        | Typical $V_{OH}$ vs. $V_{DD}$                                             |     |

| Figure 76.        | RESET pin protection when LVD is enabled(1)(2)(3)(4)(5)(6)                |     |

| Figure 77.        | RESET pin protection when LVD is disabled(1)(2)(3)(4)                     |     |

| Figure 78.        | Two typical applications with ICCSEL/V <sub>PP</sub> pin(1)               |     |

| Figure 79.        | SPI slave timing diagram with CPHA = 0(1).                                |     |

| Figure 80.        | SPI slave timing diagram with CPHA = 1(1)                                 |     |

| Figure 81.        | SPI master timing diagram(1)                                              |     |

| Figure 82.        | $R_{AIN}$ max. vs $f_{ADC}$ with $C_{AIN} = 0pF(1)$ .                     |     |

| Figure 83.        | Recommended C <sub>AIN</sub> and R <sub>AIN</sub> values(1)               |     |

| Figure 84.        | Typical A/D converter application                                         |     |

| Figure 85.        | Power supply filtering                                                    |     |

| Figure 86.        | ADC accuracy characteristics.                                             |     |

| Figure 87.        | 44-pin low profile quad flat package outline                              |     |

| Figure 88.        | 32-pin low profile quad flat package outline                              |     |

| Figure 89.        | pin 1 orientation in tape and reel conditioning                           |     |

| Figure 90.        | ST72F324Bxx-Auto Flash commercial product structure                       |     |

| Figure 91.        | ST72P324Bxx-Auto FastROM commercial product structure.                    |     |

| Figure 92.        | ST72324Bxx-Auto ROM commercial product structure                          |     |

| · · · · · · · · · |                                                                           |     |

| Address                                                                                                                                      | Block                    | Register label                                                                                                                                                 | Register name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Reset<br>status <sup>(1)</sup>                                                                        | Remarks <sup>(1)</sup>                                                                                                                                                                                                                                                          |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 000Fh<br>0010h<br>0011h                                                                                                                      | Port F <sup>(1)</sup>    | PFDR<br>PFDDR<br>PFOR                                                                                                                                          | Port F data register<br>Port F data direction register<br>Port F option register                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 00h <sup>(2)</sup><br>00h<br>00h                                                                      | R/W<br>R/W<br>R/W                                                                                                                                                                                                                                                               |  |  |  |

| 0012h to<br>0020h                                                                                                                            | Reserved area (15 bytes) |                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                       |                                                                                                                                                                                                                                                                                 |  |  |  |

| 0021h<br>0022h<br>0023h                                                                                                                      | SPI                      | SPIDR<br>SPICR<br>SPICSR                                                                                                                                       | SPI data I/O register<br>SPI control register<br>SPI control/status register                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | xxh<br>0xh<br>00h                                                                                     | R/W<br>R/W<br>R/W                                                                                                                                                                                                                                                               |  |  |  |

| 0024h<br>0025h<br>0026h<br>0027h                                                                                                             | ITC                      | ISPR0<br>ISPR1<br>ISPR2<br>ISPR3                                                                                                                               | Interrupt software priority register 0<br>Interrupt software priority register 1<br>Interrupt software priority register 2<br>Interrupt software priority register 3                                                                                                                                                                                                                                                                                                                                                                             | FFh<br>FFh<br>FFh<br>FFh                                                                              | R/W<br>R/W<br>R/W<br>R/W                                                                                                                                                                                                                                                        |  |  |  |

| 0028h                                                                                                                                        |                          | EICR                                                                                                                                                           | External interrupt control register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 00h                                                                                                   | R/W                                                                                                                                                                                                                                                                             |  |  |  |

| 0029h                                                                                                                                        | Flash                    | FCSR                                                                                                                                                           | Flash control/status register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 00h                                                                                                   | R/W                                                                                                                                                                                                                                                                             |  |  |  |

| 002Ah                                                                                                                                        | Watchdog                 | WDGCR                                                                                                                                                          | Watchdog control register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7Fh                                                                                                   | R/W                                                                                                                                                                                                                                                                             |  |  |  |

| 002Bh                                                                                                                                        | SI                       | SICSR                                                                                                                                                          | System integrity control/status register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                       | R/W                                                                                                                                                                                                                                                                             |  |  |  |

| 002Ch<br>002Dh                                                                                                                               | MCC                      | MCCSR<br>MCCBCR                                                                                                                                                | Main clock control/status register<br>Main clock controller: beep control register                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 00h<br>00h                                                                                            | R/W<br>R/W                                                                                                                                                                                                                                                                      |  |  |  |

| 002Eh to<br>0030h                                                                                                                            |                          |                                                                                                                                                                | Reserved area (3 bytes)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                       |                                                                                                                                                                                                                                                                                 |  |  |  |

| 0031h<br>0032h<br>0033h<br>0034h<br>0035h<br>0036h<br>0037h<br>0038h<br>0039h<br>003Ah<br>003Bh<br>003Ch<br>003Ch<br>003Dh<br>003Eh<br>003Fh | Timer A                  | TACR2<br>TACR1<br>TACSR<br>TAIC1HR<br>TAIC1LR<br>TAOC1LR<br>TAOC1LR<br>TACHR<br>TACLR<br>TACLR<br>TAACLR<br>TAACLR<br>TAIC2HR<br>TAIC2LR<br>TAOC2LR<br>TAOC2LR | Timer A control register 2<br>Timer A control register 1<br>Timer A control/status register<br>Timer A input capture 1 high register<br>Timer A input capture 1 low register<br>Timer A output compare 1 high register<br>Timer A output compare 1 low register<br>Timer A counter high register<br>Timer A counter low register<br>Timer A alternate counter high register<br>Timer A alternate counter low register<br>Timer A input capture 2 high register<br>Timer A output compare 2 low register<br>Timer A output compare 2 low register | 00h<br>00h<br>xxxx x0xxb<br>xxh<br>80h<br>00h<br>FFh<br>FCh<br>FCh<br>FCh<br>xxh<br>xxh<br>80h<br>00h | R/W<br>R/W<br>R/W<br>Read only<br>Read only<br>R/W<br>Read only<br>Read only |  |  |  |

| 0040h                                                                                                                                        |                          | 1                                                                                                                                                              | Reserved area (1 byte)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                       | <u>I</u>                                                                                                                                                                                                                                                                        |  |  |  |

## Table 3. Hardware register map (continued)

## 5.3.5 Stack Pointer register (SP)

| SP  |     |     |     |     |     |     |     |     |     |     |     | R   | eset va | alue: 0 | 1 FFh |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|---------|---------|-------|

| 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2       | 1       | 0     |

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | SP7 | SP6 | SP5 | SP4 | SP3 | SP2     | SP1     | SP0   |

| R/W     | R/W     | R/W   |

The Stack Pointer is a 16-bit register which is always pointing to the next free location in the stack. It is then decremented after data has been pushed onto the stack and incremented before data is popped from the stack (see *Figure 8*).

Since the stack is 256 bytes deep, the 8 most significant bits are forced by hardware. Following an MCU reset, or after a Reset Stack Pointer instruction (RSP), the Stack Pointer contains its reset value (the SP7 to SP0 bits are set) which is the stack higher address.

The least significant byte of the Stack Pointer (called S) can be directly accessed by an LD instruction.

Note: When the lower limit is exceeded, the Stack Pointer wraps around to the stack upper limit, without indicating the stack overflow. The previously stored information is then overwritten and therefore lost. The stack also wraps in case of an underflow.

The stack is used to save the return address during a subroutine call and the CPU context during an interrupt. The user may also directly manipulate the stack by means of the PUSH and POP instructions. In the case of an interrupt, the PCL is stored at the first location pointed to by the SP. Then the other registers are stored in the next locations as shown in *Figure 8*.

- When an interrupt is received, the SP is decremented and the context is pushed on the stack.

- On return from interrupt, the SP is incremented and the context is popped from the stack.

A subroutine call occupies two locations and an interrupt five locations in the stack area.

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                      |

|-----|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2   | СРНА     | <ul> <li>Clock Phase</li> <li>This bit is set and cleared by software.</li> <li>0: The first clock transition is the first data capture edge.</li> <li>1: The second clock transition is the first capture edge.</li> <li>Note: The slave must have the same CPOL and CPHA settings as the master.</li> </ul> |

| 1:0 | SPR[1:0] | Serial clock frequency<br>These bits are set and cleared by software. Used with the SPR2 bit, they select<br>the baud rate of the SPI serial clock SCK output by the SPI in master mode<br>(see <i>Table 56</i> ).<br><i>Note: These 2 bits have no effect in slave mode</i> .                                |

| Table 55. SPICR register description | (continued) |

|--------------------------------------|-------------|

|--------------------------------------|-------------|

#### Table 56. SPI master mode SCK frequency

| Serial clock          | SPR2 | SPR1 | SPR0 |

|-----------------------|------|------|------|

| f <sub>CPU</sub> /4   | 1    | 0    | 0    |

| f <sub>CPU</sub> /8   | 0    | 0    | 0    |

| f <sub>CPU</sub> /16  | 0    | 0    | 1    |

| f <sub>CPU</sub> /32  | 1    | 1    | 0    |

| f <sub>CPU</sub> /64  | 0    | 1    | 0    |

| f <sub>CPU</sub> /128 | 0    | 1    | 1    |

## SPI Control/Status Register (SPICSR)

| SPICSR Reset value: 0000 0000 |      |     |      |          |     |     | 0000 (00h) |

|-------------------------------|------|-----|------|----------|-----|-----|------------|

| 7                             | 6    | 5   | 4    | 3        | 2   | 1   | 0          |

| SPIF                          | WCOL | OVR | MODF | Reserved | SOD | SSM | SSI        |

| RO                            | RO   | RO  | RO   | -        | R/W | R/W | R/W        |

#### SPI Data I/O Register (SPIDR)

| SPIDR |     |     |     |     |     | Reset value | e: undefined |

|-------|-----|-----|-----|-----|-----|-------------|--------------|

| 7     | 6   | 5   | 4   | 3   | 2   | 1           | 0            |

| D7    | D6  | D5  | D4  | D3  | D2  | D1          | D0           |

| R/W   | R/W | R/W | R/W | R/W | R/W | R/W         | R/W          |

The SPIDR register is used to transmit and receive data on the serial bus. In a master device, a write to this register will initiate transmission/reception of another byte.

Note:

During the last clock cycle the SPIF bit is set, a copy of the received data byte in the shift register is moved to a buffer. When the user reads the serial peripheral data I/O register, the buffer is actually being read.

While the SPIF bit is set, all writes to the SPIDR register are inhibited until the SPICSR register is read.

## Warning: A write to the SPIDR register places data directly into the shift register for transmission.

A read to the SPIDR register returns the value located in the buffer and not the content of the shift register (see *Figure 48*).

| Address (Hex.) | Register label        | 7         | 6         | 5         | 4         | 3         | 2         | 1         | 0         |

|----------------|-----------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| 0021h          | SPIDR<br>Reset value  | MSB<br>x  | x         | x         | x         | x         | x         | x         | LSB<br>x  |

| 0022h          | SPICR<br>Reset value  | SPIE<br>0 | SPE<br>0  | SPR2<br>0 | MSTR<br>0 | CPOL<br>x | CPHA<br>x | SPR1<br>x | SPR0<br>x |

| 0023h          | SPICSR<br>Reset value | SPIF<br>0 | WCOL<br>0 | OVR<br>0  | MODF<br>0 | 0         | SOD<br>0  | SSM<br>0  | SSI<br>0  |

#### Table 58. SPI register map and reset values

## 10.5.3 General description

The interface is externally connected to another device by two pins (see *Figure 56*):

- TDO: Transmit Data Output. When the transmitter and the receiver are disabled, the output pin returns to its I/O port configuration. When the transmitter and/or the receiver are enabled and nothing is to be transmitted, the TDO pin is at high level.

- RDI: Receive Data Input is the serial data input. Oversampling techniques are used for data recovery by discriminating between valid incoming data and noise.

Through these pins, serial data is transmitted and received as frames comprising:

- an Idle Line prior to transmission or reception

- a start bit

- a data word (8 or 9 bits) least significant bit first

- a Stop bit indicating that the frame is complete

This interface uses two types of baud rate generator:

- a conventional type for commonly-used baud rates

- an extended type with a prescaler offering a very wide range of baud rates even with non-standard oscillator frequencies

| lable | ;/l. F  | ADCCSR register description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit   | Name    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5     | ADON    | <ul><li>A/D Converter on</li><li>This bit is set and cleared by software.</li><li>0: Disable ADC and stop conversion</li><li>1: Enable ADC and start conversion</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4     | -       | Reserved, must be kept cleared.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3:0   | CH[3:0] | Channel selection<br>These bits are set and cleared by software. They select the analog input to convert.<br>0000: Channel pin = AIN0<br>0001: Channel pin = AIN1<br>0010: Channel pin = AIN2<br>0011: Channel pin = AIN3<br>0100: Channel pin = AIN4<br>0101: Channel pin = AIN5<br>0110: Channel pin = AIN6<br>0111: Channel pin = AIN7<br>1000: Channel pin = AIN8<br>1001: Channel pin = AIN9<br>1010: Channel pin = AIN10<br>1011: Channel pin = AIN10<br>1011: Channel pin = AIN12<br>1101: Channel pin = AIN13<br>1110: Channel pin = AIN14<br>1111: Channel pin = AIN15<br>Note: The number of channels is device dependent. Refer to Section 2: Pin<br>description. |

Table 71. ADCCSR register description

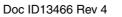

## ADC Data Register High (ADCDRH)

## Table 72. ADCDRH register description

| Bit | Name   | Function                      |

|-----|--------|-------------------------------|

| 7:0 | D[9:2] | MSB of Converted Analog Value |

#### Using a prebyte

The instructions are described with one to four opcodes.

In order to extend the number of available opcodes for an 8-bit CPU (256 opcodes), three different prebyte opcodes are defined. These prebytes modify the meaning of the instruction they precede.

The whole instruction becomes:

- PC-2 End of previous instruction

- PC-1 Prebyte

- PC Opcode

- PC+1 Additional word (0 to 2) according to the number of bytes required to compute the effective address

These prebytes enable the instruction in Y as well as indirect addressing modes to be implemented. They precede the opcode of the instruction in X or the instruction using direct addressing mode. The prebytes are:

- PDY 90 Replace an X based instruction using immediate, direct, indexed, or inherent addressing mode by a Y one.

- PIX 92 Replace an instruction using direct, direct bit, or direct relative addressing mode to an instruction using the corresponding indirect addressing mode. It also changes an instruction using X indexed addressing mode to an instruction using indirect X indexed addressing mode.

- PIY 91 Replace an instruction using X indirect indexed addressing mode by a Y one.

| Mnemo | Description               | Function/example    | Dst    | Src | 11 | н | 10 | Ν | z | С |

|-------|---------------------------|---------------------|--------|-----|----|---|----|---|---|---|

| ADC   | Add with Carry            | A = A + M + C       | А      | М   |    | Н |    | Ν | Z | С |

| ADD   | Addition                  | A = A + M           | А      | М   |    | н |    | Ν | Z | С |

| AND   | Logical And               | A = A . M           | А      | М   |    |   |    | Ν | Z |   |

| BCP   | Bit compare A, memory     | tst (A . M)         | А      | М   |    |   |    | Ν | Z |   |

| BRES  | Bit reset                 | bres Byte, #3       | М      |     |    |   |    |   |   |   |

| BSET  | Bit set                   | bset Byte, #3       | М      |     |    |   |    |   |   |   |

| BTJF  | Jump if bit is false (0)  | btjf Byte, #3, Jmp1 | М      |     |    |   |    |   |   | С |

| BTJT  | Jump if bit is true (1)   | btjt Byte, #3, Jmp1 | М      |     |    |   |    |   |   | С |

| CALL  | Call sub-routine          |                     |        |     |    |   |    |   |   |   |

| CALLR | Call sub-routine relative |                     |        |     |    |   |    |   |   |   |

| CLR   | Clear                     |                     | reg, M |     |    |   |    | 0 | 1 |   |

| СР    | Arithmetic Compare        | tst(Reg - M)        | reg    | М   |    |   |    | Ν | Z | С |

| CPL   | One Complement            | A = FFH-A           | reg, M |     |    |   |    | Ν | Z | 1 |

| DEC   | Decrement                 | dec Y               | reg, M |     |    |   |    | Ν | Z |   |

| HALT  | Halt                      |                     |        |     | 1  |   | 0  |   |   |   |

| IRET  | Interrupt routine return  | Pop CC, A, X, PC    |        |     | 11 | н | 10 | Ν | Z | С |

| INC   | Increment                 | inc X               | reg, M |     |    |   |    | Ν | Z |   |

| JP    | Absolute Jump             | jp [TBL.w]          |        |     |    |   |    |   |   |   |

| JRA   | Jump relative always      |                     |        |     |    |   |    |   |   |   |

| JRT   | Jump relative             |                     |        |     |    |   |    |   |   |   |

| JRF   | Never jump                | jrf *               |        |     |    |   |    |   |   |   |

| JRIH  | Jump if ext. INT pin = 1  | (ext. INT pin high) |        |     |    |   |    |   |   |   |

| JRIL  | Jump if ext. INT pin = 0  | (ext. INT pin low)  |        |     |    |   |    |   |   |   |

| JRH   | Jump if H = 1             | H = 1 ?             |        |     |    |   |    |   |   |   |

| JRNH  | Jump if H = 0             | H = 0 ?             |        |     |    |   |    |   |   |   |

| JRM   | Jump if I1:0 = 11         | 11:0 = 11 ?         |        |     |    |   |    |   |   |   |

| JRNM  | Jump if I1:0 <> 11        | 1:0 <> 11 ?         |        |     |    |   |    |   |   |   |

| JRMI  | Jump if N = 1 (minus)     | N = 1 ?             |        |     |    |   |    |   |   |   |

| JRPL  | Jump if N = 0 (plus)      | N = 0 ?             |        |     |    |   |    |   |   |   |

| JREQ  | Jump if Z = 1 (equal)     | Z = 1 ?             |        |     |    |   |    |   |   |   |

| JRNE  | Jump if Z = 0 (not equal) | Z = 0 ?             |        |     |    |   |    |   |   |   |

| JRC   | Jump if C = 1             | C = 1 ?             |        |     |    |   |    |   |   |   |

| JRNC  | Jump if C = 0             | C = 0 ?             |        |     |    |   |    |   |   |   |

| JRULT | Jump if C = 1             | Unsigned <          |        |     |    | 1 |    |   |   |   |

| JRUGE | Jump if C = 0             | Jmp if unsigned >=  | 1      |     |    | 1 |    |   |   |   |

#### Table 82. Instruction set overview

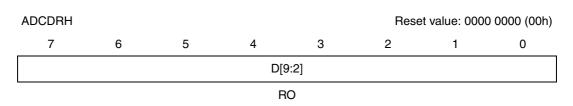

## 12.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 61*.

#### Figure 61. Pin input voltage

## 12.2 Absolute maximum ratings

Stresses above those listed as "absolute maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device under these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

## 12.2.1 Voltage characteristics

#### Table 83.Voltage characteristics

| Symbol                                    | Ratings                                            | Maximum value                                     | Unit |

|-------------------------------------------|----------------------------------------------------|---------------------------------------------------|------|

| V <sub>DD</sub> - V <sub>SS</sub>         | Supply voltage                                     | 6.5                                               |      |

| V <sub>PP</sub> - V <sub>SS</sub>         | Programming voltage                                | 13                                                |      |

|                                           | Input voltage on true open drain pin               | V <sub>SS</sub> - 0.3 to 6.5                      | V    |

| V <sub>IN</sub> <sup>(1)(2)</sup>         | Input voltage on any other pin                     | V <sub>SS</sub> - 0.3 to<br>V <sub>DD</sub> + 0.3 |      |

| $ \Delta V_{DDx} $ and $ \Delta V_{SSx} $ | Variations between different digital power pins    | 50                                                | mV   |

| IV <sub>SSA</sub> - V <sub>SSx</sub> I    | Variations between digital and analog ground pins  | 50                                                | IIIV |

| V <sub>ESD(HBM)</sub>                     | Electrostatic discharge voltage (human body model) | see Section 12.8.                                 | 3 on |

| V <sub>ESD(MM)</sub>                      | Electrostatic discharge voltage (machine model)    | page 160                                          |      |

1. Directly connecting the RESET and I/O pins to V<sub>DD</sub> or V<sub>SS</sub> could damage the device if an unintentional internal reset is generated or an unexpected change of the I/O configuration occurs (for example, due to a corrupted program counter). To guarantee safe operation, this connection has to be done through a pull-up or pull-down resistor (typical:  $4.7k\Omega$  for RESET,  $10k\Omega$  for I/Os). For the same reason, unused I/O pins must not be directly tied to V<sub>DD</sub> or V<sub>SS</sub>.

2.  $I_{INJ(PIN)}$  must never be exceeded. This is implicitly ensured if  $V_{IN}$  maximum is respected. If  $V_{IN}$  maximum cannot be respected, the injection current must be limited externally to the  $I_{INJ(PIN)}$  value. A positive injection is induced by  $V_{IN} > V_{DD}$  while a negative injection is induced by  $V_{IN} < V_{SS}$ . For true open-drain pads, there is no positive injection current, and the corresponding  $V_{IN}$  maximum must always be respected.

## 12.2.2 Current characteristics

| Table 84. Current characteristics | Table 84. | Current characteristics |

|-----------------------------------|-----------|-------------------------|

|-----------------------------------|-----------|-------------------------|

| Symbol                                                                         | Ratings                                                                 |                      | Max value | Unit |

|--------------------------------------------------------------------------------|-------------------------------------------------------------------------|----------------------|-----------|------|

| 1                                                                              | Total current into V <sub>DD</sub> power lines (source) <sup>(1)</sup>  | 32-pin devices       | 75        |      |

| I <sub>VDD</sub>                                                               | Total current into V <sub>DD</sub> power lines (source)                 | 44-pin devices       | 150       |      |

| I                                                                              | Total current out of V <sub>SS</sub> ground lines (sink) <sup>(1)</sup> | 32-pin devices       | 75        |      |

| VSS                                                                            | Total current out of $v_{SS}$ ground lines (sink).                      | 44-pin devices       | 150       |      |

|                                                                                | Output current sunk by any standard I/O and co                          | ntrol pin            | 20        |      |

| I <sub>IO</sub>                                                                | Output current sunk by any high sink I/O pin                            |                      | 40        |      |

|                                                                                | Output current source by any I/Os and control p                         | in                   | - 25      | mA   |

| I <sub>VSS</sub><br>I <sub>IO</sub><br>I <sub>INJ(PIN)</sub> <sup>(2)(3)</sup> | Injected current on V <sub>PP</sub> pin                                 | ± 5                  | IIIA      |      |

|                                                                                | Injected current on RESET pin                                           | ± 5                  |           |      |

| ı (2)(3)                                                                       | Injected current on OSC1 and OSC2 pins                                  | ± 5                  |           |      |

| 'INJ(PIN)````                                                                  | Injected current on ROM and 32 Kbyte Flash de                           | ± 5                  |           |      |

|                                                                                | Injected current on 8/16 Kbyte Flash devices PE                         | + 5                  |           |      |

|                                                                                | Injected current on any other $pin^{(4)(5)}$                            | ± 5                  |           |      |

| $\Sigma I_{\rm INJ(PIN)}^{(2)}$                                                | Total injected current (sum of all I/O and control                      | pins) <sup>(4)</sup> | ± 25      |      |

1. All power (V\_{DD}) and ground (V\_{SS}) lines must always be connected to the external supply.

- I<sub>INJ(PIN)</sub> must never be exceeded. This is implicitly insured if V<sub>IN</sub> maximum is respected. If V<sub>IN</sub> maximum cannot be respected, the injection current must be limited externally to the I<sub>INJ(PIN)</sub> value. A positive injection is induced by V<sub>IN</sub> > V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub> < V<sub>SS</sub>. For true open-drain pads, there is no positive injection current, and the corresponding V<sub>IN</sub> maximum must always be respected.

- 3. Negative injection degrades the analog performance of the device. See note in *Section 12.13.3: ADC* accuracy on page 174. If the current injection limits given in *Section Table 105.: General characteristics on* page 162 are exceeded, general device malfunction may result.

- 4. When several inputs are submitted to a current injection, the maximum SI<sub>INJ(PIN)</sub> is the absolute sum of the positive and negative injected currents (instantaneous values). These results are based on characterization with SI<sub>INJ(PIN)</sub> maximum current injection on four I/O port pins of the device.

- 5. True open drain I/O port pins do not accept positive injection.

## 12.2.3 Thermal characteristics

#### Table 85.Thermal characteristics

| Symbol           | Ratings                                                    | Value            | Unit |

|------------------|------------------------------------------------------------|------------------|------|

| T <sub>STG</sub> | Storage temperature range                                  | -65 to +150      | °C   |

| TJ               | Maximum junction temperature (see Section 13.3: Thermal of | characteristics) |      |

## 12.8 EMC characteristics

Susceptibility tests are performed on a sample basis during product characterization.

## 12.8.1 Functional electromagnetic susceptibility (EMS)

Based on a simple running application on the product (toggling two LEDs through I/O ports), the product is stressed by two electromagnetic events until a failure occurs (indicated by the LEDs).

- **ESD**: Electrostatic discharge (positive and negative) is applied on all pins of the device until a functional disturbance occurs. This test conforms with the IEC 1000-4-2 standard.

- FTB: A burst of fast transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100pF capacitor, until a functional disturbance occurs. This test conforms with the IEC 1000-4-4 standard.

A device reset allows normal operations to be resumed. The test results given in *Table 101* on page 159 are based on the EMS levels and classes defined in application note AN1709.

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### Software recommendations

The software flowchart must include the management of runaway conditions such as:

- corrupted program counter

- unexpected reset

- critical data corruption (control registers...)

#### Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the reset pin or the oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

Figure 73. Typical V<sub>OL</sub> vs. V<sub>DD</sub> (standard ports)

Figure 75. Typical V<sub>OH</sub> vs. V<sub>DD</sub>

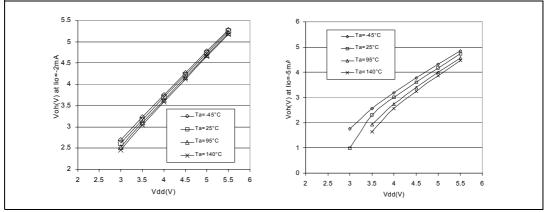

## 12.13.3 ADC accuracy

#### Table 112.ADC accuracy

|                   |                                             |                 |                                          |     | Ма                             |                   |      |

|-------------------|---------------------------------------------|-----------------|------------------------------------------|-----|--------------------------------|-------------------|------|

| Symbol            | Parameter                                   |                 | Conditions                               | Тур | ROM and<br>8/16 Kbyte<br>Flash | 32 Kbyte<br>Flash | Unit |

| IE <sub>T</sub> I | Total unadjusted error <sup>(2)</sup>       |                 |                                          | 3   | 4                              | 6                 |      |

| IE <sub>O</sub> I | Offset error <sup>(2)</sup>                 | $5V^{(2)}$      |                                          | 2   | 3                              | 5                 |      |

| IE <sub>G</sub> I | Gain error <sup>(2)</sup>                   | Ш               | CPU in run mode @ f <sub>ADC</sub> 2 MHz | 0.5 | 3                              | 4.5               | LSB  |

| IE <sub>D</sub> I | Differential linearity error <sup>(2)</sup> | V <sub>DD</sub> |                                          | 1   | 2                              | 2                 |      |

| IELI              | Integral linearity error <sup>(2)</sup>     |                 |                                          | I   | 2                              | 3                 |      |

1. Data based on characterization results, monitored in production to guarantee 99.73% within  $\pm$  max value from -40°C to 125°C ( $\pm$  3 $\sigma$  distribution limits).

ADC accuracy vs. negative injection current: Injecting negative current may reduce the accuracy of the conversion being performed on another analog input. Any positive injection current within the limits specified for I<sub>INJ(PIN)</sub> and ΣI<sub>INJ(PIN)</sub> in Section 12.9 does not affect the ADC accuracy.

#### Figure 86. ADC accuracy characteristics

| Dim.  |     | mm   |                |     | inches |     |

|-------|-----|------|----------------|-----|--------|-----|

| Dini. | Min | Тур  | Max            | Min | Тур    | Мах |

| L1    |     | 1.00 |                |     | 0.039  |     |

|       |     | N    | lumber of pins |     |        |     |

| Ν     |     |      | 3              | 2   |        |     |

Table 114.

32-pin low profile quad flat package mechanical data (continued)

# 14.2 ROM device ordering information and transfer of customer code

Customer code is made up of the ROM/FASTROM contents and the list of the selected options (if any). The ROM/FASTROM contents are to be sent with the S19 hexadecimal file generated by the development tool. All unused bytes must be set to FFh. Complete the appended ST72324B-Auto Microcontroller FASTROM/ROM Option List on page 185 to communicate the selected options to STMicroelectronics.

Refer to application note AN1635 for information on the counter listing returned by ST after code has been transferred.

The following *Figure 91: ST72P324Bxx-Auto FastROM commercial product structure* and *Figure 92: ST72324Bxx-Auto ROM commercial product structure* serve as guides for ordering. The STMicroelectronics Sales Organization will be pleased to provide detailed information on contractual points.

**Caution:** The readout protection binary value is inverted between ROM and Flash products. The option byte checksum differs between ROM and Flash.

| Example:                                                            | ST72               | 324B       | т      | А           | /xxx  | Х | S |

|---------------------------------------------------------------------|--------------------|------------|--------|-------------|-------|---|---|

| Product class                                                       |                    |            |        |             |       |   |   |

| ST72 microcontroller                                                |                    |            |        |             |       |   |   |

|                                                                     |                    |            |        |             |       |   |   |

| 324B = 324B sub-family                                              |                    |            |        |             |       |   |   |

|                                                                     |                    |            |        |             |       |   |   |

| Package type                                                        |                    |            |        |             |       |   |   |

| T = LQFP                                                            |                    |            |        |             |       |   |   |

| Temperature range                                                   |                    |            |        |             |       |   |   |

| A = -40 °C to 85 °C                                                 |                    |            |        |             |       |   |   |

| B = -40 °C to 105 °C                                                |                    |            |        |             |       |   |   |

| C = -40 °C to 125 °C                                                |                    |            |        |             |       |   |   |

| D = -40 °C to 115 °C                                                |                    |            |        |             |       |   |   |

| Code name                                                           |                    |            |        |             |       |   |   |

| Defined by                                                          |                    |            |        |             |       |   |   |

| STMicroelectronics.<br>Denotes ROM code, pinout                     |                    |            |        |             |       |   |   |

| and program memory size.                                            |                    |            |        |             |       |   |   |

|                                                                     |                    |            |        |             |       |   |   |

| Tape and Reel conditioning                                          | options            | s (left bl | ank    | if Tra      | ay) — |   |   |

| TR or $R = Pin 1$ left-oriented<br>TX or $X = Pin 1$ right-oriented |                    | 1 C        | anlia  | <b>~</b> +\ |       |   |   |

|                                                                     | (EIA 40            |            | ipilai | 11)         |       |   |   |

| ECOPACK/Fab code                                                    |                    |            |        |             |       |   |   |

| Blank or E = Lead-free ECOP.                                        | ACK <sup>®</sup> F | hoenix     | Fab    |             |       |   |   |

| S = Lead-free ECOPACK <sup>®</sup> Ca                               | tania F            | ah         |        |             |       |   |   |

Figure 92. ST72324Bxx-Auto ROM commercial product structure

## **15 Known limitations**

## 15.1 All Flash and ROM devices

#### 15.1.1 Safe connection of OSC1/OSC2 pins

The OSC1 and/or OSC2 pins must not be left unconnected, otherwise the ST7 main oscillator may start and, in this configuration, could generate an  $f_{OSC}$  clock frequency in excess of the allowed maximum (> 16 MHz), putting the ST7 in an unsafe/undefined state. Refer to *Section 6.3 on page 32*.

#### 15.1.2 External interrupt missed

To avoid any risk of generating a parasitic interrupt, the edge detector is automatically disabled for one clock cycle during an access to either DDR and OR. Any input signal edge during this period will not be detected and will not generate an interrupt.

This case can typically occur if the application refreshes the port configuration registers at intervals during runtime.

#### Workaround

The workaround is based on software checking the level on the interrupt pin before and after writing to the PxOR or PxDDR registers. If there is a level change (depending on the sensitivity programmed for this pin) the interrupt routine is invoked using the call instruction with three extra PUSH instructions before executing the interrupt routine (this is to make the call compatible with the IRET instruction at the end of the interrupt service routine).

But detection of the level change does not make sure that edge occurs during the critical one cycle duration and the interrupt has been missed. This may lead to occurrence of same interrupt twice (one hardware and another with software call).

To avoid this, a semaphore is set to '1' before checking the level change. The semaphore is changed to level '0' inside the interrupt routine. When a level change is detected, the semaphore status is checked and if it is '1' this means that the last interrupt has been missed. In this case, the interrupt routine is invoked with the call instruction.

There is another possible case that is, if writing to PxOR or PxDDR is done with global interrupts disabled (interrupt mask bit set). In this case, the semaphore is changed to '1' when the level change is detected. Detecting a missed interrupt is done after the global interrupts are enabled (interrupt mask bit reset) and by checking the status of the semaphore. If it is '1' this means that the last interrupt was missed and the interrupt routine is invoked with the call instruction.

To implement the workaround, the following software sequence is to be followed for writing into the PxOR/PxDDR registers. The example is for Port PF1 with falling edge interrupt sensitivity. The software sequence is given for both cases (global interrupt disabled/enabled).

#### Nested interrupt context

The symptom does not occur when the interrupts are handled normally, that is, when:

- The interrupt flag is cleared within its own interrupt routine

- The interrupt flag is cleared within any interrupt routine with higher or identical priority level

- The interrupt flag is cleared in any part of the code while this interrupt is disabled

If these conditions are not met, the symptom can be avoided by implementing the following sequence:

- PUSH CC

- SIM

- Reset interrupt flag

- POP CC

## 15.1.5 16-bit timer PWM mode

In PWM mode, the first PWM pulse is missed after writing the value FFFCh in the OC1R register (OC1HR, OC1LR). It leads to either full or no PWM during a period, depending on the OLVL1 and OLVL2 settings.

## 15.1.6 TIMD set simultaneously with OC interrupt

If the 16-bit timer is disabled at the same time the output compare event occurs then output compare flag gets locked and cannot be cleared before the timer is enabled again.

#### Impact on the application

If output compare interrupt is enabled, then the output compare flag cannot be cleared in the timer interrupt routine. Consequently the interrupt service routine is called repeatedly.

#### Workaround

Disable the timer interrupt before disabling the timer. Again while enabling, first enable the timer then the timer interrupts.

- Perform the following to disable the timer:

- TACR1 or TBCR1 = 0x00h; // Disable the compare interrupt

- TACSR I or TBCSR I = 0x40; // Disable the timer

- Perform the following to enable the timer again:

- TACSR & or TBCSR & = ~0x40; // Enable the timer

- TACR1 or TBCR1 = 0x40; // Enable the compare interrupt

## 15.1.7 SCI wrong break duration

#### Description

A single break character is sent by setting and resetting the SBK bit in the SCICR2 register. In some cases, the break character may have a longer duration than expected:

- 20 bits instead of 10 bits if M = 0

- 22 bits instead of 11 bits if M = 1