Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                              |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ST7                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               | SCI, SPI                                                              |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 24                                                                    |

| Program Memory Size        | 16KB (16K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 512 x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                           |

| Data Converters            | A/D 12x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 32-LQFP                                                               |

| Supplier Device Package    |                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f324bk4t6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

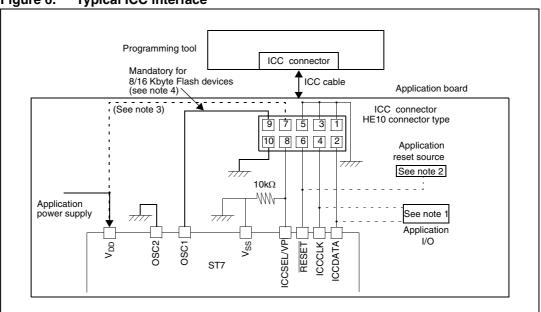

Figure 6. Typical ICC interface

- If the ICCCLK or ICCDATA pins are only used as outputs in the application, no signal isolation is necessary. As soon as the programming tool is plugged to the board, even if an ICC session is not in progress, the ICCCLK and ICCDATA pins are not available for the application. If they are used as inputs by the application, isolation such as a serial resistor has to be implemented in case another device forces the signal. Refer to the Programming Tool documentation for recommended resistor values.

- 2. During the ICC session, the programming tool must control the RESET pin. This can lead to conflicts between the programming tool and the application reset circuit if it drives more than 5mA at high level (PUSH-pull output or pull-up resistor <1K). A schottky diode can be used to isolate the application reset circuit in this case. When using a classical RC network with R>1K or a reset management IC with open drain output and pull-up resistor >1K, no additional components are needed. In all cases the user must ensure that no external reset is generated by the application during the ICC session.

- 3. The use of Pin 7 of the ICC connector depends on the programming tool architecture. This pin must be connected when using most ST programming tools (it is used to monitor the application power supply). Please refer to the programming tool manual.

- 4. Pin 9 has to be connected to the OSC1 (OSCIN) pin of the ST7 when the clock is not available in the application or if the selected clock option is not programmed in the option byte. ST7 devices with multi-oscillator capability need to have OSC2 grounded in this case.

- **Caution:** External clock ICC entry mode is mandatory in ST72F324B 8/16 Kbyte Flash devices. In this case pin 9 must be connected to the OSC1 (OSCIN) pin of the ST7 and OSC2 must be grounded. 32 Kbyte Flash devices may use external clock or application clock ICC entry mode.

# 4.5 ICP (in-circuit programming)

To perform ICP the microcontroller must be switched to ICC (in-circuit communication) mode by an external controller or programming tool.

Depending on the ICP code downloaded in RAM, Flash memory programming can be fully customized (number of bytes to program, program locations, or selection serial communication interface for downloading).

When using an STMicroelectronics or third-party programming tool that supports ICP and the specific microcontroller device, the user needs only to implement the ICP hardware interface on the application board (see *Figure 6*). For more details on the pin locations, refer to the device pinout description.

Doc ID13466 Rev 4

## 5.3.1 Accumulator (A)

The Accumulator is an 8-bit general purpose register used to hold operands and the results of the arithmetic and logic calculations and to manipulate data.

## 5.3.2 Index registers (X and Y)

These 8-bit registers are used to create effective addresses or as temporary storage areas for data manipulation. (The Cross-Assembler generates a precede instruction (PRE) to indicate that the following instruction refers to the Y register.)

The Y register is not affected by the interrupt automatic procedures.

### 5.3.3 Program counter (PC)

The program counter is a 16-bit register containing the address of the next instruction to be executed by the CPU. It is made of two 8-bit registers PCL (Program Counter Low which is the LSB) and PCH (Program Counter High which is the MSB).

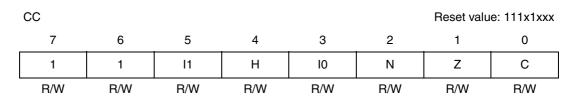

## 5.3.4 Condition Code register (CC)

The 8-bit Condition Code register contains the interrupt masks and four flags representative of the result of the instruction just executed. This register can also be handled by the PUSH and POP instructions. These bits can be individually tested and/or controlled by specific instructions.

| Table 6. | Arithmetic management bits |

|----------|----------------------------|

|----------|----------------------------|

| Blt | Name | Function                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 4   | н    | <ul> <li>Half carry</li> <li>This bit is set by hardware when a carry occurs between bits 3 and 4 of the ALU during an ADD or ADC instructions. It is reset by hardware during the same instructions.</li> <li>0: No half carry has occurred.</li> <li>1: A half carry has occurred.</li> <li>This bit is tested using the JRH or JRNH instruction. The H bit is useful in BCD arithmetic subroutines.</li> </ul>       |  |  |  |

| 2   | Ν    | Negative<br>This bit is set and cleared by hardware. It is representative of the result sign of the last<br>arithmetic, logical or data manipulation. It is a copy of the result 7th bit.<br>0: The result of the last operation is positive or null.<br>1: The result of the last operation is negative (that is, the most significant bit is a logic<br>1.<br>This bit is accessed by the JRMI and JRPL instructions. |  |  |  |

| Blt | Name | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1   | Z    | <ul> <li>Zero (Arithmetic Management bit)</li> <li>This bit is set and cleared by hardware. This bit indicates that the result of the last arithmetic, logical or data manipulation is zero.</li> <li>0: The result of the last operation is different from zero.</li> <li>1: The result of the last operation is zero.</li> <li>This bit is accessed by the JREQ and JRNE test instructions.</li> </ul>                                                                                    |  |  |  |  |  |

| 0   | С    | <ul> <li>Carry/borrow</li> <li>This bit is set and cleared by hardware and software. It indicates an overflow or an underflow has occurred during the last arithmetic operation.</li> <li>0: No overflow or underflow has occurred.</li> <li>1: An overflow or underflow has occurred.</li> <li>This bit is driven by the SCF and RCF instructions and tested by the JRC and JRNC instructions. It is also affected by the 'bit test and branch', shift and rotate instructions.</li> </ul> |  |  |  |  |  |

#### Table 6. Arithmetic management bits (continued)

| Table 7.Software interrupt bits | le 7. Software ir | nterrupt bits |

|---------------------------------|-------------------|---------------|

|---------------------------------|-------------------|---------------|

| Blt | Name | Function                                                                                                                                            |

|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 5   | 11   | Software Interrupt Priority 1<br>The combination of the I1 and I0 bits determines the current interrupt software priority<br>(see <i>Table 8</i> ). |

| 3   | 10   | Software Interrupt Priority 0<br>The combination of the I1 and I0 bits determines the current interrupt software priority<br>(see <i>Table 8</i> ). |

#### Table 8. Interrupt software priority selection

| Interrupt software priority   | Level | 11 | 10 |

|-------------------------------|-------|----|----|

| Level 0 (main)                | Low   | 1  | 0  |

| Level 1                       |       | 0  | 1  |

| Level 2                       | ↓     | 0  | 0  |

| Level 3 (= interrupt disable) | High  | 1  | 1  |

These two bits are set/cleared by hardware when entering in interrupt. The loaded value is given by the corresponding bits in the interrupt software priority registers (ISPRx). They can be also set/cleared by software with the RIM, SIM, IRET, HALT, WFI and PUSH/POP instructions.

See *Section 7: Interrupts on page 41* for more details.

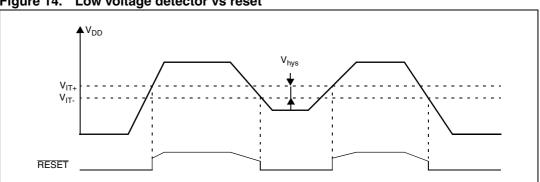

Provided the minimum  $V_{DD}$  value (guaranteed for the oscillator frequency) is above  $V_{IT-}$ , the MCU can only be in two modes:

- under full software control

- in static safe reset

In these conditions, secure operation is always ensured for the application without the need for external reset hardware.

During an LVD reset, the RESET pin is held low, thus permitting the MCU to reset other devices.

- Note: 1 The LVD allows the device to be used without any external reset circuitry.

- 2 If the medium or low thresholds are selected, the detection may occur outside the specified operating voltage range. Below 3.8V, device operation is not guaranteed.

- 3 The LVD is an optional function which can be selected by option byte.

- 4 It is recommended to make sure that the  $V_{DD}$  supply voltage rises monotonously when the device is exiting from reset, to ensure the application functions properly.

Figure 14. Low voltage detector vs reset

#### 6.5.2 AVD (auxiliary voltage detector)

The AVD is based on an analog comparison between a  $V_{\text{IT-(AVD)}}$  and  $V_{\text{IT+(AVD)}}$  reference value and the V<sub>DD</sub> main supply. The V<sub>IT</sub> reference value for falling voltage is lower than the V<sub>IT+</sub> reference value for rising voltage in order to avoid parasitic detection (hysteresis).

The output of the AVD comparator is directly readable by the application software through a real-time status bit (AVDF) in the SICSR register. This bit is read only.

The AVD function is active only if the LVD is enabled through the option byte (see Caution: Section 14.1 on page 179).

## Monitoring the V<sub>DD</sub> main supply

The AVD voltage threshold value is relative to the selected LVD threshold configured by option byte (see Section 14.1 on page 179).

If the AVD interrupt is enabled, an interrupt is generated when the voltage crosses the  $V_{IT+(AVD)}$  or  $V_{IT-(AVD)}$  threshold (AVDF bit toggles).

In the case of a drop in voltage, the AVD interrupt acts as an early warning, allowing software to shut down safely before the LVD resets the microcontroller. See Figure 15.

# 6.6 SI registers

# 6.6.1 System integrity (SI) control/status register (SICSR)

| SICSR Reset value: 000x |       |      |       |          |   |   | k 000x (00h) |  |

|-------------------------|-------|------|-------|----------|---|---|--------------|--|

| 7                       | 6     | 5    | 4     | 3        | 2 | 1 | 0            |  |

| Res                     | AVDIE | AVDF | LVDRF | Reserved |   |   | WDGRF        |  |

| -                       | R/W   | RO   | R/W   |          | - |   | R/W          |  |

Table 12.SICSR register description

| Bit | Name  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7   | -     | Reserved, must be kept cleared                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 6   | AVDIE | Voltage Detector Interrupt Enable<br>This bit is set and cleared by software. It enables an interrupt to be generated<br>when the AVDF flag changes (toggles). The pending interrupt information is<br>automatically cleared when software enters the AVD interrupt routine<br>0: AVD interrupt disabled<br>1: AVD interrupt enabled                                                                                                             |  |  |  |

| 5   | AVDF  | <ul> <li>Voltage Detector Flag</li> <li>This read-only bit is set and cleared by hardware. If the AVDIE bit is set, an interrupt request is generated when the AVDF bit changes value. Refer to <i>Figure 15</i> and to <i>Section 6.5.2: AVD (auxiliary voltage detector)</i> for additional details.</li> <li>0: V<sub>DD</sub> over V<sub>IT+(AVD)</sub> threshold</li> <li>1: V<sub>DD</sub> under V<sub>IT+(AVD)</sub> threshold</li> </ul> |  |  |  |

| 4   | LVDRF | LVD Reset Flag<br>This bit indicates that the last reset was generated by the LVD block. It is set by<br>hardware (LVD reset) and cleared by software (writing zero). See WDGRF flag<br>description for more details. When the LVD is disabled by option byte, the LVDRF<br>bit value is undefined.                                                                                                                                              |  |  |  |

| 3:1 | -     | Reserved, must be kept cleared                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 0   | WDGRF | Watchdog Reset Flag<br>This bit indicates that the last reset was generated by the Watchdog peripheral. It is<br>set by hardware (watchdog reset) and cleared by software (writing zero) or an LVD<br>reset (to ensure a stable cleared state of the WDGRF flag when CPU starts).<br>Combined with the LVDRF information, the flag description is given in <i>Table 13</i> .                                                                     |  |  |  |

| Table 13. | Reset source flags | 5 |

|-----------|--------------------|---|

|-----------|--------------------|---|

| Reset sources      | LVDRF | WDGRF |

|--------------------|-------|-------|

| External RESET pin | 0     | 0     |

| Watchdog           | 0     | 1     |

| LVD                | 1     | Х     |

| No. | Source Description |                                              | Register<br>label | Priority<br>order  | Exit from<br>Halt/Active Halt | Address vector |

|-----|--------------------|----------------------------------------------|-------------------|--------------------|-------------------------------|----------------|

|     | Reset Reset        |                                              | NI/A              |                    | yes                           | FFFEh-FFFFh    |

|     | TRAP               | Software interrupt                           | N/A               |                    | no                            | FFFCh-FFFDh    |

| 0   |                    | Not used                                     |                   |                    |                               | FFFAh-FFFBh    |

| 1   | MCC/RTC            | Main clock controller time base<br>interrupt | MCCSR             | Higher<br>priority | yes                           | FFF8h-FFF9h    |

| 2   | ei0                | External interrupt port A30                  |                   |                    | yes                           | FFF6h-FFF7h    |

| 3   | ei1                | External interrupt port F20                  |                   |                    | yes                           | FFF4h-FFF5h    |

| 4   | ei2                | External interrupt port B30                  | N/A               |                    | yes                           | FFF2h-FFF3h    |

| 5   | ei3                | External interrupt port B74                  |                   |                    | yes                           | FFF0h-FFF1h    |

| 6   |                    | Not used                                     |                   |                    |                               | FFEEh-FFEFh    |

| 7   | SPI                | SPI peripheral interrupts                    | SPICSR            |                    | yes                           | FFECh-FFEDh    |

| 8   | Timer A            | Timer A peripheral interrupts                | TASR              |                    | no                            | FFEAh-FFEBh    |

| 9   | Timer B            | Timer B peripheral interrupts                | TBSR              | ┥                  | no                            | FFE8h-FFE9h    |

| 10  | SCI                | SCI peripheral interrupts                    | SCISR             | Lower              | no                            | FFE6h-FFE7h    |

| 11  | AVD                | Auxiliary voltage detector interrupt         | SICSR             | priority           | no                            | FFE4h-FFE5h    |

## Table 25. Interrupt mapping

## 10.2.5 Low power modes

Table 37. Effect of low power modes on MCC/RTC

| Mode        | Description                                                                                                                                    |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Wait        | No effect on MCC/RTC peripheral. MCC/RTC interrupt causes the device to exit from Wait mode.                                                   |

| Active Halt | No effect on MCC/RTC counter (OIE bit is set), the registers are frozen.<br>MCC/RTC interrupt causes the device to exit from Active Halt mode. |

| Halt        | MCC/RTC counter and registers are frozen. MCC/RTC operation resumes when the MCU is woken up by an interrupt with Exit from Halt capability.   |

## 10.2.6 Interrupts

The MCC/RTC interrupt event generates an interrupt if the OIE bit of the MCCSR register is set and the interrupt mask in the CC register is not active (RIM instruction).

| Table 38. | MCC/RTC interrupt control/wake-up capability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14510 001 | meente of the ofference of the outpublic |

| Interrupt event          | Event flag | Enable control bit | Exit from WAIT | Exit from HALT    |

|--------------------------|------------|--------------------|----------------|-------------------|

| Time base overflow event | OIF        | OIE                | Yes            | No <sup>(1)</sup> |

1. The MCC/RTC interrupt wakes up the MCU from Active Halt mode, not from Halt mode.

## 10.2.7 MCC registers

## MCC control/status register (MCCSR)

| MCCSR | MCCSR Reset value: 0000 0000 (00h) |       |     |    |       | 0 0000 (00h) |     |

|-------|------------------------------------|-------|-----|----|-------|--------------|-----|

| 7     | 6                                  | 5     | 4   | 3  | 2     | 1            | 0   |

| MCO   | CP[                                | [1:0] | SMS | TB | [1:0] | OIE          | OIF |

| R/W   | R/                                 | W     | R/W | R  | /W    | R/W          | R/W |

### Table 39.MCCSR register description

| Bit | Name | Function                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | МСО  | <ul> <li>Main Clock Out selection</li> <li>This bit enables the MCO alternate function on the PF0 I/O port. It is set and cleared by software.</li> <li>0: MCO alternate function disabled (I/O pin free for general-purpose I/O).</li> <li>1: MCO alternate function enabled (f<sub>CPU</sub> on I/O port).</li> <li>Note: To reduce power consumption, the MCO function is not active in Active Halt mode.</li> </ul> |

| Bit | Name    | Function                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6:5 | CP[1:0] | CPU Clock Prescaler<br>These bits select the CPU clock prescaler which is applied in different slow modes.<br>Their action is conditioned by the setting of the SMS bit. These two bits are set and<br>cleared by software:<br>00: $f_{CPU}$ in Slow mode = $f_{OSC2}/2$<br>01: $f_{CPU}$ in Slow mode = $f_{OSC2}/4$<br>10: $f_{CPU}$ in Slow mode = $f_{OSC2}/8$<br>11: $f_{CPU}$ in Slow mode = $f_{OSC2}/16$ |

| 4   | SMS     | <ul> <li>Slow Mode Select</li> <li>This bit is set and cleared by software.</li> <li>0: Normal mode. f<sub>CPU</sub> = f<sub>OSC2</sub>.</li> <li>1: Slow mode. f<sub>CPU</sub> is given by CP1, CP0.</li> <li>See Section 8.2: Slow mode and Section 10.2: Main clock controller with real-time clock and beeper (MCC/RTC) for more details.</li> </ul>                                                         |

| 3:2 | TB[1:0] | Time Base control<br>These bits select the programmable divider time base. They are set and cleared by<br>software (see <i>Table 40</i> ). A modification of the time base is taken into account at the<br>end of the current period (previously set) to avoid an unwanted time shift. This<br>allows to use this time base as a real-time clock.                                                                |

| 1   | OIE     | Oscillator interrupt Enable<br>This bit set and cleared by software.<br>0: Oscillator interrupt disabled<br>1: Oscillator interrupt enabled<br>This interrupt can be used to exit from Active Halt mode. When this bit is set, calling<br>the ST7 software HALT instruction enters the Active Halt power saving mode.                                                                                            |

| 0   | OIF     | Oscillator interrupt Flag<br>This bit is set by hardware and cleared by software reading the MCCSR register. It<br>indicates when set that the main oscillator has reached the selected elapsed time<br>(TB1:0).<br>0: Timeout not reached<br>1: Timeout reached<br><b>Caution</b> : The BRES and BSET instructions must not be used on the MCCSR<br>register to avoid unintentionally clearing the OIF bit.     |

| Table 39. | MCCSR register | description | (continued) | ) |

|-----------|----------------|-------------|-------------|---|

|-----------|----------------|-------------|-------------|---|

#### Table 40.Time base selection

| Counter procedur  | Time base                 |                           |     | тво |

|-------------------|---------------------------|---------------------------|-----|-----|

| Counter prescaler | f <sub>OSC2</sub> = 4 MHz | f <sub>OSC2</sub> = 8 MHz | TB1 | ТБV |

| 16000             | 4ms                       | 2ms                       | 0   | 0   |

| 32000             | 8ms                       | 4ms                       | 0   | 1   |

| 80000             | 20ms                      | 10ms                      | 1   | 0   |

| 200000            | 50ms                      | 25ms                      | 1   | 1   |

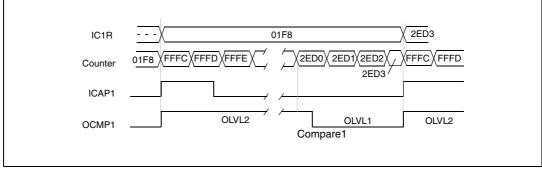

The OC1R register value required for a specific timing application can be calculated using the following formula:

OC*i*R value =

$$\frac{t * f_{CPU}}{PRESC}$$

- 5

Where:

t = Pulse period (in seconds)  $f_{CPU}$  = CPU clock frequency (in hertz) PRESC = Timer prescaler factor (2, 4 or 8 depending on the CC[1:0] bits; see *Table 50*)

If the timer clock is an external clock the formula is:

Where:

t = Pulse period (in seconds)

f<sub>EXT</sub> = External timer clock frequency (in hertz)

When the value of the counter is equal to the value of the contents of the OC1R register, the OLVL1 bit is output on the OCMP1 pin (see *Figure 45*).

- Note: 1 The OCF1 bit cannot be set by hardware in one pulse mode but the OCF2 bit can generate an Output Compare interrupt.

- 2 When the Pulse Width Modulation (PWM) and One Pulse Mode (OPM) bits are both set, the PWM mode is the only active one.

- 3 If OLVL1 = OLVL2 a continuous signal will be seen on the OCMP1 pin.

- 4 The ICAP1 pin can not be used to perform input capture. The ICAP2 pin can be used to perform input capture (ICF2 can be set and IC2R can be loaded) but the user must take care that the counter is reset each time a valid edge occurs on the ICAP1 pin and ICF1 can also generates interrupt if ICIE is set.

- 5 When one pulse mode is used OC1R is dedicated to this mode. Nevertheless OC2R and OCF2 can be used to indicate a period of time has been elapsed but cannot generate an output waveform because the level OLVL2 is dedicated to the one pulse mode.

Figure 45. One Pulse mode timing example<sup>(1)</sup>

1. IEDG1 = 1, OC1R = 2ED0h, OLVL1 = 0, OLVL2 = 1

## 10.4.5 Error flags

## Master mode fault (MODF)

Master mode fault occurs when the master device has its  $\overline{SS}$  pin pulled low.

When a Master mode fault occurs:

- The MODF bit is set and an SPI interrupt request is generated if the SPIE bit is set.

- The SPE bit is reset. This blocks all output from the device and disables the SPI peripheral.

- The MSTR bit is reset, thus forcing the device into slave mode.

Clearing the MODF bit is done through a software sequence:

- 1. A read access to the SPICSR register while the MODF bit is set.

- 2. A write to the SPICR register.

Note:

To avoid any conflicts in an application with multiple slaves, the  $\overline{SS}$  pin must be pulled high during the MODF bit clearing sequence. The SPE and MSTR bits may be restored to their original state during or after this clearing sequence.

Hardware does not allow the user to set the SPE and MSTR bits while the MODF bit is set except in the MODF bit clearing sequence.

## **Overrun condition (OVR)**

An overrun condition occurs, when the master device has sent a data byte and the slave device has not cleared the SPIF bit issued from the previously transmitted byte.

When an Overrun occurs the OVR bit is set and an interrupt request is generated if the SPIE bit is set.

In this case, the receiver buffer contains the byte sent after the SPIF bit was last cleared. A read to the SPIDR register returns this byte. All other bytes are lost.

The OVR bit is cleared by reading the SPICSR register.

### Write collision error (WCOL)

A write collision occurs when the software tries to write to the SPIDR register while a data transfer is taking place with an external device. When this happens, the transfer continues uninterrupted and the software write is unsuccessful.

Write collisions can occur both in master and slave mode. See also *Slave Select management on page 99*.

Note: A read collision will never occur since the received data byte is placed in a buffer in which access is always synchronous with the MCU operation.

The WCOL bit in the SPICSR register is set if a write collision occurs.

No SPI interrupt is generated when the WCOL bit is set (the WCOL bit is a status flag only).

A software sequence clears the WCOL bit (see *Figure 53*).

# 10.4.8 SPI registers

# SPI Control Register (SPICR)

| ę | SPICR |     |      |      |      | Reset value: 0000 xxxx (0xh) |          |   |

|---|-------|-----|------|------|------|------------------------------|----------|---|

|   | 7     | 6   | 5    | 4    | 3    | 2                            | 1        | 0 |

|   | SPIE  | SPE | SPR2 | MSTR | CPOL | CPHA                         | SPR[1:0] |   |

|   | R/W   | R/W | R/W  | R/W  | R/W  | R/W                          | R/W      |   |

| Bit | Name | Function                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | SPIE | <ul> <li>Serial Peripheral Interrupt Enable</li> <li>This bit is set and cleared by software.</li> <li>0: Interrupt is inhibited.</li> <li>1: An SPI interrupt is generated whenever SPIF = 1, MODF = 1 or OVR = 1 in the SPICSR register.</li> </ul>                                                                                                                                                                              |

| 6   | SPE  | <ul> <li>Serial Peripheral Output Enable</li> <li>This bit is set and cleared by software. It is also cleared by hardware when, in master mode, SS = 0 (see <i>Master mode fault (MODF) on page 103</i>). The SPE bit is cleared by reset, so the SPI peripheral is not initially connected to the external pins.</li> <li>0: I/O pins free for general purpose I/O</li> <li>1: SPI I/O pin alternate functions enabled</li> </ul> |

| 5   | SPR2 | <ul> <li>Divider Enable</li> <li>This bit is set and cleared by software and is cleared by reset. It is used with the SPR[1:0] bits to set the baud rate. Refer to <i>Table 56: SPI master mode SCK frequency</i>.</li> <li>0: Divider by 2 enabled</li> <li>1: Divider by 2 disabled</li> <li><i>Note: This bit has no effect in slave mode.</i></li> </ul>                                                                       |

| 4   | MSTR | <ul> <li>Master mode</li> <li>This bit is set and cleared by software. It is also cleared by hardware when, in master mode, SS = 0 (see <i>Master mode fault (MODF) on page 103</i>).</li> <li>0: Slave mode</li> <li>1: Master mode. The function of the SCK pin changes from an input to an output and the functions of the MISO and MOSI pins are reversed.</li> </ul>                                                          |

| 3   | CPOL | <ul> <li>Clock Polarity</li> <li>This bit is set and cleared by software. This bit determines the idle state of the serial Clock. The CPOL bit affects both the master and slave modes.</li> <li>0: SCK pin has a low level idle state</li> <li>1: SCK pin has a high level idle state</li> <li>Note: If CPOL is changed at the communication byte boundaries, the SPI must be disabled by resetting the SPE bit.</li> </ul>       |

| Table | 307. | SPICSR register description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit   | Name | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 7     | SPIF | <ul> <li>Serial Peripheral data transfer flag</li> <li>This bit is set by hardware when a transfer has been completed. An interrupt is generated if SPIE = 1 in the SPICR register. It is cleared by a software sequence (an access to the SPICSR register followed by a write or a read to the SPIDR register).</li> <li>0: Data transfer is in progress or the flag has been cleared</li> <li>1: Data transfer between the device and an external device has been completed. <i>Note: While the SPIF bit is set, all writes to the SPIDR register are inhibited until the SPICSR register is read.</i></li> </ul> |

| 6     | WCOL | <ul> <li>Write Collision status</li> <li>This bit is set by hardware when a write to the SPIDR register is done during a transmit sequence. It is cleared by a software sequence (see <i>Figure 53</i>).</li> <li>0: No write collision occurred</li> <li>1: A write collision has been detected.</li> </ul>                                                                                                                                                                                                                                                                                                        |

| 5     | OVR  | <ul> <li>SPI Overrun error</li> <li>This bit is set by hardware when the byte currently being received in the shift register is ready to be transferred into the SPIDR register while SPIF = 1 (see Overrun condition (OVR) on page 103). An interrupt is generated if SPIE = 1 in SPICR register. The OVR bit is cleared by software reading the SPICSR register.</li> <li>0: No overrun error</li> <li>1: Overrun error detected</li> </ul>                                                                                                                                                                       |

| 4     | MODF | <ul> <li>Mode Fault flag</li> <li>This bit is set by hardware when the SS pin is pulled low in master mode (see <i>Master mode fault (MODF) on page 103</i>). An SPI interrupt can be generated if SPIE = 1 in the SPICSR register. This bit is cleared by a software sequence (An access to the SPICR register while MODF = 1 followed by a write to the SPICR register).</li> <li>0: No master mode fault detected</li> <li>1: A fault in master mode has been detected.</li> </ul>                                                                                                                               |

| 3     | -    | Reserved, must be kept cleared.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2     | SOD  | <ul> <li>SPI Output Disable</li> <li>This bit is set and cleared by software. When set, it disables the alternate function of the SPI output (MOSI in master mode / MISO in slave mode).</li> <li>0: SPI output enabled (if SPE = 1).</li> <li>1: SPI output disabled.</li> </ul>                                                                                                                                                                                                                                                                                                                                   |

| 1     | SSM  | <ul> <li>SS Management</li> <li>This bit is set and cleared by software. When set, it disables the alternate function of the SPI SS pin and uses the SSI bit value instead. See <i>Slave Select management on page 99</i>.</li> <li>0: Hardware management (SS managed by external pin).</li> <li>1: Software management (internal SS signal controlled by SSI bit. External SS pin free for general-purpose I/O).</li> </ul>                                                                                                                                                                                       |

| 0     | SSI  | <ul> <li>SS Internal mode</li> <li>This bit is set and cleared by software. It acts as a 'chip select' by controlling the level of the SS slave select signal when the SSM bit is set.</li> <li>0: Slave selected.</li> <li>1: Slave deselected.</li> </ul>                                                                                                                                                                                                                                                                                                                                                         |

Table 57. SPICSR register description

## ADC Data Register Low (ADCDRL)

| ADCDRL |   |      |       |   | Rese | t value: 0000   | 0000 (00h) |

|--------|---|------|-------|---|------|-----------------|------------|

| 7      | 6 | 5    | 4     | 3 | 2    | 1               | 0          |

|        |   | Rese | erved |   |      | D[ <sup>-</sup> | 1:0]       |

|        |   |      | -     |   |      | B               | 0          |

## Table 73. ADCDRL register description

| Bit | Name   | Function                           |

|-----|--------|------------------------------------|

| 7:2 | -      | Reserved. Forced by hardware to 0. |

| 1:0 | D[1:0] | LSB of Converted Analog Value      |

### Table 74. ADC register map and reset values

| Address (Hex.) | Register label        | 7        | 6          | 5         | 4       | 3        | 2        | 1        | 0        |

|----------------|-----------------------|----------|------------|-----------|---------|----------|----------|----------|----------|

| 0070h          | ADCCSR<br>Reset value | EOC<br>0 | SPEED<br>0 | ADON<br>0 | 0       | CH3<br>0 | CH2<br>0 | CH1<br>0 | CH0<br>0 |

| 0071h          | ADCDRH<br>Reset value | D9<br>0  | D8<br>0    | D7<br>0   | D6<br>0 | D5<br>0  | D4<br>0  | D3<br>0  | D2<br>0  |

| 0072h          | ADCDRL<br>Reset value | 0        | 0          | 0         | 0       | 0        | 0        | D1<br>0  | D0<br>0  |

#### Supply current characteristics 12.5

The following current consumption specified for the ST7 functional operating modes over temperature range does not take into account the clock source current consumption. To obtain the total device consumption, the two current values must be added (except for Halt mode for which the clock is stopped).

#### 12.5.1 **ROM current consumption**

| Table 89. | ROM | current | consumption |

|-----------|-----|---------|-------------|

|           |     | ounone  | oonoumption |

| Symbol          | Parameter                                          | Conditions                                                                                                                                                                                                                                              | -                            | ROM<br>vices                |                              | K ROM                       | Unit |

|-----------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-----------------------------|------------------------------|-----------------------------|------|

|                 |                                                    |                                                                                                                                                                                                                                                         | Тур                          | Max <sup>(1)</sup>          | Тур                          | Max <sup>(1)</sup>          |      |

|                 | Supply current in Run mode <sup>(2)</sup>          |                                                                                                                                                                                                                                                         | 0.55<br>1.10<br>2.20<br>4.38 | 0.87<br>1.75<br>3.5<br>7.0  | 0.46<br>0.93<br>1.9<br>3.7   | 0.69<br>1.4<br>2.7<br>5.5   | mA   |

|                 | Supply current in Slow mode <sup>(2)</sup>         |                                                                                                                                                                                                                                                         | 53<br>100<br>194<br>380      | 87<br>175<br>350<br>700     | 30<br>70<br>150<br>310       | 60<br>120<br>250<br>500     | μA   |

| I <sub>DD</sub> | Supply current in Wait mode <sup>(2)</sup>         |                                                                                                                                                                                                                                                         | 0.31<br>0.61<br>1.22<br>2.44 | 0.5<br>1.0<br>2.0<br>4.0    | 0.22<br>0.45<br>0.91<br>1.82 | 0.37<br>0.75<br>1.5<br>3    | mA   |

|                 | Supply current in Slow Wait<br>mode <sup>(2)</sup> | $      f_{OSC} = 2 \text{ MHz}, \      f_{CPU} = 62.5 \text{ kHz} $                                                                                                                                                                                     | 36<br>69<br>133<br>260       | 63<br>125<br>250<br>500     | 20<br>40<br>90<br>190        | 40<br>90<br>180<br>350      |      |

|                 | Supply current in Halt mode <sup>(3)</sup>         | $-40^{\circ}C \le T_{A} \le +85^{\circ}C$                                                                                                                                                                                                               | <1                           | 10                          | <1                           | 10                          | μA   |

|                 | Supply current in Active Halt mode <sup>(4)</sup>  | $\begin{array}{l} -40^{\circ}\text{C} \leq \text{T}_{\text{A}} \leq +125^{\circ}\text{C} \\ \\ f_{\text{OSC}} = 2 \text{ MHz} \\ f_{\text{OSC}} = 4 \text{ MHz} \\ \\ f_{\text{OSC}} = 8 \text{ MHz} \\ \\ f_{\text{OSC}} = 16 \text{ MHz} \end{array}$ | <1<br>15<br>28<br>55<br>107  | 50<br>20<br>38<br>75<br>200 | <1<br>11<br>22<br>43<br>85   | 50<br>15<br>30<br>60<br>150 |      |

1. Data based on characterization results, tested in production at V<sub>DD</sub> max. and f<sub>CPU</sub> max.

2.

Measurements are done in the following conditions: - Program executed from RAM, CPU running with RAM access. The increase in consumption when executing from Flash is 50%

- All I/O pins in input mode with a static value at V<sub>DD</sub> or V<sub>SS</sub> (no load)

- All peripherals in reset state

LVD disabled.

- Clock input (OSC1) driven by external square wave

- In Slow and Slow Wait modes, f<sub>CPU</sub> is based on f<sub>OSC</sub> divided by 32

To obtain the total current consumption of the device, add the clock source (*Section 12.6.3*) and the peripheral power

consumption (Section 12.5.4).

- All I/O pins in push-pull 0 mode (when applicable) with a static value at V<sub>DD</sub> or V<sub>SS</sub> (no load), LVD disabled. Data based on characterization results, tested in production at V<sub>DD</sub> max. and f<sub>CPU</sub> max.

- Data based on characterization results, not tested in production. All I/O pins in push-pull 0 mode (when applicable) with a static value at  $V_{DD}$  or  $V_{SS}$  (no load); clock input (OSC1) driven by external square wave, LVD disabled. To obtain the total current consumption of the device, add the clock source consumption (*Section 12.6.3*). 4.

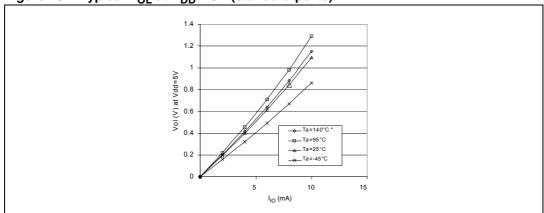

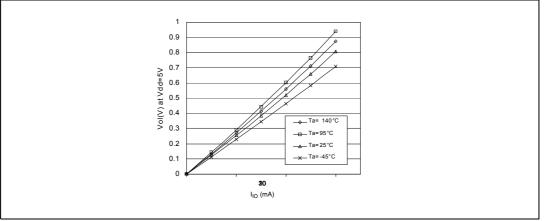

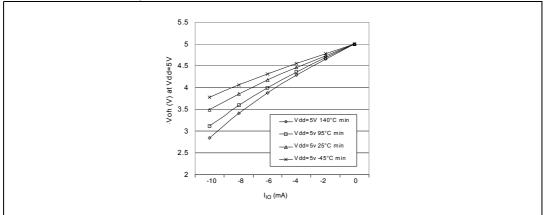

Figure 72. Typical  $V_{OH}$  at  $V_{DD} = 5V$

# **12.12** Communication interface characteristics

## 12.12.1 Serial peripheral interface (SPI)

The following characteristics are ubject to general operating conditions for  $V_{DD}$ ,  $f_{CPU}$ , and  $T_A$  unless otherwise specified. The data is based on design simulation and/or characterization results, not tested in production.

When no communication is on-going the data output line of the SPI (MOSI in master mode, MISO in slave mode) has its alternate function capability released. In this case, the pin status depends on the I/O port configuration. Refer to the I/O port characteristics for more details on the input/output alternate function characteristics (SS, SCK, MOSI, MISO).

| Symbol                                                        | Parameter                    | Conditions                      | Min                            | Мах                 | Unit |

|---------------------------------------------------------------|------------------------------|---------------------------------|--------------------------------|---------------------|------|

| f <sub>SCK</sub>                                              | SPI clock froguency          | Master f <sub>CPU</sub> = 8 MHz | f <sub>CPU</sub> /128 = 0.0625 | $f_{CPU}/4 = 2$     | MHz  |

| 1/t <sub>c(SCK)</sub>                                         | SPI clock frequency          | Slave f <sub>CPU</sub> = 8 MHz  | 0                              | $f_{CPU}/2 = 4$     |      |

| t <sub>r(SCK)</sub><br>t <sub>f(SCK)</sub>                    | SPI clock rise and fall time |                                 | see I/O po                     | ort pin description |      |

| $t_{su(\overline{SS})}^{(1)}$                                 | SS setup time <sup>(2)</sup> | Slave                           | t <sub>CPU</sub> + 50          |                     |      |

| $t_{h(\overline{SS})}^{(1)}$                                  | SS hold time                 | Slave                           | 120                            |                     |      |

| t <sub>w(SCKH)</sub> (1)<br>t <sub>w(SCKL)</sub> (1)          | SCK high and low time        | Master<br>Slave                 | 100<br>90                      |                     |      |

| t <sub>su(MI)</sub> (1)<br>t <sub>su(SI)</sub> (1)            | Data input setup time        | Master<br>Slave                 | 100<br>100                     |                     |      |

| $\begin{array}{c}t_{h(MI)}^{(1)}\\t_{h(SI)}^{(1)}\end{array}$ | Data input hold time         | Master<br>Slave                 | 100<br>100                     |                     | ns   |

| t <sub>a(SO)</sub> <sup>(1)</sup>                             | Data output access time      | Slave                           | 0                              | 120                 |      |

| t <sub>dis(SO)</sub> <sup>(1)</sup>                           | Data output disable time     | Slave                           |                                | 240                 |      |

| t <sub>v(SO)</sub> <sup>(1)</sup>                             | Data output valid time       | Slove (after enable edge)       |                                | 120                 |      |

| t <sub>h(SO)</sub> <sup>(1)</sup>                             | Data output hold time        | Slave (after enable edge)       | 0                              |                     |      |

| t <sub>v(MO)</sub> <sup>(1)</sup>                             | Data output valid time       | Master (after anable adae)      |                                | 120                 |      |

| t <sub>h(MO)</sub> <sup>(1)</sup>                             | Data output hold time        | Master (after enable edge)      | 0                              |                     |      |

Table 110.

SPI characteristics

1. Data based on design simulation and/or characterization results, not tested in production.

2. Depends on  $f_{CPU}$ . For example, if  $f_{CPU}$  = 8 MHz, then  $t_{CPU}$  = 1 /  $f_{CPU}$  = 125ns and  $t_{su(SS)}$  = 175ns.

## 14.1.2 Flash ordering information

| Figure 90. | ST72F324Bxx-Auto Flash | commercial product structure |

|------------|------------------------|------------------------------|

|------------|------------------------|------------------------------|

| <b>Product class</b><br>ST72 microcontroller<br><b>Family type</b><br>F = Flash            |      |   |        |      |      |  |

|--------------------------------------------------------------------------------------------|------|---|--------|------|------|--|

|                                                                                            |      |   |        |      |      |  |

|                                                                                            |      |   |        |      |      |  |

| <b>Sub-family type</b><br>324B = 324B sub-family                                           | <br> |   |        |      |      |  |

| <b>Pin count</b><br>K = 32 pins<br>J = 44 pins                                             | <br> |   |        |      |      |  |

| Program memory size<br>2 = 8 Kbytes                                                        |      |   |        |      |      |  |

| 2 = 8 Kbytes<br>4 = 16 Kbytes                                                              |      |   |        |      |      |  |

| 6 = 32 Kbytes                                                                              |      |   |        |      |      |  |

| Package type                                                                               |      |   |        |      |      |  |

| T = LQFP                                                                                   |      |   |        |      |      |  |

| Temperature range                                                                          |      |   |        |      |      |  |

| $A = -40 \ ^{\circ}C \ to \ 85 \ ^{\circ}C$                                                |      |   |        |      |      |  |

| C = -40 °C to 125 °C                                                                       |      |   |        |      |      |  |

| Tape and Reel conditioning oTR or R = Pin 1 left-orientedTX or X = Pin 1 right-oriented (I |      |   | ray) — |      |      |  |

| ECOPACK/Fab code<br>Blank or E = Lead-free ECOPA<br>S = Lead-free ECOPACK <sup>®</sup> Cat |      | b |        | <br> | <br> |  |

For a list of available options (e.g. memory size, package) and orderable part numbers or for further information on any aspect of this device, please go to www.st.com or contact the ST Sales Office nearest to you.

| Example:                                                            | ST72               | 324B       | т      | А           | /xxx  | Х | S |

|---------------------------------------------------------------------|--------------------|------------|--------|-------------|-------|---|---|

| Product class                                                       |                    |            |        |             |       |   |   |

| ST72 microcontroller                                                |                    |            |        |             |       |   |   |

|                                                                     |                    |            |        |             |       |   |   |

| 324B = 324B sub-family                                              |                    |            |        |             |       |   |   |

|                                                                     |                    |            |        |             |       |   |   |

| Package type                                                        |                    |            |        |             |       |   |   |

| T = LQFP                                                            |                    |            |        |             |       |   |   |

| Temperature range                                                   |                    |            |        |             |       |   |   |

| A = -40 °C to 85 °C                                                 |                    |            |        |             |       |   |   |

| B = -40 °C to 105 °C                                                |                    |            |        |             |       |   |   |

| C = -40 °C to 125 °C                                                |                    |            |        |             |       |   |   |

| D = -40 °C to 115 °C                                                |                    |            |        |             |       |   |   |

| Code name                                                           |                    |            |        |             |       |   |   |

| Defined by                                                          |                    |            |        |             |       |   |   |

| STMicroelectronics.<br>Denotes ROM code, pinout                     |                    |            |        |             |       |   |   |

| and program memory size.                                            |                    |            |        |             |       |   |   |

|                                                                     |                    |            |        |             |       |   |   |

| Tape and Reel conditioning                                          | options            | s (left bl | ank    | if Tra      | ay) — |   |   |

| TR or $R = Pin 1$ left-oriented<br>TX or $X = Pin 1$ right-oriented |                    | 1 C        | anlia  | <b>~</b> +\ |       |   |   |

|                                                                     | (EIA 40            |            | ipilai | 11)         |       |   |   |

| ECOPACK/Fab code                                                    |                    |            |        |             |       |   |   |

| Blank or E = Lead-free ECOP.                                        | ACK <sup>®</sup> F | hoenix     | Fab    |             |       |   |   |

| S = Lead-free ECOPACK <sup>®</sup> Ca                               | tania F            | ah         |        |             |       |   |   |

Figure 92. ST72324Bxx-Auto ROM commercial product structure

## Nested interrupt context

The symptom does not occur when the interrupts are handled normally, that is, when:

- The interrupt flag is cleared within its own interrupt routine

- The interrupt flag is cleared within any interrupt routine with higher or identical priority level

- The interrupt flag is cleared in any part of the code while this interrupt is disabled

If these conditions are not met, the symptom can be avoided by implementing the following sequence:

- PUSH CC

- SIM

- Reset interrupt flag

- POP CC

## 15.1.5 16-bit timer PWM mode

In PWM mode, the first PWM pulse is missed after writing the value FFFCh in the OC1R register (OC1HR, OC1LR). It leads to either full or no PWM during a period, depending on the OLVL1 and OLVL2 settings.

## 15.1.6 TIMD set simultaneously with OC interrupt

If the 16-bit timer is disabled at the same time the output compare event occurs then output compare flag gets locked and cannot be cleared before the timer is enabled again.

## Impact on the application

If output compare interrupt is enabled, then the output compare flag cannot be cleared in the timer interrupt routine. Consequently the interrupt service routine is called repeatedly.

## Workaround

Disable the timer interrupt before disabling the timer. Again while enabling, first enable the timer then the timer interrupts.

- Perform the following to disable the timer:

- TACR1 or TBCR1 = 0x00h; // Disable the compare interrupt

- TACSR I or TBCSR I = 0x40; // Disable the timer

- Perform the following to enable the timer again:

- TACSR & or TBCSR & = ~0x40; // Enable the timer

- TACR1 or TBCR1 = 0x40; // Enable the compare interrupt

## 15.1.7 SCI wrong break duration

### Description

A single break character is sent by setting and resetting the SBK bit in the SCICR2 register. In some cases, the break character may have a longer duration than expected:

- 20 bits instead of 10 bits if M = 0

- 22 bits instead of 11 bits if M = 1

In the same way, as long as the SBK bit is set, break characters are sent to the TDO pin. This may lead to generate one break more than expected.

#### Occurrence

The occurrence of the problem is random and proportional to the baud rate. With a transmit frequency of 19200 baud ( $f_{CPU} = 8MHz$  and SCIBRR = 0xC9), the wrong break duration occurrence is around 1%.

#### Workaround

If this wrong duration is not compliant with the communication protocol in the application, software can request that an Idle line be generated before the break character. In this case, the break duration is always correct assuming the application is not doing anything between the idle and the break. This can be ensured by temporarily disabling interrupts.

The exact sequence is:

- 1. Disable interrupts

- 2. Reset and set TE (IDLE request)

- 3. Set and reset SBK (break request)

- 4. Re-enable interrupts

## 15.2 8/16 Kbyte Flash devices only

## 15.2.1 39-pulse ICC entry mode

ICC mode entry using ST7 application clock (39 pulses) is not supported. External clock mode must be used (36 pulses). Refer to the *ST7 Flash Programming Reference Manual*.

## 15.2.2 Negative current injection on pin PB0

Negative current injection on pin PB0 degrades the performance of the device and is not allowed on this pin.

## 15.3 8/16 Kbyte ROM devices only

## 15.3.1 Readout protection with LVD

Readout protection is not supported if the LVD is enabled.

## 15.3.2 I/O Port A and F configuration

When using an external quartz crystal or ceramic resonator, a few  $f_{OSC2}$  clock periods may be lost when the signal pattern in *Table 122* occurs. This is because this pattern causes the device to enter test mode and return to user mode after a few clock periods. User program execution and I/O status are not changed, only a few clock cycles are lost.

This happens with either one of the following configurations

- PA3 = 0, PF4 = 1, PF1 = 0 while PLL option is disabled and PF0 is toggling

- PA3 = 0, PF4 = 1, PF1 = 0, PF0 = 1 while PLL option is enabled

This is detailed in *Table 122*