Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                              |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ST7                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               | SCI, SPI                                                              |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 24                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 1K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                           |

| Data Converters            | A/D 12x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 32-LQFP                                                               |

| Supplier Device Package    |                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f324bk6t6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

57

|    | 12.10               | Control                                                                                            | pin characteristics 166                                                                                                                                                                                                                                                                                                                                 | 6                                         |

|----|---------------------|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

|    |                     | 12.10.1                                                                                            | Asynchronous RESET pin166                                                                                                                                                                                                                                                                                                                               | 6                                         |

|    |                     | 12.10.2                                                                                            | ICCSEL/VPP pin                                                                                                                                                                                                                                                                                                                                          | 8                                         |

|    | 12.11               | Timer p                                                                                            | eripheral characteristics 168                                                                                                                                                                                                                                                                                                                           | 8                                         |

|    |                     | 12.11.1                                                                                            | 16-bit timer                                                                                                                                                                                                                                                                                                                                            | 8                                         |

|    | 12.12               | Commu                                                                                              | inication interface characteristics 169                                                                                                                                                                                                                                                                                                                 | 9                                         |

|    |                     | 12.12.1                                                                                            | Serial peripheral interface (SPI) 169                                                                                                                                                                                                                                                                                                                   | 9                                         |

|    | 12.13               | 10-bit A                                                                                           | DC characteristics 17 <sup>-</sup>                                                                                                                                                                                                                                                                                                                      | 1                                         |

|    |                     | 12.13.1                                                                                            | Analog power supply and reference pins                                                                                                                                                                                                                                                                                                                  | 3                                         |

|    |                     | 12.13.2                                                                                            | General PCB design guidelines 173                                                                                                                                                                                                                                                                                                                       | 3                                         |

|    |                     | 12.13.3                                                                                            | ADC accuracy                                                                                                                                                                                                                                                                                                                                            | 4                                         |

| 13 | Packa               | age cha                                                                                            | racteristics                                                                                                                                                                                                                                                                                                                                            | 5                                         |

|    | 13.1                | LQFP4                                                                                              | 4 package characteristics 175                                                                                                                                                                                                                                                                                                                           | 5                                         |

|    | 13.2                | LQFP3                                                                                              | 2 package characteristics 176                                                                                                                                                                                                                                                                                                                           | 6                                         |

|    | 13.3                | Therma                                                                                             | Il characteristics                                                                                                                                                                                                                                                                                                                                      | 8                                         |

|    | 13.4                | Ecopac                                                                                             | k information                                                                                                                                                                                                                                                                                                                                           | 8                                         |

|    | 13.5                | Packag                                                                                             | ing for automatic handling 178                                                                                                                                                                                                                                                                                                                          | 8                                         |

| 14 | Devic               | e confi                                                                                            | guration and ordering information                                                                                                                                                                                                                                                                                                                       | 9                                         |

|    | 14.1                | Flash d                                                                                            | evices                                                                                                                                                                                                                                                                                                                                                  | 9                                         |

|    |                     | 14.1.1                                                                                             | Flash configuration                                                                                                                                                                                                                                                                                                                                     | 9                                         |

|    |                     | 14.1.2                                                                                             | Flash ordering information                                                                                                                                                                                                                                                                                                                              | 2                                         |

|    | 14.2                | _                                                                                                  |                                                                                                                                                                                                                                                                                                                                                         |                                           |

|    |                     | ROM de                                                                                             | evice ordering information and transfer of customer code 183                                                                                                                                                                                                                                                                                            | 3                                         |

|    | 14.3                |                                                                                                    | evice ordering information and transfer of customer code 183                                                                                                                                                                                                                                                                                            |                                           |

|    | 14.3                |                                                                                                    |                                                                                                                                                                                                                                                                                                                                                         | 7                                         |

|    | 14.3                | Develop                                                                                            | oment tools                                                                                                                                                                                                                                                                                                                                             | 7<br>7                                    |

|    | 14.3                | Develop<br>14.3.1                                                                                  | oment tools                                                                                                                                                                                                                                                                                                                                             | 7<br>7<br>7                               |

|    | 14.3                | Develop<br>14.3.1<br>14.3.2                                                                        | oment tools       187         Introduction       187         Evaluation tools and starter kits       187                                                                                                                                                                                                                                                | 7<br>7<br>7<br>7                          |

|    | 14.3                | Develop<br>14.3.1<br>14.3.2<br>14.3.3                                                              | oment tools       187         Introduction       187         Evaluation tools and starter kits       187         Development and debugging tools       187                                                                                                                                                                                              | 7<br>7<br>7<br>7                          |

|    | 14.3                | Develop<br>14.3.1<br>14.3.2<br>14.3.3<br>14.3.4<br>14.3.5                                          | Dement tools       187         Introduction       187         Evaluation tools and starter kits       187         Development and debugging tools       187         Programming tools       187                                                                                                                                                         | 7<br>7<br>7<br>7<br>8                     |

| 15 | 14.4                | Develop<br>14.3.1<br>14.3.2<br>14.3.3<br>14.3.4<br>14.3.5<br>ST7 Ap                                | oment tools       187         Introduction       187         Evaluation tools and starter kits       187         Development and debugging tools       187         Programming tools       187         Socket and emulator adapter information       187                                                                                                | 7<br>7<br>7<br>7<br>8                     |

| 15 | 14.4                | Develop<br>14.3.1<br>14.3.2<br>14.3.3<br>14.3.4<br>14.3.5<br>ST7 Ap<br>m limita                    | oment tools       187         Introduction       187         Evaluation tools and starter kits       187         Development and debugging tools       187         Programming tools       187         Socket and emulator adapter information       188         plication notes       188                                                              | 7<br>7<br>7<br>7<br>8<br>8<br><b>9</b>    |

| 15 | 14.4<br><b>Know</b> | Develop<br>14.3.1<br>14.3.2<br>14.3.3<br>14.3.4<br>14.3.5<br>ST7 Ap<br>m limita                    | oment tools       187         Introduction       187         Evaluation tools and starter kits       187         Development and debugging tools       187         Programming tools       187         Socket and emulator adapter information       188         plication notes       188         Ntions       188                                     | 7<br>7<br>7<br>7<br>8<br>8<br>9<br>9      |

| 15 | 14.4<br><b>Know</b> | Develop<br>14.3.1<br>14.3.2<br>14.3.3<br>14.3.4<br>14.3.5<br>ST7 Ap<br><b>n limita</b><br>All Flas | oment tools       187         Introduction       187         Evaluation tools and starter kits       187         Development and debugging tools       187         Programming tools       187         Socket and emulator adapter information       188         plication notes       188         Ations       188         h and ROM devices       189 | 7<br>7<br>7<br>7<br>8<br>8<br>9<br>9<br>9 |

| Doc | ID13466 | Rev | 4 |

|-----|---------|-----|---|

|-----|---------|-----|---|

1

| 6 | Revis | ion hist | ory                                                  | 195   |

|---|-------|----------|------------------------------------------------------|-------|

|   |       | 15.3.2   | I/O Port A and F configuration                       | . 193 |

|   |       | 15.3.1   | Readout protection with LVD                          | . 193 |

|   | 15.3  | 8/16 Kb  | yte ROM devices only                                 | 193   |

|   |       | 15.2.2   | Negative current injection on pin PB0                | . 193 |

|   |       | 15.2.1   | 39-pulse ICC entry mode                              | . 193 |

|   | 15.2  | 8/16 Kb  | yte Flash devices only                               | 193   |

|   |       | 15.1.7   | SCI wrong break duration                             | . 192 |

|   |       | 15.1.6   | TIMD set simultaneously with OC interrupt            | . 192 |

|   |       | 15.1.5   | 16-bit timer PWM mode                                | . 192 |

|   |       | 15.1.4   | Clearing active interrupts outside interrupt routine | . 191 |

|   |       | 15.1.3   | Unexpected reset fetch                               | . 191 |

|        |        | Pin                              |      | Le             | vel    |       |     | Рог  | rt  |     |     |                                                            |                                                                                                                                                                                                        |                        |  |

|--------|--------|----------------------------------|------|----------------|--------|-------|-----|------|-----|-----|-----|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--|

| N      | о.     |                                  | e    |                |        |       | Ir  | nput |     | Out | put | Main<br>function                                           |                                                                                                                                                                                                        |                        |  |

| LQFP44 | LQFP32 | Name                             | Type | Input          | Output | float | ndm | int  | ana | QO  | РР  | (after<br>reset)                                           | Alternate function                                                                                                                                                                                     |                        |  |

| 26     | 11     | PC3<br>(HS)/ICAP1_B              | I/O  | CT             | HS     | x     | х   |      |     | х   | х   | Port C3                                                    | Timer B inpu                                                                                                                                                                                           | it capture 1           |  |

| 27     | 12     | PC4/MISO/ICCD<br>ATA             | I/O  | CT             |        | x     | х   |      |     | x   | x   | Port C4                                                    | SPI master<br>in/slave out<br>data                                                                                                                                                                     | ICC data<br>input      |  |

| 28     | 13     | PC5/MOSI<br>/AIN14               | I/O  | CT             |        | x     | х   |      | х   | x   | x   | Port C5                                                    | SPI master<br>out/slave in<br>data                                                                                                                                                                     | ADC analog<br>input 14 |  |

| 29     | 14     | PC6/SCK<br>/ICCCLK               | I/O  | CT             |        | х     | х   |      |     | х   | х   | Port C6                                                    | SPI serial<br>clock                                                                                                                                                                                    | ICC clock<br>output    |  |

| 30     | 15     | PC7/SS/AIN15                     | I/O  | CT             |        | x     | х   |      | x   | x   | x   | Port C7                                                    | SPI slave<br>select<br>(active low)                                                                                                                                                                    | ADC analog<br>input 15 |  |

| 31     | 16     | PA3 (HS)                         | I/O  | CT             | HS     | X     |     | ei0  |     | Х   | Х   | Port A3                                                    |                                                                                                                                                                                                        |                        |  |

| 32     | -      | V <sub>DD_1</sub> <sup>(1)</sup> | S    |                |        |       |     |      |     |     |     | Digital ma                                                 | in supply volta                                                                                                                                                                                        | age                    |  |

| 33     | -      | V <sub>SS_1</sub> <sup>(1)</sup> | S    |                |        |       |     |      |     |     |     | Digital gro                                                | und voltage                                                                                                                                                                                            |                        |  |

| 34     | 17     | PA4 (HS)                         | I/O  | $C_{T}$        | HS     | Х     | Х   |      |     | Х   | х   | Port A4                                                    |                                                                                                                                                                                                        |                        |  |

| 35     | -      | PA5 (HS)                         | I/O  | $C_T$          | HS     | Х     | Х   |      |     | Х   | Х   | Port A5                                                    |                                                                                                                                                                                                        |                        |  |

| 36     | 18     | PA6 (HS)                         | I/O  | $C_T$          | HS     | Х     |     |      |     | Т   |     | Port A6 <sup>(2)</sup>                                     |                                                                                                                                                                                                        |                        |  |

| 37     | 19     | PA7 (HS)                         | I/O  | $C_{T}$        | HS     | Х     |     |      |     | Т   |     | Port A7 <sup>(2)</sup>                                     |                                                                                                                                                                                                        |                        |  |

| 38     | 20     | V <sub>PP</sub> /ICCSEL          | I    |                |        |       |     |      |     |     |     | programm<br>the progra<br>See <u>Sectio</u><br>High voltag | Must be tied low. In the Flash programming mode, this pin acts as the programming voltage input $V_{PP}$ See <i>Section 12.10.2</i> for more details. High voltage must not be applied to ROM devices. |                        |  |

| 39     | 21     | RESET                            | I/O  | CT             |        |       |     |      |     |     |     | Top priority                                               | y non-maskat                                                                                                                                                                                           | ole interrupt          |  |

| 40     | 22     | V <sub>SS_2</sub> <sup>(1)</sup> | S    |                |        |       |     |      |     |     |     | Digital gro                                                | und voltage                                                                                                                                                                                            |                        |  |

| 41     | 23     | OSC2 <sup>(3)</sup>              | 0    |                |        |       |     |      |     |     |     | Resonator                                                  | oscillator inv                                                                                                                                                                                         | erter output           |  |

| 42     | 24     | OSC1 <sup>(3)</sup>              | I    |                |        |       |     |      |     |     |     |                                                            | External clock input or resonator oscillator inverter input                                                                                                                                            |                        |  |

| 43     | 25     | V <sub>DD_2</sub> <sup>(1)</sup> | S    |                |        |       |     |      |     |     |     | Digital ma                                                 | in supply volta                                                                                                                                                                                        | age                    |  |

| 44     | 26     | PE0/TDO                          | I/O  | CT             |        | х     | Х   |      |     | Х   | Х   | Port E0                                                    | SCI transmit                                                                                                                                                                                           | data out               |  |

| 1      | 27     | PE1/RDI                          | I/O  | C <sub>T</sub> |        | X     | Х   |      |     | Х   | Х   | Port E1                                                    | SCI receive                                                                                                                                                                                            | data in                |  |

# Table 2. Device pin description (continued)

| Address                                                                                                                                      | Block                    | Register label                                                                                                                                        | Register name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Reset<br>status <sup>(1)</sup>                                                                        | Remarks <sup>(1)</sup>                                                                                                                                                         |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 0041h<br>0042h<br>0043h<br>0043h<br>0045h<br>0046h<br>0047h<br>0048h<br>0049h<br>004Ah<br>004Bh<br>004Ch<br>004Ch<br>004Ch<br>004Eh<br>004Fh | Timer B                  | TBCR2<br>TBCR1<br>TBCSR<br>TBIC1HR<br>TBIC1LR<br>TBOC1HR<br>TBOC1LR<br>TBCHR<br>TBCLR<br>TBACHR<br>TBACLR<br>TBIC2HR<br>TBIC2LR<br>TBOC2HR<br>TBOC2LR | Timer B control register 2<br>Timer B control register 1<br>Timer B control/status register<br>Timer B input capture 1 high register<br>Timer B output compare 1 high register<br>Timer B output compare 1 low register<br>Timer B counter high register<br>Timer B counter low register<br>Timer B alternate counter high register<br>Timer B alternate counter low register<br>Timer B alternate counter low register<br>Timer B input capture 2 high register<br>Timer B output compare 2 low register<br>Timer B output compare 2 low register | 00h<br>00h<br>xxxx x0xxb<br>xxh<br>80h<br>00h<br>FFh<br>FCh<br>FCh<br>FCh<br>xxh<br>xxh<br>80h<br>00h | R/W<br>R/W<br>Read only<br>Read only<br>R/W<br>R/W<br>Read only<br>Read only<br>Read only<br>Read only<br>Read only<br>Read only<br>Read only<br>Read only<br>Read only<br>R/W |  |  |

| 0050h<br>0051h<br>0052h<br>0053h<br>0054h<br>0055h<br>0056h<br>0057h                                                                         | SCI                      | SCISR<br>SCIDR<br>SCIBRR<br>SCICR1<br>SCICR2<br>SCIERPR<br>SCIETPR                                                                                    | SCI status register<br>SCI data register<br>SCI baud rate register<br>SCI control register 1<br>SCI control register 2<br>SCI extended receive prescaler register<br>Reserved area<br>SCI extended transmit prescaler register                                                                                                                                                                                                                                                                                                                     | C0h<br>xxh<br>00h<br>x000 0000b<br>00h<br>00h<br><br>00h                                              | Read only<br>R/W<br>R/W<br>R/W<br>R/W<br>R/W<br>R/W                                                                                                                            |  |  |

| 0058h to<br>006Fh                                                                                                                            |                          |                                                                                                                                                       | Reserved area (24 bytes)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                       |                                                                                                                                                                                |  |  |

| 0070h<br>0071h<br>0072h                                                                                                                      | ADC                      | ADCCSR<br>ADCDRH<br>ADCDRL                                                                                                                            | Control/status register<br>Data high register<br>Data low register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 00h<br>00h<br>00h                                                                                     | R/W<br>Read only<br>Read only                                                                                                                                                  |  |  |

| 0073h<br>007Fh                                                                                                                               | Reserved area (13 bytes) |                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                       |                                                                                                                                                                                |  |  |

#### Table 3. Hardware register map (continued)

1. Legend: x = undefined, R/W = read/write.

2. The bits associated with unavailable pins must always keep their reset value.

3. The contents of the I/O port DR registers are readable only in output configuration. In input configuration, the values of the I/O pins are returned instead of the DR register contents.

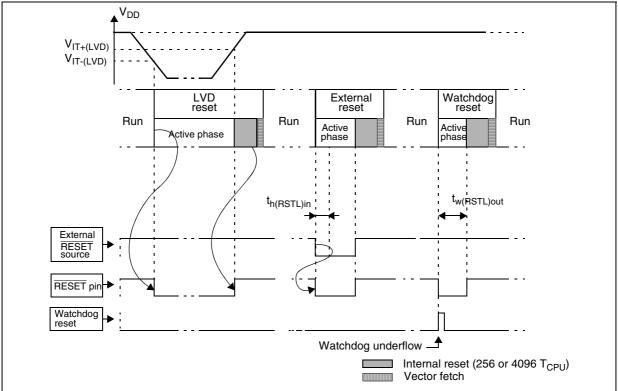

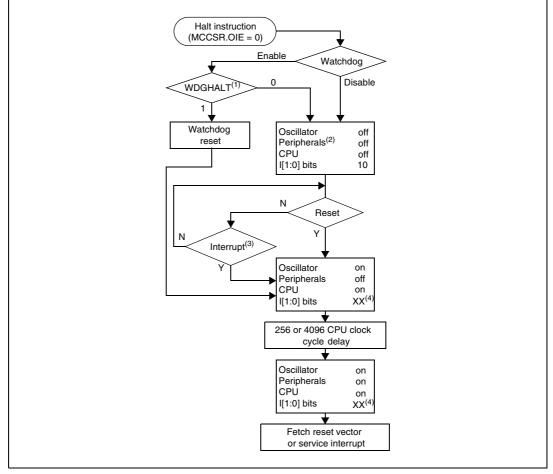

#### Figure 13. RESET sequences

# 6.5 System integrity management (SI)

The system integrity management block contains the LVD and auxiliary voltage detector (AVD) functions. It is managed by the SICSR register.

# 6.5.1 LVD (low voltage detector)

The LVD function generates a static reset when the V<sub>DD</sub> supply voltage is below a V<sub>IT</sub>-reference value. This means that it secures the power-up as well as the power-down keeping the ST7 in reset.

The V<sub>IT</sub> reference value for a voltage drop is lower than the V<sub>IT+</sub> reference value for poweron in order to avoid a parasitic reset when the MCU starts running and sinks current on the supply (hysteresis).

The LVD reset circuitry generates a reset when  $V_{DD}$  is below:

- V<sub>IT+</sub> when V<sub>DD</sub> is rising

- V<sub>IT</sub>- when V<sub>DD</sub> is falling

The LVD function is illustrated in Figure 13.

The voltage threshold can be configured by option byte to be low, medium or high.

| No. | Source<br>block | Description                                  | Register<br>label | Priority<br>order  | Exit from<br>Halt/Active Halt | Address vector |

|-----|-----------------|----------------------------------------------|-------------------|--------------------|-------------------------------|----------------|

|     | Reset           | Reset                                        | N/A               |                    | yes                           | FFFEh-FFFFh    |

|     | TRAP            | Software interrupt                           | IN/A              |                    | no                            | FFFCh-FFFDh    |

| 0   |                 | Not used                                     |                   |                    |                               | FFFAh-FFFBh    |

| 1   | MCC/RTC         | Main clock controller time base<br>interrupt | MCCSR             | Higher<br>priority | yes                           | FFF8h-FFF9h    |

| 2   | ei0             | External interrupt port A30                  |                   |                    | yes                           | FFF6h-FFF7h    |

| 3   | ei1             | External interrupt port F20                  |                   |                    | yes                           | FFF4h-FFF5h    |

| 4   | ei2             | External interrupt port B30                  | N/A               |                    | yes                           | FFF2h-FFF3h    |

| 5   | ei3             | External interrupt port B74                  |                   |                    | yes                           | FFF0h-FFF1h    |

| 6   |                 | Not used                                     |                   |                    |                               | FFEEh-FFEFh    |

| 7   | SPI             | SPI peripheral interrupts                    | SPICSR            |                    | yes                           | FFECh-FFEDh    |

| 8   | Timer A         | Timer A peripheral interrupts                | TASR              |                    | no                            | FFEAh-FFEBh    |

| 9   | Timer B         | Timer B peripheral interrupts                | TBSR              | ┥                  | no                            | FFE8h-FFE9h    |

| 10  | SCI             | SCI peripheral interrupts                    | SCISR             | Lower              | no                            | FFE6h-FFE7h    |

| 11  | AVD             | Auxiliary voltage detector interrupt         | SICSR             | priority           | no                            | FFE4h-FFE5h    |

#### Table 25. Interrupt mapping

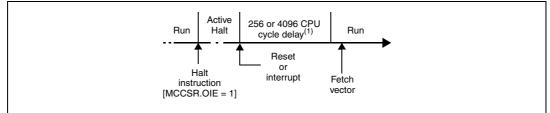

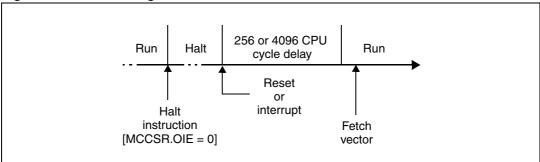

# 8.4 Active Halt and Halt modes

Active Halt and Halt modes are the two lowest power consumption modes of the MCU. They are both entered by executing the 'HALT' instruction. The decision to enter either in Active Halt or Halt mode is given by the MCC/RTC interrupt enable flag (OIE bit in the MCCSR register).

Table 26. MCC/RTC low power mode selection

| MCCSR OIE bit | Power saving mode entered when HALT instruction is executed |

|---------------|-------------------------------------------------------------|

| 0             | Halt mode                                                   |

| 1             | Active Halt mode                                            |

## 8.4.1 Active Halt mode

Active Halt mode is the lowest power consumption mode of the MCU with a real-time clock available. It is entered by executing the 'HALT' instruction when the OIE bit of the Main Clock Controller Status register (MCCSR) is set (see *Section 10.2: Main clock controller with real-time clock and beeper (MCC/RTC) on page 69* for more details on the MCCSR register).

The MCU can exit Active Halt mode on reception of either an MCC/RTC interrupt, a specific interrupt (see *Table 25: Interrupt mapping*) or a reset. When exiting Active Halt mode by means of an interrupt, no 256 or 4096 CPU cycle delay occurs. The CPU resumes operation by servicing the interrupt or by fetching the reset vector which woke it up (see *Figure 25*).

When entering Active Halt mode, the I[1:0] bits in the CC register are forced to '10b' to enable interrupts. Therefore, if an interrupt is pending, the MCU wakes up immediately.

In Active Halt mode, only the main oscillator and its associated counter (MCC/RTC) are running to keep a wake-up time base. All other peripherals are not clocked except those which get their clock supply from another clock generator (such as external or auxiliary oscillator).

The safeguard against staying locked in Active Halt mode is provided by the oscillator interrupt.

- Note: As soon as the interrupt capability of one of the oscillators is selected (MCCSR.OIE bit set), entering Active Halt mode while the Watchdog is active does not generate a reset. This means that the device cannot spend more than a defined delay in this power saving mode.

- **Caution:** When exiting Active Halt mode following an interrupt, OIE bit of MCCSR register must not be cleared before  $t_{DELAY}$  after the interrupt occurs ( $t_{DELAY} = 256$  or 4096  $t_{CPU}$  delay depending on option byte). Otherwise, the ST7 enters Halt mode for the remaining  $t_{DELAY}$  period.

#### Figure 24. Active Halt timing overview

1. This delay occurs only if the MCU exits Active Halt mode by means of a reset.

Doc ID13466 Rev 4

- 1. WDGHALT is an option bit. See *Section 14.1 on page 179* for more details.

- 2. Peripheral clocked with an external clock source can still be active.

- 3. Only some specific interrupts can exit the MCU from Halt mode (such as external interrupt). Refer to *Table 25: Interrupt mapping* for more details.

- Before servicing an interrupt, the CC register is pushed on the stack. The I[1:0] bits of the CC register are set to the current software priority level of the interrupt routine and recovered when the CC register is popped.

| Table 31. | I/O port interrupt co | ontrol/wake-up capability |

|-----------|-----------------------|---------------------------|

|-----------|-----------------------|---------------------------|

| Interrupt event                               | Event flag | Enable Control bit | Exit from WAIT | Exit from HALT |

|-----------------------------------------------|------------|--------------------|----------------|----------------|

| External interrupt on selected external event | -          | DDRx, ORx          | Yes            | Yes            |

# 9.5.1 I/O port implementation

The I/O port register configurations are summarized Table 32.

Table 32.Port configuration

| Port   | Pin name     | Input (D | )DR = 0)           | Output (DDR = 1) |                 |  |  |

|--------|--------------|----------|--------------------|------------------|-----------------|--|--|

| FOIL   | Fininanie    | OR = 0   | OR = 1             | OR = 0           | OR = 1          |  |  |

|        | PA7:6        | Floa     | ating              | True open-dra    | ain (high sink) |  |  |

| Port A | PA5:4        | Floating | Pull-up            | Open drain       | Push-pull       |  |  |

|        | PA3 Floating |          | Floating interrupt | Open drain       | Push-pull       |  |  |

| Port B | PB3 Floating |          | Floating interrupt | Open drain       | Push-pull       |  |  |

| FULD   | PB4, PB2:0   | Floating | Pull-up            | Open drain       | Push-pull       |  |  |

| Port C | PC7:0        | Floating | Pull-up            | Open drain       | Push-pull       |  |  |

| Port D | PD5:0        | Floating | Pull-up            | Open drain       | Push-pull       |  |  |

| Port E | PE1:0        | Floating | Pull-up            | Open drain       | Push-pull       |  |  |

| Port F | PF7:6, 4     | Floating | Pull-up            | Open drain       | Push-pull       |  |  |

| FUILE  | PF2:0        | Floating | Pull-up            | Open drain       | Push-pull       |  |  |

### Table 33. I/O port register map and reset values

| Address (Hex.)     | Register label     | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

|--------------------|--------------------|-----|---|---|---|---|---|---|-----|

| Reset value of all | I/O port registers | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0   |

| 0000h              | PADR               |     |   |   |   |   |   |   |     |

| 0001h              | PADDR              | MSB |   |   |   |   |   |   | LSB |

| 0002h              | PAOR               |     |   |   |   |   |   |   |     |

| 0003h              | PBDR               |     |   |   |   |   |   |   |     |

| 0004h              | PBDDR              | MSB |   |   |   |   |   |   | LSB |

| 0005h              | PBOR               |     |   |   |   |   |   |   |     |

| 0006h              | PCDR               |     |   |   |   |   |   |   |     |

| 0007h              | PCDDR              | MSB |   |   |   |   |   |   | LSB |

| 0008h              | PCOR               |     |   |   |   |   |   |   |     |

| 0009h              | PDDR               |     |   |   |   |   |   |   |     |

| 000Ah              | PDDDR              | MSB |   |   |   |   |   |   | LSB |

| 000Bh              | PDOR               |     |   |   |   |   |   |   |     |

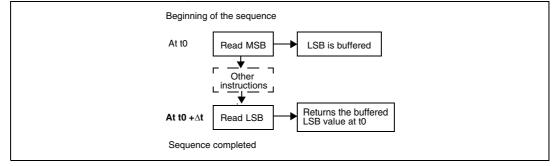

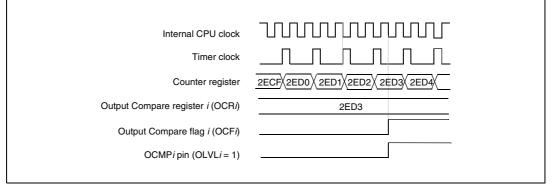

#### 16-bit read sequence

The 16-bit read sequence (from either the Counter register or the Alternate Counter register) is illustrated in the following *Figure 35*.

Figure 35. 16-bit read sequence

The user must first read the MSB, afterwhich the LSB value is automatically buffered.

This buffered value remains unchanged until the 16-bit read sequence is completed, even if the user reads the MSB several times.

After a complete reading sequence, if only the CLR register or ACLR register are read, they return the LSB of the count value at the time of the read.

Whatever the timer mode used (input capture, output compare, one pulse mode or PWM mode) an overflow occurs when the counter rolls over from FFFFh to 0000h then:

- The TOF bit of the SR register is set.

- A timer interrupt is generated if:

- TOIE bit of the CR1 register is set and

- I bit of the CC register is cleared.

If one of these conditions is false, the interrupt remains pending to be issued as soon as they are both true.

Clearing the overflow interrupt request is done in two steps:

- 1. Reading the SR register while the TOF bit is set.

- 2. An access (read or write) to the CLR register.

Note: The TOF bit is not cleared by access to the ACLR register. The advantage of accessing the ACLR register rather than the CLR register is that it allows simultaneous use of the overflow function and reading the free running counter at random times (for example, to measure elapsed time) without the risk of clearing the TOF bit erroneously.

The timer is not affected by Wait mode.

In Halt mode, the counter stops counting until the mode is exited. Counting then resumes from the previous count (MCU awakened by an interrupt) or from the reset count (MCU awakened by a reset).

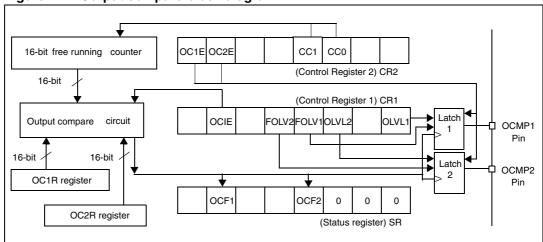

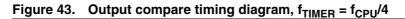

Figure 41. Output compare block diagram

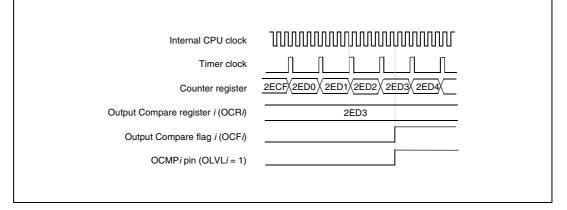

# Output Compare 2 Low Register (OC2LR)

This is an 8-bit register that contains the low part of the value to be compared to the CLR register.

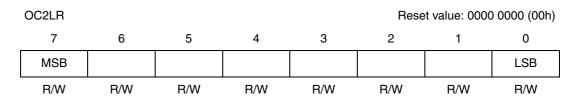

### **Counter High Register (CHR)**

This is an 8-bit register that contains the high part of the counter value.

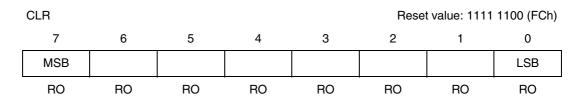

## **Counter Low Register (CLR)**

This is an 8-bit register that contains the low part of the counter value. A write to this register resets the counter. An access to this register after accessing the CSR register clears the TOF bit.

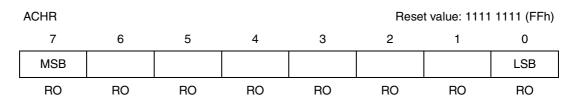

### Alternate Counter High Register (ACHR)

This is an 8-bit register that contains the high part of the counter value.

| Table 57.         SPICSR register description |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|-----------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Bit                                           | Name | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 7                                             | SPIF | <ul> <li>Serial Peripheral data transfer flag</li> <li>This bit is set by hardware when a transfer has been completed. An interrupt is generated if SPIE = 1 in the SPICR register. It is cleared by a software sequence (an access to the SPICSR register followed by a write or a read to the SPIDR register).</li> <li>0: Data transfer is in progress or the flag has been cleared</li> <li>1: Data transfer between the device and an external device has been completed. <i>Note: While the SPIF bit is set, all writes to the SPIDR register are inhibited until the SPICSR register is read.</i></li> </ul> |  |  |

| 6                                             | WCOL | <ul> <li>Write Collision status</li> <li>This bit is set by hardware when a write to the SPIDR register is done during a transmit sequence. It is cleared by a software sequence (see <i>Figure 53</i>).</li> <li>0: No write collision occurred</li> <li>1: A write collision has been detected.</li> </ul>                                                                                                                                                                                                                                                                                                        |  |  |

| 5                                             | OVR  | <ul> <li>SPI Overrun error</li> <li>This bit is set by hardware when the byte currently being received in the shift register is ready to be transferred into the SPIDR register while SPIF = 1 (see Overrun condition (OVR) on page 103). An interrupt is generated if SPIE = 1 in SPICR register. The OVR bit is cleared by software reading the SPICSR register.</li> <li>0: No overrun error</li> <li>1: Overrun error detected</li> </ul>                                                                                                                                                                       |  |  |

| 4                                             | MODF | <ul> <li>Mode Fault flag</li> <li>This bit is set by hardware when the SS pin is pulled low in master mode (see <i>Master mode fault (MODF) on page 103</i>). An SPI interrupt can be generated if SPIE = 1 in the SPICSR register. This bit is cleared by a software sequence (An access to the SPICR register while MODF = 1 followed by a write to the SPICR register).</li> <li>0: No master mode fault detected</li> <li>1: A fault in master mode has been detected.</li> </ul>                                                                                                                               |  |  |

| 3                                             | -    | Reserved, must be kept cleared.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| 2                                             | SOD  | <ul> <li>SPI Output Disable</li> <li>This bit is set and cleared by software. When set, it disables the alternate function of the SPI output (MOSI in master mode / MISO in slave mode).</li> <li>0: SPI output enabled (if SPE = 1).</li> <li>1: SPI output disabled.</li> </ul>                                                                                                                                                                                                                                                                                                                                   |  |  |

| 1                                             | SSM  | <ul> <li>SS Management</li> <li>This bit is set and cleared by software. When set, it disables the alternate function of the SPI SS pin and uses the SSI bit value instead. See <i>Slave Select management on page 99</i>.</li> <li>0: Hardware management (SS managed by external pin).</li> <li>1: Software management (internal SS signal controlled by SSI bit. External SS pin free for general-purpose I/O).</li> </ul>                                                                                                                                                                                       |  |  |

| 0                                             | SSI  | <ul> <li>SS Internal mode</li> <li>This bit is set and cleared by software. It acts as a 'chip select' by controlling the level of the SS slave select signal when the SSM bit is set.</li> <li>0: Slave selected.</li> <li>1: Slave deselected.</li> </ul>                                                                                                                                                                                                                                                                                                                                                         |  |  |

Table 57. SPICSR register description

#### Changing the conversion channel

The application can change channels during conversion. When software modifies the CH[3:0] bits in the ADCCSR register, the current conversion is stopped, the EOC bit is cleared, and the A/D converter starts converting the newly selected channel.

## 10.6.4 Low power modes

*Note:* The A/D converter may be disabled by resetting the ADON bit. This feature allows reduced power consumption when no conversion is needed.

Table 70. Effect of low power modes on ADC

| Mode | Description                                                                                                                                                                                                                         |  |  |  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Wait | No effect on A/D converter                                                                                                                                                                                                          |  |  |  |

| Halt | A/D converter disabled.<br>After wake-up from Halt mode, the A/D converter requires a stabilization time t <sub>STAB</sub><br>(see <i>Section 12: Electrical characteristics</i> ) before accurate conversions can be<br>performed. |  |  |  |

#### 10.6.5 Interrupts

None.

## 10.6.6 ADC registers

#### ADC Control/Status Register (ADCCSR)

|   | ADCCSR |       |      |          |   | Rese | t value: 0000 | 0000 (00h) |

|---|--------|-------|------|----------|---|------|---------------|------------|

|   | 7      | 6     | 5    | 4        | 3 | 2    | 1             | 0          |

|   | EOC    | SPEED | ADON | Reserved |   | CH   | [3:0]         |            |

| - | RO     | R/W   | RW   | -        |   | R    | W             |            |

#### Table 71. ADCCSR register description

| Bit | Name  | Function                                                                                                                                                                                                                       |

|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | EOC   | End of Conversion<br>This bit is set by hardware. It is cleared by hardware when software reads the<br>ADCDRH register or writes to any bit of the ADCCSR register.<br>0: Conversion is not complete<br>1: Conversion complete |

| 6   | SPEED | ADC clock selection<br>This bit is set and cleared by software.<br>0: $f_{ADC} = f_{CPU}/4$<br>1: $f_{ADC} = f_{CPU}/2$                                                                                                        |

| Table 71. ADCUSR register description |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|---------------------------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Bit                                   | Name    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| 5                                     | ADON    | <ul><li>A/D Converter on</li><li>This bit is set and cleared by software.</li><li>0: Disable ADC and stop conversion</li><li>1: Enable ADC and start conversion</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 4                                     | -       | Reserved, must be kept cleared.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 3:0                                   | CH[3:0] | Channel selection<br>These bits are set and cleared by software. They select the analog input to convert.<br>0000: Channel pin = AIN0<br>0001: Channel pin = AIN1<br>0010: Channel pin = AIN2<br>0011: Channel pin = AIN3<br>0100: Channel pin = AIN4<br>0101: Channel pin = AIN5<br>0110: Channel pin = AIN6<br>0111: Channel pin = AIN7<br>1000: Channel pin = AIN7<br>1000: Channel pin = AIN8<br>1001: Channel pin = AIN9<br>1010: Channel pin = AIN10<br>1011: Channel pin = AIN12<br>1101: Channel pin = AIN12<br>1101: Channel pin = AIN13<br>1110: Channel pin = AIN15<br>Note: The number of channels is device dependent. Refer to Section 2: Pin<br>description. |  |  |

Table 71. ADCCSR register description

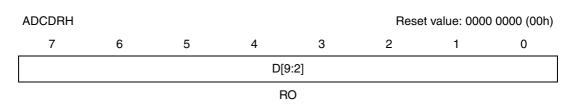

# ADC Data Register High (ADCDRH)

### Table 72. ADCDRH register description

| Bit | Name   | Function                      |  |

|-----|--------|-------------------------------|--|

| 7:0 | D[9:2] | MSB of Converted Analog Value |  |

| able 82. Instruction set overview (continued) |                        |                                 |         |         |   |   |    |   |   |   |

|-----------------------------------------------|------------------------|---------------------------------|---------|---------|---|---|----|---|---|---|

| Mnemo                                         | Description            | Function/example                | Dst     | Src     | ľ | н | 10 | Ν | z | C |

| JRUGT                                         | Jump if $(C + Z = 0)$  | Unsigned >                      |         |         |   |   |    |   |   |   |

| JRULE                                         | Jump if $(C + Z = 1)$  | Unsigned <=                     |         |         |   |   |    |   |   |   |

| LD                                            | Load                   | dst <= src                      | reg, M  | M, reg  |   |   |    | Ν | Ζ |   |

| MUL                                           | Multiply               | X,A = X * A                     | A, X, Y | X, Y, A |   | 0 |    |   |   | 0 |

| NEG                                           | Negate (2's compl)     | neg \$10                        | reg, M  |         |   |   |    | Ν | Z | С |

| NOP                                           | No Operation           |                                 |         |         |   |   |    |   |   |   |

| OR                                            | OR operation           | A = A + M                       | А       | М       |   |   |    | Ν | Z |   |

| DOD                                           | Dan from the Otack     | pop reg                         | reg     | М       |   |   |    |   |   |   |

| POP                                           | Pop from the Stack     | pop CC                          | СС      | М       | Ŀ | Н | 10 | Ν | Z | С |

| PUSH                                          | Push onto the Stack    | push Y                          | М       | reg, CC |   |   |    |   |   |   |

| RCF                                           | Reset carry flag       | C = 0                           |         |         |   |   |    |   |   | 0 |

| RIM                                           | Enable Interrupts      | 11:0 = 10 (level 0)             |         |         | 1 |   | 0  |   |   |   |

| RLC                                           | Rotate Left true C     | C <= A <= C                     | reg, M  |         |   |   |    | Ν | Ζ | С |

| RRC                                           | Rotate Right true C    | $C \Rightarrow A \Rightarrow C$ | reg, M  |         |   |   |    | Ν | Z | С |

| RSP                                           | Reset Stack Pointer    | S = Max allowed                 |         |         |   |   |    |   |   |   |

| SBC                                           | Subtract with Carry    | A = A - M - C                   | А       | М       |   |   |    | Ν | Z | С |

| SCF                                           | Set CARRY FLAG         | C = 1                           |         |         |   |   |    |   |   | 1 |

| SIM                                           | Disable Interrupts     | 11:0 = 11 (level 3)             |         |         | 1 |   | 1  |   |   |   |

| SLA                                           | Shift Left Arithmetic  | C <= A <= 0                     | reg, M  |         |   |   |    | Ν | Z | С |

| SLL                                           | Shift Left Logic       | C <= A <= 0                     | reg, M  |         |   |   |    | Ν | Z | С |

| SRL                                           | Shift Right Logic      | 0 => A => C                     | reg, M  |         |   |   |    | 0 | Z | С |

| SRA                                           | Shift Right Arithmetic | A7 => A => C                    | reg, M  |         |   |   |    | Ν | Z | С |

| SUB                                           | Subtraction            | A = A - M                       | А       | М       |   |   |    | Ν | Z | С |

| SWAP                                          | SWAP nibbles           | A7-A4 <=> A3-A0                 | reg, M  |         |   |   | 1  | Ν | Z | 1 |

| TNZ                                           | Test for Neg and Zero  | tnz lbl1                        |         |         |   |   |    | Ν | Z |   |

| TRAP                                          | S/W TRAP               | S/W interrupt                   |         |         | 1 |   | 1  |   |   |   |

| WFI                                           | WAIT for Interrupt     |                                 |         |         | 1 |   | 0  |   |   |   |

| XOR                                           | Exclusive OR           | A = A XOR M                     | A       | М       |   |   | 1  | Ν | Z |   |

| Table 82. Instruction set overview (continued) | Table 82. | Instruction set overview (continued) |

|------------------------------------------------|-----------|--------------------------------------|

|------------------------------------------------|-----------|--------------------------------------|

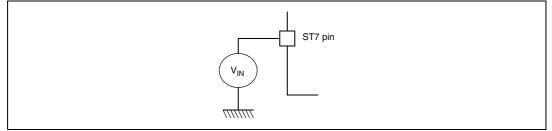

# 12.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 61*.

#### Figure 61. Pin input voltage

# 12.2 Absolute maximum ratings

Stresses above those listed as "absolute maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device under these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

# 12.2.1 Voltage characteristics

#### Table 83.Voltage characteristics

| Symbol                                    | Ratings                                                        | Maximum value                                     | Unit |

|-------------------------------------------|----------------------------------------------------------------|---------------------------------------------------|------|

| V <sub>DD</sub> - V <sub>SS</sub>         | Supply voltage                                                 | 6.5                                               |      |

| V <sub>PP</sub> - V <sub>SS</sub>         | Programming voltage                                            | 13                                                |      |

|                                           | Input voltage on true open drain pin                           | V <sub>SS</sub> - 0.3 to 6.5                      | V    |

| V <sub>IN</sub> <sup>(1)(2)</sup>         | Input voltage on any other pin                                 | V <sub>SS</sub> - 0.3 to<br>V <sub>DD</sub> + 0.3 |      |

| $ \Delta V_{DDx} $ and $ \Delta V_{SSx} $ | Variations between different digital power pins                | 50                                                | mV   |

| IV <sub>SSA</sub> - V <sub>SSx</sub> I    | Variations between digital and analog ground pins              | 50                                                | IIIV |

| V <sub>ESD(HBM)</sub>                     | Electrostatic discharge voltage (human body model) see Section |                                                   | 3 on |

| V <sub>ESD(MM)</sub>                      | Electrostatic discharge voltage (machine model)                | page 160                                          |      |

Directly connecting the RESET and I/O pins to V<sub>DD</sub> or V<sub>SS</sub> could damage the device if an unintentional internal reset is generated or an unexpected change of the I/O configuration occurs (for example, due to a corrupted program counter). To guarantee safe operation, this connection has to be done through a pull-up or pull-down resistor (typical: 4.7kΩ for RESET, 10kΩ for I/Os). For the same reason, unused I/O pins must not be directly tied to V<sub>DD</sub> or V<sub>SS</sub>.

2.  $I_{INJ(PIN)}$  must never be exceeded. This is implicitly ensured if  $V_{IN}$  maximum is respected. If  $V_{IN}$  maximum cannot be respected, the injection current must be limited externally to the  $I_{INJ(PIN)}$  value. A positive injection is induced by  $V_{IN} > V_{DD}$  while a negative injection is induced by  $V_{IN} < V_{SS}$ . For true open-drain pads, there is no positive injection current, and the corresponding  $V_{IN}$  maximum must always be respected.

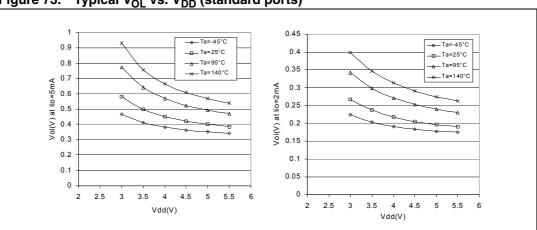

Figure 73. Typical V<sub>OL</sub> vs. V<sub>DD</sub> (standard ports)

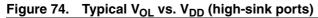

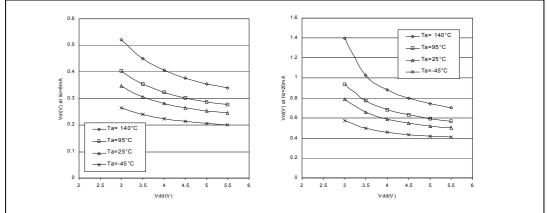

Figure 75. Typical V<sub>OH</sub> vs. V<sub>DD</sub>

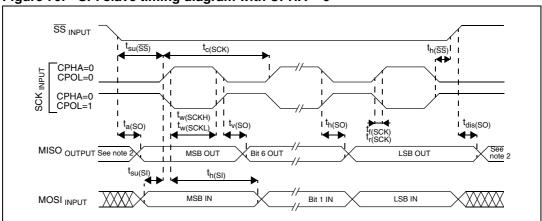

Figure 79. SPI slave timing diagram with CPHA =  $0^{(1)}$

- 1. Measurement points are done at CMOS levels: 0.3xV<sub>DD</sub> and 0.7xV<sub>DD</sub>.

- When no communication is on-going the data output line of the SPI (MOSI in master mode, MISO in slave mode) has its alternate function capability released. In this case, the pin status depends on the I/O port configuration.

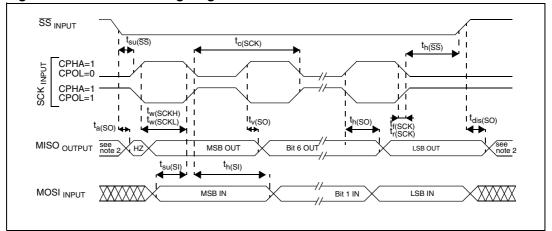

Figure 80. SPI slave timing diagram with CPHA =  $1^{(1)}$

- 1. Measurement points are done at CMOS levels:  $0.3xV_{DD}$  and  $0.7xV_{DD}$ .

- When no communication is on-going the data output line of the SPI (MOSI in master mode, MISO in slave mode) has its alternate function capability released. In this case, the pin status depends on the I/O port configuration.