Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betans                     |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | -                                                                               |

| Core Size                  | · ·                                                                             |

| Speed                      | -                                                                               |

| Connectivity               | · ·                                                                             |

| Peripherals                | -                                                                               |

| Number of I/O              | -                                                                               |

| Program Memory Size        | · ·                                                                             |

| Program Memory Type        | -                                                                               |

| EEPROM Size                | -                                                                               |

| RAM Size                   | · ·                                                                             |

| Voltage - Supply (Vcc/Vdd) | -                                                                               |

| Data Converters            | · ·                                                                             |

| Oscillator Type            | -                                                                               |

| Operating Temperature      | -                                                                               |

| Mounting Type              |                                                                                 |

| Package / Case             | · · · · · · · · · · · · · · · · · · ·                                           |

| Supplier Device Package    | · · · · · · · · · · · · · · · · · · ·                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f3640mdfb-uz |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 18.2    | Cor   | nversion Rate                                                       |     |

|---------|-------|---------------------------------------------------------------------|-----|

| 18.3    | Ext   | ended Analog Input Pins                                             |     |

| 18.4    | Cur   | rrent Consumption Reducing Function                                 |     |

| 18.5    | Ext   | ernal Sensor                                                        |     |

| 19. D/A |       | nverter                                                             |     |

| 19.1    | Sur   | nmary                                                               |     |

| 20. CR  | CO    | peration                                                            | 251 |

| 21. Pro | ograr | mmable I/O Ports                                                    | 253 |

| 21.1    | Por   | t Pi Direction Register (PDi Register, i = 0 to 10)                 |     |

| 21.2    | Por   | t Pi Register (Pi Register, i = 0 to 10)                            |     |

| 21.3    |       | I-up Control Register 0 to Pull-up Control Register 2 (Registers PL |     |

| 21.4    |       | t Control Register (PCR Register)                                   |     |

| 22. Fla | sh M  | 1emory Version                                                      |     |

| 22.1    |       | mory Map                                                            |     |

| 22.     |       | Boot Mode                                                           |     |

|         | 1.2   | User Boot Function                                                  |     |

| 22.2    |       | nctions to Prevent Flash Memory from Rewriting                      |     |

| 22.     |       | ROM Code Protect Function                                           |     |

|         | 2.2   | ID Code Check Function                                              |     |

|         |       | Forced Frase Function                                               |     |

| 22.     | 2.4   | Standard Serial I/O Mode Disable Function                           |     |

| 22.3    |       | U Rewrite Mode                                                      |     |

| 22.     | 3.1   | EW0 Mode                                                            |     |

| 22.     | 3.2   | EW1 Mode                                                            |     |

| 22.     | 3.3   | Flash Memory Control Register (Registers FMR0, FMR1, FMR2           | ,   |

| 22.     | 3.4   | Precautions on CPU Rewrite Mode                                     |     |

| 22.     | 3.5   | Software Commands                                                   |     |

| 22.     | 3.6   | Data Protect Function                                               |     |

| 22.     | 3.7   | Status Register                                                     |     |

| 22.     | 3.8   | Full Status Check                                                   |     |

| 22.4    | Sta   | ndard Serial I/O Mode                                               |     |

Address

Symbol

After Reset

|                | - 5                                                      | - / · · |           |

|----------------|----------------------------------------------------------|---------|-----------|

| 0060h          |                                                          |         |           |

| 0061h          |                                                          |         |           |

| 0062h          |                                                          |         |           |

| 0063h          |                                                          |         |           |

| 0064h          |                                                          |         |           |

| 0065h          |                                                          |         |           |

| 0066h          |                                                          |         |           |

| 0067h          |                                                          |         |           |

| 0068h          |                                                          |         |           |

| 0069h          | DMA2 Interrupt Control Register                          | DM2IC   | XXXXX000b |

| 006Ah          | DMA3 Interrupt Control Register                          | DM3IC   | XXXXX000b |

| 006Bh          | UART5 BUS Collision Detection Interrupt Control Register | U5BCNIC | XXXXX000b |

| 006Ch          | UART5 Transmit Interrupt Control Register                | S5TIC   | XXXXX000b |

| 006Dh          | UART5 Receive Interrupt Control Register                 | S5RIC   | XXXXX000b |

| 006Eh          | UART6 BUS Collision Detection Interrupt Control Register | U6BCNIC | XXXXX000b |

| 006Fh          | UART6 Transmit Interrupt Control Register                | S6TIC   | XXXXX000b |

| 0070h          | UART6 Receive Interrupt Control Register                 | S6RIC   | XXXXX000b |

| 0071h          | UART7 BUS Collision Detection Interrupt Control Register | U7BCNIC | XXXXX000b |

| 0072h          | UART7 Transmit Interrupt Control Register                | S7TIC   | XXXXX000b |

| 0073h          | UART7 Receive Interrupt Control Register                 | S7RIC   | XXXXX000b |

| 0074h          |                                                          | 0.1.00  | 7000000   |

| 0075h          |                                                          |         |           |

| 0076h          |                                                          |         |           |

| 0077h          |                                                          |         |           |

| 0078h          |                                                          |         |           |

| 0079h          |                                                          |         | -         |

| 007Ah          |                                                          |         | -         |

| 007Bh          |                                                          |         | -         |

| 007Ch          |                                                          |         |           |

| 007Dh          |                                                          |         |           |

| 007Eh          |                                                          |         |           |

| 007Eh          |                                                          |         |           |

| 007FN<br>0080h |                                                          |         |           |

| 0080h          |                                                          |         |           |

| 0081h          |                                                          |         |           |

| 0082h          |                                                          |         |           |

| 0083h<br>0084h |                                                          |         |           |

|                |                                                          |         |           |

| 0085h          |                                                          |         |           |

| 0086h          |                                                          |         |           |

| 0087h          |                                                          |         |           |

| 0088h          |                                                          |         |           |

| 0089h          |                                                          |         |           |

| 008Ah          |                                                          |         |           |

| 008Bh          |                                                          |         |           |

| 008Ch          |                                                          |         |           |

| 008Dh          |                                                          |         |           |

| 008Eh          |                                                          |         |           |

| 008Fh          |                                                          |         |           |

| 0090h          |                                                          |         |           |

| 0091h          |                                                          |         |           |

| 0092h          |                                                          |         |           |

| 0093h          |                                                          |         |           |

| 0094h          |                                                          |         |           |

| 0095h          |                                                          |         |           |

| 0096h          |                                                          | T       | Ì         |

| 0097h          |                                                          |         | Ì         |

| 0098h          |                                                          |         |           |

| 0099h          |                                                          |         | 1         |

| 009Ah          |                                                          |         | 1         |

| 009Bh          |                                                          |         |           |

| 000Ch          |                                                          | 1       |           |

Register

# Table 4.3SFR Information (3) (1)

Note:

009Ch 009Dh 009Eh 009Fh to 015Fh

1. The blank areas are reserved and cannot be accessed by users.

X: Undefined

## 5.6 Internal Space

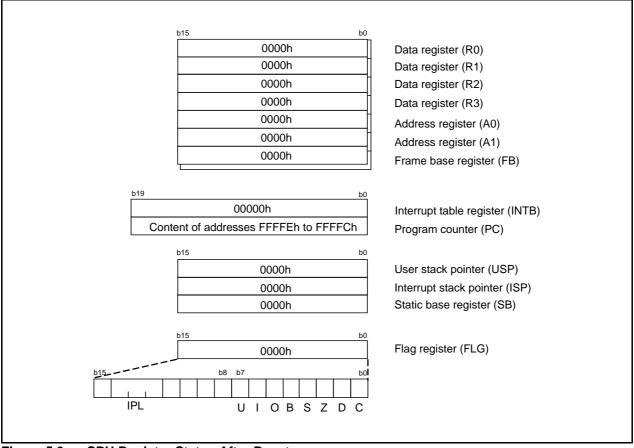

Figure 5.3 shows CPU Register Status After Reset. Refer to **4.** "**Special Function Registers (SFRs)**" for SFR states after reset.

Figure 5.3 CPU Register Status After Reset

|     | Symbol<br>DBR | Address<br>000Bh                | After Reset<br>00h                                                                                                               |    |

|-----|---------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----|

|     |               |                                 |                                                                                                                                  | _  |

|     | Bit Symbol    | Bit Name                        | Function                                                                                                                         | RW |

|     | (b1-b0)       | No register bits. If necessary, | set to 0. Read as 0                                                                                                              | _  |

|     | OFS           | Offset bit                      | 0 : Not offset<br>1 : Offset                                                                                                     | RW |

|     | BSR0          |                                 | b5 b4 b3 b5 b4 b3                                                                                                                | RW |

|     | BSR1          | Bank selection bits             | 0 0 0 : Bank 0 0 0 1 : Bank 1<br>0 1 0 : Bank 2 0 1 1 : Bank 3<br>1 0 0 : Bank 4 1 0 1 : Bank 5<br>1 1 0 : Bank 6 1 1 1 : Bank 7 | RW |

|     | BSR2          |                                 |                                                                                                                                  | RW |

| [ ] | <br>(b7-b6)   | No register bits. If necessary, | set to 0. Read as 0                                                                                                              |    |

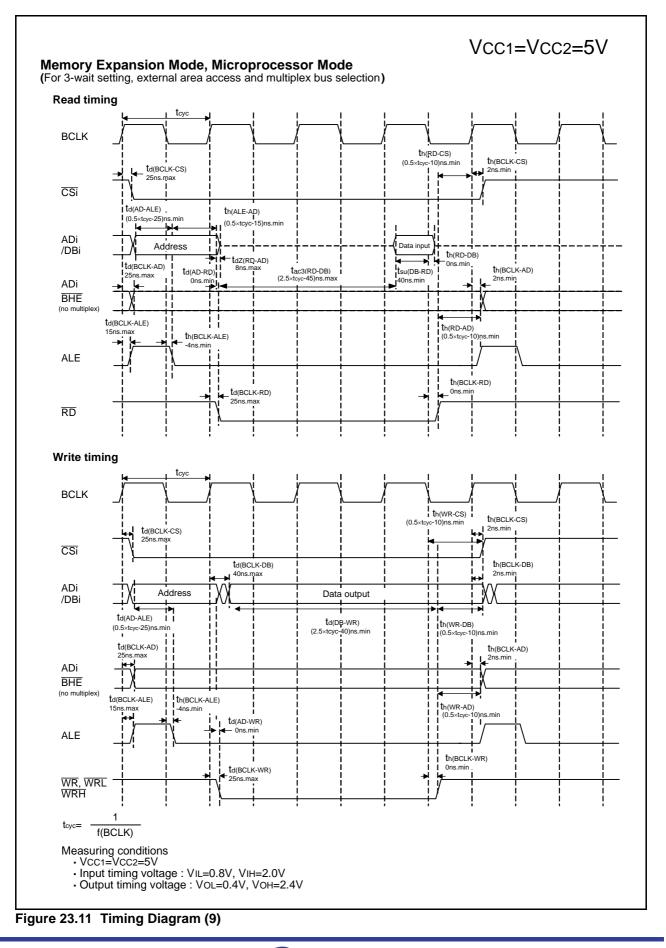

| 7 b6 b5 b4 b3 b2 b1 b0<br>0 0 0 0 0 0 0 0 0       | Symbol<br>CSPR | Address<br>037Ch                                                   |                                                                                                                                               | set <sup>(1)</sup> |

|---------------------------------------------------|----------------|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

|                                                   | Bit Symbol     | Bit Name                                                           | Function                                                                                                                                      | RW                 |

|                                                   | <br>(b6-b0)    | Reserved bits                                                      | Set to 0                                                                                                                                      | RW                 |

|                                                   | CSPRO          | Count source protection mode select bit <sup>(2)</sup>             | <ul> <li>0 : Count source protection mode<br/>disabled</li> <li>1 : Count source protection mode enab</li> </ul>                              | RW                 |

| Optional Feature           7 b6 b5 b4 b3 b2 b1 b0 | e Select       | Address <sup>(1, 5)</sup>                                          | ss Afte                                                                                                                                       | r Reset            |

|                                                   | OFS1           | FFFF                                                               | Fh F                                                                                                                                          | Fh <sup>(2)</sup>  |

|                                                   | Bit Symbol     | Bit Name                                                           | Function                                                                                                                                      | RW                 |

|                                                   | WDTON          | Watchdog timer start<br>select bit <sup>(3, 4)</sup>               | <ul> <li>0 : Watchdog timer starts automatically<br/>after reset</li> <li>1 : Watchdog timer is in a stopped state<br/>after reset</li> </ul> | RW                 |

|                                                   | <br>(b2-b1)    | Reserved bits                                                      | Set to 1                                                                                                                                      | RW                 |

|                                                   | ROMCP1         | ROM code protection bit                                            | 0 : ROM code protection enabled<br>1 : ROM code protection disabled                                                                           | RW                 |

| <u></u>                                           | <br>(b6-b4)    | Reserved bits                                                      | Set to 1                                                                                                                                      | RW                 |

|                                                   | CSPROINI       | After-reset count source protection mode select bit <sup>(3)</sup> | <ul><li>0 : Count source protection mode<br/>enabled after reset</li><li>1 : Count source protection mode<br/>disabled after reset</li></ul>  | RW                 |

|                                                   |                |                                                                    |                                                                                                                                               |                    |

4. This function is also effective in user boot mode.

5. The OFS1 address can be set in single-chip and memory expansion mode.

The OFS1 address cannot be used in micro microprocessor mode. Before using the OFS1 address, clear the internal ROM.

Notes :

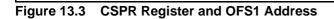

1. The DMAS bit can be set to 0 by writing a 0 in a program (This bit remains unchanged even if 1 is written). 2. Set at least either the DAD bit or DSD bit to 0 (address direction fixed).

Figure 14.3 Registers DM0CON, DM1CON, DM2CON, and DM3CON

# **16. Three-Phase Motor Control Timer Function**

Timers A1, A2, A4, and B2 can be used to output three-phase motor drive waveforms. Table 16.1 lists the Three-phase Motor Control Timer Functions Specifications. Figure 16.1 shows the Three-phase Motor Control Timer Functions Block Diagram. Also, the related registers are shown on Figures 16.2 to 16.7.

| Item                    | Specification                                                                 |  |  |

|-------------------------|-------------------------------------------------------------------------------|--|--|

| Three-Phase Waveform    | Six pins (U, $\overline{U}$ , V, $\overline{V}$ , W, $\overline{W}$ )         |  |  |

| Output Pin              |                                                                               |  |  |

| Forced Cutoff Input (1) | Input "L" to the SD pin                                                       |  |  |

| Used Timers             | Timer A4, A1, A2 (used in one-shot timer mode)                                |  |  |

|                         | Timer A4: U- and U-phase waveform control                                     |  |  |

|                         | Timer A1: V- and V-phase waveform control                                     |  |  |

|                         | Timer A2: W- and W-phase waveform control                                     |  |  |

|                         | Timer B2 (used in timer mode)                                                 |  |  |

|                         | Carrier wave cycle control                                                    |  |  |

|                         | Dead time timer (3 eight-bit timers and shared reload register)               |  |  |

|                         | Dead time control                                                             |  |  |

| Output Waveform         | Triangular wave modulation, sawtooth wave modulation                          |  |  |

|                         | <ul> <li>Enable to output "H" or "L" for one cycle</li> </ul>                 |  |  |

|                         | • Enable to set positive-phase level and negative-phase level independently   |  |  |

| Carrier Wave Cycle      | Triangular wave modulation : count source x (m + 1) x 2                       |  |  |

|                         | Sawtooth wave modulation : count source x (m + 1)                             |  |  |

|                         | m: setting value of the TB2 register, 0000h to FFFFh                          |  |  |

|                         | Count source: f1TIMAB, f2TIMAB, f8TIMAB, f32TIMAB, f64TIMAB, fOCO-S,          |  |  |

|                         | fC32                                                                          |  |  |

| Three-Phase PWM Output  | Triangular wave modulation: count source x n x 2                              |  |  |

| Width                   | Sawtooth wave modulation: count source x n                                    |  |  |

|                         | n: setting value of registers TA4, TA1, and TA2 (of registers TA4, TA41, TA1, |  |  |

|                         | TA11, TA2, and TA21 when setting the INV11 bit to 1), 0001h to FFFh           |  |  |

|                         | Count source: f1TIMAB, f2TIMAB, f8TIMAB, f32TIMAB, f64TIMAB, fOCO-S,          |  |  |

|                         | fC32                                                                          |  |  |

| Dead Time               | Count source x p, or no dead time                                             |  |  |

|                         | p: setting value of the DTT register, 01h to FFh                              |  |  |

|                         | Count source: f1TIMAB, f2TIMAB, f1TIMAB divided by 2, f2TIMAB divided by 2    |  |  |

|                         |                                                                               |  |  |

| Active Level            | Enable to select "H" or "L"                                                   |  |  |

| Positive and Negative-  | Positive-and negative-phases concurrent active disable function               |  |  |

| Phase Concurrent Active | Positive-and negative-phases concurrent active detect function                |  |  |

| Disable Function        |                                                                               |  |  |

| Interrupt Frequency     | Timer B2 interrupt is generated every q times                                 |  |  |

|                         | q: carrier wave cycle-to-cycle basis, 1 to 15                                 |  |  |

Table 16.1

Three-phase Motor Control Timer Functions Specifications

Notes:

- 1. Forced cutoff with  $\overline{SD}$  input is effective when the IVPCR1 bit in the TB2SC register is set to 1 (threephase output forcible cutoff by  $\overline{SD}$  input enabled). If an "L" signal is applied to the  $\overline{SD}$  pin when the IVPCR1 bit is 1, the related pins go to a high-impedance state regardless of which functions of those pins are being used.

- 2. Related pins: P7\_2/CLK2/TA1OUT/V, P7\_3/CTS2/RTS2/TA1IN/V, P7\_4/TA2OUT/W, P7\_5/TA2IN/W, P8\_0/TA4OUT/RXD5/SCL5/U, P8\_1/TA4IN/CTS5/RTS5/U

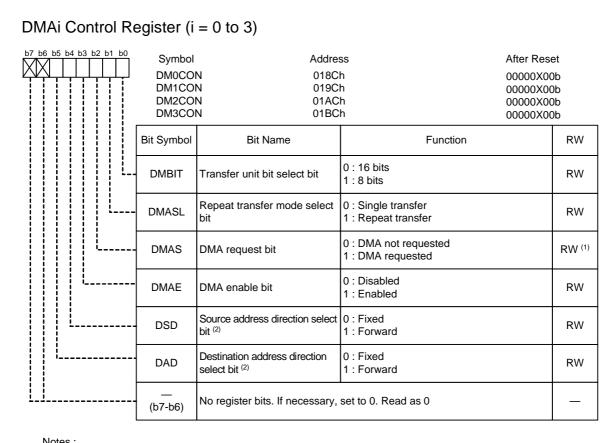

# 17.1.2.6 $\overline{\text{CTS}}$ / $\overline{\text{RTS}}$ Function

The  $\overline{\text{CTS}}$  function is used to start transmit operation when "L" is applied to the  $\overline{\text{CTSi}}$  /  $\overline{\text{RTSi}}$  (i = 0 to 2, 5 to 7) pin. Transmit operation begins when the  $\overline{\text{CTSi}}$  /  $\overline{\text{RTSi}}$  pin is held "L". If the "L" signal is switched to "H" during a transmit operation, the operation stops after the ongoing transmit / receive operation is completed.

When the RTS function is used, the CTSi / RTSi pin outputs "L" when the microcomputer is ready to receive. The output level becomes "H" when a start bit is detected.

• The CRD bit in the UiC0 register = 1 (disable  $\overline{\text{CTS}} / \overline{\text{RTS}}$  function)

CTSi / RTSi pin is programmable I/O function

- The CRD bit = 0, the CRS bit = 0 ( $\overline{\text{CTS}}$  function is selected)

- The CRD bit = 0, the CRS bit = 1 ( $\overline{\text{RTS}}$  function is selected)

# 17.1.2.7 CTS / RTS Separate Function (UART0)

This function separates  $\overline{\text{CTS0}}$  /  $\overline{\text{RTS0}}$ , outputs  $\overline{\text{RTS0}}$  from the P6\_0 pin, and inputs  $\overline{\text{CTS0}}$  from the P6\_4 pin. To use this function, set the register bits as shown below.

- The CRD bit in the U0C0 register

- The CRS bit in the U0C0 register

- The CRD bit in the U1C0 register

- = 0 (enable  $\overline{\text{CTS}}$  /  $\overline{\text{RTS}}$  of UART1)

- The CRS bit in the U1C0 register

- = 0 (input  $\overline{\text{CTS}}$  of UART1) = 1 (inputs  $\overline{\text{CTS0}}$  from the P6\_4 pin)

= 1 (output  $\overline{\text{RTS}}$  of UARTO)

= 0 (enable  $\overline{\text{CTS}} / \overline{\text{RTS}}$  of UART0)

- The RCSP bit in the UCON registerThe CLKMD1 bit in the UCON register

- = 0 (CLKS1 not used)

Note that when using the  $\overline{\text{CTS}}$  /  $\overline{\text{RTS}}$  separate function,  $\overline{\text{CTS}}$  /  $\overline{\text{RTS}}$  of UART1 function cannot be used.

Figure 17.23 CTS / RTS Separate Function

CTSi / RTSi pin is CTS function

CTSi / RTSi pin is RTS function

## 18.1.2 Repeat Mode

In repeat mode, analog voltage applied to a selected pin is repeatedly converted to a digital code. Table 18.3 shows the Repeat Mode Specifications. Figure 18.5 shows the Registers ADCON0 and ADCON1 (Repeat Mode).

| Table 10.5 Repeat Noue Specifications | Table 18.3 | <b>Repeat Mode</b> | <b>Specifications</b> |

|---------------------------------------|------------|--------------------|-----------------------|

|---------------------------------------|------------|--------------------|-----------------------|

| Item                                   | Specification                                                                                                                                                                                                                                                                                                         |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Function                               | Bits CH2 to CH0 in the ADCON0 register and bits ADGSEL1 and ADGSEL0<br>in the ADCON2 register, or bits ADEX1 and ADEX0 in the ADCON1 register<br>select a pin. Analog voltage applied to this pin is repeatedly converted to a<br>digital code.                                                                       |

| A/D Conversion Start<br>Condition      | <ul> <li>When the TRG bit in the ADCON0 register is 0 (software trigger) the ADST bit in the ADCON0 register is set to 1 (A/D conversion start)</li> <li>When the TRG bit is 1 (ADTRG trigger) input on the ADTRG pin changes state from high to low after the ADST bit is set to 1 (A/D conversion start)</li> </ul> |

| A/D Conversion Stop<br>Condition       | Set the ADST bit to 0 (A/D conversion stop)                                                                                                                                                                                                                                                                           |

| Interrupt Request<br>Generation timing | No interrupt requests generated                                                                                                                                                                                                                                                                                       |

| Analog Input Pin                       | Select one pin from AN0 to AN7, AN0_0 to AN0_7, AN2_0 to AN2_7, ANEX0, and ANEX1                                                                                                                                                                                                                                      |

| Reading of Result of A/D<br>Converter  | Read one of the registers AD0 to AD7 that corresponds to the selected pin                                                                                                                                                                                                                                             |

## 18.2 Conversion Rate

The conversion rate is defined as follows.

Start dummy time depends on which  $\phi$ AD is selected. Table 18.7 shows Start Dummy Time. When the ADST bit in the ADCON0 register is set to 1 (A/D conversion start), A/D conversion starts after start dummy time elapses. 0 (A/D conversion stop) is read if the ADST bit is read before A/D conversion starts. For multiple pins or A/D conversion repeat mode, for each pin, between-execution dummy time is inserted between A/D conversion execution time and the next A/D conversion execution time.

The ADST bit is set to 0 during the end dummy time, and the last A/D conversion result is set to the ADi register in one-shot mode and single sweep mode.

While in one-shot mode:

Start dummy time + A/D conversion execution time + end dummy time

When two pins are selected while in single sweep mode:

Start dummy time + (A/D conversion execution time + between-execution dummy time + A/D conversion execution time) + end dummy time

Start dummy time: See Table 18.7 "Start Dummy Time"

A/D conversion execution time: 40  $\phi$ AD cycles per pin Between-execution dummy time: 1  $\phi$ AD cycle End dummy time: 2 to 3 cycles of fAD

Table 18.7 Start Dummy Time

| <pre> \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$</pre> | Start Dummy Time     |

|----------------------------------------------------------------------|----------------------|

| fAD                                                                  | 1 to 2 cycles of fAD |

| fAD divided by 2                                                     | 2 to 3 cycles of fAD |

| fAD divided by 3                                                     | 3 to 4 cycles of fAD |

| fAD divided by 4                                                     | 3 to 4 cycles of fAD |

| fAD divided by 6                                                     | 4 to 5 cycles of fAD |

| fAD divided by 12                                                    | 7 to 8 cycles of fAD |

## 18.3 Extended Analog Input Pins

In one-shot and repeat modes, pins ANEX0 and ANEX1 can be used as analog input pins. Use bits ADEX1 and ADEX0 in the ADCON1 register to select whether or not to use ANEX0 and ANEX1. The A/D conversion results of ANEX0 and ANEX1 inputs are stored in registers AD0 and AD1, respectively.

# 18.4 Current Consumption Reducing Function

When not using the A/D converter, power consumption can be reduced by setting the ADSTBY bit in the ADCON1 register to 0 (A/D operation stopped: standby) to shut off any analog circuit current flow. To use the A/D converter, set the ADSTBY bit to 1 (A/D operation enabled) after operating longer than one cycle of a timer count source, and then set the ADST bit in the ADCON0 register to 1 (A/D conversion start). Do not set bits ADST and ADSTBY to 1 at the same time.

Also, do not set the ADSTBY bit to 0 (A/D operation stopped: standby) during A/D conversion.

# 22. Flash Memory Version

The flash memory can perform in three rewrite modes: CPU rewrite mode, standard serial I/O mode, and parallel I/O mode. Table 22.1 lists specifications of the flash memory version. See Tables 1.1 and 1.2 Specifications Overview for the items not listed in Table 22.1.

| Item                             |  | Specification                                            |  |

|----------------------------------|--|----------------------------------------------------------|--|

| Flash Memory Rewrite Mode        |  | 3 modes (CPU rewrite, standard serial I/O, parallel I/O) |  |

| Erase Block Program ROM 1        |  | See Figure 22.1 "Flash Memory Block Diagram"             |  |

| Program ROM 2                    |  | 1 block (16 Kbytes)                                      |  |

| Data Flash                       |  | 2 blocks (4 Kbytes each)                                 |  |

| Program Method                   |  | In units of 2 words                                      |  |

| Erase Method                     |  | Block erase                                              |  |

| Program and Erase Control Method |  | Program and erase controlled by software command         |  |

| Protect Method                   |  | The lock bit protects each block                         |  |

| Number of Commands               |  | 8 commands                                               |  |

| Program and Erase Endurance      |  | 100 times <sup>(1)</sup>                                 |  |

| Data Retention                   |  | 10 years                                                 |  |

| ROM Code Protection              |  | Parallel I/O and standard serial I/O modes are supported |  |

Table 22.1 Flash Memory Version Specifications

Note:

1. Definition of program and erase endurance

The program and erase endurance refers to the number of per-block erasures.

For example, assume a case where a 4 Kbyte block is programmed in 1,024 operations, writing two words at a time, and erased thereafter. In this case, the block is reckoned as having been programmed and erased once. If the program and erase endurance is 100 times, each block can be erased up to 100 times.

Table 22.2 Flash Memory Rewrite Modes Overview

| Flash Memory<br>Rewrite Mode    | CPU rewrite Mode <sup>(1)</sup>                                                                                                                                                                                                           | Standard Serial I/O Mode                     | Parallel I/O Mode                                                                                            |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| Function                        | Program ROM 1, program<br>ROM 2, and data flash are<br>rewritten when the CPU<br>executes software commands.<br>EW0 mode:<br>Rewritable in areas other than<br>flash memory <sup>(2)</sup><br>EW1 mode:<br>Rewritable in the flash memory | 0 1 0                                        | Program ROM 1,<br>program ROM 2 and<br>data flash are rewritten<br>using a dedicated<br>parallel programmer. |

| Areas Which Can<br>Be Rewritten | Program ROM 1, program ROM 2, and data flash                                                                                                                                                                                              | Program ROM 1, program ROM 2, and data flash | Program ROM 1, program<br>ROM 2, and data flash                                                              |

| Operating Mode                  | Single-chip mode<br>Memory expansion mode<br>(EW0 mode)                                                                                                                                                                                   | Boot mode                                    | Parallel I/O mode                                                                                            |

| ROM Programmer                  | None                                                                                                                                                                                                                                      | Serial programmer                            | Parallel programmer                                                                                          |

Notes:

- The PM13 bit remains set to 1 while the FMR01 bit in the FMR0 register = 1 (CPU rewrite mode enabled). The PM13 bit is reverted to its original value by clearing the FMR01 bit to 0 (CPU rewrite mode disabled). However, if the PM13 bit is changed during CPU rewrite mode, its changed value is not reflected until after the FMR01 bit is cleared to 0.

- 2. In CPU rewrite mode, bits PM10 and PM13 in the PM1 register are set to 1. The rewrite control program can only be executed in the internal RAM or in an external area that is enabled for use when the PM10 bit and PM13 bit are 1. When the PM13 bit = 0 and the flash memory is used in 4-Mbyte mode, the extended accessible area (40000h to BFFFFh) cannot be used.

## 22.3 CPU Rewrite Mode

In CPU rewrite mode, the flash memory can be rewritten when the CPU executes software commands. Program ROM 1, program ROM 2, and the data flash can be rewritten with the microcomputer mounted on a board without using a ROM programmer.

The program and block erase commands are executed only in each block area of program ROM 1, program ROM 2, and the data flash.

Erase-write 0 (EW0) mode and erase-write 1 (EW1) mode are provided as CPU rewrite mode. Table 22.9 lists differences between erase-write 0 (EW0) and erase-write 1 (EW1) modes.

| Item                                             | EW0 Mode                                                                                                                                                                                                       | EW1 Mode                                                                                                                                                                                 |

|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operating Mode                                   | <ul><li>Single-chip mode</li><li>Memory expansion mode</li></ul>                                                                                                                                               | Single-chip mode                                                                                                                                                                         |

| Rewrite Control<br>Program Allocatable           | Program ROM 1     Program ROM 2                                                                                                                                                                                | Program ROM 1     Program ROM 2                                                                                                                                                          |

| Area                                             | External memory area                                                                                                                                                                                           |                                                                                                                                                                                          |

| Rewrite Control<br>Program Executable<br>Area    | The rewrite control program must be transferred to any area other than the flash memory (e.g., RAM) before being executed <sup>(2)</sup>                                                                       | The rewrite control program can be executed in program ROM 1 and program ROM 2.                                                                                                          |

| Rewritable Area                                  | <ul><li>Program ROM 1</li><li>Program ROM 2</li><li>Data flash</li></ul>                                                                                                                                       | Program ROM 1, program ROM 2, and data flash, excluding blocks with the rewrite control program                                                                                          |

| Software Command<br>Restriction                  | None                                                                                                                                                                                                           | <ul> <li>Program and block erase commands<br/>cannot be executed in a block having<br/>the rewrite control program.</li> <li>Read status register command cannot<br/>be used.</li> </ul> |

| Mode after Program<br>or Erase                   | Read status register mode                                                                                                                                                                                      | Read array mode                                                                                                                                                                          |

| CPU State during<br>Auto Write and Auto<br>Erase | Operating                                                                                                                                                                                                      | Maintains hold state (I/O ports maintains<br>the state before the command execution)<br>(1)                                                                                              |

| Flash Memory Status<br>Detection                 | <ul> <li>Read bits FMR00, FMR06, and<br/>FMR07 in the FMR0 register by<br/>program</li> <li>Execute the read status register<br/>command to read bits SR7, SR5, and<br/>SR4 in the status register.</li> </ul> | Read bits FMR00, FMR06, and FMR07<br>in the FMR0 register by program                                                                                                                     |

Table 22.9 EW0 Mode and EW1 Mode

Notes:

- 1. Do not generate an interrupt (except  $\overline{\text{NMI}}$  interrupt) or start a DMA transfer.

- 2. When in CPU rewrite mode, bits PM10 and PM13 in the PM1 register are set to 1. The rewrite control program can only be executed in the internal RAM or in an external area that is enabled for use when the PM10 bit and PM13 bit are 1. When the PM13 bit = 0 and the flash memory is used in 4-Mbyte mode, the extended accessible area (40000h to BFFFFh) cannot be used.

# VCC1=VCC2=5V

#### Timing Requirements

### (VCC1 = VCC2 = 5V, VSS = 0V, at Topr = -20 to $85^{\circ}$ C/-40 to $85^{\circ}$ C unless otherwise specified)

#### Table 23.13 Timer A Input (Counter Input in Event Counter Mode)

| Symbol  | Parameter                    | Stan | Unit |       |  |

|---------|------------------------------|------|------|-------|--|

| Symbol  | i alameter                   | Min. | Max. | Offic |  |

| tc(TA)  | TAilN Input Cycle Time       | 100  |      | ns    |  |

| tw(TAH) | TAiIN Input HIGH Pulse Width | 40   |      | ns    |  |

| tw(TAL) | TAIIN Input LOW Pulse Width  | 40   |      | ns    |  |

#### Table 23.14 Timer A Input (Gating Input in Timer Mode)

| Symbol  | Parameter                    | Stan | Unit |       |  |

|---------|------------------------------|------|------|-------|--|

| Symbol  | i alameter                   | Min. | Max. | Offic |  |

| tc(TA)  | TAiIN Input Cycle Time       | 400  |      | ns    |  |

| tw(TAH) | TAiIN Input HIGH Pulse Width | 200  |      | ns    |  |

| tw(TAL) | TAIIN Input LOW Pulse Width  | 200  |      | ns    |  |

#### Table 23.15 Timer A Input (External Trigger Input in One-shot Timer Mode)

| Symbol  | Parameter                    | Stan | Unit |       |  |

|---------|------------------------------|------|------|-------|--|

| Symbol  | i arameter                   | Min. | Max. | Offic |  |

| tc(TA)  | TAIIN Input Cycle Time       | 200  |      | ns    |  |

| tw(TAH) | TAIIN Input HIGH Pulse Width | 100  |      | ns    |  |

| tw(TAL) | TAIIN Input LOW Pulse Width  | 100  |      | ns    |  |

#### Table 23.16 Timer A Input (External Trigger Input in Pulse Width Modulation Mode)

| Symbol  | Parameter                    | Stan | Unit |       |  |

|---------|------------------------------|------|------|-------|--|

| Symbol  |                              |      | Max. | Offic |  |

| tw(TAH) | TAIIN Input HIGH Pulse Width | 100  |      | ns    |  |

| tw(TAL) | TAilN Input LOW Pulse Width  | 100  |      | ns    |  |

#### Table 23.17 Timer A Input (Two-phase Pulse Input in Event Counter Mode)

| Symbol          | Parameter               | Stan | Unit |       |  |

|-----------------|-------------------------|------|------|-------|--|

| Symbol          | T arameter              | Min. | Max. | Offic |  |

| tc(TA)          | TAiIN Input Cycle Time  | 800  |      | ns    |  |

| tsu(TAIN-TAOUT) | TAiOUT Input Setup Time | 200  |      | ns    |  |

| tsu(TAOUT-TAIN) | TAilN Input Setup Time  | 200  |      | ns    |  |

# VCC1=VCC2=5V

#### Switching Characteristics

#### (VCC1 = VCC2 = 5V, VSS = 0V, at Topr = -20 to $85^{\circ}$ C/-40 to $85^{\circ}$ C unless otherwise specified)

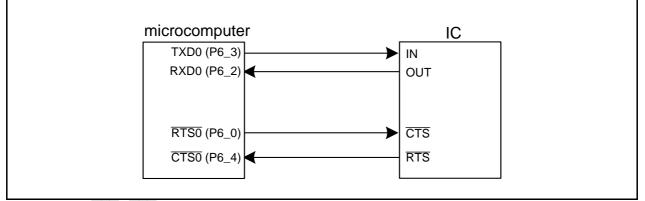

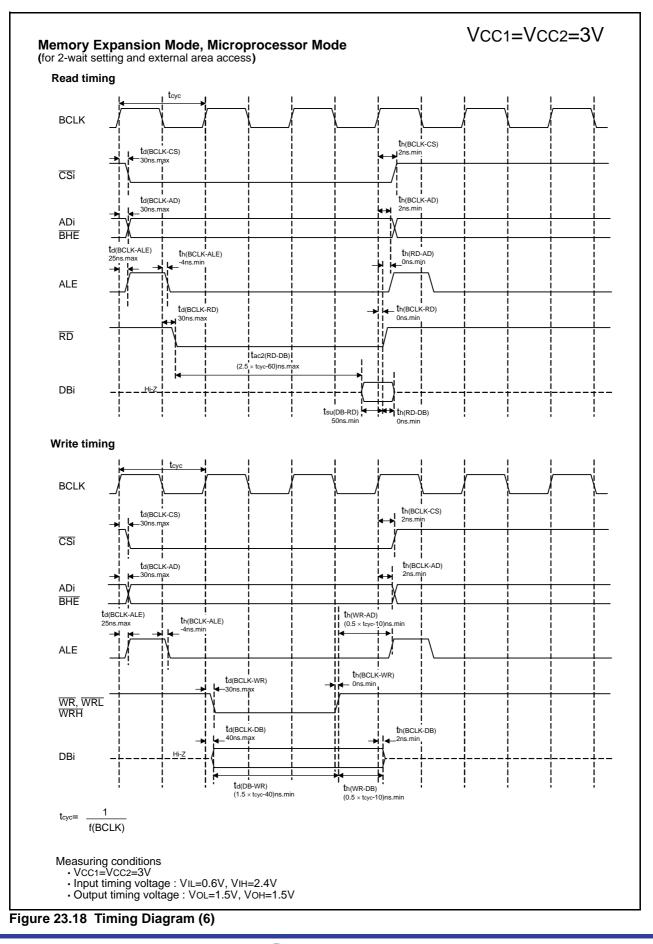

| Table 23.26 | Memory Expansion and Microprocessor Modes (for 1- to 3-wait setting, external area |

|-------------|------------------------------------------------------------------------------------|

|             | access and multiplex bus selection) <sup>(5)</sup>                                 |

| Symphol       | Parameter                                             | Measuring   | Standard |      | Unit |  |

|---------------|-------------------------------------------------------|-------------|----------|------|------|--|

| Symbol        | Parameter                                             | Condition   | Min.     | Max. |      |  |

| td(BCLK-AD)   | Address Output Delay Time                             |             |          | 25   | ns   |  |

| th(BCLK-AD)   | Address Output Hold Time (in relation to BCLK)        |             | 2        |      | ns   |  |

| th(RD-AD)     | Address Output Hold Time (in relation to RD)          |             | (NOTE 1) |      | ns   |  |

| th(WR-AD)     | Address Output Hold Time (in relation to WR)          |             | (NOTE 1) |      | ns   |  |

| td(BCLK-CS)   | Chip Select Output Delay Time                         |             |          | 25   | ns   |  |

| th(BCLK-CS)   | Chip Select Output Hold Time (in relation to BCLK)    |             | 2        |      | ns   |  |

| th(RD-CS)     | Chip Select Output Hold Time (in relation to RD)      |             | (NOTE 1) |      | ns   |  |

| th(WR-CS)     | Chip Select Output Hold Time (in relation to WR)      |             | (NOTE 1) |      | ns   |  |

| td(BCLK-RD)   | RD Signal Output Delay Time                           |             |          | 25   | ns   |  |

| th(BCLK-RD)   | RD Signal Output Hold Time                            |             | 0        |      | ns   |  |

| td(BCLK-WR)   | WR Signal Output Delay Time                           |             |          | 25   | ns   |  |

| th(BCLK-WR)   | WR Signal Output Hold Time                            | See         | 0        |      | ns   |  |

| td(BCLK-DB)   | Data Output Delay Time (in relation to BCLK)          | Figure 23.2 |          | 40   | ns   |  |

| th(BCLK-DB)   | Data Output Hold Time (in relation to BCLK)           |             | 2        |      | ns   |  |

| td(DB-WR)     | Data Output Delay Time (in relation to WR)            |             | (NOTE 2) |      | ns   |  |

| th(WR-DB)     | Data Output Hold Time (in relation to WR)             |             | (NOTE 1) |      | ns   |  |

| td(BCLK-HLDA) | HLDA Output Delay Time                                |             |          | 40   | ns   |  |

| td(BCLK-ALE)  | ALE Signal Output Delay Time (in relation to BCLK)    |             |          | 15   | ns   |  |

| th(BCLK-ALE)  | ALE Signal Output Hold Time (in relation to BCLK)     |             | -4       |      | ns   |  |

| td(AD-ALE)    | ALE Signal Output Delay Time (in relation to Address) |             | (NOTE 3) |      | ns   |  |

| th(AD-ALE)    | ALE Signal Output Hold Time (in relation to Address)  |             | (NOTE 4) |      | ns   |  |

| td(AD-RD)     | RD Signal Output Delay From the End of Address        | 1           | 0        |      | ns   |  |

| td(AD-WR)     | WR Signal Output Delay From the End of Address        |             | 0        |      | ns   |  |

| tdz(RD-AD)    | Address Output Floating Start Time                    | 1           |          | 8    | ns   |  |

Notes:

1. Calculated according to the BCLK frequency as follows:

2. Calculated according to the BCLK frequency as follows:

$\frac{(n-0.5)x10^9}{f(BCLK)} - 40[ns]$  n is "2" for 2-wait setting, "3" for 3-wait setting.

3. Calculated according to the BCLK frequency as follows:

$$\frac{0.5 \times 10^9}{f(BCLK)} - 25[ns]$$

4. Calculated according to the BCLK frequency as follows:

5. When using multiplex bus, set f(BCLK) 12.5MHz or less.

## 24.6 Protect

Set the PRC2 bit to 1 (write enabled) and then write to given SFR address, and the PRC2 bit will be cleared to 0 (write protected). Change the registers protected by the PRC2 bit in the next instruction after setting the PRC2 bit to 1. Make sure no interrupts or DMA transfers will occur between the instruction in which the PRC2 bit is set to 1 and the next instruction.

# 24.13.12 Writing

#### EW0 Mode

If the power supply voltage drops while rewriting any block in which the rewrite control program is stored, the rewrite control program may not be correctly rewritten and, consequently, the flash memory becomes unable to be rewritten thereafter. In this case, use standard serial I/O or parallel I/O mode.

## EW1 Mode

- Avoid rewriting any block in which the rewrite control program is stored.

- When a software command is executed for another block on the flash memory, the software command may not be executed as expected. This may occur when RAM is written by the rewriting program which is executed in EW1 mode.

Example Program (When the program command is executed)

| PRG_CMD: |            |   |          |   |                                                                                                                                   |

|----------|------------|---|----------|---|-----------------------------------------------------------------------------------------------------------------------------------|

| MOV.W    | PRG_ADDR   | , | A0       | ; |                                                                                                                                   |

| MOV.W    | PRG_ADDR+2 | , | A1       | ; |                                                                                                                                   |

| STE.W    | #0041h     | , | [A1A0]   | ; | Program command                                                                                                                   |

| STE.W    | WR_DATA0   | , | [A1A0]   | ; | The first word data to write                                                                                                      |

| ADD.W    | #4         | , | PRG_ADDR | ; | ←Write to RAM<br>(This is acknowledged as the second<br>data to write)                                                            |

| MOV.W    | PRG_ADDR   | , | A0       | ; |                                                                                                                                   |

| STE.W    | WR_DATA1   | , | [A1A0]   | ; | The second word data to write<br>(Depending on the value of<br>WR_DATA1, this may be<br>acknowledged as next software<br>command) |

|          | :          |   |          |   |                                                                                                                                   |

|          | :          |   |          |   |                                                                                                                                   |

|          |            |   |          |   |                                                                                                                                   |

JMP PRG\_CMD

\*PRG\_ADDR; RAM address (the executing command address to be stored.)

When rewriting flash memory, execute a rewriting program on the area other than flash memory such as RAM or external area in EW0 mode. When using EW1 mode, do not write to RAM in EW1 mode.

### 24.13.13 DMA transfer

In EW1 mode, make sure that no DMA transfers will occur while the FMR00 bit in the FMR0 register = 0 (during the auto program or auto erase period).

| Item              | M16C/62P                                                                                                                          | M16C/64                                                                                                                                                                                        |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A/D converter     | Operation frequency:<br>3.3V:f AD = 10MHz(±5LSB)                                                                                  | Operation frequency:<br>3.0V:f AD =10MHz(±3LSB)                                                                                                                                                |

|                   | 5.0V: fAD = 12MHz(±3LSB)                                                                                                          | 3.3V:f AD = 16MHz (±3LSB)                                                                                                                                                                      |

|                   | 0.01.1712 - 12.01.12(20202)                                                                                                       | 5.0V:f AD = 25MHz(±3LSB)                                                                                                                                                                       |

|                   | VREFCUT: Wait 1µs after connecting.                                                                                               | A/D Standby: Start in 1cycle after connecting.                                                                                                                                                 |

|                   | Selectable 10 bit or 8 bit conversion mode                                                                                        | Fixed 10 bit conversion mode                                                                                                                                                                   |

|                   | Selectable with/without sample and hold function                                                                                  | Fixed sample and hold function                                                                                                                                                                 |

|                   | Available external operational amplifier connection mode                                                                          | No external operational amplifier connection mode                                                                                                                                              |

|                   | Can be used when operating with 2.0V≤VREF≤VCC1                                                                                    | Be sure to use VCC1, AVCC, VREF with same power supply                                                                                                                                         |

|                   | ADST bit when using external trigger: After A/<br>D conversion, ADST bit "1" is maintained.                                       | ADST bit when using external trigger: After A/<br>D conversion, ADST bit becomes "0".                                                                                                          |

|                   | The operation after writing "1" in ADST bit:<br>ADST bit set to "1" shortly.                                                      | The operation after writing "1" in ADST bit:<br>After the passage of dummy time period,<br>ADST bit is set to "1".                                                                             |

| Timer A, B        | Operating clocks:<br>• 1, 2, 8, or 32 in f1 clock<br>• fc32                                                                       | <ul> <li>Operating clocks:</li> <li>1, 2, 8, 32, or 64 in f1 clock(one frequency circuit in timer A and B and Three-phase timer)</li> <li>fc32</li> <li>On-chip oscillator (125kHz)</li> </ul> |

|                   | Fixed PWM output level                                                                                                            | PWM output level can be inverted                                                                                                                                                               |

|                   | Select up count or down count:<br>Selectable with TAjOUT pin (j=0 to 4)                                                           | Select up count or down count:<br>Not selectable with TAjout pin (j=0 to 4)                                                                                                                    |

|                   | Timer Bi register (i=0 to 5) in pulse<br>measurement mode / pulse period<br>measurement mode: disable to set the initial<br>value | Timer Bi register (i=0 to 5) in pulse<br>measurement mode / pulse period<br>measurement mode: enable to set the initial<br>value                                                               |

|                   | Timer B over-flow flag: disable to clear the flag while not counting.                                                             | Timer B overflow flag: enable to clear the flag while not counting                                                                                                                             |

|                   | Timer A2 to A4 two-phase pulse signal<br>Processing select bit in up/down flag register<br>is write enable only.                  | Timer A2 to A4 two-phase pulse signal<br>Processing Select bit in up/down flag<br>register is read and write enable.                                                                           |

| Three-phase timer | Three-phase timer output cutoff: NMI pin\                                                                                         | Three-phase timer output cutoff: SD pin                                                                                                                                                        |

| Watchdog timer    | Common to start and refresh register                                                                                              | Reset register and Start register are divided.<br>Optional function select address (OFS1)<br>enables select and protect count source.                                                          |

| Serial interface  | UART3ch (UART 0 to 2)                                                                                                             | UART6ch (UART 0 to 2,5 to 7)                                                                                                                                                                   |

| UART              | Operating clock:<br>diveded by 1, 2, 8, or 32 in f1 clock                                                                         | Operating clock:<br>diveded by 1, 2, 8, or 32 (Each UART0 to<br>UART2, UART5 to UART7 has one divider<br>circuit)                                                                              |

| SIO               | Operating clock:<br>diveded by 1, 2, 8, or 32 in f1 clock                                                                         | Operating clock:<br>diveded by 1, 2, 8, or 32 in f1 clock<br>(one divider circuit belongs to SI/O3 and SI/<br>O4)                                                                              |

|                   | SOUT output: high impedance                                                                                                       | SOUT output: selectable "high impedance"<br>and "last bit level hold" function.                                                                                                                |

# Table Appendix 2.2 Difference Between M16C/64 and M16C/62P (2)