Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | dsPIC                                                                         |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 20 MIPS                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                         |

| Number of I/O              | 21                                                                            |

| Program Memory Size        | 6KB (2K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 256 x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                     |

| Data Converters            | A/D 6x10b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

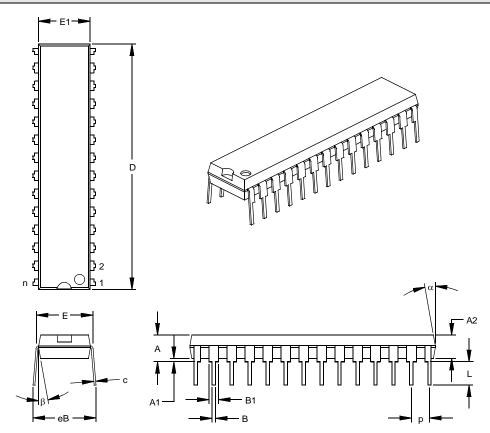

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                |

| Supplier Device Package    | 28-SOIC                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f1010-20e-so |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

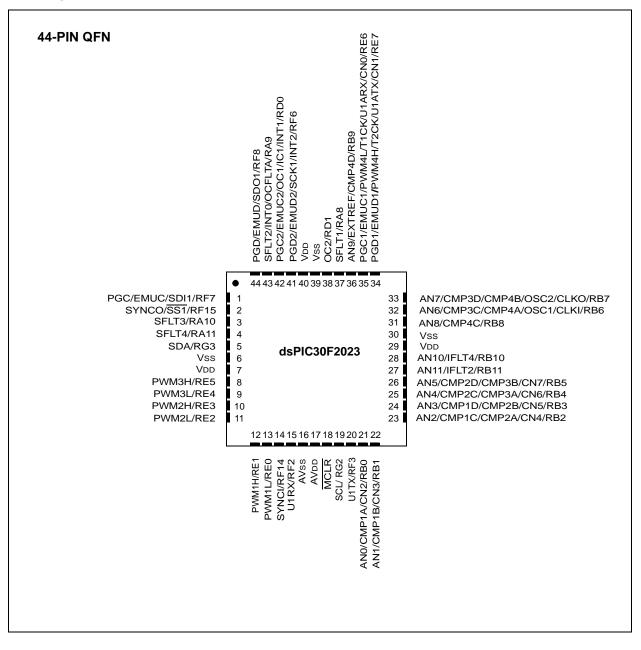

#### **Pin Diagrams**

## 1.0 DEVICE OVERVIEW

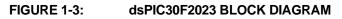

**Note:** This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "*dsPIC30F Family Reference Manual*" (DS70046). For more information on the device instruction set and programming, refer to the "*dsPIC30F/ 33F Programmer's Reference Manual*" (DS70157). This document contains device specific information for the dsPIC30F1010/202X SMPS devices. These devices contain extensive Digital Signal Processor (DSP) functionality within a high-performance 16-bit microcontroller (MCU) architecture, as reflected in the following block diagrams. Figure 1-1 and Table 1-1 describe the dsPIC30F1010 SMPS device, Figure 1-2 and Table 1-2 describe the dsPIC30F2020 device and Figure 1-3 and Table 1-3 describe the dsPIC30F2023 SMPS device.

## TABLE 1-3: PINOUT I/O DESCRIPTIONS FOR dsPIC30F2023 (CONTINUED)

| Pin Name                         | 9   | Pin<br>Type | Buffer<br>Type | Description                                                                                              |  |  |  |  |

|----------------------------------|-----|-------------|----------------|----------------------------------------------------------------------------------------------------------|--|--|--|--|

| PGD                              |     | I/O         | ST             | In-Circuit Serial Programming™ data input/output pin.                                                    |  |  |  |  |

| PGC                              |     | Ι           | ST             | In-Circuit Serial Programming clock input pin.                                                           |  |  |  |  |

| PGD1                             |     | I/O         | ST             | In-Circuit Serial Programming data input/output pin 1.                                                   |  |  |  |  |

| PGC1                             |     | I           | ST             | In-Circuit Serial Programming clock input pin 1.                                                         |  |  |  |  |

| PGD2                             |     | I/O         | ST             | In-Circuit Serial Programming data input/output pin 2.                                                   |  |  |  |  |

| PGC2                             |     | I           | ST             | In-Circuit Serial Programming clock input pin 2.                                                         |  |  |  |  |

| RA8-RA11                         |     | I/O         | ST             | PORTA is a bidirectional I/O port.                                                                       |  |  |  |  |

| RB0-RB11                         |     | I/O         | ST             | PORTB is a bidirectional I/O port.                                                                       |  |  |  |  |

| RD0,RD1                          |     | I/O         | ST             | PORTD is a bidirectional I/O port.                                                                       |  |  |  |  |

| RE0-RE7                          |     | I/O         | ST             | PORTE is a bidirectional I/O port.                                                                       |  |  |  |  |

| RF2, RF3,<br>RF6-RF8, RF<br>RF15 | 14, | I/O         | ST             | PORTF is a bidirectional I/O port.                                                                       |  |  |  |  |

| RG2, RG3                         |     | I/O         | ST             | PORTG is a bidirectional I/O port.                                                                       |  |  |  |  |

| SCK1                             |     | I/O         | ST             | Synchronous serial clock input/output for SPI #1.                                                        |  |  |  |  |

| SDI1                             |     | Ι           | ST             | SPI #1 Data In.                                                                                          |  |  |  |  |

| SDO1                             |     | 0           | —              | SPI #1 Data Out.                                                                                         |  |  |  |  |

| SS1                              |     | I           | ST             | SPI #1 Slave Synchronization.                                                                            |  |  |  |  |

| SCL                              |     | I/O         | ST             | Synchronous serial clock input/output for I <sup>2</sup> C.                                              |  |  |  |  |

| SDA                              |     | I/O         | ST             | Synchronous serial data input/output for I <sup>2</sup> C.                                               |  |  |  |  |

| T1CK<br>T2CK                     |     | 1           | ST<br>ST       | Timer1 external clock input.<br>Timer2 external clock input.                                             |  |  |  |  |

| U1RX                             |     | I           | ST             | UART1 Receive.                                                                                           |  |  |  |  |

| U1TX                             |     | ò           | _              | UART1 Transmit.                                                                                          |  |  |  |  |

| U1ARX                            |     | I           | ST             | Alternate UART1 Receive.                                                                                 |  |  |  |  |

| U1ATX                            |     | ò           | _              | Alternate UART1 Transmit                                                                                 |  |  |  |  |

| CMP1A                            |     | I           | Analog         | Comparator 1 Channel A                                                                                   |  |  |  |  |

| CMP1B                            |     | Ι           | Analog         | Comparator 1 Channel B                                                                                   |  |  |  |  |

| CMP1C                            |     | Ι           | Analog         | Comparator 1 Channel C                                                                                   |  |  |  |  |

| CMP1D                            |     | Ι           | Analog         | Comparator 1 Channel D                                                                                   |  |  |  |  |

| CMP2A                            |     | I           | Analog         | Comparator 2 Channel A                                                                                   |  |  |  |  |

| CMP2B                            |     | I           | Analog         | Comparator 2 Channel B                                                                                   |  |  |  |  |

| CMP2C                            |     | I           | Analog         | Comparator 2 Channel C                                                                                   |  |  |  |  |

| CMP2D                            |     | Ì           | Analog         | Comparator 2 Channel D                                                                                   |  |  |  |  |

| CMP3A                            |     | i           | Analog         | Comparator 3 Channel A                                                                                   |  |  |  |  |

| CMP3B                            |     |             | Analog         | Comparator 3 Channel B                                                                                   |  |  |  |  |

| CMP3C                            |     | I           | Analog         | Comparator 3 Channel C                                                                                   |  |  |  |  |

| CMP3D                            |     | I           | Analog         | Comparator 3 Channel D                                                                                   |  |  |  |  |

| CMP4A                            |     |             | Analog         | Comparator 4 Channel A                                                                                   |  |  |  |  |

| CMP4B                            |     | i           | Analog         | Comparator 4 Channel B                                                                                   |  |  |  |  |

| CMP4C                            |     | 1           | Analog         | Comparator 4 Channel C                                                                                   |  |  |  |  |

| CMP4C<br>CMP4D                   |     | I           | Analog         | Comparator 4 Channel D                                                                                   |  |  |  |  |

| CN0-CN7                          |     | I           | ST             | Input Change notification inputs<br>Can be software programmed for internal weak pull-ups on all inputs. |  |  |  |  |

| Vdd                              |     | Р           | —              | Positive supply for logic and I/O pins.                                                                  |  |  |  |  |

| Vss                              |     | Р           | _              | Ground reference for logic and I/O pins.                                                                 |  |  |  |  |

| EXTREF                           |     | I           | Analog         |                                                                                                          |  |  |  |  |

| Legend: C                        | MOS | -           | -              | atible input or output Analog = Analog input                                                             |  |  |  |  |

| S                                |     | = 5         | Schmitt Trigg  | er input with CMOS levels O = Output                                                                     |  |  |  |  |

| I                                |     | =           | nput           | P = Power                                                                                                |  |  |  |  |

NOTES:

## 3.2.2 DATA SPACES

The X data space is used by all instructions and supports all Addressing modes. There are separate read and write data buses. The X read data bus is the return data path for all instructions that view data space as combined X and Y address space. It is also the X address space data path for the dual operand read instructions (MAC class). The X write data bus is the only write path to data space for all instructions.

The X data space also supports modulo addressing for all instructions, subject to Addressing mode restrictions. Bit-Reversed Addressing is only supported for writes to X data space.

The Y data space is used in concert with the X data space by the MAC class of instructions (CLR, ED, EDAC, MAC, MOVSAC, MPY, MPY.N and MSC) to provide two concurrent data read paths. No writes occur across the Y bus. This class of instructions dedicates two W register pointers, W10 and W11, to always address Y data space, independent of X data space, whereas W8 and W9 always address X data space. Note that during accumulator write back, the data address space is considered a combination of X and Y data spaces, so the write occurs across the X bus. Consequently, the write can be to any address in the entire data space.

The Y data space can only be used for the data prefetch operation associated with the MAC class of instructions. It also supports modulo addressing for automated circular buffers. Of course, all other instructions can access the Y data address space through the X data path, as part of the composite linear space.

The boundary between the X and Y data spaces is defined as shown in Figure 3-6 and is not user programmable. Should an EA point to data outside its own assigned address space, or to a location outside physical memory, an all-zero word/byte will be returned. For example, although Y address space is visible by all non-MAC instructions using any Addressing mode, an attempt by a MAC instruction to fetch data from that space, using W8 or W9 (X space pointers), will return 0x0000.

#### TABLE 3-2: EFFECT OF INVALID MEMORY ACCESSES

| Attempted Operation                                         | Data Returned |

|-------------------------------------------------------------|---------------|

| EA = an unimplemented address                               | 0x0000        |

| W8 or W9 used to access Y data space in a MAC instruction   | 0x0000        |

| W10 or W11 used to access X data space in a MAC instruction | 0x0000        |

All effective addresses are 16 bits wide and point to bytes within the data space. Therefore, the data space address range is 64 Kbytes or 32K words.

## 3.2.3 DATA SPACE WIDTH

The core data width is 16 bits. All internal registers are organized as 16-bit wide words. Data space memory is organized in byte addressable, 16-bit wide blocks.

## 3.2.4 DATA ALIGNMENT

To help maintain backward compatibility with PIC® MCU devices and improve data space memory usage efficiency, the dsPIC30F instruction set supports both word and byte operations. Data is aligned in data memory and registers as words, but all data space EAs resolve to bytes. Data byte reads will read the complete word, which contains the byte, using the LSb of any EA to determine which byte to select. The selected byte is placed onto the LSB of the X data path (no byte accesses are possible from the Y data path as the MAC class of instruction can only fetch words). That is, data memory and registers are organized as two parallel byte-wide entities with shared (word) address decode, but separate write lines. Data byte writes only write to the corresponding side of the array or register which matches the byte address.

As a consequence of this byte accessibility, all effective address calculations (including those generated by the DSP operations, which are restricted to word sized data) are internally scaled to step through word-aligned memory. For example, the core would recognize that Post-Modified Register Indirect Addressing mode, [Ws++], will result in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. Should a misaligned read or write be attempted, an address error trap will be generated. If the error occurred on a read, the instruction underway is completed, whereas if it occurred on a write, the instruction will be executed but the write will not occur. In either case, a trap will then be executed, allowing the system and/or user to examine the machine state prior to execution of the address fault.

## FIGURE 3-8: DATA ALIGNMENT

| ,    | 15 <b>MSB</b> | 8 7 | LSB    | 0 |      |

|------|---------------|-----|--------|---|------|

| 0001 | Byte 1        |     | Byte 0 |   | 0000 |

| 0003 | Byte 3        |     | Byte 2 |   | 0002 |

| 0005 | Byte 5        |     | Byte 4 |   | 0004 |

All byte loads into any W register are loaded into the LSB. The MSB is not modified.

A Sign-Extend (SE) instruction is provided to allow users to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, users can clear the MSB of any W register by executing a Zero-Extend (ZE) instruction on the appropriate address.

Although most instructions are capable of operating on word or byte data sizes, it should be noted that some instructions, including the DSP instructions, operate only on words.

## 3.2.5 NEAR DATA SPACE

An 8 Kbyte 'near' data space is reserved in X address memory space between 0x0000 and 0x1FFF, which is directly addressable via a 13-bit absolute address field within all memory direct instructions. The remaining X address space and all of the Y address space is addressable indirectly. Additionally, the whole of X data space is addressable using MOV instructions, which support memory direct addressing with a 16-bit address field.

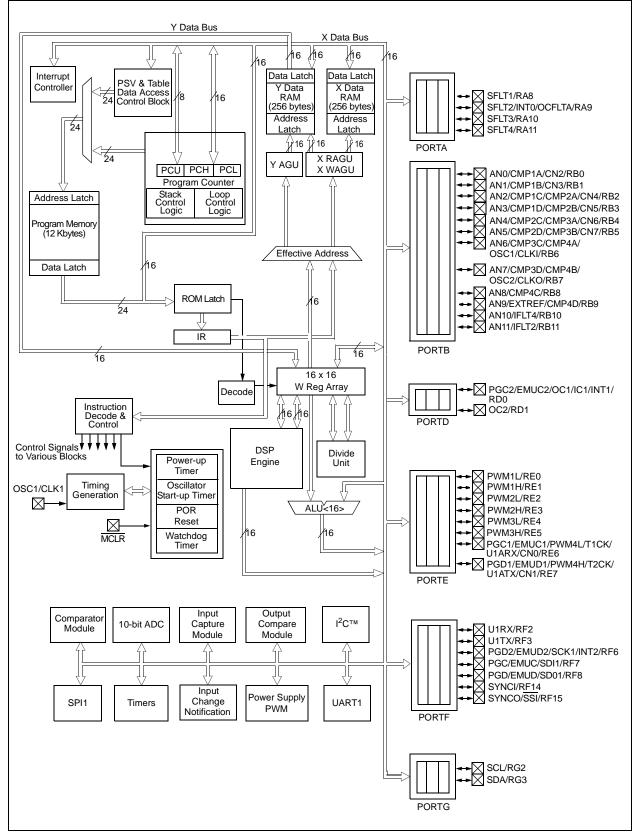

#### 3.2.6 SOFTWARE STACK

The dsPIC DSC device contains a software stack. W15 is used as the Stack Pointer.

The Stack Pointer always points to the first available free word and grows from lower addresses towards higher addresses. It pre-decrements for stack pops and post-increments for stack pushes, as shown in Figure 3-9. Note that for a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, ensuring that the MSB is always clear.

Note: A PC push during exception processing will concatenate the SRL register to the MSB of the PC prior to the push.

There is a Stack Pointer Limit register (SPLIM) associated with the Stack Pointer. SPLIM is uninitialized at Reset. As is the case for the Stack Pointer, SPLIM<0> is forced to '0', because all stack operations must be word-aligned. Whenever an Effective Address (EA) is generated using W15 as a source or destination pointer, the address thus generated is compared with the value in SPLIM. If the contents of the Stack Pointer (W15) and the SPLIM register are equal and a push operation is performed, a stack error trap will not occur. The stack error trap will occur on a subsequent push operation. Thus, for example, if it is desirable to cause a stack error trap when the stack grows beyond address 0x2000 in RAM, initialize the SPLIM with the value, 0x1FFE.

Similarly, a Stack Pointer Underflow (stack error) trap is generated when the Stack Pointer address is found to be less than 0x0800, thus preventing the stack from interfering with the Special Function Register (SFR) space.

A write to the SPLIM register should not be immediately followed by an indirect read operation using W15.

#### FIGURE 3-9: CALL STACK FRAME

## 3.2.7 DATA RAM PROTECTION

The dsPIC30F1010/202X devices support data RAM protection features which enable segments of RAM to be protected when used in conjunction with Boot Code Segment Security. BSRAM (Secure RAM segment for BS) is accessible only from the Boot Segment Flash code when enabled. See Table 3-3 for the BSRAM SFR.

| REGISTER     | J-1J. IF CO.  |                     |                 |                  |                  |                    |       |  |

|--------------|---------------|---------------------|-----------------|------------------|------------------|--------------------|-------|--|

| U-0          | R/W-1         | R/W-0               | R/W-0           | U-0              | U-0              | U-0                | U-0   |  |

| —            |               | CNIP<2:0>           |                 | —                | —                | —                  | —     |  |

| bit 15       |               |                     |                 |                  |                  |                    | bit 8 |  |

|              |               |                     |                 |                  |                  |                    |       |  |

| U-0          | U-0           | U-0                 | U-0             | U-0              | U-0              | U-0                | U-0   |  |

| _            | —             | —                   | —               | —                | —                | —                  |       |  |

| bit 7        |               |                     |                 |                  |                  |                    | bit 0 |  |

|              |               |                     |                 |                  |                  |                    |       |  |

| Legend:      |               |                     |                 |                  |                  |                    |       |  |

| R = Readab   | le bit        | W = Writable        | bit             | U = Unimpler     | mented bit, read | l as '0'           |       |  |

| -n = Value a | It POR        | '1' = Bit is set    |                 | '0' = Bit is cle | ared             | x = Bit is unknown |       |  |

|              |               |                     |                 |                  |                  |                    |       |  |

| bit 15       | Unimpleme     | nted: Read as '     | 0'              |                  |                  |                    |       |  |

| bit 14-12    | CNIP<2:0>:    | Change Notifica     | ation Interrupt | t Priority bits  |                  |                    |       |  |

|              | 111 = Interru | upt is priority 7 ( | highest priori  | ty interrupt)    |                  |                    |       |  |

|              | •             |                     |                 |                  |                  |                    |       |  |

|              | •             |                     |                 |                  |                  |                    |       |  |

|              | •             |                     |                 |                  |                  |                    |       |  |

|              |               | upt is priority 1   |                 |                  |                  |                    |       |  |

|              |               | upt source is dis   |                 |                  |                  |                    |       |  |

| bit 11-0     | Unimpleme     | nted: Read as '     | 0'              |                  |                  |                    |       |  |

|              |               |                     |                 |                  |                  |                    |       |  |

## REGISTER 5-15: IPC6: INTERRUPT PRIORITY CONTROL REGISTER 6

| U-0          | U-0              | U-0                | U-0              | R-0               | R-0             | R-0             | R-0  |

|--------------|------------------|--------------------|------------------|-------------------|-----------------|-----------------|------|

| _            |                  |                    | _                |                   | ILR             | R<3:0>          |      |

| bit 15       |                  |                    |                  |                   |                 |                 | bit  |

|              |                  |                    |                  |                   |                 |                 |      |

| U-0          | R-0              | R-0                | R-0              | R-0               | R-0             | R-0             | R-0  |

| —            |                  |                    |                  | VECNUM<6:0        | >               |                 |      |

| bit 7        |                  |                    |                  |                   |                 |                 | bit  |

|              |                  |                    |                  |                   |                 |                 |      |

| Legend:      |                  |                    |                  |                   |                 |                 |      |

| R = Readab   | le bit           | W = Writable       | bit              | U = Unimplen      | nented bit, rea | ad as '0'       |      |

| -n = Value a | t POR            | '1' = Bit is set   |                  | '0' = Bit is clea | ared            | x = Bit is unkr | nown |

|              |                  |                    |                  |                   |                 |                 |      |

| bit 15-12    | Unimpleme        | ented: Read as '   | 0'               |                   |                 |                 |      |

| bit 11-8     | ILR: New C       | PU Interrupt Price | ority Level bits | 6                 |                 |                 |      |

|              | 1111 <b>= CP</b> | J Interrupt Priori | ty Level is 15   |                   |                 |                 |      |

|              | •                |                    |                  |                   |                 |                 |      |

|              | •                |                    |                  |                   |                 |                 |      |

|              | •                |                    |                  |                   |                 |                 |      |

|              |                  | J Interrupt Priori | •                |                   |                 |                 |      |

|              |                  | U Interrupt Priori | •                |                   |                 |                 |      |

| bit 7        | Unimpleme        | ented: Read as '   | 0'               |                   |                 |                 |      |

| bit 6-0      | VECNUM:          | Vector Number o    | f Pending Inte   | errupt bits       |                 |                 |      |

|              | 0111111 =        | Interrupt Vector   | pending is nu    | mber 135          |                 |                 |      |

|              | •                |                    |                  |                   |                 |                 |      |

|              | •                |                    |                  |                   |                 |                 |      |

|              | -                |                    |                  |                   |                 |                 |      |

|              | 000001 =         | Interrupt Vector   | pending is nu    | mber 9            |                 |                 |      |

## REGISTER 5-20: INTTREG: INTERRUPT CONTROL AND STATUS REGISTER

## 12.23.1 FAULT INTERRUPTS

The FLTIENx bits in the PWMCONx registers determine if an interrupt will be generated when the FLTx input is asserted high. The FLTMOD bits in the FCL-CONx register determines how the PWM generator and its outputs respond to the selected Fault input pin. The FLTDAT<1:0> bits in the IOCONx registers supply the data values to be assigned to the PWMxH,L pins in the advent of a Fault.

The Fault pin logic can operate separately from the PWM logic as an external interrupt pin. If the faults are disabled from affecting the PWM generators in the FCLCONx register, then the Fault pin can be used as a general purpose interrupt pin.

#### 12.23.2 FAULT STATES

The IOCONx register has two bits that determine the state of each PWMx I/O pin when they are overridden by a Fault input. When these bits are cleared, the PWM I/O pin is driven to the inactive state. If the bit is set, the PWM I/O pin is driven to the active state. The active and inactive states are referenced to the polarity defined for each PWM I/O pin (HPOL and LPOL polarity control bits).

## 12.23.3 FAULT INPUT MODES

The Fault input pin has two modes of operation:

- Latched Mode: When the Fault pin is asserted, the PWM outputs go to the states defined in the FLTDAT bits in the IOCONx registers. The PWM outputs remain in this state until the Fault pin is deasserted AND the corresponding interrupt flag has been cleared in software. When both of these actions have occurred, the PWM outputs return to normal operation at the beginning of the next PWM cycle boundary. If the FLTSTAT bit is cleared before the Fault condition ends, the PWM module waits until the Fault pin is no longer asserted to restore the outputs. Software can clear the FLTSTAT bit by writing a zero to the FLTIEN bit.

- Cycle-by-Cycle Mode: When the Fault input pin is asserted, the PWM outputs remain in the deasserted PWM state for as long as the Fault pin is asserted. For Complementary Output modes, PWMH is low (deasserted) and PWML is high (asserted). After the Fault pin is driven high, the PWM outputs return to normal operation at the beginning of the following PWM cycle.

The operating mode for each Fault input pin is selected using the FLTMOD<1:0> control bits in the FCLCONx register.

#### 12.23.4 FAULT ENTRY

The response of the PWM pins to the Fault input pins is always asynchronous with respect to the device clock signals. That is, the PWM outputs should immediately go to the states defined in the FLTDAT register bits without any interaction from the dsPIC DSC device or software.

Refer to Section 12.28 "Fault and Current-Limit Override Issues with Dead-Time Logic" for information regarding data sensitivity and behavior in response to current-limit or Fault events.

#### 12.23.5 FAULT EXIT

The restoration of the PWM signals after a Fault condition has ended must occur at a PWM cycle boundary to ensure proper synchronization of PWM signal edges and manual signal overrides. The next PWM cycle begins when the PTMRx value is zero.

#### 12.23.6 FAULT EXIT WITH PTMR DISABLED

There is a special case for exiting a Fault condition when the PWM time base is disabled (PTEN = 0). When a Fault input is programmed for Cycle-by-Cycle mode, the PWM outputs are immediately restored to normal operation when the Fault input pin is deasserted. The PWM outputs should return to their default programmed values. (The time base is disabled, so there is no reason to wait for the beginning of the next PWM cycle.)

When a Fault input is programmed for Latched mode, the PWM outputs are restored immediately when the Fault input pin is deasserted AND the FSTAT bit has been cleared in software.

#### 12.23.7 FAULT PIN SOFTWARE CONTROL

The Fault pin can be controlled manually in software. Since the Fault input is shared with a PORT I/O pin, the PORT pin can be configured as an output by clearing the corresponding TRIS bit. When the PORT bit for the pin is cleared, the Fault input will be activated.

**Note:** The user should use caution when controlling the Fault inputs in software. If the TRIS bit for the Fault pin is cleared and the PORT bit is set high, then the Fault input cannot be driven externally.

## 14.5 Automatic Clock Stretch

In the Slave modes, the module can synchronize buffer reads and write to the master device by clock stretching.

## 14.5.1 TRANSMIT CLOCK STRETCHING

Both 10-bit and 7-bit Transmit modes implement clock stretching by asserting the SCLREL bit after the falling edge of the ninth clock if the TBF bit is cleared, indicating the buffer is empty.

In Slave Transmit modes, clock stretching is always performed, irrespective of the STREN bit.

Clock synchronization takes place following the ninth clock of the transmit sequence. If the device samples an ACK on the falling edge of the ninth clock, and if the TBF bit is still clear, then the SCLREL bit is automatically cleared. The SCLREL being cleared to '0' will assert the SCL line low. The user's ISR must set the SCLREL bit before transmission is allowed to continue. By holding the SCL line low, the user has time to service the ISR and load the contents of the I2CTRN before the master device can initiate another transmit sequence.

- Note 1: If the user loads the contents of I2CTRN, setting the TBF bit before the falling edge of the ninth clock, the SCLREL bit will not be cleared and clock stretching will not occur.

- **2:** The SCLREL bit can be set in software, regardless of the state of the TBF bit.

## 14.5.2 RECEIVE CLOCK STRETCHING

The STREN bit in the I2CCON register can be used to enable clock stretching in Slave Receive mode. When the STREN bit is set, the SCL pin will be held low at the end of each data receive sequence.

## 14.5.3 CLOCK STRETCHING DURING 7-BIT ADDRESSING (STREN = 1)

When the STREN bit is set in Slave Receive mode, the SCL line is held low when the buffer register is full. The method for stretching the SCL output is the same for both 7 and 10-bit Addressing modes.

Clock stretching takes place following the ninth clock of the receive sequence. On the falling edge of the ninth clock at the end of the ACK sequence, if the RBF bit is set, the SCLREL bit is automatically cleared, forcing the SCL output to be held low. The user's ISR must set the SCLREL bit before reception is allowed to continue. By holding the SCL line low, the user has time to service the ISR and read the contents of the I2CRCV before the master device can initiate another receive sequence. This will prevent buffer overruns from occurring.

- Note 1: If the user reads the contents of the I2CRCV, clearing the RBF bit before the falling edge of the ninth clock, the SCLREL bit will not be cleared and clock stretching will not occur.

- 2: The SCLREL bit can be set in software, regardless of the state of the RBF bit. The user should be careful to clear the RBF bit in the ISR before the next receive sequence in order to prevent an Overflow condition.

## 14.5.4 CLOCK STRETCHING DURING 10-BIT ADDRESSING (STREN = 1)

Clock stretching takes place automatically during the addressing sequence. Because this module has a register for the entire address, it is not necessary for the protocol to wait for the address to be updated.

After the address phase is complete, clock stretching will occur on each data receive or transmit sequence as was described earlier.

## 14.6 Software Controlled Clock Stretching (STREN = 1)

When the STREN bit is '1', the SCLREL bit may be cleared by software to allow software to control the clock stretching. The logic will synchronize writes to the SCLREL bit with the SCL clock. Clearing the SCLREL bit will not assert the SCL output until the module detects a falling edge on the SCL output and SCL is sampled low. If the SCLREL bit is cleared by the user while the SCL line has been sampled low, the SCL output will be asserted (held low). The SCL output will remain low until the SCLREL bit is set, and all other devices on the I<sup>2</sup>C bus have deasserted SCL. This ensures that a write to the SCLREL bit will not violate the minimum high time requirement for SCL.

If the STREN bit is '0', a software write to the SCLREL bit will be disregarded and have no effect on the SCLREL bit.

## 14.7 Interrupts

The  $l^2C$  module generates two interrupt flags, MI2CIF ( $l^2C$  Master Interrupt Flag) and SI2CIF ( $l^2C$  Slave Interrupt Flag). The MI2CIF interrupt flag is activated on completion of a master message event. The SI2CIF interrupt flag is activated on detection of a message directed to the slave.

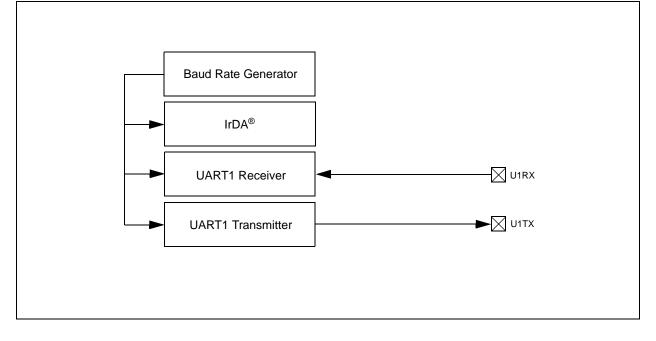

## 15.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART) MODULE

**Note:** This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "*dsPIC30F Family Reference Manual*" (DS70046).

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the dsPIC30F1010/202X device family. The UART is a full-duplex asynchronous system that can communicate with peripheral devices, such as personal computers, LIN, RS-232 and RS-485 interfaces. The module also includes an IrDA encoder and decoder.

The primary features of the UART module are:

- Full-Duplex 8 or 9-bit Data Transmission through the U1TX and U1RX pins

- Even, Odd or No Parity Options (for 8-bit data)

- · One or Two Stop bits

- Fully Integrated Baud Rate Generator with 16-bit Prescaler

- Baud Rates Ranging from 1 Mbps to 15 bps at 16 MIPS

- 4-Deep First-In-First-Out (FIFO) Transmit Data Buffer

- 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-bit mode with Address Detect (9th bit = 1)

- Transmit and Receive Interrupts

- Loopback mode for Diagnostic Support

- Support for Sync and Break Characters

- Supports Automatic Baud Rate Detection

- IrDA Encoder and Decoder Logic

- 16x Baud Clock Output for IrDA Support

A simplified block diagram of the UART is shown in Figure 15-1. The UART module consists of these key important hardware elements:

- Baud Rate Generator

- Asynchronous Transmitter

- Asynchronous Receiver

## FIGURE 15-1: UART SIMPLIFIED BLOCK DIAGRAM

| TABI               | LE 19-2:             | INSTR                                   | INSTRUCTION SET OVERVIEW (CONTINUED) |                                                  |                   |                |                          |  |  |  |  |  |

|--------------------|----------------------|-----------------------------------------|--------------------------------------|--------------------------------------------------|-------------------|----------------|--------------------------|--|--|--|--|--|

| Base<br>Instr<br># | Assembly<br>Mnemonic | Assembly Syntax                         |                                      | Description                                      | # of<br>word<br>s | # of<br>cycles | Status Flags<br>Affected |  |  |  |  |  |

| 11                 | BTSS                 | BTSS                                    | f,#bit4                              | Bit Test f, Skip if Set                          | 1                 | 1<br>(2 or 3)  | None                     |  |  |  |  |  |

|                    |                      | BTSS Ws, #bit4 Bit Test Ws, Skip if Set |                                      | Bit Test Ws, Skip if Set                         | 1                 | 1<br>(2 or 3)  | None                     |  |  |  |  |  |

| 12                 | BTST                 | BTST                                    | f,#bit4                              | Bit Test f                                       | 1                 | 1              | Z                        |  |  |  |  |  |

|                    |                      | BTST.C                                  | Ws,#bit4                             | Bit Test Ws to C                                 | 1                 | 1              | С                        |  |  |  |  |  |

|                    |                      | BTST.Z                                  | Ws,#bit4                             | Bit Test Ws to Z                                 | 1                 | 1              | Z                        |  |  |  |  |  |

|                    |                      | BTST.C                                  | Ws,Wb                                | Bit Test Ws <wb> to C</wb>                       | 1                 | 1              | С                        |  |  |  |  |  |

|                    |                      | BTST.Z                                  | Ws,Wb                                | Bit Test Ws <wb> to Z</wb>                       | 1                 | 1              | Z                        |  |  |  |  |  |

| 13                 | BTSTS                | BTSTS                                   | f,#bit4                              | Bit Test then Set f                              | 1                 | 1              | Z                        |  |  |  |  |  |

|                    |                      | BTSTS.C                                 | Ws,#bit4                             | Bit Test Ws to C, then Set                       | 1                 | 1              | С                        |  |  |  |  |  |

|                    |                      | BTSTS.Z                                 | Ws,#bit4                             | Bit Test Ws to Z, then Set                       | 1                 | 1              | Z                        |  |  |  |  |  |

| 14                 | CALL                 | CALL                                    | lit23                                | Call subroutine                                  | 2                 | 2              | None                     |  |  |  |  |  |

|                    |                      | CALL                                    | Wn                                   | Call indirect subroutine                         | 1                 | 2              | None                     |  |  |  |  |  |

| 15                 | CLR                  | CLR                                     | f                                    | f = 0x0000                                       | 1                 | 1              | None                     |  |  |  |  |  |

|                    |                      | CLR                                     | WREG                                 | WREG = 0x0000                                    | 1                 | 1              | None                     |  |  |  |  |  |

|                    |                      | CLR                                     | Ws                                   | Ws = 0x0000                                      | 1                 | 1              | None                     |  |  |  |  |  |

|                    |                      | CLR                                     | Acc,Wx,Wxd,Wy,Wyd,AWB                | Clear Accumulator                                | 1                 | 1              | OA,OB,SA,SB              |  |  |  |  |  |

| 16                 | CLRWDT               | CLRWDT                                  |                                      | Clear Watchdog Timer                             | 1                 | 1              | WDTO,Sleep               |  |  |  |  |  |

| 17                 | COM                  | COM                                     | f                                    | $f = \overline{f}$                               | 1                 | 1              | N,Z                      |  |  |  |  |  |

|                    |                      | COM                                     | f,WREG                               | WREG = f                                         | 1                 | 1              | N,Z                      |  |  |  |  |  |

|                    |                      | COM                                     | Ws,Wd                                | $Wd = \overline{Ws}$                             | 1                 | 1              | N,Z                      |  |  |  |  |  |

| 18                 | CP                   | CP                                      | f                                    | Compare f with WREG                              | 1                 | 1              | C,DC,N,OV,Z              |  |  |  |  |  |

|                    |                      | CP                                      | Wb,#lit5                             | Compare Wb with lit5                             | 1                 | 1              | C,DC,N,OV,Z              |  |  |  |  |  |

|                    |                      | CP                                      | Wb,Ws                                | Compare Wb with Ws (Wb – Ws)                     | 1                 | 1              | C,DC,N,OV,Z              |  |  |  |  |  |

| 19                 | CPO                  | CP0                                     | f                                    | Compare f with 0x0000                            | 1                 | 1              | C,DC,N,OV,Z              |  |  |  |  |  |

|                    |                      | CP0                                     | Ws                                   | Compare Ws with 0x0000                           |                   | 1              | C,DC,N,OV,Z              |  |  |  |  |  |

| 20                 | CPB                  | CPB                                     | f                                    | Compare f with WREG, with Borrow                 | 1                 | 1              | C,DC,N,OV,Z              |  |  |  |  |  |

|                    |                      | CPB                                     | Wb,#lit5                             | Compare Wb with lit5, with Borrow                | 1                 | 1              | C,DC,N,OV,Z              |  |  |  |  |  |

|                    |                      | CPB                                     | Wb,Ws                                | Compare Wb with Ws, with Borrow<br>(Wb – Ws – C) | 1                 | 1              | C,DC,N,OV,Z              |  |  |  |  |  |

| 21                 | CPSEQ                | CPSEQ                                   | Wb, Wn                               | Compare Wb with Wn, skip if =                    | 1                 | 1<br>(2 or 3)  | None                     |  |  |  |  |  |

| 22                 | CPSGT                | CPSGT                                   | Wb, Wn                               | Compare Wb with Wn, skip if >                    | 1                 | 1<br>(2 or 3)  | None                     |  |  |  |  |  |

| 23                 | CPSLT                | CPSLT                                   | Wb, Wn                               | Compare Wb with Wn, skip if <                    | 1                 | 1<br>(2 or 3)  | None                     |  |  |  |  |  |

| 24                 | CPSNE                | CPSNE                                   | Wb, Wn                               | Compare Wb with Wn, skip if $\neq$               | 1                 | 1<br>(2 or 3)  | None                     |  |  |  |  |  |

| 25                 | DAW                  | DAW                                     | Wn                                   | Wn = decimal adjust Wn                           | 1                 | 1              | С                        |  |  |  |  |  |

| 26                 | DEC                  | DEC                                     | f                                    | f = f - 1                                        | 1                 | 1              | C,DC,N,OV,Z              |  |  |  |  |  |

|                    |                      | DEC                                     | f,WREG                               | WREG = $f - 1$                                   | 1                 | 1              | C,DC,N,OV,Z              |  |  |  |  |  |

|                    |                      | DEC                                     | Ws,Wd                                | Wd = Ws - 1                                      | 1                 | 1              | C,DC,N,OV,Z              |  |  |  |  |  |

| 27                 | DEC2                 | DEC2                                    | f                                    | f = f - 2                                        | 1                 | 1              | C,DC,N,OV,Z              |  |  |  |  |  |

|                    |                      | DEC2                                    | f,WREG                               | WREG = f - 2                                     | 1                 | 1              | C,DC,N,OV,Z              |  |  |  |  |  |

|                    |                      | DEC2                                    | Ws,Wd                                | Wd = Ws - 2                                      | 1                 | 1              | C,DC,N,OV,Z              |  |  |  |  |  |

| 28                 | DISI                 | DISI                                    | #lit14                               | Disable Interrupts for k instruction cycles      | 1                 | 1              | None                     |  |  |  |  |  |

| 29                 | DIV                  | DIV.S                                   | Wm,Wn                                | Signed 16/16-bit Integer Divide                  | 1                 | 18             | N,Z,C, OV                |  |  |  |  |  |

|                    |                      | DIV.SD                                  | Wm,Wn                                | Signed 32/16-bit Integer Divide                  | 1                 | 18             | N,Z,C, OV                |  |  |  |  |  |

|                    |                      | DIV.U                                   | Wm,Wn                                | Unsigned 16/16-bit Integer Divide                | 1                 | 18             | N,Z,C, OV                |  |  |  |  |  |

|                    |                      | DIV.UD                                  | Wm,Wn                                | Unsigned 32/16-bit Integer Divide                | 1                 | 18             | N,Z,C, OV                |  |  |  |  |  |

| 30                 | DIVF                 | DIVF                                    | Wm,Wn                                | Signed 16/16-bit Fractional Divide               | 1                 | 18             | N,Z,C, OV                |  |  |  |  |  |

| 31                 | DO                   | DO                                      | <pre>#lit14,Expr</pre>               | Do code to PC + Expr, lit14 + 1 times            | 2                 | 2              | None                     |  |  |  |  |  |

| <u> </u>           |                      | DO                                      | Wn,Expr                              | Do code to PC + Expr, (Wn) + 1 times             | 2                 | 2              | None                     |  |  |  |  |  |

| 32                 | ED                   | ED                                      | Wm * Wm,Acc,Wx,Wy,Wxd                | Euclidean Distance (no accumulate)               | 1                 | 1              | OA,OB,OAB,<br>SA,SB,SAB  |  |  |  |  |  |

| 33                 | EDAC                 | EDAC                                    | Wm * Wm,Acc,Wx,Wy,Wxd                | Euclidean Distance                               | 1                 | 1              | OA,OB,OAB,<br>SA,SB,SAB  |  |  |  |  |  |

| TABLE 19-2: | INSTRUCTION SET OVERVIEW | (CONTINUED) |   |

|-------------|--------------------------|-------------|---|

|             |                          |             | / |

| Base<br>Instr<br># | Assembly<br>Mnemonic |        | Assembly Syntax | Description                                       | # of<br>word<br>s | # of<br>cycles | Status Flags<br>Affected |

|--------------------|----------------------|--------|-----------------|---------------------------------------------------|-------------------|----------------|--------------------------|

| 52                 | NEG                  | NEG    | Acc             | Negate Accumulator                                | 1                 | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | NEG    | f               | $f = \overline{f} + 1$                            | 1                 | 1              | C,DC,N,OV,Z              |

|                    |                      | NEG    | f,WREG          | WREG = $\overline{f}$ + 1                         | 1                 | 1              | C,DC,N,OV,Z              |

|                    |                      | NEG    | Ws,Wd           | $Wd = \overline{Ws} + 1$                          | 1                 | 1              | C,DC,N,OV,Z              |

| 53                 | NOP                  | NOP    |                 | No Operation                                      | 1                 | 1              | None                     |

|                    |                      | NOPR   |                 | No Operation                                      | 1                 | 1              | None                     |

| 54                 | POP                  | POP    | f               | Pop f from Top-of-Stack (TOS)                     | 1                 | 1              | None                     |

|                    |                      | POP    | Wdo             | Pop from Top-of-Stack (TOS) to Wdo                | 1                 | 1              | None                     |

|                    |                      | POP.D  | Wnd             | Pop from Top-of-Stack (TOS) to<br>W(nd):W(nd + 1) | 1                 | 2              | None                     |

|                    |                      | POP.S  |                 | Pop Shadow Registers                              | 1                 | 1              | All                      |

| 55                 | PUSH                 | PUSH   | f               | Push f to Top-of-Stack (TOS)                      | 1                 | 1              | None                     |

|                    |                      | PUSH   | Wso             | Push Wso to Top-of-Stack (TOS)                    | 1                 | 1              | None                     |

|                    |                      | PUSH.D | Wns             | Push W(ns):W(ns + 1) to Top-of-Stack<br>(TOS)     | 1                 | 2              | None                     |

|                    |                      | PUSH.S |                 | Push Shadow Registers                             | 1                 | 1              | None                     |

| 56                 | PWRSAV               | PWRSAV | #lit1           | Go into Sleep or Idle mode                        | 1                 | 1              | WDTO,Sleep               |

| 57                 | RCALL                | RCALL  | Expr            | Relative Call                                     | 1                 | 2              | None                     |

|                    |                      | RCALL  | Wn              | Computed Call                                     | 1                 | 2              | None                     |

| 58                 | REPEAT               | REPEAT | #lit14          | Repeat Next Instruction lit14 + 1 times           | 1                 | 1              | None                     |

|                    |                      | REPEAT | Wn              | Repeat Next Instruction (Wn) + 1 times            | 1                 | 1              | None                     |

| 59                 | RESET                | RESET  |                 | Software device Reset                             | 1                 | 1              | None                     |

| 60                 | RETFIE               | RETFIE |                 | Return from interrupt                             | 1                 | 3 (2)          | None                     |

| 61                 | RETLW                | RETLW  | #lit10,Wn       | Return with literal in Wn                         | 1                 | 3 (2)          | None                     |

| 62                 | RETURN               | RETURN |                 |                                                   | 1                 | 3 (2)          | None                     |

| 63                 | RLC                  | RLC    | f               | f = Rotate Left through Carry f                   | 1                 | 1              | C,N,Z                    |

|                    |                      | RLC    | f,WREG          | WREG = Rotate Left through Carry f                | 1                 | 1              | C,N,Z                    |

|                    |                      | RLC    | Ws,Wd           | Wd = Rotate Left through Carry Ws                 | 1                 | 1              | C,N,Z                    |

| 64                 | RLNC                 | RLNC   | f               | f = Rotate Left (No Carry) f                      | 1                 | 1              | N,Z                      |

|                    |                      | RLNC   | f,WREG          | WREG = Rotate Left (No Carry) f                   | 1                 | 1              | N,Z                      |

|                    |                      | RLNC   | Ws,Wd           | Wd = Rotate Left (No Carry) Ws                    | 1                 | 1              | N,Z                      |

| 65                 | RRC                  | RRC    | f               | f = Rotate Right through Carry f                  | 1                 | 1              | C,N,Z                    |

|                    |                      | RRC    | f,WREG          | WREG = Rotate Right through Carry f               | 1                 | 1              | C,N,Z                    |

|                    |                      | RRC    | Ws,Wd           | Wd = Rotate Right through Carry Ws                | 1                 | 1              | C,N,Z                    |

| 66                 | RRNC                 | RRNC   | f               | f = Rotate Right (No Carry) f                     | 1                 | 1              | N,Z                      |

|                    |                      | RRNC   | f,WREG          | WREG = Rotate Right (No Carry) f                  | 1                 | 1              | N,Z                      |

|                    |                      | RRNC   | Ws,Wd           | Wd = Rotate Right (No Carry) Ws                   | 1                 | 1              | N,Z                      |

| 67                 | SAC                  | SAC    | Acc,#Slit4,Wdo  | Store Accumulator                                 | 1                 | 1              | None                     |

|                    |                      | SAC.R  | Acc,#Slit4,Wdo  | Store Rounded Accumulator                         | 1                 | 1              | None                     |

| 68                 | SE                   | SE     | Ws,Wnd          | Wnd = sign extended Ws                            | 1                 | 1              | C,N,Z                    |

| 69                 | SETM                 | SETM   | f               | f = 0xFFFF                                        | 1                 | 1              | None                     |

|                    |                      | SETM   | WREG            | WREG = 0xFFFF                                     | 1                 | 1              | None                     |

|                    |                      | SETM   | Ws              | Ws = 0xFFFF                                       | 1                 | 1              | None                     |

| 70                 | SFTAC                | SFTAC  | Acc,Wn          | Arithmetic Shift Accumulator by (Wn)              | 1                 | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | SFTAC  | Acc,#Slit6      | Arithmetic Shift Accumulator by Slit6             | 1                 | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

| 71                 | SL                   | SL     | f               | f = Left Shift f                                  | 1                 | 1              | C,N,OV,Z                 |

|                    |                      | SL     | f,WREG          | WREG = Left Shift f                               | 1                 | 1              | C,N,OV,Z                 |

|                    |                      | SL     | Ws,Wd           | Wd = Left Shift Ws                                | 1                 | 1              | C,N,OV,Z                 |

|                    |                      | SL     | Wb,Wns,Wnd      | Wnd = Left Shift Wb by Wns                        | 1                 | 1              | N,Z                      |

|                    |                      | SL     | Wb,#lit5,Wnd    | Wnd = Left Shift Wb by lit5                       | 1                 | 1              | N,Z                      |

## TABLE 19-2: INSTRUCTION SET OVERVIEW (CONTINUED)

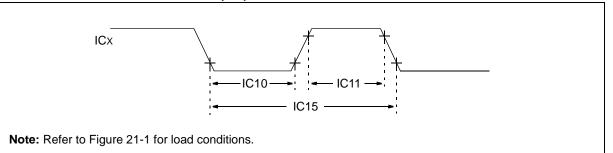

## FIGURE 21-7: INPUT CAPTURE x (ICx) TIMING CHARACTERISTICS

## TABLE 21-23: INPUT CAPTURE x TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                     | Standard Operati<br>(unless otherwis<br>Operating temper | <b>e stated)</b><br>rature -40°C ≤ T4 | <b>3V and 5.0</b><br>A ≤ +85°C fo<br>A ≤ +125°C | or Industr | ial                              |

|--------------------|--------|---------------------|----------------------------------------------------------|---------------------------------------|-------------------------------------------------|------------|----------------------------------|

| Param<br>No.       | Symbol | Characte            | ristic <sup>(1)</sup>                                    | Min                                   | Мах                                             | Units      | Conditions                       |

| IC10               | TccL   | ICx Input Low Time  | No Prescaler                                             | 0.5 Tcy + 20                          |                                                 | ns         |                                  |

|                    |        |                     | With Prescaler                                           | 10                                    | _                                               | ns         |                                  |

| IC11               | TccH   | ICx Input High Time | No Prescaler                                             | 0.5 Tcy + 20                          | _                                               | ns         |                                  |

|                    |        | With Prescaler      | 10                                                       | _                                     | ns                                              |            |                                  |

| IC15               | TccP   | ICx Input Period    | •                                                        | (2 Tcy + 40)/N                        | _                                               | ns         | N = Prescale<br>value (1, 4, 16) |

Note 1: These parameters are characterized but not tested in manufacturing.

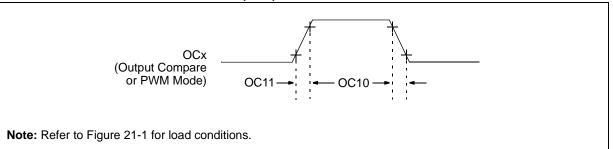

#### FIGURE 21-8: OUTPUT COMPARE x (OCx) MODULE TIMING CHARACTERISTICS

#### TABLE 21-24: OUTPUT COMPARE x MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                               | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.3V and 5.0V (\pm 10\%) \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                    |                         |       |                    |  |  |

|--------------------|--------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------------|-------|--------------------|--|--|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup> | Min                                                                                                                                                                                                                                                                                                | Тур <sup>(2)</sup> | Max                     | Units | Conditions         |  |  |

| OC10               | TccF   | OCx Output Fall Time          | —                                                                                                                                                                                                                                                                                                  | —                  | _                       | ns    | See Parameter D032 |  |  |

| OC11               | TccR   | OCx Output Rise Time          | —                                                                                                                                                                                                                                                                                                  | _                  | — ns See Parameter D031 |       |                    |  |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 5V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

<sup>© 2006-2014</sup> Microchip Technology Inc.

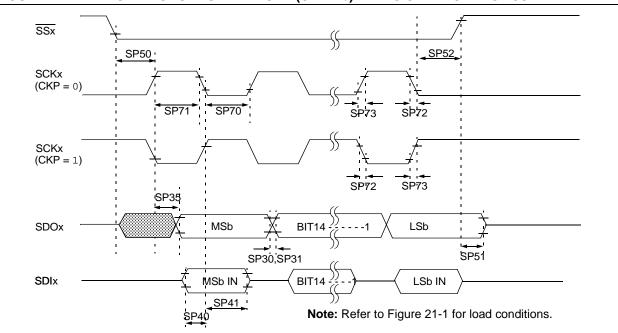

#### FIGURE 21-14: SPIX MODULE SLAVE MODE (CKE = 0) TIMING CHARACTERISTICS

#### TABLE 21-29: SPIX MODULE SLAVE MODE (CKE = 0) TIMING REQUIREMENTS

| АС СН        | ARACTERI              | STICS                                             | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.3V and 5.0V (\pm 10\%)} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |                    |     |       |                    |  |

|--------------|-----------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|--------------------|--|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                     | Min                                                                                                                                                                                                                                                                                           | Тур <sup>(2)</sup> | Max | Units | Conditions         |  |

| SP70         | TscL                  | SCKx Input Low Time                               | 30                                                                                                                                                                                                                                                                                            | -                  | _   | ns    |                    |  |

| SP71         | TscH                  | SCKx Input High Time                              | 30                                                                                                                                                                                                                                                                                            | _                  |     | ns    |                    |  |

| SP72         | TscF                  | SCKx Input Fall Time <sup>(3)</sup>               |                                                                                                                                                                                                                                                                                               | 10                 | 25  | ns    |                    |  |

| SP73         | TscR                  | SCKx Input Rise Time <sup>(3)</sup>               |                                                                                                                                                                                                                                                                                               | 10                 | 25  | ns    |                    |  |

| SP30         | TdoF                  | SDOx Data Output Fall Time <sup>(3)</sup>         | —                                                                                                                                                                                                                                                                                             |                    | _   | ns    | See Parameter D032 |  |

| SP31         | TdoR                  | SDOx Data Output Rise Time <sup>(3)</sup>         | —                                                                                                                                                                                                                                                                                             | _                  | _   | ns    | See Parameter D031 |  |

| SP35         | TscH2doV<br>TscL2doV  | SDOx Data Output Valid after<br>SCKx Edge         | —                                                                                                                                                                                                                                                                                             | _                  | 30  | ns    |                    |  |

| SP40         | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge        | 20                                                                                                                                                                                                                                                                                            | _                  | _   | ns    |                    |  |

| SP41         | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge         | 20                                                                                                                                                                                                                                                                                            | _                  | _   | ns    |                    |  |

| SP50         | TssL2scH,<br>TssL2scL | $\overline{SSx}$ to SCKx $\uparrow$ or SCKx Input | 120                                                                                                                                                                                                                                                                                           | —                  | —   | ns    |                    |  |

| SP51         | TssH2doZ              | SSx↑ to SDOx Output High-Impedance <sup>(3)</sup> | 10                                                                                                                                                                                                                                                                                            | —                  | 50  | ns    |                    |  |

| SP52         | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                               | 1.5 TCY + 40                                                                                                                                                                                                                                                                                  | _                  |     | ns    |                    |  |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 5V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

3: Assumes 50 pF load on all SPIx pins.

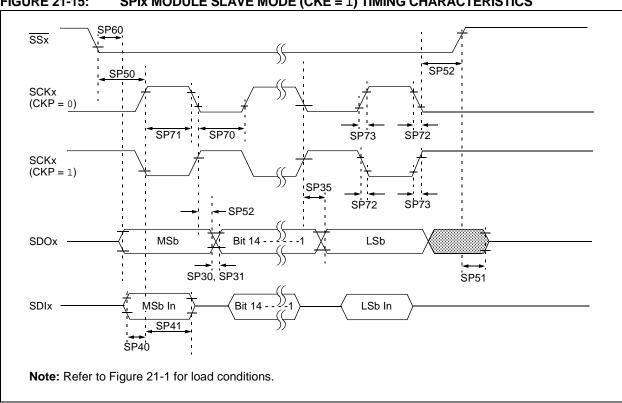

#### FIGURE 21-15: SPIx MODULE SLAVE MODE (CKE = 1) TIMING CHARACTERISTICS

| TABLE 21-34: | COMPARATOR OPERATING CONDITIONS |

|--------------|---------------------------------|

|--------------|---------------------------------|

| Symbol | Characteristic    | Min | Тур | Max | Units | Comments                                                                        |  |  |

|--------|-------------------|-----|-----|-----|-------|---------------------------------------------------------------------------------|--|--|

| Vdd    | Voltage Range     | 3.0 | —   | 3.6 | V     | Operating range of 3.0 V-3.6V                                                   |  |  |

| Vdd    | Voltage Range     | 4.5 | —   | 5.5 | V     | Operating range of 4.5 V-5.5 V                                                  |  |  |

| Темр   | Temperature Range | -40 | _   | 105 | °C    | Note that junction temperature can exceed +125°C under these ambient conditions |  |  |

## TABLE 21-35: COMPARATOR AC AND DC SPECIFICATIONS

|                             |                                    | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature: -40°C $\leq$ TA $\leq$ +105°C |                 |           |          |                                                                                                                       |  |  |  |

|-----------------------------|------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------|-----------|----------|-----------------------------------------------------------------------------------------------------------------------|--|--|--|

| Symbol                      | Characteristic                     | Min                                                                                                             | Typ Max Units C |           | Comments |                                                                                                                       |  |  |  |

| VIOFF                       | Input offset voltage               | —                                                                                                               | ±5              | ±15       | mV       |                                                                                                                       |  |  |  |

| VICM                        | Input Common-Mode<br>Voltage Range | 0                                                                                                               | —               | VDD - 1.5 | V        |                                                                                                                       |  |  |  |

| VGAIN                       | Open Loop Gain                     | 90                                                                                                              | —               | —         | db       |                                                                                                                       |  |  |  |

| CMRR                        | Common-Mode Rejection<br>Ratio     | 70                                                                                                              | —               | —         | db       |                                                                                                                       |  |  |  |