Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

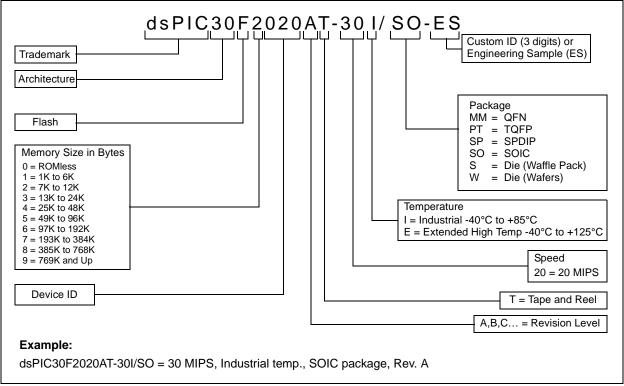

#### Details

•XFI

| Becano                     |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | dsPIC                                                                         |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 20 MIPS                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                         |

| Number of I/O              | 21                                                                            |

| Program Memory Size        | 12KB (4K x 24)                                                                |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | · ·                                                                           |

| RAM Size                   | 512 x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                     |

| Data Converters            | A/D 8x10b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f2020-20e-mm |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

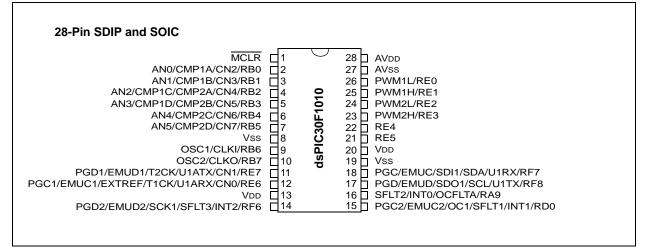

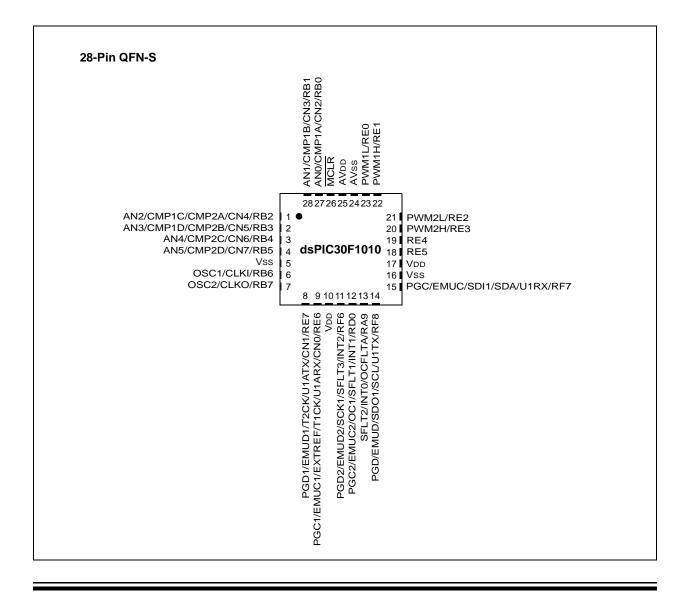

#### **Pin Diagrams**

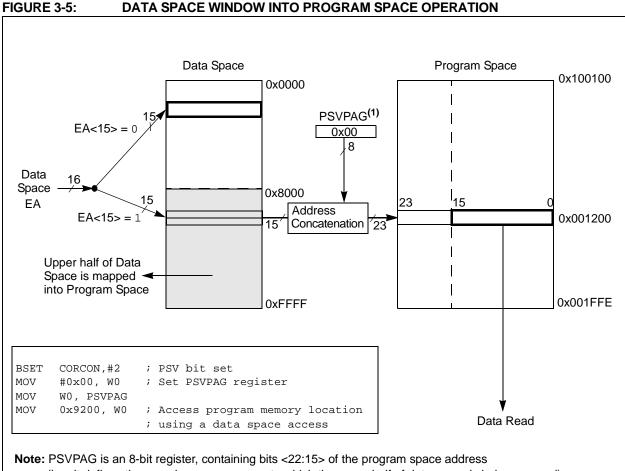

# 2.2 Programmer's Model

The programmer's model is shown in Figure 2-1 and consists of 16x16-bit working registers (W0 through W15), 2x40-bit accumulators (ACCA and ACCB), STATUS register (SR), Data Table Page register (TBLPAG), Program Space Visibility Page register (PSVPAG), DO and REPEAT registers (DOSTART, DOEND, DCOUNT and RCOUNT), and Program Counter (PC). The working registers can act as data, address or offset registers. All registers are memory mapped. W0 acts as the W register for file register addressing.

Some of these registers have a shadow register associated with each of them, as shown in Figure 2-1. The shadow register is used as a temporary holding register and can transfer its contents to or from its host register upon the occurrence of an event. None of the shadow registers are accessible directly. The following rules apply for transfer of registers into and out of shadows.

- PUSH.S and POP.S W0, W1, W2, W3, SR (DC, N, OV, Z and C bits only) are transferred.

- DO instruction DOSTART, DOEND, DCOUNT shadows are pushed on loop start, and popped on loop end.

When a byte operation is performed on a working register, only the Least Significant Byte (LSB) of the target register is affected. However, a benefit of memory mapped working registers is that both the Least and Most Significant Bytes (MSBs) can be manipulated through byte wide data memory space accesses.

#### 2.2.1 SOFTWARE STACK POINTER/ FRAME POINTER

The dsPIC<sup>®</sup> DSC devices contain a software stack. W15 is the dedicated software Stack Pointer (SP), and will be automatically modified by exception processing and subroutine calls and returns. However, W15 can be referenced by any instruction in the same manner as all other W registers. This simplifies the reading, writing and manipulation of the Stack Pointer (e.g., creating stack frames).

| Note: | In order to protect against misaligi | ned |

|-------|--------------------------------------|-----|

|       | stack accesses, W15<0> is always cle | ar. |

W15 is initialized to 0x0800 during a Reset. The user may reprogram the SP during initialization to any location within data space.

W14 has been dedicated as a Stack Frame Pointer as defined by the LNK and ULNK instructions. However, W14 can be referenced by any instruction in the same manner as all other W registers.

### 2.2.2 STATUS REGISTER

The dsPIC DSC core has a 16-bit STATUS Register (SR), the LSB of which is referred to as the SR Low Byte (SRL) and the MSB as the SR High Byte (SRH). See Figure 2-1 for SR layout.

SRL contains all the MCU ALU operation status flags (including the Z bit), as well as the CPU Interrupt Priority Level Status bits, IPL<2:0>, and the REPEAT active Status bit, RA. During exception processing, SRL is concatenated with the MSB of the PC to form a complete word value, which is then stacked.

The upper byte of the STATUS register contains the DSP Adder/Subtracter status bits, the DO Loop Active bit (DA) and the Digit Carry (DC) Status bit.

### 2.2.3 PROGRAM COUNTER

The Program Counter is 23 bits wide. Bit 0 is always clear. Therefore, the PC can address up to 4M instruction words.

#### 2.4.2.4 Data Space Write Saturation

In addition to adder/subtracter saturation, writes to data space may also be saturated, but without affecting the contents of the source accumulator. The data space write saturation logic block accepts a 16-bit, 1.15 fractional value from the round logic block as its input, together with overflow status from the original source (accumulator) and the 16-bit round adder. These are combined and used to select the appropriate 1.15 fractional value as output to write to data space memory.

If the SATDW bit in the CORCON register is set, data (after rounding or truncation) is tested for overflow and adjusted accordingly. For input data greater than 0x007FFF, data written to memory is forced to the maximum positive 1.15 value, 0x7FFF. For input data less than 0xFF8000, data written to memory is forced to the maximum negative 1.15 value, 0x8000. The MSb of the source (bit 39) is used to determine the sign of the operand being tested.

If the SATDW bit in the CORCON register is not set, the input data is always passed through unmodified under all conditions.

#### 2.4.3 BARREL SHIFTER

The barrel shifter is capable of performing up to 15-bit arithmetic or logic right shifts, or up to 16-bit left shifts in a single cycle. The source can be either of the two DSP accumulators or the X bus (to support multi-bit shifts of register or memory data).

The shifter requires a signed binary value to determine both the magnitude (number of bits) and direction of the shift operation. A positive value will shift the operand right. A negative value will shift the operand left. A value of '0' will not modify the operand.

The barrel shifter is 40 bits wide, thereby obtaining a 40-bit result for DSP shift operations and a 16-bit result for MCU shift operations. Data from the X bus is presented to the barrel shifter between bit positions 16 to 31 for right shifts, and bit positions 0 to 15 for left shifts.

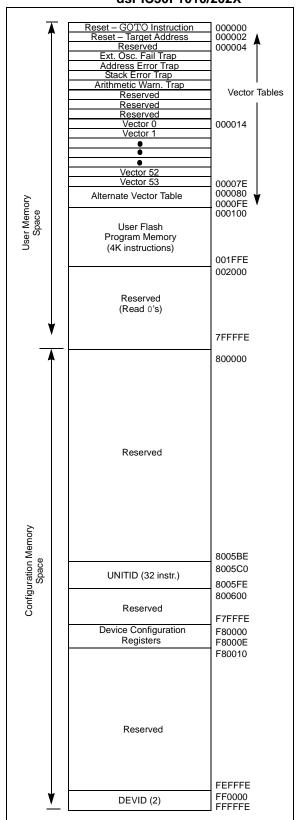

# 3.0 MEMORY ORGANIZATION

**Note:** This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "*dsPIC30F Family Reference Manual*" (DS70046). For more information on the device instruction set and programming, refer to the "*dsPIC30F/ 33F Programmer's Reference Manual*" (DS70157).

# 3.1 Program Address Space

The program address space is 4M instruction words. It is addressable by a 24-bit value from either the 23-bit PC, table instruction Effective Address (EA), or data space EA, when program space is mapped into data space, as defined by Table 3-1. Note that the program space address is incremented by two between successive program words, in order to provide compatibility with data space addressing.

User program space access is restricted to the lower 4M instruction word address range (0x000000 to 0x7FFFFE), for all accesses other than  ${\tt TBLRD/TBLWT}$ , which use TBLPAG<7> to determine user or configuration space access. In Table 3-1, Read/Write instructions, bit 23 allows access to the Device ID, the User ID and the Configuration bits. Otherwise, bit 23 is always clear.

| Note: | The address map shown in Figure 3-1 is |

|-------|----------------------------------------|

|       | conceptual, and the actual memory con- |

|       | figuration may vary across individual  |

|       | devices depending on available memory. |

#### FIGURE 3-1:

#### PROGRAM SPACE MEMORY MAP FOR dsPIC30F1010/202X

(i.e., it defines the page in program space to which the upper half of data space is being mapped).

# 3.2 Data Address Space

The core has two data spaces. The data spaces can be considered either separate (for some DSP instructions), or as one unified linear address range (for MCU instructions). The data spaces are accessed using two Address Generation Units (AGUs) and separate data paths.

# 3.2.1 DATA SPACE MEMORY MAP

The data space memory is split into two blocks, X and Y data space. A key element of this architecture is that Y space is a subset of X space, and is fully contained within X space. In order to provide an apparent linear addressing space, X and Y spaces have contiguous addresses.

When executing any instruction other than one of the MAC class of instructions, the X block consists of the 256 byte data address space (including all Y addresses). When executing one of the MAC class of instructions, the X block consists of the 256 bytes data address space excluding the Y address block (for data reads only). In other words, all other instructions regard the entire data memory as one composite address space. The MAC class instructions extract the Y address space from data space and address it using EAs sourced from W10 and W11. The remaining X data space is addressed using W8 and W9. Both address spaces are concurrently accessed only with the MAC class instructions.

A data space memory map is shown in Figure 3-6.

#### REGISTER 5-6: IEC0: INTERRUPT ENABLE CONTROL REGISTER 0

| REGISTER      |                               | INTERRUPT                                      |                |                  |                  |                 |               |  |  |  |  |  |

|---------------|-------------------------------|------------------------------------------------|----------------|------------------|------------------|-----------------|---------------|--|--|--|--|--|

| U-0           | R/W-0                         | R/W-0                                          | R/W-0          | R/W-0            | R/W-0            | R/W-0           | R/W-0         |  |  |  |  |  |

| —             | MI2CIE                        | SI2CIE                                         | NVMIE          | ADIE             | U1TXIE           | U1RXIE          | SPI1IE        |  |  |  |  |  |

| bit 15        |                               |                                                |                |                  |                  |                 | bit 8         |  |  |  |  |  |

| R/W-0         | R/W-0                         | R/W-0                                          | U-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0         |  |  |  |  |  |

| T3IE          | T2IE                          | OC2IE                                          | —              | T1IE             | OC1IE            | IC1IE           | <b>INTOIE</b> |  |  |  |  |  |

| bit 7         |                               |                                                |                |                  | •                |                 | bit 0         |  |  |  |  |  |

| Legend:       |                               |                                                |                |                  |                  |                 |               |  |  |  |  |  |

| R = Readable  | e bit                         | W = Writable                                   | bit            | U = Unimplei     | mented bit, read | d as '0'        |               |  |  |  |  |  |

| -n = Value at | POR                           | '1' = Bit is set                               | 1              | '0' = Bit is cle |                  | x = Bit is unkr | iown          |  |  |  |  |  |

|               |                               |                                                |                |                  |                  |                 |               |  |  |  |  |  |

| bit 15        | Unimplemen                    | nted: Read as '                                | 0'             |                  |                  |                 |               |  |  |  |  |  |

| bit 14        | MI2CIE: I <sup>2</sup> C I    | Master Events                                  | Interrupt Enal | ole bit          |                  |                 |               |  |  |  |  |  |

|               |                               | request enable<br>request not en               |                |                  |                  |                 |               |  |  |  |  |  |

| bit 13        |                               | Slave Events Ir                                |                | e bit            |                  |                 |               |  |  |  |  |  |

|               |                               | request enable                                 |                |                  |                  |                 |               |  |  |  |  |  |

|               | 0 = Interrupt                 | request not en                                 | abled          |                  |                  |                 |               |  |  |  |  |  |

| bit 12        |                               | volatile Memor                                 | •              | able bit         |                  |                 |               |  |  |  |  |  |

|               |                               | request enable<br>request not er               |                |                  |                  |                 |               |  |  |  |  |  |

| bit 11        | ADIE: ADC C                   | Conversion Cor                                 | nplete Interru | ot Enable bit    |                  |                 |               |  |  |  |  |  |

|               |                               | request enable<br>request not en               |                |                  |                  |                 |               |  |  |  |  |  |

| bit 10        | -                             | U1TXIE: UART1 Transmitter Interrupt Enable bit |                |                  |                  |                 |               |  |  |  |  |  |

|               |                               | request enable<br>request not en               |                |                  |                  |                 |               |  |  |  |  |  |

| bit 9         | -                             | RT1 Receiver I                                 |                | le bit           |                  |                 |               |  |  |  |  |  |

|               |                               | request enable<br>request not en               |                |                  |                  |                 |               |  |  |  |  |  |

| bit 8         | •                             | Event Interrup                                 |                |                  |                  |                 |               |  |  |  |  |  |

|               | 1 = Interrupt request enabled |                                                |                |                  |                  |                 |               |  |  |  |  |  |

|               | 0 = Interrupt                 | request not en                                 | abled          |                  |                  |                 |               |  |  |  |  |  |

| bit 7         |                               | T3IE: Timer3 Interrupt Enable bit              |                |                  |                  |                 |               |  |  |  |  |  |

|               |                               | request enable<br>request not en               |                |                  |                  |                 |               |  |  |  |  |  |

| bit 6         | T2IE: Timer2                  | Interrupt Enab                                 | le bit         |                  |                  |                 |               |  |  |  |  |  |

|               |                               | request enable                                 |                |                  |                  |                 |               |  |  |  |  |  |

|               | -                             | request not en                                 |                |                  |                  |                 |               |  |  |  |  |  |

| bit 5         | •                             | ut Compare Ch                                  |                | upt Enable bit   |                  |                 |               |  |  |  |  |  |

|               |                               | request enable<br>request not en               |                |                  |                  |                 |               |  |  |  |  |  |

| bit 4         |                               | ited: Read as '                                |                |                  |                  |                 |               |  |  |  |  |  |

| bit 3         | -                             | Interrupt Enab                                 |                |                  |                  |                 |               |  |  |  |  |  |

|               | 1 = Interrupt                 | request enable<br>request not en               | ed             |                  |                  |                 |               |  |  |  |  |  |

|               | 1                             | •                                              |                |                  |                  |                 |               |  |  |  |  |  |

# REGISTER 5-6: IEC0: INTERRUPT ENABLE CONTROL REGISTER 0 (CONTINUED)

| bit 2 | <b>OC1IE:</b> Output Compare Channel 1 Interrupt Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled             |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| bit 1 | IC1IE: Input Capture Channel 1 Interrupt Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled                     |

| bit 0 | <ul> <li>INTOIE: External Interrupt 0 Enable bit</li> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> </ul> |

# dsPIC30F1010/202X

| <b>REGISTER 5</b> | 5-7: IEC1:                                                                                               | INTERRUPT                                   | ENABLE C        | ONTROL RE               | GISTER 1         |                 |        |  |  |  |  |  |

|-------------------|----------------------------------------------------------------------------------------------------------|---------------------------------------------|-----------------|-------------------------|------------------|-----------------|--------|--|--|--|--|--|

| R/W-0             | R/W-0                                                                                                    | R/W-0                                       | U-0             | R/W-0                   | U-0              | U-0             | U-0    |  |  |  |  |  |

| AC3IE             | AC2IE                                                                                                    | AC1IE                                       |                 | CNIE                    |                  | —               |        |  |  |  |  |  |

| bit 15            |                                                                                                          |                                             |                 |                         |                  |                 | bit 8  |  |  |  |  |  |

|                   |                                                                                                          |                                             |                 |                         |                  |                 |        |  |  |  |  |  |

| U-0               | R/W-0                                                                                                    | R/W-0                                       | R/W-0           | R/W-0                   | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |  |

| _                 | PWM4IE                                                                                                   | PWM3IE                                      | PWM2IE          | PWM1IE                  | PSEMIE           | INT2IE          | INT1IE |  |  |  |  |  |

| bit 7             |                                                                                                          |                                             |                 |                         |                  |                 | bit 0  |  |  |  |  |  |

| Legend:           |                                                                                                          |                                             |                 |                         |                  |                 |        |  |  |  |  |  |

| R = Readable      | bit                                                                                                      | W = Writable                                | hit             | II – I Inimplei         | mented bit, read | d as '0'        |        |  |  |  |  |  |

| -n = Value at     |                                                                                                          | '1' = Bit is set                            |                 | $0^{\circ} = 0^{\circ}$ |                  | x = Bit is unkr | own    |  |  |  |  |  |

|                   |                                                                                                          |                                             |                 |                         |                  |                 |        |  |  |  |  |  |

| bit 15            | AC3IE: Anal                                                                                              | og Comparator                               | #3 Interrupt E  | nable bit               |                  |                 |        |  |  |  |  |  |

|                   |                                                                                                          | t request enable                            | -               |                         |                  |                 |        |  |  |  |  |  |

|                   | •                                                                                                        | t request not en                            |                 |                         |                  |                 |        |  |  |  |  |  |

| bit 14            |                                                                                                          | og Comparator                               | -               | nable bit               |                  |                 |        |  |  |  |  |  |

|                   |                                                                                                          | t request enable<br>t request not en        |                 |                         |                  |                 |        |  |  |  |  |  |

| bit 13            | •                                                                                                        | og Comparator                               |                 | nahle hit               |                  |                 |        |  |  |  |  |  |

| bit fo            |                                                                                                          | t request enable                            | -               |                         |                  |                 |        |  |  |  |  |  |

|                   | •                                                                                                        | t request not en                            |                 |                         |                  |                 |        |  |  |  |  |  |

| bit 12            | Unimplemer                                                                                               | nted: Read as '                             | 0'              |                         |                  |                 |        |  |  |  |  |  |

| bit 11            | CNIE: Input                                                                                              | Change Notifica                             | ation Interrupt | Enable bit              |                  |                 |        |  |  |  |  |  |

|                   | •                                                                                                        | t request enable                            |                 |                         |                  |                 |        |  |  |  |  |  |

| bit 10-7          | -                                                                                                        | t request not en<br>n <b>ted:</b> Read as ' |                 |                         |                  |                 |        |  |  |  |  |  |

| bit 6             | -                                                                                                        | Ilse Width Modu                             |                 | ator #4 Interrun        | ot Enable bit    |                 |        |  |  |  |  |  |

| Sit o             |                                                                                                          | t request enable                            |                 |                         |                  |                 |        |  |  |  |  |  |

|                   | •                                                                                                        | t request not en                            |                 |                         |                  |                 |        |  |  |  |  |  |

| bit 5             | PWM3IE: Pulse Width Modulation Generator #3 Interrupt Enable bit                                         |                                             |                 |                         |                  |                 |        |  |  |  |  |  |

|                   | <ul> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> </ul>             |                                             |                 |                         |                  |                 |        |  |  |  |  |  |

| bit 1             |                                                                                                          | •                                           |                 | tor #2 Interrup         | t Enchla hit     |                 |        |  |  |  |  |  |

| bit 4             | <b>PWM2IE:</b> Pulse Width Modulation Generator #2 Interrupt Enable bit<br>1 = Interrupt request enabled |                                             |                 |                         |                  |                 |        |  |  |  |  |  |

|                   |                                                                                                          | t request not en                            |                 |                         |                  |                 |        |  |  |  |  |  |

| bit 3             | PWM1IE: Pu                                                                                               | Ise Width Modu                              | lation Genera   | ator #1 Interrup        | ot Enable bit    |                 |        |  |  |  |  |  |

|                   |                                                                                                          | t request enable                            |                 |                         |                  |                 |        |  |  |  |  |  |

|                   | -                                                                                                        | t request not en                            |                 |                         |                  |                 |        |  |  |  |  |  |

| bit 2             |                                                                                                          | VM Special Eve                              |                 | rupt Enable bi          | t                |                 |        |  |  |  |  |  |

|                   |                                                                                                          | t request enable<br>t request not en        |                 |                         |                  |                 |        |  |  |  |  |  |

| bit 1             |                                                                                                          | ernal Interrupt 2                           |                 |                         |                  |                 |        |  |  |  |  |  |

|                   |                                                                                                          | t request enable                            |                 |                         |                  |                 |        |  |  |  |  |  |

|                   | -                                                                                                        | t request not en                            |                 |                         |                  |                 |        |  |  |  |  |  |

| bit 0             |                                                                                                          | ernal Interrupt 1                           |                 |                         |                  |                 |        |  |  |  |  |  |

|                   |                                                                                                          | t request enable<br>t request not en        |                 |                         |                  |                 |        |  |  |  |  |  |

|                   |                                                                                                          | request not en                              |                 |                         |                  |                 |        |  |  |  |  |  |

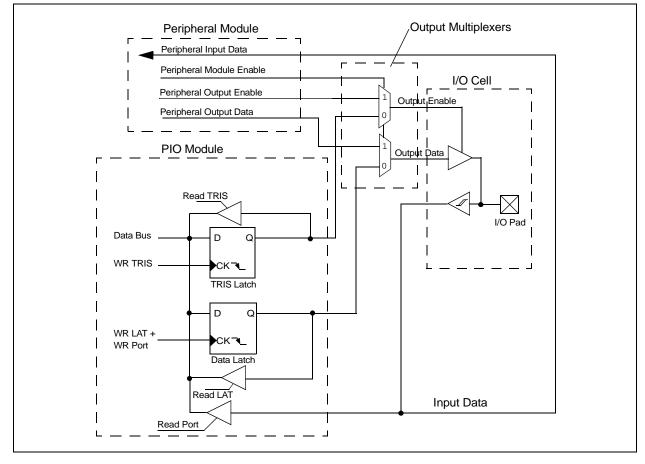

# 6.0 I/O PORTS

**Note:** This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "*dsPIC30F Family Reference Manual*" (DS70046).

All of the device pins (except VDD, VSS, MCLR and OSC1/CLKI) are shared between the peripherals and the parallel I/O ports.

All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

# 6.1 Parallel I/O (PIO) Ports

When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin may be read, but the output driver for the parallel port bit will be disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin may be driven by a port.

All port pins have three registers directly associated with the operation of the port pin. The data direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin

is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx), read the latch. Writes to the latch, write the latch (LATx). Reads from the port (PORTx), read the port pins, and writes to the port pins, write the latch (LATx).

Any bit and its associated data and control registers that are not valid for a particular device will be disabled. That means the corresponding LATx and TRISx registers and the port pin will read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs.

A Parallel I/O (PIO) port that shares a pin with a peripheral is, in general, subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pad cell. Figure 6-1 shows how ports are shared with other peripherals, and the associated I/O cell (pad) to which they are connected. Table 6-1 and Table 6-2 show the register formats for the shared ports, PORTA through PORTF, for the dsPIC30F1010/2020 and PORTA through PORTG for the dsPIC30F2023 device, respectively.

#### FIGURE 6-1: BLOCK DIAGRAM OF A SHARED PORT STRUCTURE

# REGISTER 12-12: FCLCONx: PWM FAULT CURRENT-LIMIT CONTROL REGISTER (CONTINUED)

| bit 6-3 | FLTSRC<3:0>: Fault Control Signal Source Select for PWM Generator #X bits<br>0000 = Analog Comparator #1<br>0001 = Analog Comparator #2<br>0010 = Analog Comparator #3<br>0011 = Analog Comparator #4                                                               |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 0100 = Reserved<br>0101 = Reserved<br>0110 = Reserved<br>0111 = Reserved                                                                                                                                                                                            |

|         | 1000 =         Shared Fault #1 (SFLT1)           1001 =         Shared Fault #2 (SFLT2)           1020 =         Shared Fault #3 (SFLT3)           1011 =         Shared Fault #4 (SFLT4)                                                                           |

|         | <ul> <li>1100 = Reserved</li> <li>1101 = Independent Fault #2 (IFLT2)</li> <li>1110 = Reserved</li> <li>1111 = Independent Fault #4 (IFLT4)</li> </ul>                                                                                                              |

| bit 2   | <b>FLTPOL:</b> Fault Polarity for PWM Generator #X bit<br>1 = The selected Fault source is low active<br>0 = The selected Fault source is high active                                                                                                               |

| bit 1-0 | <b>FLTMOD&lt;1:0&gt;:</b> Fault Mode for PWM Generator #x bits<br>00 = The selected Fault source forces PWMxH, PWMxL pins to FLTDAT values (latched condition)<br>01 = The selected Fault source forces PWMxH, PWMxL pins to FLTDAT values (cycle)<br>10 = Reserved |

11 = Fault input is disabled

| R/W-0                      | R/W-0                                                                                                     | R/W-0                                                                                                                       | R/W-0                                                                                       | R/W-0                                                   | R/W-0            | R/W-0              | R/W-0 |  |

|----------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------|------------------|--------------------|-------|--|

| PHR                        | PHF                                                                                                       | PLR                                                                                                                         | PLF                                                                                         | FLTLEBEN                                                | CLLEBEN          | LEB<               | :9:8> |  |

| bit 15                     |                                                                                                           |                                                                                                                             |                                                                                             |                                                         |                  |                    | bit   |  |

| R/W-0                      | R/W-0                                                                                                     | R/W-0                                                                                                                       | R/W-0                                                                                       | R/W-0                                                   | U-0              | U-0                | U-0   |  |

|                            |                                                                                                           | LEB<7:3>                                                                                                                    |                                                                                             |                                                         |                  | —                  | _     |  |

| bit 7                      |                                                                                                           |                                                                                                                             |                                                                                             |                                                         |                  |                    | bit   |  |

| Legend:                    |                                                                                                           |                                                                                                                             |                                                                                             |                                                         |                  |                    |       |  |

| R = Readabl                | le bit                                                                                                    | W = Writable                                                                                                                | bit                                                                                         | U = Unimplen                                            | nented bit, read | d as '0'           |       |  |

| -n = Value at POR          |                                                                                                           | '1' = Bit is set                                                                                                            |                                                                                             | '0' = Bit is clea                                       | ared             | x = Bit is unknown |       |  |

| bit 14<br>bit 13<br>bit 12 | 1 = Falling ec<br>0 = LEB ignor<br><b>PLR:</b> PWML<br>1 = Rising ed<br>0 = LEB ignor<br><b>PLF:</b> PWML | Falling Edge T<br>lge of PWMH v<br>res falling edge<br>Rising Edge Tr<br>ge of PWML w<br>res rising edge<br>Falling Edge Tr | vill trigger LEI<br>e of PWMH<br>igger Enable<br>ill trigger LEE<br>of PWML<br>igger Enable | B counter<br>bit<br>3 counter<br>bit                    |                  |                    |       |  |

| bit 11                     | 0 = LEB igno                                                                                              | lge of PWML w<br>res falling edge                                                                                           | of PWML                                                                                     | 3 counter<br>anking Enable b                            |                  |                    |       |  |

| bit II                     | 1 = Leading E                                                                                             | Edge Blanking i                                                                                                             | s applied to s                                                                              | selected Fault Ir                                       | nput             |                    |       |  |

| bit 10                     | 1 = Leading E                                                                                             | Edge Blanking i                                                                                                             | s applied to s                                                                              | Blanking Enable<br>selected Current<br>to selected Curr | t-Limit Input    |                    |       |  |

| bit 9-3                    | <b>LEB:</b> Leading<br>Value is 8 nse                                                                     |                                                                                                                             | g for Current-                                                                              | Limit and Fault                                         | Inputs bits      |                    |       |  |

|                            |                                                                                                           | ec increments                                                                                                               |                                                                                             |                                                         |                  |                    |       |  |

#### REGISTER 12-14: LEBCONX: LEADING EDGE BLANKING CONTROL REGISTER

# dsPIC30F1010/202X

| R/W-0                      | R/W-0                                                                                | R/W-0                                                                                                                            | U-0                                                                          | U-0                | U-0             | U-0                | U-0   |  |

|----------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--------------------|-----------------|--------------------|-------|--|

| FRMEN                      | SPIFSD                                                                               | FRMPOL                                                                                                                           | —                                                                            | —                  | —               | —                  | _     |  |

| bit 15                     |                                                                                      |                                                                                                                                  |                                                                              |                    |                 |                    | bit 8 |  |

|                            |                                                                                      |                                                                                                                                  |                                                                              |                    |                 |                    |       |  |

| U-0                        | U-0                                                                                  | U-0                                                                                                                              | U-0                                                                          | U-0                | U-0             | R/W-0              | U-0   |  |

| _                          | _                                                                                    |                                                                                                                                  | —                                                                            |                    | —               | FRMDLY             | —     |  |

| bit 7                      |                                                                                      |                                                                                                                                  |                                                                              |                    |                 |                    | bit 0 |  |

|                            |                                                                                      |                                                                                                                                  |                                                                              |                    |                 |                    |       |  |

| Legend:                    |                                                                                      |                                                                                                                                  |                                                                              |                    |                 |                    |       |  |

| R = Readable               | e bit                                                                                | W = Writable                                                                                                                     | bit                                                                          | U = Unimpler       | nented bit, rea | d as '0'           |       |  |

| -n = Value at              | POR                                                                                  | '1' = Bit is set                                                                                                                 |                                                                              | '0' = Bit is cle   | ared            | x = Bit is unknown |       |  |

| bit 15<br>bit 14<br>bit 13 | 1 = Framed S<br>0 = Framed S<br><b>SPIFSD</b> : Frar<br>1 = Frame sy<br>0 = Frame sy | med SPIx Supp<br>SPIx support en<br>SPIx support dis<br>me Sync Pulse<br>inc pulse input (<br>inc pulse output<br>ame Sync Pulse | abled ( <del>SSx</del> p<br>sabled<br>Direction Cor<br>(slave)<br>t (master) |                    | ie sync pulse i | nput/output)       |       |  |

|                            | 1 = Frame sy                                                                         | nc pulse is acti<br>nc pulse is acti                                                                                             | ve-high                                                                      |                    |                 |                    |       |  |

| bit 12-2                   | Unimplemen                                                                           | ted: Read as '                                                                                                                   | כ'                                                                           |                    |                 |                    |       |  |

| bit 1                      | 1 = Frame sy                                                                         | ame Sync Pulse<br>nc pulse coinci<br>nc pulse prece                                                                              | des with first                                                               | bit clock          |                 |                    |       |  |

| bit 0                      | Unimplemen                                                                           | ited: This bit m                                                                                                                 | ust not be set                                                               | t to '1' by the us | ser application |                    |       |  |

|                            |                                                                                      |                                                                                                                                  |                                                                              |                    |                 |                    |       |  |

#### REGISTER 13-3: SPIxCON2: SPIx CONTROL REGISTER 2

### TABLE 15-1: UART1 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15   | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8      | Bit 7        | Bit 6  | Bit 5 | Bit 4       | Bit 3  | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|----------|-------------|----------|--------|----------|--------|--------|--------|-------|------------|--------------|--------|-------|-------------|--------|-------|--------|-------|---------------|

| U1MODE   | 0220        | UARTEN   | —      | USIDL    | IREN   | —      | ALTIO  | _     | _          | WAKE         | LPBACK | ABAUD | RXINV       | BRGH   | PDSEI | L<1:0> | STSEL | 0000          |

| U1STA    | 0222        | UTXISEL1 | UTXINV | UTXISEL0 |        | UTXBRK | UTXEN  | UTXBF | TRMT       | URXISE       | L<1:0> | ADDEN | RIDLE       | PERR   | FERR  | OERR   | URXDA | 0110          |

| U1TXREG  | 0224        | _        | _      | _        |        | _      |        |       |            |              |        | UART  | Fransmit Re | gister |       |        |       | xxxx          |

| U1RXREG  | 0226        | _        | _      | —        | _      | _      | _      | _     |            |              |        | UART  | Receive Re  | gister |       |        |       | 0000          |

| U1BRG    | 0228        |          |        |          |        |        |        | Bau   | d Rate Ger | erator Presc | aler   |       |             |        |       |        |       | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# REGISTER 16-6: A/D CONVERT PAIR CONTROL REGISTER 1 (ADCPC1)

| IRQEN3         PEND3         SWTRG3         TRGSRC3<4:0>           bit 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | bit a<br>R/W-0                |  |  |  |  |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--|--|--|--|--|--|--|--|--|--|

| R/W-0         R/W-0         R/W-0         R/W-0         R/W-0         R/W-0         R/W-0         R/W-0         IRQEN2         PEND2         SWTRG2         TRGSRC2<4:0>         TRGSRC2<4:0>         IRDE         IRDE |                               |  |  |  |  |  |  |  |  |  |  |

| IRQEN2 PEND2 SWTRG2 TRGSRC2<4:0><br>bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R/W-0                         |  |  |  |  |  |  |  |  |  |  |

| IRQEN2 PEND2 SWTRG2 TRGSRC2<4:0><br>bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | K/VV-U                        |  |  |  |  |  |  |  |  |  |  |

| bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                               |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit                           |  |  |  |  |  |  |  |  |  |  |

| Legend:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                               |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                               |  |  |  |  |  |  |  |  |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                               |  |  |  |  |  |  |  |  |  |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | IOWN                          |  |  |  |  |  |  |  |  |  |  |

| hit 15 IDOEN2: Interrupt Degradet Enchle 2 hit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                               |  |  |  |  |  |  |  |  |  |  |

| bit 15 <b>IRQEN3:</b> Interrupt Request Enable 3 bit<br>1 = Enable IRQ generation when requested conversion of channels AN7 and AN6 is ca                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ompleted                      |  |  |  |  |  |  |  |  |  |  |

| 0 = IRQ is not generated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | mpieteu.                      |  |  |  |  |  |  |  |  |  |  |

| bit 14 PEND3: Pending Conversion Status 3 bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                               |  |  |  |  |  |  |  |  |  |  |

| 1 = Conversion of channels AN7 and AN6 is pending. Set when selected trigger is ass                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | erted.                        |  |  |  |  |  |  |  |  |  |  |

| 0 = Conversion is complete<br>bit 13 SWTRG3: Software Trigger 3 bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                               |  |  |  |  |  |  |  |  |  |  |

| 1 = Start conversion of AN7 and AN6 (if selected by TRGSRC bits). If other conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | is are in                     |  |  |  |  |  |  |  |  |  |  |

| progress, then conversion will be performed when the conversion resources are availab                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                               |  |  |  |  |  |  |  |  |  |  |

| be reset when the PEND bit is set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                               |  |  |  |  |  |  |  |  |  |  |