# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | dsPIC                                                                         |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 20 MIPS                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                         |

| Number of I/O              | 21                                                                            |

| Program Memory Size        | 12KB (4K x 24)                                                                |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 512 x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                     |

| Data Converters            | A/D 8x10b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Through Hole                                                                  |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                       |

| Supplier Device Package    | 28-SPDIP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f2020-20e-sp |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

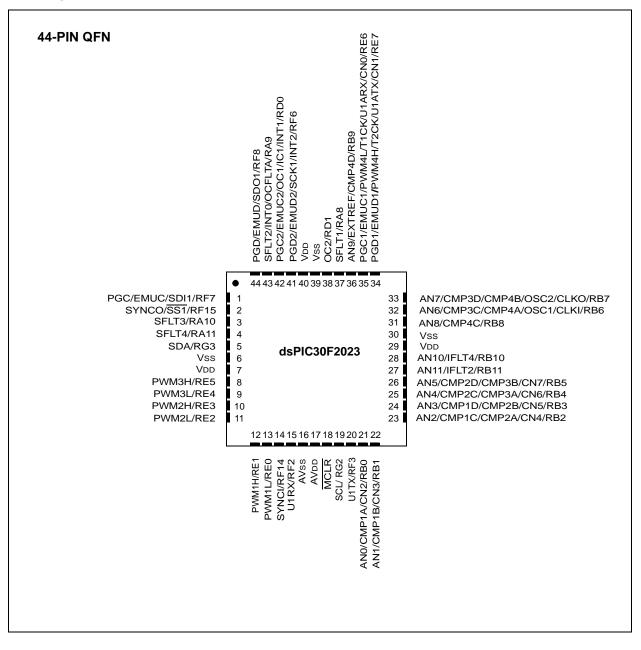

#### **Pin Diagrams**

| Pin Name       |               | Pin<br>Type | Buffer<br>Type   | Description                                                                                              |

|----------------|---------------|-------------|------------------|----------------------------------------------------------------------------------------------------------|

| RB0-RB7        | $\rightarrow$ | 1/0         | ST               | PORTB is a bidirectional I/O port.                                                                       |

| RA9            |               | I/O         | ST               | PORTA is a bidirectional I/O port.                                                                       |

| RD0            |               | I/O         | ST               | PORTD is a bidirectional I/O port.                                                                       |

| RE0-RE7        |               | 1/O         | ST               | PORTE is a bidirectional I/O port.                                                                       |

| RF6, RF7, RF   | -0            | I/O         | ST               | PORTF is a bidirectional I/O port.                                                                       |

|                | -0            |             |                  |                                                                                                          |

| SCK1<br>SDI1   |               | I/O         | ST<br>ST         | Synchronous serial clock input/output for SPI #1.                                                        |

| SD01           |               | I<br>O      | 51               | SPI #1 Data In.<br>SPI #1 Data Out.                                                                      |

| SCL            |               | 1/0         | ST               | Synchronous serial clock input/output for I <sup>2</sup> C <sup>™</sup> .                                |

| SDA            |               | 1/O<br>1/O  | ST               | Synchronous serial data input/output for $I^2C$ .                                                        |

|                |               |             |                  |                                                                                                          |

| T1CK<br>T2CK   |               | I           | ST<br>ST         | Timer1 external clock input.<br>Timer2 external clock input.                                             |

|                |               | -           |                  |                                                                                                          |

| U1RX           |               |             | ST               | UART1 Receive.                                                                                           |

| U1TX<br>U1ARX  |               | 0           | —<br>ST          | UART1 Transmit.<br>Alternate UART1 Receive.                                                              |

| UTARX          |               | 0           | 0                | Alternate UART1 Transmit.                                                                                |

|                |               |             | -                |                                                                                                          |

| CMP1A          |               |             | Analog           | Comparator 1 Channel A                                                                                   |

| CMP1B<br>CMP1C |               | I           | Analog           | Comparator 1 Channel B<br>Comparator 1 Channel C                                                         |

| CMP1D          |               | I           | Analog<br>Analog | Comparator 1 Channel D                                                                                   |

| CMP2A          |               | 1           | Analog           | Comparator 2 Channel A                                                                                   |

| CMP2B          |               | I           | Analog           | Comparator 2 Channel B                                                                                   |

| CMP2C          |               | I           | Analog           | Comparator 2 Channel C                                                                                   |

| CMP2D          |               | i           | Analog           | Comparator 2 Channel D                                                                                   |

| CMP3A          |               | Ì           | Analog           | Comparator 3 Channel A                                                                                   |

| CMP3B          |               | I           | Analog           | Comparator 3 Channel B                                                                                   |

| CMP3C          |               | I           | Analog           | Comparator 3 Channel C                                                                                   |

| CMP3D          |               | I           | Analog           | Comparator 3 Channel D                                                                                   |

| CMP4A          |               | Ι           | Analog           | Comparator 4 Channel A                                                                                   |

| CMP4B          |               | I           | Analog           | Comparator 4 Channel B                                                                                   |

| CN0-CN7        |               | Ι           | ST               | Input Change notification inputs<br>Can be software programmed for internal weak pull-ups on all inputs. |

| Vdd            |               | Р           | —                | Positive supply for logic and I/O pins.                                                                  |

| Vss            |               | Р           | —                | Ground reference for logic and I/O pins.                                                                 |

| EXTREF         |               | I           | Analog           | External reference to Comparator DAC                                                                     |

| Legend: CN     | NOS           | = (         | CMOS compa       | atible input or output Analog = Analog input                                                             |

| ST             |               |             |                  | er input with CMOS levels O = Output                                                                     |

| I              |               |             | nput             | P = Power                                                                                                |

TABLE 1-2: PINOUT I/O DESCRIPTIONS FOR dsPIC30F2020 (CONTINUED)

### 3.2.2 DATA SPACES

The X data space is used by all instructions and supports all Addressing modes. There are separate read and write data buses. The X read data bus is the return data path for all instructions that view data space as combined X and Y address space. It is also the X address space data path for the dual operand read instructions (MAC class). The X write data bus is the only write path to data space for all instructions.

The X data space also supports modulo addressing for all instructions, subject to Addressing mode restrictions. Bit-Reversed Addressing is only supported for writes to X data space.

The Y data space is used in concert with the X data space by the MAC class of instructions (CLR, ED, EDAC, MAC, MOVSAC, MPY, MPY.N and MSC) to provide two concurrent data read paths. No writes occur across the Y bus. This class of instructions dedicates two W register pointers, W10 and W11, to always address Y data space, independent of X data space, whereas W8 and W9 always address X data space. Note that during accumulator write back, the data address space is considered a combination of X and Y data spaces, so the write occurs across the X bus. Consequently, the write can be to any address in the entire data space.

The Y data space can only be used for the data prefetch operation associated with the MAC class of instructions. It also supports modulo addressing for automated circular buffers. Of course, all other instructions can access the Y data address space through the X data path, as part of the composite linear space.

The boundary between the X and Y data spaces is defined as shown in Figure 3-6 and is not user programmable. Should an EA point to data outside its own assigned address space, or to a location outside physical memory, an all-zero word/byte will be returned. For example, although Y address space is visible by all non-MAC instructions using any Addressing mode, an attempt by a MAC instruction to fetch data from that space, using W8 or W9 (X space pointers), will return 0x0000.

#### TABLE 3-2: EFFECT OF INVALID MEMORY ACCESSES

| Attempted Operation                                         | Data Returned |

|-------------------------------------------------------------|---------------|

| EA = an unimplemented address                               | 0x0000        |

| W8 or W9 used to access Y data space in a MAC instruction   | 0x0000        |

| W10 or W11 used to access X data space in a MAC instruction | 0x0000        |

All effective addresses are 16 bits wide and point to bytes within the data space. Therefore, the data space address range is 64 Kbytes or 32K words.

### 3.2.3 DATA SPACE WIDTH

The core data width is 16 bits. All internal registers are organized as 16-bit wide words. Data space memory is organized in byte addressable, 16-bit wide blocks.

### 3.2.4 DATA ALIGNMENT

To help maintain backward compatibility with PIC® MCU devices and improve data space memory usage efficiency, the dsPIC30F instruction set supports both word and byte operations. Data is aligned in data memory and registers as words, but all data space EAs resolve to bytes. Data byte reads will read the complete word, which contains the byte, using the LSb of any EA to determine which byte to select. The selected byte is placed onto the LSB of the X data path (no byte accesses are possible from the Y data path as the MAC class of instruction can only fetch words). That is, data memory and registers are organized as two parallel byte-wide entities with shared (word) address decode, but separate write lines. Data byte writes only write to the corresponding side of the array or register which matches the byte address.

As a consequence of this byte accessibility, all effective address calculations (including those generated by the DSP operations, which are restricted to word sized data) are internally scaled to step through word-aligned memory. For example, the core would recognize that Post-Modified Register Indirect Addressing mode, [Ws++], will result in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. Should a misaligned read or write be attempted, an address error trap will be generated. If the error occurred on a read, the instruction underway is completed, whereas if it occurred on a write, the instruction will be executed but the write will not occur. In either case, a trap will then be executed, allowing the system and/or user to examine the machine state prior to execution of the address fault.

#### FIGURE 3-8: DATA ALIGNMENT

| ,    | 15 <b>MSB</b> | 8 7 | LSB    | 0 |      |

|------|---------------|-----|--------|---|------|

| 0001 | Byte 1        |     | Byte 0 |   | 0000 |

| 0003 | Byte 3        |     | Byte 2 |   | 0002 |

| 0005 | Byte 5        |     | Byte 4 |   | 0004 |

| U-0          | R/W-0                      | R/W-0                            | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

|--------------|----------------------------|----------------------------------|------------------|------------------|------------------|-----------------|--------|

|              | MI2CIF                     | SI2CIF                           | NVMIF            | ADIF             | U1TXIF           | U1RXIF          | SPI1IF |

| bit 15       |                            |                                  |                  |                  |                  |                 | bit 8  |

|              |                            |                                  |                  |                  |                  | =               |        |

| R/W-0        | R/W-0                      | R/W-0                            | U-0              | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

| T3IF         | T2IF                       | OC2IF                            |                  | T1IF             | OC1IF            | IC1IF           | INTOIF |

| bit 7        |                            |                                  |                  |                  |                  |                 | bit 0  |

| Legend:      |                            |                                  |                  |                  |                  |                 |        |

| R = Readab   | ole bit                    | W = Writable                     | bit              | U = Unimple      | mented bit, read | d as '0'        |        |

| -n = Value a | t POR                      | '1' = Bit is se                  | t                | '0' = Bit is cle |                  | x = Bit is unkr | nown   |

|              |                            |                                  |                  |                  |                  |                 |        |

| bit 15       | Unimplemen                 | ted: Read as                     | '0'              |                  |                  |                 |        |

| bit 14       | MI2CIF: I <sup>2</sup> C M | Master Events                    | Interrupt Flag   | Status bit       |                  |                 |        |

|              |                            | request has o                    |                  |                  |                  |                 |        |

| L: 40        |                            | request has n                    |                  | Matura hit       |                  |                 |        |

| bit 13       |                            | Blave Events Ir<br>request has o |                  | tatus dit        |                  |                 |        |

|              |                            | request has n                    |                  |                  |                  |                 |        |

| bit 12       | NVMIF: Nonv                | olatile Memor                    | y Interrupt Flag | g Status bit     |                  |                 |        |

|              |                            | request has o                    |                  |                  |                  |                 |        |

|              | -                          | request has n                    |                  |                  |                  |                 |        |

| bit 11       |                            |                                  |                  | ot Flag Status b | bit              |                 |        |

|              |                            | request has o request has n      |                  |                  |                  |                 |        |

| bit 10       | -                          | RT1 Transmitte                   |                  | a Status bit     |                  |                 |        |

|              |                            | request has o                    | -                | 9                |                  |                 |        |

|              | 0 = Interrupt              | request has n                    | ot occurred      |                  |                  |                 |        |

| bit 9        |                            | RT1 Receiver I                   |                  | Status bit       |                  |                 |        |

|              |                            | request has o request has n      |                  |                  |                  |                 |        |

| bit 8        | •                          | Event Interrup                   |                  | bit              |                  |                 |        |

|              |                            | request has o                    | -                |                  |                  |                 |        |

|              | -                          | request has n                    |                  |                  |                  |                 |        |

| bit 7        |                            | Interrupt Flag                   |                  |                  |                  |                 |        |

|              |                            | request has o<br>request has n   |                  |                  |                  |                 |        |

| bit 6        | -                          | Interrupt Flag                   |                  |                  |                  |                 |        |

|              |                            | request has o                    |                  |                  |                  |                 |        |

|              | 0 = Interrupt              | request has n                    | ot occurred      |                  |                  |                 |        |

| bit 5        | OC2IF: Outpu               | ut Compare Cl                    | nannel 2 Interr  | upt Flag Status  | s bit            |                 |        |

|              |                            | request has o                    |                  |                  |                  |                 |        |

| L:+ 4        | •                          | request has n                    |                  |                  |                  |                 |        |

| bit 4        | -                          | ted: Read as                     |                  |                  |                  |                 |        |

| bit 3        |                            | Interrupt Flag                   |                  |                  |                  |                 |        |

|              |                            | request has o<br>request has n   |                  |                  |                  |                 |        |

|              | ·- ·F·                     |                                  |                  |                  |                  |                 |        |

#### REGISTER 5-3: IFS0: INTERRUPT FLAG STATUS REGISTER 0

## TABLE 6-2: dsPIC30F2023 PORT REGISTER MAP

| SFR<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13 | Bit<br>12 | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset State         |

|-------------|-------|---------|---------|--------|-----------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------------|

| TRISA       | 02C0  | _       |         | —      |           | TRISA11 | TRISA10 | TRIS9  | TRISA8 |        |        |        | _      | _      |        | _      | _      | 0000 1111 0000 0000 |

| PORTA       | 02C2  | _       |         | _      | ١         | RA11    | RA10    | RA9    | RA8    | I      | ١      |        | _      | -      |        | _      | _      | 0000 0000 0000 0000 |

| LATA        | 02C4  | _       |         | -      | ١         | LATA11  | LATA10  | LATA9  | LATA8  | I      | ١      |        | _      | -      |        | _      | _      | 0000 0000 0000 0000 |

| TRISB       | 02C6  |         |         | _      |           | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRIS6  | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | 0000 1111 1111 1111 |

| PORTB       | 02C8  | _       |         | _      |           | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | 0000 0000 0000 0000 |

| LATB        | 02CA  | _       |         | -      | ١         | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | 0000 0000 0000 0000 |

| TRISD       | 02D2  |         |         | _      |           | _       |         |        | _      |        |        | _      | _      | _      | _      | TRISD1 | TRISD0 | 0000 0000 0000 001  |

| PORTD       | 02D4  |         | _       | -      | _         | _       | _       | _      | _      | _      | _      | _      | _      | _      | _      | RD1    | RD0    | 0000 0000 0000 0000 |

| LATD        | 02D6  | _       |         | -      | ١         |         |         | ١      | _      | I      | ١      |        | _      | -      |        | LATD1  | LATD0  | 0000 0000 0000 0000 |

| TRISE       | 02D8  |         |         | _      |           | _       |         |        | _      | TRSE7  | TRSE6  | TRISE5 | TRISE4 | TRISE3 | TRISE2 | TRISE1 | TRISE0 | 0000 0000 1111 1113 |

| PORTE       | 02DA  | _       |         | -      | ١         |         |         | ١      | _      | RE7    | RE6    | RE5    | RE4    | RE3    | RE2    | RE1    | RE0    | 0000 0000 0000 0000 |

| LATE        | 02DC  | _       |         | -      | ١         |         |         | ١      | _      | LATE7  | LATE6  | LATE5  | LATE4  | LATE3  | LATE2  | LATE1  | LATE0  | 0000 0000 0000 0000 |

| TRISF       | 02DE  | TRISF15 | TRISF14 | _      |           | _       |         |        | TRISF8 | TRISF7 | TRISF6 | _      | _      | TRISF3 | TRISF2 | _      | _      | 1100 0001 1100 110  |

| PORTF       | 02E0  | RF15    | RF14    | _      | _         | _       | _       | _      | RF8    | RF7    | RF6    | _      | _      | RF3    | RF2    | _      | _      | 0000 0000 0000 000  |

| LATF        | 02E2  | LATF15  | LATF14  | _      | _         | _       | _       | _      | LATF8  | LATF7  | LATF6  | _      | _      | LATF3  | LATF2  | _      | _      | 0000 0000 0000 0000 |

| TRISG       | 02E4  | _       | _       | _      | _         | _       | _       | _      | _      | _      | _      | _      | _      | TRISG3 | TRISG2 | _      | _      | 0000 0000 0000 110  |

| PORTG       | 02E6  | _       |         | _      | _         | _       |         |        | _      | _      |        | _      | _      | RG3    | RG2    | _      | _      | 0000 0000 0000 0000 |

| LATG        | 02E8  | _       |         | _      |           | _       |         |        | _      | _      | _      | _      | _      | LATG3  | LATG2  | _      |        | 0000 0000 0000 0000 |

Note: Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

### TABLE 6-3: dsPIC30F1010/202X INPUT CHANGE NOTIFICATION REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit<br>12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3         | Bit 2  | Bit 1  | Bit 0  | Reset State         |

|-------------|-------|--------|--------|--------|-----------|--------|--------|-------|-------|--------|--------|--------|--------|---------------|--------|--------|--------|---------------------|

| CNEN1       | 0060  | _      | _      | _      | _         |        | _      | _     | -     | CN7IE  | CN6IE  | CN5IE  | CN4IE  | CN3IE         | CN2IE  | CN1IE  | CN0IE  | 0000 0000 0000 0000 |

| CNPU1       | 0064  | _      | 1      | _      | _         |        | _      | _     | _     | CN7PUE | CN6PUE | CN5PUE | CN4PUE | <b>CN3PUE</b> | CN2PUE | CN1PUE | CN0PUE | 0000 0000 0000 0000 |

Note: Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

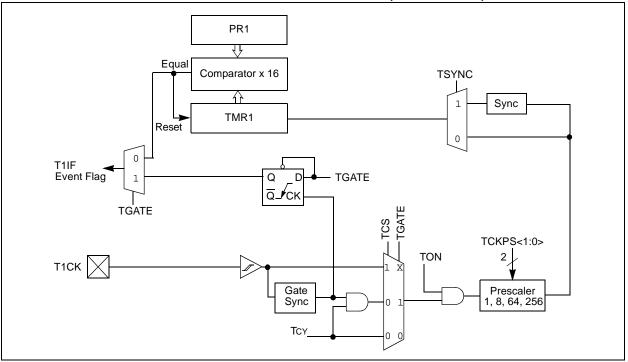

#### FIGURE 8-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM (TYPE A TIMER)

### 8.1 Timer Gate Operation

The 16-bit timer can be placed in the Gated Time Accumulation mode. This mode allows the internal TCY to increment the respective timer when the gate input signal (T1CK pin) is asserted high. Control bit TGATE (T1CON<6>) must be set to enable this mode. The timer must be enabled (TON = 1) and the timer clock source set to internal (TCS = 0).

When the CPU goes into the Idle mode, the timer will stop incrementing, unless TSIDL = 0. If TSIDL = 1, the timer will resume the incrementing sequence upon termination of the CPU Idle mode.

## 8.2 Timer Prescaler

The input clock (Fosc/2 or external clock) to the 16-bit Timer, has a prescale option of 1:1, 1:8, 1:64, and 1:256 selected by control bits TCKPS<1:0> (T1CON<5:4>). The prescaler counter is cleared when any of the following occurs:

- a write to the TMR1 register

- clearing of the TON bit (T1CON<15>)

- device Reset such as POR

However, if the timer is disabled (TON = 0), then the timer prescaler cannot be reset since the prescaler clock is halted.

TMR1 is not cleared when T1CON is written. It is cleared by writing to the TMR1 register.

## 8.3 Timer Operation During Sleep Mode

During CPU Sleep mode, the timer will operate if:

- The timer module is enabled (TON = 1) and

- The timer clock source is selected as external (TCS = 1) and

- The TSYNC bit (T1CON<2>) is asserted to a logic '0', which defines the external clock source as asynchronous

When all three conditions are true, the timer will continue to count up to the period register and be reset to 0x0000.

When a match between the timer and the period register occurs, an interrupt can be generated, if the respective timer interrupt enable bit is asserted.

## 8.4 Timer Interrupt

The 16-bit timer has the ability to generate an interrupt on period match. When the timer count matches the period register, the T1IF bit is asserted and an interrupt will be generated, if enabled. The T1IF bit must be cleared in software. The timer interrupt flag T1IF is located in the IFS0 control register in the Interrupt Controller.

When the Gated Time Accumulation mode is enabled, an interrupt will also be generated on the falling edge of the gate signal (at the end of the accumulation cycle).

Enabling an interrupt is accomplished via the respective timer interrupt enable bit, T1IE. The timer interrupt enable bit is located in the IEC0 control register in the Interrupt Controller.

## 11.1 Timer2 and Timer3 Selection Mode

Each output compare channel can select between one of two 16-bit timers: Timer2 or Timer3.

The selection of the timers is controlled by the OCTSEL bit (OCxCON<3>). Timer2 is the default timer resource for the Output Compare module.

### 11.2 Simple Output Compare Match Mode

When control bits OCM<2:0> (OCxCON<2:0>) = 001, 010 or 011, the selected output compare channel is configured for one of three simple Output Compare Match modes:

- Compare forces I/O pin low

- Compare forces I/O pin high

- Compare toggles I/O pin

The OCxR register is used in these modes. The OCxR register is loaded with a value and is compared to the selected incrementing timer count. When a compare occurs, one of these Compare Match modes occurs. If the counter resets to zero before reaching the value in OCxR, the state of the OCx pin remains unchanged.

## 11.3 Dual Output Compare Match Mode

When control bits OCM<2:0> (OCxCON<2:0>) = 100 or 101, the selected output compare channel is configured for one of two Dual Output Compare modes, which are:

- Single Output Pulse mode

- Continuous Output Pulse mode

#### 11.3.1 SINGLE PULSE MODE

For the user to configure the module for the generation of a single output pulse, the following steps are required (assuming the timer is off):

- Determine instruction cycle time Tcy.

- Calculate desired pulse width value based on TCY.

- Calculate time to start pulse from timer start value of 0x0000.

- Write pulse width start and stop times into OCxR and OCxRS compare registers (x denotes channel 1, 2).

- Set timer period register to value equal to, or greater than, value in OCxRS compare register.

- Set OCM<2:0> = 100.

- Enable timer, TON (TxCON<15>) = 1.

To initiate another single pulse, issue another write to set OCM<2:0> = 100.

#### 11.3.2 CONTINUOUS PULSE MODE

For the user to configure the module for the generation of a continuous stream of output pulses, the following steps are required:

- Determine instruction cycle time Tcy.

- · Calculate desired pulse value based on Tcy.

- Calculate timer to start pulse width from timer start value of 0x0000.

- Write pulse width start and stop times into OCxR and OCxRS (x denotes channel 1, 2) compare registers, respectively.

- Set timer period register to value equal to, or greater than, value in OCxRS compare register.

- Set OCM<2:0> = 101.

- Enable timer, TON (TxCON<15>) = 1.

## 11.4 Simple PWM Mode

When control bits OCM<2:0> (OCxCON<2:0>) = 110 or 111, the selected output compare channel is configured for the PWM mode of operation. When configured for the PWM mode of operation, OCxR is the Main latch (read-only) and OCxRS is the secondary latch. This enables glitchless PWM transitions.

The user must perform the following steps in order to configure the output compare module for PWM operation:

- 1. Set the PWM period by writing to the appropriate period register.

- 2. Set the PWM duty cycle by writing to the OCxRS register.

- 3. Configure the output compare module for PWM operation.

- 4. Set the TMRx prescale value and enable the Timer, TON (TxCON<15>) = 1.

NOTES:

## 14.2 I<sup>2</sup>C Module Addresses

The I2CADD register contains the Slave mode addresses. The register is a 10-bit register.

If the A10M bit (I2CCON<10>) is '0', the address is interpreted by the module as a 7-bit address. When an address is received, it is compared to the 7 Least Significant bits of the I2CADD register.

If the A10M bit is '1', the address is assumed to be a 10-bit address. When an address is received, it will be compared with the binary value '1 1 1 1 0 A9 A8' (where A9, A8 are two Most Significant bits of I2CADD). If that value matches, the next address will be compared with the Least Significant 8 bits of I2CADD, as specified in the 10-bit addressing protocol.

## 14.3 I<sup>2</sup>C 7-bit Slave Mode Operation

Once enabled (I2CEN = 1), the slave module will wait for a Start bit to occur (i.e., the I<sup>2</sup>C module is 'Idle'). Following the detection of a Start bit, 8 bits are shifted into I2CRSR and the address is compared against I2CADD. In 7-bit mode (A10M = 0), bits I2CADD<6:0> are compared against I2CRSR<7:1> and I2CRSR<0> is the R\_W bit. All incoming bits are sampled on the rising edge of SCL.

If an address match occurs, an acknowledgement will be sent, and the slave event interrupt flag (SI2CIF) is set on the falling edge of the ninth ( $\overline{ACK}$ ) bit. The address match does not affect the contents of the I2CRCV buffer or the RBF bit.

#### 14.3.1 SLAVE TRANSMISSION

If the R\_W bit received is a '1', then the serial port will go into Transmit mode. It will send ACK on the ninth bit and then hold SCL to '0' until the CPU responds by writing to I2CTRN. SCL is released by setting the SCLREL bit, and 8 bits of data are shifted out. Data bits are shifted out on the falling edge of SCL, such that SDA is valid during SCL high (see timing diagram). The interrupt pulse is sent on the falling edge of the ninth clock pulse, regardless of the status of the ACK received from the master.

#### 14.3.2 SLAVE RECEPTION

If the R\_W bit received is a '0' during an address match, then Receive mode is initiated. Incoming bits are sampled on the rising edge of SCL. After 8 bits are received, if I2CRCV is not full or I2COV is not set, I2CRSR is transferred to I2CRCV. ACK is sent on the ninth clock.

If the RBF flag is set, indicating that I2CRCV is still holding data from a previous operation (RBF = 1), then  $\overline{ACK}$  is not sent; however, the interrupt pulse is generated. In the case of an overflow, the contents of the I2CRSR are not loaded into the I2CRCV.

| Note: | The I2CRCV will be loaded if the I2COV          |

|-------|-------------------------------------------------|

|       | bit = 1 and the RBF flag = 0. In this case,     |

|       | a read of the I2CRCV was performed, but         |

|       | the user did not clear the state of the         |

|       | I2COV bit before the next receive               |

|       | occurred. The acknowledgement is not            |

|       | sent ( $\overline{ACK} = 1$ ) and the I2CRCV is |

|       | updated.                                        |

## 14.4 I<sup>2</sup>C 10-bit Slave Mode Operation

In 10-bit mode, the basic receive and transmit operations are the same as in the 7-bit mode. However, the criteria for address match is more complex.

The  $I^2C$  specification dictates that a slave must be addressed for a write operation, with two address bytes following a Start bit.

The A10M bit is a control bit that signifies that the address in I2CADD is a 10-bit address rather than a 7-bit address. The address detection protocol for the first byte of a message address is identical for 7-bit and 10-bit messages, but the bits being compared are different.

I2CADD holds the entire 10-bit address. Upon receiving an address following a Start bit, I2CRSR <7:3> is compared against a literal '11110' (the default 10-bit address) and I2CRSR<2:1> are compared against I2CADD<9:8>. If a match occurs and if  $R_W = 0$ , the interrupt pulse is sent. The ADD10 bit will be cleared to indicate a partial address match. If a match fails or  $R_W = 1$ , the ADD10 bit is cleared and the module returns to the Idle state.

The low byte of the address is then received and compared with I2CADD<7:0>. If an address match occurs, the interrupt pulse is generated and the ADD10 bit is set, indicating a complete 10-bit address match. If an address match did not occur, the ADD10 bit is cleared and the module returns to the Idle state.

#### 14.4.1 10-BIT MODE SLAVE TRANSMISSION

Once a slave is addressed in this fashion, with the full 10-bit address (we will refer to this state as "PRI-OR\_ADDR\_MATCH"), the master can begin sending data bytes for a slave reception operation.

#### 14.4.2 10-BIT MODE SLAVE RECEPTION

Once addressed, the master can generate a Repeated Start, reset the high byte of the address and set the R\_W bit without generating a Stop bit, thus initiating a slave transmit operation.

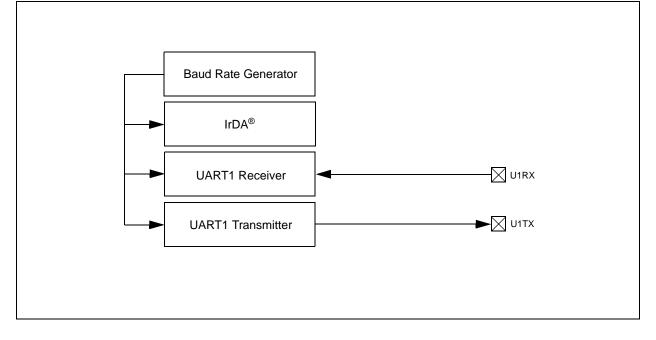

## 15.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART) MODULE

**Note:** This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "*dsPIC30F Family Reference Manual*" (DS70046).

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the dsPIC30F1010/202X device family. The UART is a full-duplex asynchronous system that can communicate with peripheral devices, such as personal computers, LIN, RS-232 and RS-485 interfaces. The module also includes an IrDA encoder and decoder.

The primary features of the UART module are:

- Full-Duplex 8 or 9-bit Data Transmission through the U1TX and U1RX pins

- Even, Odd or No Parity Options (for 8-bit data)

- One or Two Stop bits

- Fully Integrated Baud Rate Generator with 16-bit Prescaler

- Baud Rates Ranging from 1 Mbps to 15 bps at 16 MIPS

- 4-Deep First-In-First-Out (FIFO) Transmit Data Buffer

- 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-bit mode with Address Detect (9th bit = 1)

- Transmit and Receive Interrupts

- · Loopback mode for Diagnostic Support

- Support for Sync and Break Characters

- Supports Automatic Baud Rate Detection

- IrDA Encoder and Decoder Logic

- 16x Baud Clock Output for IrDA Support

A simplified block diagram of the UART is shown in Figure 15-1. The UART module consists of these key important hardware elements:

- Baud Rate Generator

- Asynchronous Transmitter

- Asynchronous Receiver

### FIGURE 15-1: UART SIMPLIFIED BLOCK DIAGRAM

#### REGISTER 16-5: A/D CONVERT PAIR CONTROL REGISTER 0 (ADCPC0) (CONTINUED)

bit 4-0 TRGSRC0<4:0>: Trigger 0 Source Selection bits

Selects trigger source for conversion of analog channels AN1 and AN0.

- 00000 = No conversion enabled

- 00001 = Individual software trigger selected

- 00010 = Global software trigger selected

- 00011 = PWM Special Event Trigger selected

- 00100 = PWM generator #1 trigger selected

- 00101 = PWM generator #2 trigger selected

- 00110 = PWM generator #3 trigger selected

- 00111 = PWM generator #4 trigger selected

- 01100 = Timer #1 period match

- 01101 = Timer #2 period match

- 01110 = PWM GEN #1 current-limit ADC trigger

- 01111 = PWM GEN #2 current-limit ADC trigger

- 10000 = PWM GEN #3 current-limit ADC trigger

- 10001 = PWM GEN #4 current-limit ADC trigger

- 10110 = PWM GEN #1 fault ADC trigger

- 10111 = PWM GEN #2 fault ADC trigger

- 11000 = PWM GEN #3 fault ADC trigger

- 11001 = PWM GEN #4 fault ADC trigger

## REGISTER 18-1: OSCCON: OSCILLATOR CONTROL REGISTER (CONTINUED)

| bit 5 | LOCK: PLL Lock Status bit (read-only)                                                               |

|-------|-----------------------------------------------------------------------------------------------------|

|       | 1 = Indicates that PLL is in lock                                                                   |

|       | 0 = Indicates that PLL is out of lock (or disabled)                                                 |

|       | This bit is Reset upon:                                                                             |

|       | Reset on POR                                                                                        |

|       | Reset when a valid clock switching sequence is initiated by the clock switch state machine          |

|       | Set when PLL lock is achieved after a PLL start                                                     |

|       | Reset when lock is lost<br>Read zero when PLL is not selected as a Group 1 system clock             |

|       | Read zero when PLL is not selected as a Group 1 system clock                                        |

| bit 4 | PRCDEN: Pseudo Random Clock Dither Enable bit                                                       |

|       | 1 = Pseudo random clock dither is enabled                                                           |

|       | 0 = Pseudo random clock dither is disabled                                                          |

| bit 3 | <b>CF:</b> Clock Fail Detect bit (read/clearable by application)                                    |

|       | 1 = FSCM has detected clock failure                                                                 |

|       | 0 = FSCM has NOT detected clock failure                                                             |

|       | This bit is Reset upon:<br>Reset on POR                                                             |

|       | Reset when a valid clock switching sequence is initiated by the clock switch state machine          |

|       | Set when clock fail detected                                                                        |

| bit 2 | TSEQEN: FRC Tune Sequencer Enable bit                                                               |

|       | 1 = The TUN<3:0>, TSEQ1<3:0>,, TSEQ7<3:0> bits in the OSCTUN and the OSCTUN2 registers              |

|       | sequentially tune the FRC oscillator. Each field being sequentially selected via the ROLL<2:0> sig- |

|       | nals from the PWM module.                                                                           |

|       | 0 = The TUN<3:0> bits in OSCTUN register tunes the FRC oscillator                                   |

| bit 1 | Unimplemented: Read as '0'                                                                          |

| bit 0 | OSWEN: Oscillator Switch Enable bit                                                                 |

|       | 1 = Request oscillator switch to selection specified by NOSC<1:0> bits                              |

|       | 0 = Oscillator switch is complete                                                                   |

|       | This bit is Reset upon:                                                                             |

|       | Reset on POR                                                                                        |

|       | Reset after a successful clock switch                                                               |

Reset after a redundant clock switch

Reset after FSCM switches the oscillator to (Group 3) FRC

## TABLE 18-8: SYSTEM INTEGRATION REGISTER MAP FOR dsPIC30F202X

| SFR<br>Name | Addr | Bit 15 | Bit 14 | Bit 13   | Bit 12     | Bit 11   | Bit 10 | Bit 9     | Bit 8 | Bit 7          | Bit 6 | Bit 5  | Bit 4  | Bit 3    | Bit 2           | Bit 1  | Bit 0               | Reset State                    |

|-------------|------|--------|--------|----------|------------|----------|--------|-----------|-------|----------------|-------|--------|--------|----------|-----------------|--------|---------------------|--------------------------------|

| RCON        | 0740 | TRAPR  | IOPUWR |          | _          | _        | _      |           |       | EXTR           | SWR   | SWDTEN | WDTO   | SLEEP    | IDLE            | _      | POR                 | Depends on type of Reset.      |

| OSCCON      | 0742 | I      | CC     | )SC<2:0> |            |          | ١      | NOSC<2:0> | >     | CLKLOCK        |       | LOCK   | PRCDEN | CF       | TSEQEN          | _      | OSWEN               | Depends on Configuration bits. |

| OSCTUN      | 0748 |        | TSEQ3< | <3:0>    | TSEQ2<3:0> |          |        |           |       | TSEQ1<3:0>     |       |        |        | TUN<3:0> |                 |        |                     | 0000 0000 0000 0000            |

| OSCTUN2     | 074A |        | TSEQ7< | <3:0>    |            |          | TSEQ6< | :3:0>     |       | TSEQ5<3:0> TSE |       |        |        |          | TSEQ4           | 4<3:0> |                     | 0000 0000 0000 0000            |

| LFSR        | 074C | I      |        |          |            |          |        |           |       | LFSR<14:0>     |       |        |        |          |                 |        |                     | 0000 0000 0000 0000            |

| PMD1        | 0770 | I      |        | T3MD     | T2MD       | T1MD     | -      | PWMMD     | ١     | I2CMD          | Ι     | U1MD   | _      | SPI1MD   |                 | _      | ADCMD               | 0000 0000 0000 0000            |

| PMD2        | 0772 |        |        |          | _          | _        | -      |           | IC1MD |                |       | _      | _      |          | — — OC2MD OC1MD |        | 0000 0000 0000 0000 |                                |

| PMD3        | 0774 |        |        | 1        | _          | CMP_PSMD | -      |           |       | _              | -     | _      | _      |          | _               | _      | —                   | 0000 0000 0000 0000            |

Note: Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

#### TABLE 18-9: DEVICE CONFIGURATION REGISTER MAP

| File Name | Addr.  | Bits 23-16 | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3 | Bit 2    | Bit 1    | Bit 0   |

|-----------|--------|------------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|-------|----------|----------|---------|

| FBS       | F80000 | _          |        | —      | -      | -      | _      |        | _     | -     | —      | —      | —      | _      |       | BSS<2:0> |          | BWRP    |

| FGS       | F80004 | _          | _      | —      |        |        | _      | -      | _     |       | _      | —      | _      | _      | _     | GSS1     | GSS0     | GWRP    |

| FOSCSEL   | F80006 |            |        | _      |        |        |        |        |       |       | _      | _      | _      | _      |       | -        | FNOS     | SC<1:0> |

| FOSC      | F80008 | _          |        | _      | _      |        |        |        |       |       | FCKS   | M<1:0> | FRANGE | _      | -     | OSCIOFNC | POSCI    | MD<1:0> |

| FWDT      | F8000A | _          | _      | _      | _      | _      | _      | _      | _     | _     | FWDTEN | WWDTEN | -      | WDTPRE |       | WDTPOST  | <3:0>    |         |

| FPOR      | F8000C | -          |        | _      |        |        | _      |        | _     |       | _      | _      | _      | _      | -     | FPV      | /RT<2:0: | >       |

Note: Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

| Base<br>Instr<br># | Assembly<br>Mnemonic |        | Assembly Syntax | Description                                       | # of<br>word<br>s | # of<br>cycles | Status Flags<br>Affected |

|--------------------|----------------------|--------|-----------------|---------------------------------------------------|-------------------|----------------|--------------------------|

| 52                 | NEG                  | NEG    | Acc             | Negate Accumulator                                | 1                 | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | NEG    | f               | $f = \overline{f} + 1$                            | 1                 | 1              | C,DC,N,OV,Z              |

|                    |                      | NEG    | f,WREG          | WREG = $\overline{f}$ + 1                         | 1                 | 1              | C,DC,N,OV,Z              |

|                    |                      | NEG    | Ws,Wd           | $Wd = \overline{Ws} + 1$                          | 1                 | 1              | C,DC,N,OV,Z              |

| 53                 | NOP                  | NOP    |                 | No Operation                                      | 1                 | 1              | None                     |

|                    |                      | NOPR   |                 | No Operation                                      | 1                 | 1              | None                     |

| 54                 | POP                  | POP    | f               | Pop f from Top-of-Stack (TOS)                     | 1                 | 1              | None                     |

|                    |                      | POP    | Wdo             | Pop from Top-of-Stack (TOS) to Wdo                | 1                 | 1              | None                     |

|                    |                      | POP.D  | Wnd             | Pop from Top-of-Stack (TOS) to<br>W(nd):W(nd + 1) | 1                 | 2              | None                     |

|                    |                      | POP.S  |                 | Pop Shadow Registers                              | 1                 | 1              | All                      |

| 55                 | PUSH                 | PUSH   | f               | Push f to Top-of-Stack (TOS)                      | 1                 | 1              | None                     |

|                    |                      | PUSH   | Wso             | Push Wso to Top-of-Stack (TOS)                    | 1                 | 1              | None                     |

|                    |                      | PUSH.D | Wns             | Push W(ns):W(ns + 1) to Top-of-Stack<br>(TOS)     | 1                 | 2              | None                     |

|                    |                      | PUSH.S |                 | Push Shadow Registers                             | 1                 | 1              | None                     |

| 56                 | PWRSAV               | PWRSAV | #lit1           | Go into Sleep or Idle mode                        | 1                 | 1              | WDTO,Sleep               |

| 57                 | RCALL                | RCALL  | Expr            | Relative Call                                     | 1                 | 2              | None                     |

|                    |                      | RCALL  | Wn              | Computed Call                                     | 1                 | 2              | None                     |

| 58                 | REPEAT               | REPEAT | #lit14          | Repeat Next Instruction lit14 + 1 times           | 1                 | 1              | None                     |

|                    |                      | REPEAT | Wn              | Repeat Next Instruction (Wn) + 1 times            | 1                 | 1              | None                     |

| 59                 | RESET                | RESET  |                 | Software device Reset                             | 1                 | 1              | None                     |

| 60                 | RETFIE               | RETFIE |                 | Return from interrupt                             | 1                 | 3 (2)          | None                     |

| 61                 | RETLW                | RETLW  | #lit10,Wn       | Return with literal in Wn                         | 1                 | 3 (2)          | None                     |

| 62                 | RETURN               | RETURN |                 | Return from Subroutine                            | 1                 | 3 (2)          | None                     |

| 63                 | RLC                  | RLC    | f               | f = Rotate Left through Carry f                   | 1                 | 1              | C,N,Z                    |

|                    |                      | RLC    | f,WREG          | WREG = Rotate Left through Carry f                | 1                 | 1              | C,N,Z                    |

|                    |                      | RLC    | Ws,Wd           | Wd = Rotate Left through Carry Ws                 | 1                 | 1              | C,N,Z                    |

| 64                 | RLNC                 | RLNC   | f               | f = Rotate Left (No Carry) f                      | 1                 | 1              | N,Z                      |

|                    |                      | RLNC   | f,WREG          | WREG = Rotate Left (No Carry) f                   | 1                 | 1              | N,Z                      |

|                    |                      | RLNC   | Ws,Wd           | Wd = Rotate Left (No Carry) Ws                    | 1                 | 1              | N,Z                      |

| 65                 | RRC                  | RRC    | f               | f = Rotate Right through Carry f                  | 1                 | 1              | C,N,Z                    |

|                    |                      | RRC    | f,WREG          | WREG = Rotate Right through Carry f               | 1                 | 1              | C,N,Z                    |

|                    |                      | RRC    | Ws,Wd           | Wd = Rotate Right through Carry Ws                | 1                 | 1              | C,N,Z                    |

| 66                 | RRNC                 | RRNC   | f               | f = Rotate Right (No Carry) f                     | 1                 | 1              | N,Z                      |

|                    |                      | RRNC   | f,WREG          | WREG = Rotate Right (No Carry) f                  | 1                 | 1              | N,Z                      |

|                    |                      | RRNC   | Ws,Wd           | Wd = Rotate Right (No Carry) Ws                   | 1                 | 1              | N,Z                      |

| 67                 | SAC                  | SAC    | Acc,#Slit4,Wdo  | Store Accumulator                                 | 1                 | 1              | None                     |

|                    |                      | SAC.R  | Acc,#Slit4,Wdo  | Store Rounded Accumulator                         | 1                 | 1              | None                     |

| 68                 | SE                   | SE     | Ws,Wnd          | Wnd = sign extended Ws                            | 1                 | 1              | C,N,Z                    |

| 69                 | SETM                 | SETM   | f               | f = 0xFFFF                                        | 1                 | 1              | None                     |

|                    |                      | SETM   | WREG            | WREG = 0xFFFF                                     | 1                 | 1              | None                     |

|                    |                      | SETM   | Ws              | Ws = 0xFFFF                                       | 1                 | 1              | None                     |

| 70                 | SFTAC                | SFTAC  | Acc,Wn          | Arithmetic Shift Accumulator by (Wn)              | 1                 | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | SFTAC  | Acc,#Slit6      | Arithmetic Shift Accumulator by Slit6             | 1                 | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

| 71                 | SL                   | SL     | f               | f = Left Shift f                                  | 1                 | 1              | C,N,OV,Z                 |

|                    |                      | SL     | f,WREG          | WREG = Left Shift f                               | 1                 | 1              | C,N,OV,Z                 |

|                    |                      | SL     | Ws,Wd           | Wd = Left Shift Ws                                | 1                 | 1              | C,N,OV,Z                 |

|                    |                      | SL     | Wb,Wns,Wnd      | Wnd = Left Shift Wb by Wns                        | 1                 | 1              | N,Z                      |

|                    |                      | SL     | Wb,#lit5,Wnd    | Wnd = Left Shift Wb by lit5                       | 1                 | 1              | N,Z                      |

#### TABLE 19-2: INSTRUCTION SET OVERVIEW (CONTINUED)

### 20.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 20.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

#### 20.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

## 20.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

## 20.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

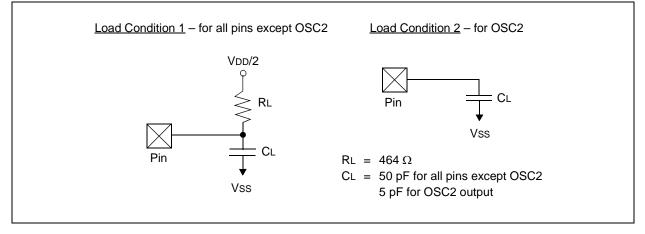

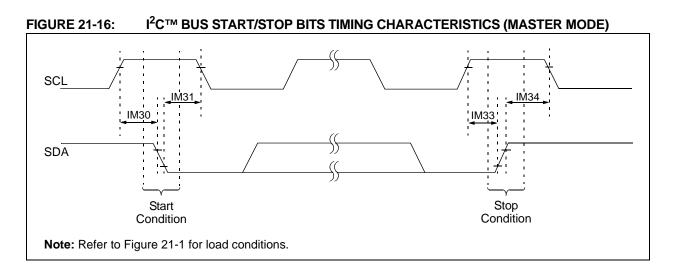

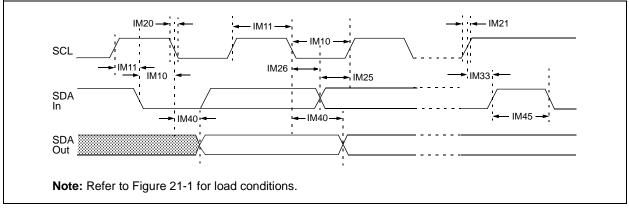

## 21.2 AC Characteristics and Timing Parameters

The information contained in this section defines dsPIC30F AC characteristics and timing parameters.

#### TABLE 21-11: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

|                    | Standard Operating Conditions: 3.3V and 5.0V (±10%) (unless otherwise stated)                                                       |  |  |  |  |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| AC CHARACTERISTICS | Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |  |  |  |  |

|                    | Operating voltage VDD range as described in DC Spec Section 21.0.                                                                   |  |  |  |  |

#### FIGURE 21-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

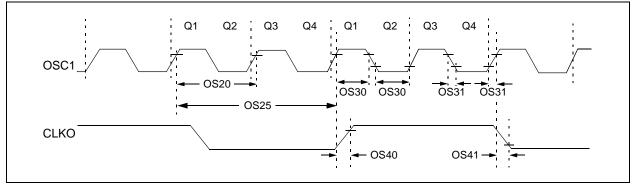

#### FIGURE 21-2: EXTERNAL CLOCK TIMING

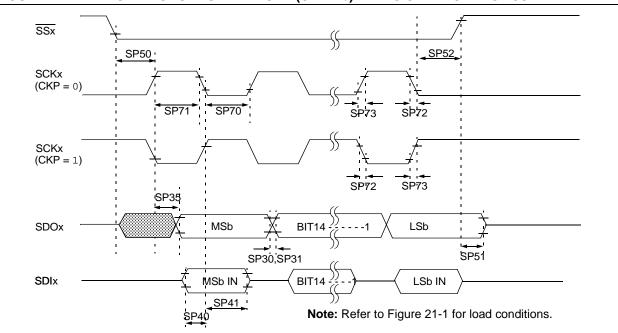

#### FIGURE 21-14: SPIX MODULE SLAVE MODE (CKE = 0) TIMING CHARACTERISTICS

#### TABLE 21-29: SPIX MODULE SLAVE MODE (CKE = 0) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                                   | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                    |     |       |                    |  |

|--------------------|-----------------------|---------------------------------------------------|-------------------------------------------------------|--------------------|-----|-------|--------------------|--|

| Param<br>No.       | Symbol                | Characteristic <sup>(1)</sup>                     | Min                                                   | Тур <sup>(2)</sup> | Max | Units | Conditions         |  |

| SP70               | TscL                  | SCKx Input Low Time                               | 30                                                    | -                  | _   | ns    |                    |  |

| SP71               | TscH                  | SCKx Input High Time                              | 30                                                    | _                  |     | ns    |                    |  |

| SP72               | TscF                  | SCKx Input Fall Time <sup>(3)</sup>               |                                                       | 10                 | 25  | ns    |                    |  |

| SP73               | TscR                  | SCKx Input Rise Time <sup>(3)</sup>               |                                                       | 10                 | 25  | ns    |                    |  |

| SP30               | TdoF                  | SDOx Data Output Fall Time <sup>(3)</sup>         | —                                                     |                    | _   | ns    | See Parameter D032 |  |

| SP31               | TdoR                  | SDOx Data Output Rise Time <sup>(3)</sup>         | —                                                     | _                  | _   | ns    | See Parameter D031 |  |

| SP35               | TscH2doV<br>TscL2doV  | SDOx Data Output Valid after<br>SCKx Edge         | —                                                     | _                  | 30  | ns    |                    |  |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge        | 20                                                    | _                  | _   | ns    |                    |  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge         | 20                                                    | _                  | _   | ns    |                    |  |

| SP50               | TssL2scH,<br>TssL2scL | $\overline{SSx}$ to SCKx $\uparrow$ or SCKx Input | 120                                                   | —                  | _   | ns    |                    |  |

| SP51               | TssH2doZ              | SSx↑ to SDOx Output High-Impedance <sup>(3)</sup> | 10                                                    | —                  | 50  | ns    |                    |  |

| SP52               | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                               | 1.5 Tcy + 40                                          | —                  | —   | ns    |                    |  |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 5V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

3: Assumes 50 pF load on all SPIx pins.

NOTES:

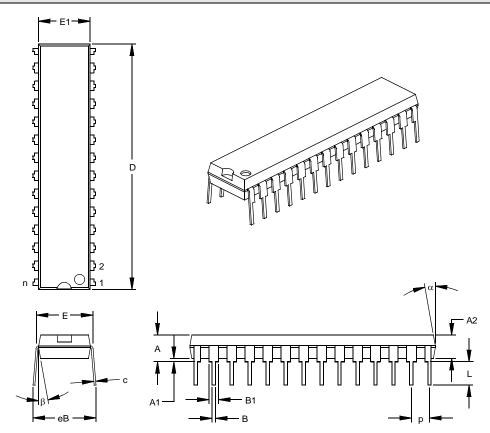

## 28-Lead Skinny Plastic Dual In-line (SP) – 300 mil Body (PDIP)

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units | INCHES* |       |       | MILLIMETERS |       |       |  |

|----------------------------|-------|---------|-------|-------|-------------|-------|-------|--|

| Dimension Limits           |       | MIN     | NOM   | MAX   | MIN         | NOM   | MAX   |  |

| Number of Pins             | n     | 28      |       |       | 28          |       |       |  |

| Pitch                      | р     |         | .100  |       |             | 2.54  |       |  |

| Top to Seating Plane       | А     | .140    | .150  | .160  | 3.56        | 3.81  | 4.06  |  |

| Molded Package Thickness   | A2    | .125    | .130  | .135  | 3.18        | 3.30  | 3.43  |  |

| Base to Seating Plane      | A1    | .015    |       |       | 0.38        |       |       |  |

| Shoulder to Shoulder Width | E     | .300    | .310  | .325  | 7.62        | 7.87  | 8.26  |  |

| Molded Package Width       | E1    | .275    | .285  | .295  | 6.99        | 7.24  | 7.49  |  |

| Overall Length             | D     | 1.345   | 1.365 | 1.385 | 34.16       | 34.67 | 35.18 |  |

| Tip to Seating Plane       | L     | .125    | .130  | .135  | 3.18        | 3.30  | 3.43  |  |

| Lead Thickness             | С     | .008    | .012  | .015  | 0.20        | 0.29  | 0.38  |  |

| Upper Lead Width           | B1    | .040    | .053  | .065  | 1.02        | 1.33  | 1.65  |  |

| Lower Lead Width           | В     | .016    | .019  | .022  | 0.41        | 0.48  | 0.56  |  |

| Overall Row Spacing        | § eB  | .320    | .350  | .430  | 8.13        | 8.89  | 10.92 |  |

| Mold Draft Angle Top       | α     | 5       | 10    | 15    | 5           | 10    | 15    |  |

| Mold Draft Angle Bottom    | β     | 5       | 10    | 15    | 5           | 10    | 15    |  |

\* Controlling Parameter

§ Significant Characteristic

Notes:

Dimension D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MO-095