Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | dsPIC                                                                          |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 30 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                          |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 12KB (4K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 512 x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                      |

| Data Converters            | A/D 12x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 44-QFN (8x8)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f2023t-30i-ml |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 1-3: PINOUT I/O DESCRIPTIONS FOR dsPIC30F2023 (CONTINUED)

| Pin Name                         | 9   | Pin<br>Type | Buffer<br>Type | Description                                                                                              |  |  |  |  |  |

|----------------------------------|-----|-------------|----------------|----------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| PGD                              |     | I/O         | ST             | In-Circuit Serial Programming™ data input/output pin.                                                    |  |  |  |  |  |

| PGC                              |     | Ι           | ST             | In-Circuit Serial Programming clock input pin.                                                           |  |  |  |  |  |

| PGD1                             |     | I/O         | ST             | In-Circuit Serial Programming data input/output pin 1.                                                   |  |  |  |  |  |

| PGC1                             |     | I           | ST             | In-Circuit Serial Programming clock input pin 1.                                                         |  |  |  |  |  |

| PGD2                             |     | I/O         | ST             | In-Circuit Serial Programming data input/output pin 2.                                                   |  |  |  |  |  |

| PGC2                             |     | I           | ST             | In-Circuit Serial Programming clock input pin 2.                                                         |  |  |  |  |  |

| RA8-RA11                         |     | I/O         | ST             | PORTA is a bidirectional I/O port.                                                                       |  |  |  |  |  |

| RB0-RB11                         |     | I/O         | ST             | PORTB is a bidirectional I/O port.                                                                       |  |  |  |  |  |

| RD0,RD1                          |     | I/O         | ST             | PORTD is a bidirectional I/O port.                                                                       |  |  |  |  |  |

| RE0-RE7                          |     | I/O         | ST             | PORTE is a bidirectional I/O port.                                                                       |  |  |  |  |  |

| RF2, RF3,<br>RF6-RF8, RF<br>RF15 | 14, | I/O         | ST             | PORTF is a bidirectional I/O port.                                                                       |  |  |  |  |  |

| RG2, RG3                         |     | I/O         | ST             | PORTG is a bidirectional I/O port.                                                                       |  |  |  |  |  |

| SCK1                             |     | I/O         | ST             | Synchronous serial clock input/output for SPI #1.                                                        |  |  |  |  |  |

| SDI1                             |     | Ι           | ST             | SPI #1 Data In.                                                                                          |  |  |  |  |  |

| SDO1                             |     | 0           | —              | SPI #1 Data Out.                                                                                         |  |  |  |  |  |

| SS1                              |     | I           | ST             | SPI #1 Slave Synchronization.                                                                            |  |  |  |  |  |

| SCL                              |     | I/O         | ST             | Synchronous serial clock input/output for I <sup>2</sup> C.                                              |  |  |  |  |  |

| SDA                              |     | I/O         | ST             | Synchronous serial data input/output for I <sup>2</sup> C.                                               |  |  |  |  |  |

| T1CK<br>T2CK                     |     | 1           | ST<br>ST       | Timer1 external clock input.<br>Timer2 external clock input.                                             |  |  |  |  |  |

| U1RX                             |     | I           | ST             | UART1 Receive.                                                                                           |  |  |  |  |  |

| U1TX                             |     | ò           | _              | UART1 Transmit.                                                                                          |  |  |  |  |  |

| U1ARX                            |     | I           | ST             | Alternate UART1 Receive.                                                                                 |  |  |  |  |  |

| U1ATX                            |     | ò           | _              | Alternate UART1 Transmit                                                                                 |  |  |  |  |  |

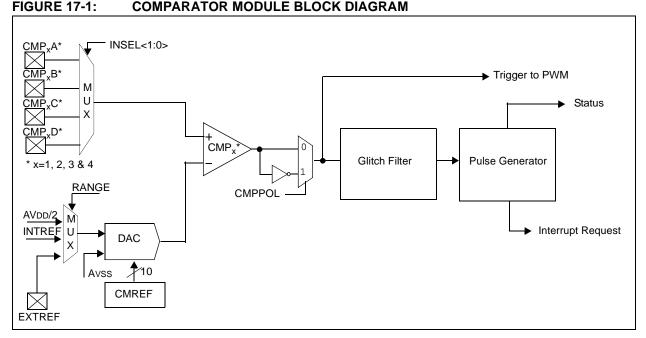

| CMP1A                            |     | I           | Analog         | Comparator 1 Channel A                                                                                   |  |  |  |  |  |

| CMP1B                            |     | Ι           | Analog         | Comparator 1 Channel B                                                                                   |  |  |  |  |  |

| CMP1C                            |     | Ι           | Analog         | Comparator 1 Channel C                                                                                   |  |  |  |  |  |

| CMP1D                            |     | Ι           | Analog         | Comparator 1 Channel D                                                                                   |  |  |  |  |  |

| CMP2A                            |     | I           | Analog         | Comparator 2 Channel A                                                                                   |  |  |  |  |  |

| CMP2B                            |     | I.          | Analog         | Comparator 2 Channel B                                                                                   |  |  |  |  |  |

| CMP2C                            |     | I           | Analog         | Comparator 2 Channel C                                                                                   |  |  |  |  |  |

| CMP2D                            |     | Ì           | Analog         | Comparator 2 Channel D                                                                                   |  |  |  |  |  |

| CMP3A                            |     | i           | Analog         | Comparator 3 Channel A                                                                                   |  |  |  |  |  |

| CMP3B                            |     |             | Analog         | Comparator 3 Channel B                                                                                   |  |  |  |  |  |

| CMP3C                            |     | I           | Analog         | Comparator 3 Channel C                                                                                   |  |  |  |  |  |

| CMP3D                            |     | I           | Analog         | Comparator 3 Channel D                                                                                   |  |  |  |  |  |

| CMP4A                            |     |             | Analog         | Comparator 4 Channel A                                                                                   |  |  |  |  |  |

| CMP4B                            |     | i           | Analog         | Comparator 4 Channel B                                                                                   |  |  |  |  |  |

| CMP4C                            |     | 1           | Analog         | Comparator 4 Channel C                                                                                   |  |  |  |  |  |

| CMP4C<br>CMP4D                   |     | I           | Analog         |                                                                                                          |  |  |  |  |  |

| CN0-CN7                          |     | I           | ST             | Input Change notification inputs<br>Can be software programmed for internal weak pull-ups on all inputs. |  |  |  |  |  |

| Vdd                              |     | Р           | —              | Positive supply for logic and I/O pins.                                                                  |  |  |  |  |  |

| Vss                              |     | Р           | _              | Ground reference for logic and I/O pins.                                                                 |  |  |  |  |  |

| EXTREF                           |     | I           | Analog         |                                                                                                          |  |  |  |  |  |

| Legend: C                        | MOS | -           | -              | ompatible input or output Analog = Analog input                                                          |  |  |  |  |  |

| S                                |     | = 5         | Schmitt Trigg  | er input with CMOS levels O = Output                                                                     |  |  |  |  |  |

| I                                |     | =           | nput           | P = Power                                                                                                |  |  |  |  |  |

# 2.2 Programmer's Model

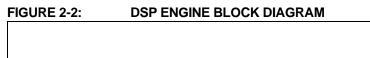

The programmer's model is shown in Figure 2-1 and consists of 16x16-bit working registers (W0 through W15), 2x40-bit accumulators (ACCA and ACCB), STATUS register (SR), Data Table Page register (TBLPAG), Program Space Visibility Page register (PSVPAG), DO and REPEAT registers (DOSTART, DOEND, DCOUNT and RCOUNT), and Program Counter (PC). The working registers can act as data, address or offset registers. All registers are memory mapped. W0 acts as the W register for file register addressing.

Some of these registers have a shadow register associated with each of them, as shown in Figure 2-1. The shadow register is used as a temporary holding register and can transfer its contents to or from its host register upon the occurrence of an event. None of the shadow registers are accessible directly. The following rules apply for transfer of registers into and out of shadows.

- PUSH.S and POP.S W0, W1, W2, W3, SR (DC, N, OV, Z and C bits only) are transferred.

- DO instruction DOSTART, DOEND, DCOUNT shadows are pushed on loop start, and popped on loop end.

When a byte operation is performed on a working register, only the Least Significant Byte (LSB) of the target register is affected. However, a benefit of memory mapped working registers is that both the Least and Most Significant Bytes (MSBs) can be manipulated through byte wide data memory space accesses.

#### 2.2.1 SOFTWARE STACK POINTER/ FRAME POINTER

The dsPIC<sup>®</sup> DSC devices contain a software stack. W15 is the dedicated software Stack Pointer (SP), and will be automatically modified by exception processing and subroutine calls and returns. However, W15 can be referenced by any instruction in the same manner as all other W registers. This simplifies the reading, writing and manipulation of the Stack Pointer (e.g., creating stack frames).

| Note: | In order to protect against misaligi | ned |

|-------|--------------------------------------|-----|

|       | stack accesses, W15<0> is always cle | ar. |

W15 is initialized to 0x0800 during a Reset. The user may reprogram the SP during initialization to any location within data space.

W14 has been dedicated as a Stack Frame Pointer as defined by the LNK and ULNK instructions. However, W14 can be referenced by any instruction in the same manner as all other W registers.

## 2.2.2 STATUS REGISTER

The dsPIC DSC core has a 16-bit STATUS Register (SR), the LSB of which is referred to as the SR Low Byte (SRL) and the MSB as the SR High Byte (SRH). See Figure 2-1 for SR layout.

SRL contains all the MCU ALU operation status flags (including the Z bit), as well as the CPU Interrupt Priority Level Status bits, IPL<2:0>, and the REPEAT active Status bit, RA. During exception processing, SRL is concatenated with the MSB of the PC to form a complete word value, which is then stacked.

The upper byte of the STATUS register contains the DSP Adder/Subtracter status bits, the DO Loop Active bit (DA) and the Digit Carry (DC) Status bit.

## 2.2.3 PROGRAM COUNTER

The Program Counter is 23 bits wide. Bit 0 is always clear. Therefore, the PC can address up to 4M instruction words.

The SA and SB bits are modified each time data passes through the adder/subtracter, but can only be cleared by the user. When set, they indicate that the accumulator has overflowed its maximum range (bit 31 for 32-bit saturation, or bit 39 for 40-bit saturation) and will be saturated (if saturation is enabled). When saturation is not enabled, SA and SB default to bit 39 overflow and thus indicate that a catastrophic overflow has occurred. If the COVTE bit in the INTCON1 register is set, SA and SB bits will generate an arithmetic warning trap when saturation is disabled.

The overflow and saturation Status bits can optionally be viewed in the STATUS Register (SR) as the logical OR of OA and OB (in bit OAB) and the logical OR of SA and SB (in bit SAB). This allows programmers to check one bit in the STATUS Register to determine if either accumulator has overflowed, or one bit to determine if either accumulator has saturated. This is useful for complex number arithmetic, which typically uses both the accumulators.

The device supports three Saturation and Overflow modes.

1. Bit 39 Overflow and Saturation:

When bit 39 overflow and saturation occurs, the saturation logic loads the maximally positive 9.31 (0x7FFFFFFFF) or maximally negative 9.31 value (0x800000000) into the target accumulator. The SA or SB bit is set and remains set until cleared by the user. This is referred to as 'super saturation' and provides protection against erroneous data or unexpected algorithm problems (e.g., gain calculations).

- Bit 31 Overflow and Saturation: When bit 31 overflow and saturation occurs, the saturation logic then loads the maximally positive 1.31 value (0x007FFFFFF) or maximally negative 1.31 value (0x0080000000) into the target accumulator. The SA or SB bit is set and remains set until cleared by the user. When this Saturation mode is in effect, the guard bits are not used (so the OA, OB or OAB bits are never set).

- 3. Bit 39 Catastrophic Overflow

The bit 39 overflow Status bit from the adder is used to set the SA or SB bit, which remain set until cleared by the user. No saturation operation is performed and the accumulator is allowed to overflow (destroying its sign). If the COVTE bit in the INTCON1 register is set, a catastrophic overflow can initiate a trap exception.

# 2.4.2.2 Accumulator 'Write Back'

The MAC class of instructions (with the exception of MPY, MPY.N, ED and EDAC) can optionally write a rounded version of the high word (bits 31 through 16) of the accumulator that is not targeted by the instruction into data space memory. The write is performed across the X bus into combined X and Y address space. The following addressing modes are supported:

- 1. W13, Register Direct: The rounded contents of the non-target accumulator are written into W13 as a 1.15 fraction.

- [W13] + = 2, Register Indirect with Post-Increment: The rounded contents of the non-target accumulator are written into the address pointed to by W13 as a 1.15 fraction. W13 is then incremented by 2 (for a word write).

## 2.4.2.3 Round Logic

The round logic is a combinational block, which performs a conventional (biased) or convergent (unbiased) round function during an accumulator write (store). The Round mode is determined by the state of the RND bit in the CORCON register. It generates a 16-bit, 1.15 data value which is passed to the data space write saturation logic. If rounding is not indicated by the instruction, a truncated 1.15 data value is stored and the least significant word (lsw) is simply discarded.

Conventional rounding takes bit 15 of the accumulator, zero-extends it and adds it to the ACCxH word (bits 16 through 31 of the accumulator). If the ACCxL word (bits 0 through 15 of the accumulator) is between 0x8000 and 0xFFFF (0x8000 included), ACCxH is incremented. If ACCxL is between 0x0000 and 0x7FFF, ACCxH is left unchanged. A consequence of this algorithm is that over a succession of random rounding operations, the value will tend to be biased slightly positive.

Convergent (or unbiased) rounding operates in the same manner as conventional rounding, except when ACCxL equals 0x8000. If this is the case, the LSb (bit 16 of the accumulator) of ACCxH is examined. If it is '1', ACCxH is incremented. If it is '0', ACCxH is not modified. Assuming that bit 16 is effectively random in nature, this scheme will remove any rounding bias that may accumulate.

The SAC and SAC.R instructions store either a truncated (SAC) or rounded (SAC.R) version of the contents of the target accumulator to data memory, via the X bus (subject to data saturation, see **Section 2.4.2.4** "**Data Space Write Saturation**"). Note that for the MAC class of instructions, the accumulator write back operation will function in the same manner, addressing combined MCU (X and Y) data space though the X bus. For this class of instructions, the data is always subject to rounding.

#### REGISTER 5-1: INTCON1: INTERRUPT CONTROL REGISTER 1 (CONTINUED)

- bit 2 STKERR: Stack Error Trap Status bit

- 1 = Stack error trap has occurred

- 0 = Stack error trap has not occurred

- bit 1 OSCFAIL: Oscillator Failure Trap Status bit

- 1 = Oscillator failure trap has occurred

- 0 = Oscillator failure trap has not occurred

- bit 0 Unimplemented: Read as '0'

# 9.0 TIMER2/3 MODULE

**Note:** This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "*dsPIC30F Family Reference Manual*" (DS70046).

This section describes the 32-bit General Purpose Timer module (Timer2/3) and associated operational modes. Figure 9-1 depicts the simplified block diagram of the 32-bit Timer2/3 module. Figure 9-2 and Figure 9-3 show Timer2/3 configured as two independent 16-bit timers: Timer2 and Timer3, respectively.

Note: The dsPIC30F1010 device does not feature Timer3. Timer2 is a 'Type B' timer and Timer3 is a 'Type C' timer. Please refer to the appropriate timer type in Section 21.0 "Electrical Characteristics" of this document.

The Timer2/3 module is a 32-bit timer, which can be configured as two 16-bit timers, with selectable operating modes. These timers are utilized by other peripheral modules such as:

- Input Capture

- Output Compare/Simple PWM

The following sections provide a detailed description, including setup and control registers, along with associated block diagrams for the operational modes of the timers.

The 32-bit timer has the following modes:

- Two independent 16-bit timers (Timer2 and Timer3) with all 16-bit operating modes (except Asynchronous Counter mode)

- Single 32-bit Timer operation

- Single 32-bit Synchronous Counter

Further, the following operational characteristics are supported:

- ADC Event Trigger

- Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation during Idle and Sleep modes

- Interrupt on a 32-bit Period Register Match

These operating modes are determined by setting the appropriate bit(s) in the 16-bit T2CON and T3CON SFRs.

For 32-bit timer/counter operation, Timer2 is the least significant word and Timer3 is the most significant word of the 32-bit timer.

Note: For 32-bit timer operation, T3CON control bits are ignored. Only T2CON control bits are used for setup and control. Timer 2 clock and gate inputs are utilized for the 32-bit timer module, but an interrupt is generated with the Timer3 interrupt flag (T3IF) and the interrupt is enabled with the Timer3 interrupt enable bit (T3IE).

**16-bit Mode:** In the 16-bit mode, Timer2 and Timer3 can be configured as two independent 16-bit timers. Each timer can be set up in either 16-bit Timer mode or 16-bit Synchronous Counter mode. See **Section 8.0 "Timer1 Module"** for details on these two operating modes.

The only functional difference between Timer2 and Timer3 is that Timer2 provides synchronization of the clock prescaler output. This is useful for high-frequency external clock inputs.

**32-bit Timer Mode:** In the 32-bit Timer mode, the timer increments on every instruction cycle up to a match value, preloaded into the combined 32-bit period register PR3/PR2, then resets to '0' and continues to count.

For synchronous 32-bit reads of the Timer2/Timer3 pair, reading the least significant word (TMR2 register) will cause the most significant word to be read and latched into a 16-bit holding register, termed TMR3HLD.

For synchronous 32-bit writes, the holding register (TMR3HLD) must first be written to. When followed by a write to the TMR2 register, the contents of TMR3HLD will be transferred and latched into the MSB of the 32-bit timer (TMR3).

**32-bit Synchronous Counter Mode:** In the 32-bit Synchronous Counter mode, the timer increments on the rising edge of the applied external clock signal, which is synchronized with the internal phase clocks. The timer counts up to a match value preloaded in the combined 32-bit period register, PR3/PR2, then resets to '0' and continues.

When the timer is configured for the Synchronous Counter mode of operation and the CPU goes into the Idle mode, the timer will stop incrementing, unless the TSIDL (T2CON<13>) bit = 0. If TSIDL = 1, the timer module logic will resume the incrementing sequence upon termination of the CPU Idle mode.

#### TABLE 9-1: TIMER2/3 REGISTER MAP

| SFR<br>Name | Addr.                     | Bit 15          | Bit 14                                                     | Bit 13 | Bit 12 | Bit 11 | Bit<br>10 | Bit 9 | Bit 8 | Bit 7               | Bit 6               | Bit 5               | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Reset State         |

|-------------|---------------------------|-----------------|------------------------------------------------------------|--------|--------|--------|-----------|-------|-------|---------------------|---------------------|---------------------|--------|-------|-------|-------|-------|---------------------|

| TMR2        | TMR2 0106 Timer2 Register |                 |                                                            |        |        |        |           |       |       |                     | uuuu uuuu uuuu uuuu |                     |        |       |       |       |       |                     |

| TMR3HLD     | 0108                      |                 | Timer3 Holding Register (For 32-bit timer operations only) |        |        |        |           |       |       |                     |                     | uuuu uuuu uuuu uuuu |        |       |       |       |       |                     |

| TMR3        | 010A                      | Timer3 Register |                                                            |        |        |        |           |       |       |                     | uuuu uuuu uuuu uuuu |                     |        |       |       |       |       |                     |

| PR2         | 010C                      |                 |                                                            |        |        |        |           |       | Pei   | riod Registe        | r 2                 |                     |        |       |       |       |       | 1111 1111 1111 1111 |

| PR3         | 010E                      |                 |                                                            |        |        |        |           |       | Per   | riod Registe        | r 3                 |                     |        |       |       |       |       | 1111 1111 1111 1111 |

| T2CON       | 0110                      | TON             | TON - TSIDL TGATE TCKPS<1:0> T32 - TCS -                   |        |        |        |           |       |       | 0000 0000 0000 0000 |                     |                     |        |       |       |       |       |                     |

| T3CON       | 0112                      | TON             | —                                                          | TSIDL  | _      | _      | —         | —     | -     | -                   | TGATE               | TCKPS               | S<1:0> | —     | —     | TCS   | —     | 0000 0000 0000 0000 |

|             |                           |                 |                                                            |        |        |        |           |       |       |                     |                     |                     |        |       |       |       |       |                     |

Legend: u = uninitialized bit

Note: Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

NOTES:

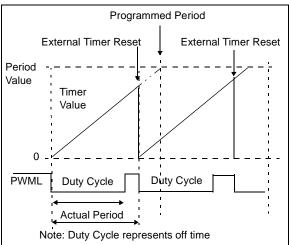

#### 12.4.7 CONSTANT OFF-TIME PWM

Constant Off-Time mode is shown in Figure 12-9. Constant Off-Time PWM is a variable-frequency mode where the actual PWM period is less than or equal to the specified period value. The PWM time base is externally reset some time after the PWM signal duty cycle value has been reached, and the PWM signal has been deasserted. This mode is implemented by enabling the On-Time PWM mode (Current Reset mode) and using the complementary output.

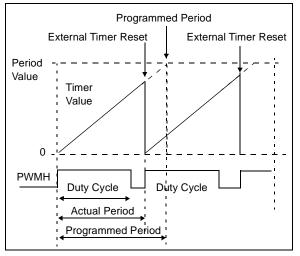

#### 12.4.8 CURRENT RESET PWM MODE

Current Reset PWM is shown in Figure 12-10. Current Reset PWM uses a Variable-Frequency mode where the actual PWM period is less than or equal to the specified period value. The PWM time base is externally reset some time after the PWM signal duty cycle value has been reached and the PWM signal has been deasserted. Current Reset PWM is a constant on-time PWM mode.

#### FIGURE 12-10: CURRENT RESET PWM

Typically, in the converter application, an energy storage inductor is charged with current while the PWM signal is asserted, and the inductor current is discharged by the load when the PWM signal is deasserted. In this application of current reset PWM, an external current measurement circuit determines when the inductor is discharged, and then generates a signal that the PWM module uses to reset the time base counter. In Current Reset mode, complementary outputs are available.

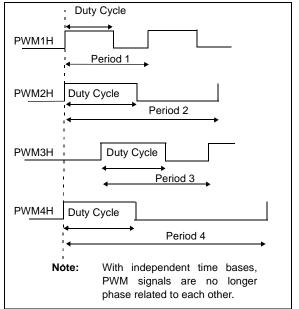

#### 12.4.9 INDEPENDENT TIME BASE PWM

Independent Time Base PWM, as shown in Figure 12-11, is often used when the dsPIC DSC is controlling different power converter subcircuits such as the Power Factor Correction circuit, which may use 100 kHz PWM, and the full-bridge forward converter section may use 250 kHz PWM.

#### FIGURE 12-11: INDEPENDENT TIME BASE PWM

#### 12.25 Simultaneous PWM Faults and Current Limits

The current-limit override function, if enabled and active, forces the PWMxH,L pins to the values specified by the CLDAT<1:0> bits in the IOCONx registers UNLESS the Fault function is enabled and active. If the selected Fault input is active, the PWMxH,L outputs assume the values specified by the FLTDAT<1:0> bits in the IOCONx registers.

## 12.26 PWM Fault and Current-Limit TRG Outputs To ADC

The Fault and current-limit source selection fields in the FCLCONx registers (FLTSRC<3:0> and CLSRC<3:0>) control multiplexers in each PWM generator module. The control multiplexers select the desired Fault and current-limit signals for their respective modules. The selected Fault and current-limit signals are also available to the ADC module as trigger signals that initiate ADC sampling and conversion operations.

## 12.27 PWM Output Override Priority

If the PWM module is enabled, the priority of PWMx pin ownership is:

- 1. PWM Generator (lowest priority)

- 2. Output Override

- 3. Current-Limit Override

- 4. Fault Override

- 5. PENx (GPIO/PWM) ownership (highest priority)

If the PWM module is disabled, the GPIO module controls the PWMx pins.

## 12.28 Fault and Current-Limit Override Issues with Dead-Time Logic

The PWMxH and PWMxL outputs are immediately driven low (deasserted) as specified by the CLDAT<1:0> and the FLTDAT<1:0> bits when a current-limit or a Fault event occurs.

The override data is gated with the PWM signals going into the dead-time logic block, and at the output of the PWM module, just ahead of the PWM pin output buffers.

Many applications require fast response to current shutdown for accurate current control and/or to limit circuitry damage to Fault currents.

Some applications will set the complementary PWM outputs high in synchronous rectifier designs when a Fault or current-limit event occurs. If the CLDAT or FLTDAT bits are set to '1', and their associated event occurs, then these asserted outputs will be delayed by clocked logic in the dead-time circuitry.

# 12.29 Asserting Outputs via Current Limit

It is possible to use the CLDAT bits to assert the PWMxH,L outputs in response to a current-limit event. Such behavior could be used as a current "force" feature in response to an external current or voltage measurement that indicates a sudden sharp increase in the load on the power-converter output. Forcing the PWM "ON" could be viewed as a "Feed-Forward" term that allows quick system response to unexpected load increases without waiting for the digital control loop to respond.

# 12.30 PWM Immediate Update

For high-performance PWM control-loop applications, the user may want to force the duty cycle updates to occur immediately. Setting the IUE bit in the PWMCONx register enables this feature.

In a closed-loop control application, any delay between the sensing of a system's state and the subsequent outputting of PWM control signals that drive the application reduces the loop stability. Setting the IUE bit minimizes the delay between writing the duty cycle registers and the response of the PWM generators to that change.

# 12.31 PWM Output Override

All control bits associated with the PWM output override function are contained in the IOCONx register.

If the PENH, PENL bits are set, the PWM module controls the PWMx output pins.

The PWM output override bits allow the user to manually drive the PWM I/O pins to specified logic states independent of the duty cycle comparison units.

The OVRDAT<1:0> bits in the IOCONx register determine the state of the PWM I/O pins when a particular output is overridden via the OVRENH,L bits.

The OVRENH, OVRENL bits are active high control bits. When the OVREN bits are set, the corresponding OVRDAT bit overrides the PWM output from the PWM generator.

## 12.31.1 COMPLEMENTARY OUTPUT MODE

When the PWM is in Complementary Output mode, the dead-time generator is still active with overrides. The output overrides and Fault overrides generate control signals used by the dead-time unit to set the outputs as requested, including dead time.

Dead-time insertion can be performed when PWM channels are overridden manually.

| R/W-0                                                                                                                                                                                                                                                                                                                                                                                               | R/W-0                                                                                                                                                                                                                | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| SPIFSD                                                                                                                                                                                                                                                                                                                                                                                              | FRMPOL                                                                                                                                                                                                               | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | bit 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |