#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                          |

|----------------------------|------------------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                                 |

| Core Processor             | 8051                                                                                     |

| Core Size                  | 8-Bit                                                                                    |

| Speed                      | 40MHz                                                                                    |

| Connectivity               | EBI/EMI, Serial Port                                                                     |

| Peripherals                | POR, WDT                                                                                 |

| Number of I/O              | 32                                                                                       |

| Program Memory Size        | 32KB (32K x 8)                                                                           |

| Program Memory Type        | FLASH                                                                                    |

| EEPROM Size                | -                                                                                        |

| RAM Size                   | 1K x 8                                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                              |

| Data Converters            | -                                                                                        |

| Oscillator Type            | Internal                                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                                          |

| Mounting Type              | Through Hole                                                                             |

| Package / Case             | 40-DIP                                                                                   |

| Supplier Device Package    | -                                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/w77e058a40dl |

|                            |                                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

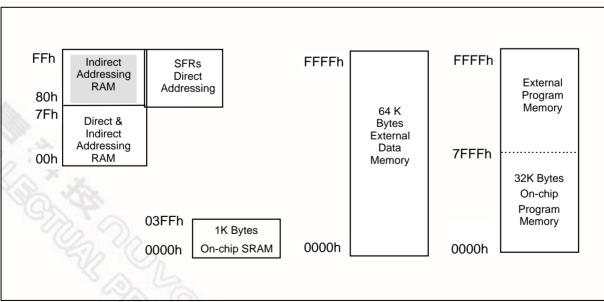

### 6. MEMORY ORGANIZATION

The W77E058 separates the memory into two separate sections, the Program Memory and the Data Memory. The Program Memory is used to store the instruction op-codes, while the Data Memory is used to store data or for memory mapped devices.

### 6.1 Program Memory

The Program Memory on the W77E058 can be up to 64 Kbytes long. There is also on-chip ROM which can be used similarly to that of the 8052, except that the ROM size is 32 Kbytes. All instructions are fetched for execution from this memory area. The MOVC instruction can also access this memory region. Exceeding the maximum address of on-chip ROM will access the external memory.

### 6.2 Data Memory

The W77E058 can access up to 64Kbytes of external Data Memory. This memory region is accessed by the MOVX instructions. Unlike the 8051 derivatives, the W77E058 contains on-chip 1K bytes MOVX SRAM of Data Memory, which can only be accessed by MOVX instructions. These 1K bytes of SRAM are between address 0000H and 03FFH. Access to the on-chip MOVX SRAM is optional under software control. When enabled by software, any MOVX instruction that uses this area will go to the on-chip RAM. MOVX addresses greater than 03FFH automatically go to external memory through Port 0 and 2. When disabled, the 1KB memory area is transparent to the system memory map. Any MOVX directed to the space between 0000H and FFFFH goes to the expanded bus on Port 0 and 2. This is the default condition. In addition, the W77E058 has the standard 256 bytes of on-chip Scratchpad RAM. This can be accessed either by direct addressing or by indirect addressing. There are also some Special Function Registers (SFRs), which can only be accessed by direct addressing. Since the Scratchpad RAM is only 256 bytes, it can be used only when data contents are small. In the event that larger data contents are present, two selections can be used. One is on-chip MOVX SRAM, the other is the external Data Memory. The on-chip MOVX SRAM can only be accessed by a MOVX instruction, the same as that for external Data Memory. However, the on-chip RAM has the fastest access times.

Figure 1. Memory Map

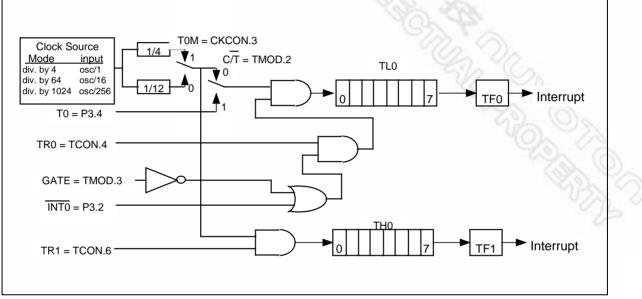

#### **Timer Control**

| <b>'</b> |          |     |     |       |       |            |     |     |

|----------|----------|-----|-----|-------|-------|------------|-----|-----|

| Bit:     | 7        | 6   | 5   | 4     | 3     | 2          | 1   | 0   |

|          | TF1      | TR1 | TF0 | TR0   | IE1   | IT1        | IE0 | IT0 |

| Mnemon   | ic: TCON |     |     | CON N | St. 1 | Address: 8 | 38h |     |

- TF1: Timer 1 overflow flag: This bit is set when Timer 1 overflows. It is cleared automatically when the program does a timer 1 interrupt service routine. Software can also set or clear this bit.

- TR1: Timer 1 run control: This bit is set or cleared by software to turn timer/counter on or off.

- TF0: Timer 0 overflow flag: This bit is set when Timer 0 overflows. It is cleared automatically when the program does a timer 0 interrupt service routine. Software can also set or clear this bit.

- TR0: Timer 0 run control: This bit is set or cleared by software to turn timer/counter on or off.

- IE1: Interrupt 1 edge detect: Set by hardware when an edge/level is detected on INT1. This bit is cleared by hardware when the service routine is vectored to only if the interrupt was edge triggered. Otherwise it follows the pin.

- IT1: Interrupt 1 type control: Set/cleared by software to specify falling edge/ low level triggered external inputs.

- IE0: Interrupt 0 edge detect: Set by hardware when an edge/level is detected on INT0. This bit is cleared by hardware when the service routine is vectored to only if the interrupt was edge triggered. Otherwise it follows the pin.

- IT0: Interrupt 0 type control: Set/cleared by software to specify falling edge/ low level triggered external inputs.

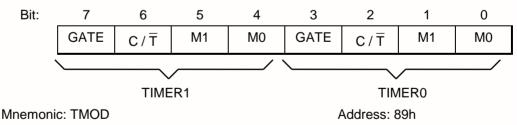

#### **Timer Mode Control**

- GATE: Gating control: When this bit is set, Timer/counter x is enabled only while INTx pin is high and TRx control bit is set. When cleared, Timer x is enabled whenever TRx control bit is set.

- $C/\overline{T}$ : Timer or Counter Select: When cleared, the timer is incremented by internal clocks. When set, the timer counts high-to-low edges of the Tx pin.

### W77E058A

# nuvoTon

M1, M0: Mode Select bits:

#### M1 MO Mode

- 0 0 Mode 0: 8-bits with 5-bit prescale.

- 0 Mode 1: 18-bits, no prescale. 1

- 1 0 Mode 2: 8-bits with auto-reload from THx

- Mode 3: (Timer 0) TL0 is an 8-bit timer/counter controlled by the standard Timer 0 control bits. TH0 is a 8-bit timer only controlled by Timer 1 control bits. (Timer 1) 1 1 Timer/counter is stopped.

#### Timer 0 LSB

|               | Bit:    | 7      | 6     | 5      | 4     | 3          | 2          | 12        | 0          |

|---------------|---------|--------|-------|--------|-------|------------|------------|-----------|------------|

|               |         | TL0.7  | TL0.6 | TL0.5  | TL0.4 | TL0.3      | TL0.2      | TL0.1     | TL0.0      |

|               | Mnemoni | c: TL0 |       |        |       | ŀ          | Address: 8 | 3Ah       |            |

| TL0.7-0:Timer | 0 LSB   |        |       |        |       |            |            |           |            |

| Timer 1 LSB   |         |        |       |        |       |            |            |           |            |

|               | Bit:    | 7      | 6     | 5      | 4     | 3          | 2          | 1         | 0          |

|               |         | TL1.7  | TL1.6 | TL1.5  | TL1.4 | TL1.3      | TL1.2      | TL1.1     | TL1.0      |

|               | Mnemoni | c: TL1 |       |        |       | ŀ          | Address: 8 | 3Bh       |            |

| TL1.7-0:Timer | 1 LSB   |        |       |        |       |            |            |           |            |

| Timer 0 MSE   | 8       |        |       |        |       |            |            |           |            |

|               | Bit:    | 7      | 6     | 5      | 4     | 3          | 2          | 1         | 0          |

|               |         | TH0.7  | TH0.6 | TH0.5  | TH0.4 | TH0.3      | TH0.2      | TH0.1     | TH0.0      |

|               | Mnemoni | c: TH0 |       |        |       | A          | Address: 8 | 3Ch       |            |

| TH0.7-0:Time  | r 0 MSB |        |       |        |       |            |            |           |            |

| Timer 1 MSB   | 2       |        |       |        |       |            |            |           |            |

|               | Bit:    | 7      | 6     | 5      | 4     | 3          | 2          | 1         | 0          |

|               |         | TH1.7  | TH1.6 | TH1.5  | TH1.4 | TH1.3      | TH1.2      | TH1.1     | TH1.0      |

|               | Mnemoni | c: TH1 |       |        | 1     | ļ          | Address: 8 | 3Dh       |            |

| TH1.7-0:Time  | r 1 MSB |        |       |        |       |            |            |           |            |

|               |         |        |       |        |       |            |            |           |            |

|               |         |        |       |        |       |            |            |           |            |

|               |         |        |       |        |       |            |            |           |            |

|               |         |        |       |        |       | Publicatio | on Release | Date: Apr |            |

|               |         |        |       | - 15 - |       |            |            | Re        | vision A10 |

| Serial                                                                                                                                                                                                                                                                                                                        | Port Control                  |                |            |           |            |            |            |             |            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------------|------------|-----------|------------|------------|------------|-------------|------------|

|                                                                                                                                                                                                                                                                                                                               | Bit:                          | 7              | 6          | 5         | 4          | 3          | 2          | 1           | 0          |

|                                                                                                                                                                                                                                                                                                                               |                               | SM0/FE         | SM1        | SM2       | REN        | TB8        | RB8        | TI          | RI         |

|                                                                                                                                                                                                                                                                                                                               | Mnem                          | onic: SCON     |            |           | 172        |            | Address: 9 | 98h         |            |

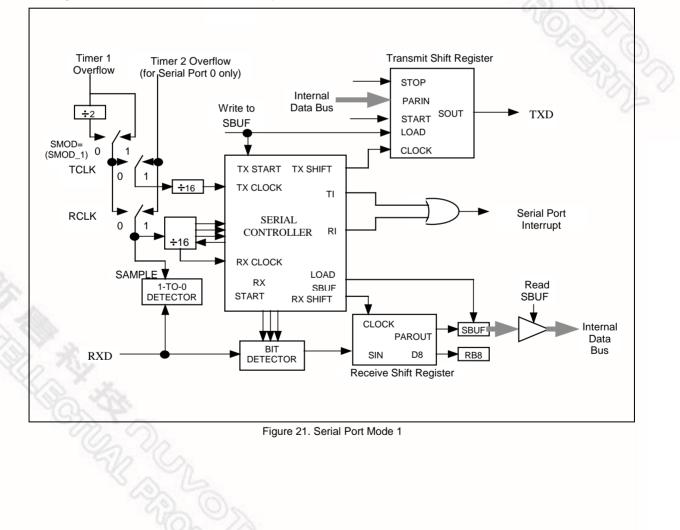

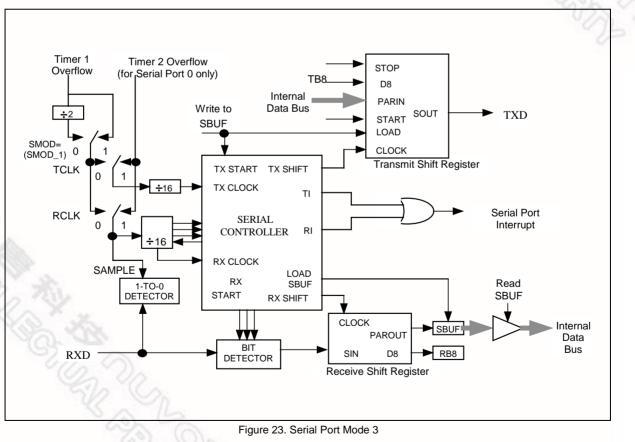

| SM0/FE: Serial port 0, Mode 0 bit or Framing Error Flag: The SMOD0 bit in PCON SFR determines whether this bit acts as SM0 or as FE. The operation of SM0 is described below. When used as FE, this bit will be set to indicate an invalid stop bit. This bit must be manually cleared in software to clear the FE condition. |                               |                |            |           |            |            |            |             |            |

| SM1:                                                                                                                                                                                                                                                                                                                          | Serial port Mo                | de bit 1:      |            |           |            |            |            |             |            |

|                                                                                                                                                                                                                                                                                                                               | SM0 S                         | SM1 Mode       |            | cription  | Length     | E          | Baud rate  |             |            |

|                                                                                                                                                                                                                                                                                                                               | 0                             | 0 0            |            | chronous  | 8          |            | 1/12 Tclk  |             |            |

|                                                                                                                                                                                                                                                                                                                               | 0                             | 1 1            |            | nchronous |            |            | /ariable   |             |            |

|                                                                                                                                                                                                                                                                                                                               | 1                             | 0 2            | -          | nchronous |            | 6          | 64/32 Tclk | SP2         |            |

|                                                                                                                                                                                                                                                                                                                               | 1                             | 1 3            | Asyr       | nchronous | 11         | ١          | /ariable   |             |            |

| SM2:                                                                                                                                                                                                                                                                                                                          |                               |                |            |           |            |            |            |             |            |

| REN:                                                                                                                                                                                                                                                                                                                          | Receive enable                | e: When set t  | o 1 serial | reception | is enabled | , otherwi  | se recept  | ion is disa | bled.      |

| TB8:                                                                                                                                                                                                                                                                                                                          | This is the 9th as desired.   | bit to be trar | nsmitted i | n modes : | 2 and 3. T | his bit is | set and o  | cleared by  | v software |

| RB8:                                                                                                                                                                                                                                                                                                                          | In modes 2 an that was receiv |                |            |           |            | de 1, if s | SM2 = 0,   | RB8 is th   | e stop bit |

- TI: Transmit interrupt flag: This flag is set by hardware at the end of the 8th bit time in mode 0, or at the beginning of the stop bit in all other modes during serial transmission. This bit must be cleared by software.

- RI: Receive interrupt flag: This flag is set by hardware at the end of the 8th bit time in mode 0, or halfway through the stop bits time in the other modes during serial reception. However the restrictions of SM2 apply to this bit. This bit can be cleared only by software.

#### **Serial Data Buffer**

| Bit: | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|------|--------|--------|--------|--------|--------|--------|--------|--------|

|      | SBUF.7 | SBUF.6 | SBUF.5 | SBUF.4 | SBUF.3 | SBUF.2 | SBUF.1 | SBUF.0 |

|      |        |        |        |        |        |        |        |        |

Mnemonic: SBUF

Address: 99h

SBUF.7-0: Serial data on the serial port 0 is read from or written to this location. It actually consists of two separate internal 8-bit registers. One is the receive resister, and the other is the transmit buffer. Any read access gets data from the receive data buffer, while write access is to the transmit data buffer.

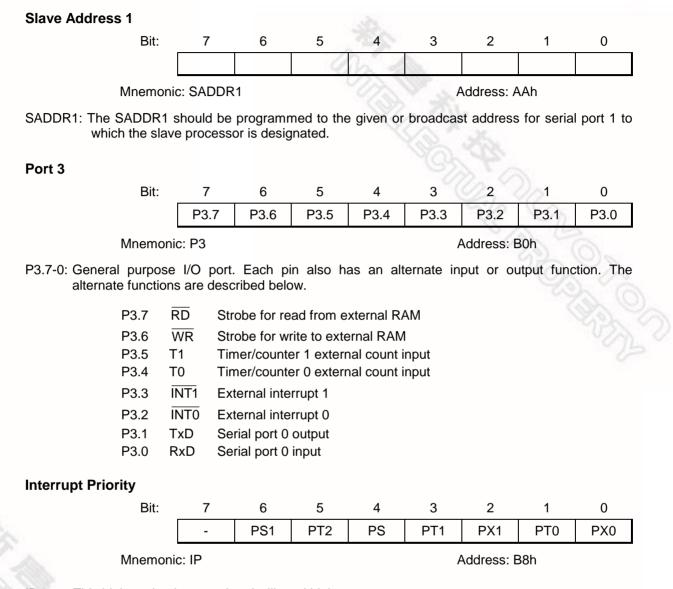

IP.7: This bit is un-implemented and will read high.

- PS1: This bit defines the Serial port 1 interrupt priority. PS = 1 sets it to higher priority level.

- PT2: This bit defines the Timer 2 interrupt priority. PT2 = 1 sets it to higher priority level.

- PS: This bit defines the Serial port 0 interrupt priority. PS = 1 sets it to higher priority level.

- PT1: This bit defines the Timer 1 interrupt priority. PT1 = 1 sets it to higher priority level.

- PX1: This bit defines the External interrupt 1 priority. PX1 = 1 sets it to higher priority level.

- PT0: This bit defines the Timer 0 interrupt priority. PT0 = 1 sets it to higher priority level.

- PX0: This bit defines the External interrupt 0 priority. PX0 = 1 sets it to higher priority level.

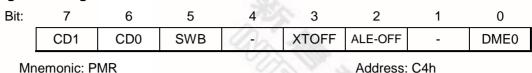

**Power Management Register**

CD1, CD0: Clock Divide Control. These bit selects the number of clocks required to generate one machine cycle. There are three modes including divide by 4, 64 or 1024. Switching between modes must first go back devide by 4 mode. For instance, to go from 64 to 1024 clocks/machine cycle the device must first go from 64 to 4 clocks/machine cycle, and then from 4 to 1024 clocks/machine cycle.

| CD1, | CD0 | Clocks/machine Cycle |

|------|-----|----------------------|

| 0    | 0   | Reserved             |

| 0    | 1   | 4                    |

| 1    | 0   | 64                   |

| 1    | 1   | 1024                 |

- SWB: Switchback Enable. Setting this bit allows an enabled external interrupt or serial port activity to force the CD1,CD0 to divide by 4 state (0,1). The device will switch modes at the start of the jump to interrupt service routine while a external interrupt is enabled and actually recongnized by microcontroller. While a serial port reception, the switchback occurs at the start of the instruction following the falling edge of the start bit.

- XTOFF: Crystal Oscillator Disable. Setting this bit disables the external crystal oscillator. This bit can only be set to 1 while the microcontroller is operating from the RC oscillator. Clearing this bit restarts the crystal oscillator, the XTUP (STATUS.4) bit will be set after crystal oscillator warmed-up has completed.

- ALE0FF: This bit disables the expression of the ALE signal on the device pin during all on-board program and data memory accesses. External memory accesses will automatically enable ALE independent of ALEOFF.

0 = ALE expression is enable; 1 = ALE expression is disable

DME0: This bit determines the on-chip MOVX SRAM to be enabled or disabled. Set this bit to 1 will enable the on-chip 1KB MOVX SRAM.

### **STATUS Register**

| Bit: | 7 | 6   | 5   | 4    | 3     | 2     | 1     | 0     |  |

|------|---|-----|-----|------|-------|-------|-------|-------|--|

| 1    | - | HIP | LIP | XTUP | SPTA1 | SPRA1 | SPTA0 | SPRA0 |  |

|      |   |     |     |      |       |       |       |       |  |

Mnemonic: STATUS

Address: C5h

HIP: High Priority Interrupt Status. When set, it indicates that software is servicing a high priority interrupt. This bit will be cleared when the program executes the corresponding RETI instruction.

- RCLK: Receive Clock Flag: This bit determines the serial port 0 time-base when receiving data in serial modes 1 or 3. If it is 0, then timer 1 overflow is used for baud rate generation, otherwise timer 2 overflow is used. Setting this bit forces timer 2 in baud rate generator mode.

- TCLK: Transmit Clock Flag: This bit determines the serial port 0 time-base when transmitting data in modes 1 and 3. If it is set to 0, the timer 1 overflow is used to generate the baud rate clock otherwise timer 2 overflow is used. Setting this bit forces timer 2 in baud rate generator mode.

- EXEN2: Timer 2 External Enable. This bit enables the capture/reload function on the T2EX pin if Timer 2 is not generating baud clocks for the serial port. If this bit is 0, then the T2EX pin will be ignored, otherwise a negative transition detected on the T2EX pin will result in capture or reload.

- TR2: Timer 2 Run Control. This bit enables/disables the operation of timer 2. Clearing this bit will halt the timer 2 and preserve the current count in TH2, TL2.

- C / T2 : Counter/Timer Select. This bit determines whether timer 2 will function as a timer or a counter. Independent of this bit, the timer will run at 2 clocks per tick when used in baud rate generator mode. If it is set to 0, then timer 2 operates as a timer at a speed depending on T2M bit (CKCON.5), otherwise it will count negative edges on T2 pin.

- CP/RL2 :Capture/Reload Select. This bit determines whether the capture or reload function will be used for timer 2. If either RCLK or TCLK is set, this bit will be ignored and the timer will function in an auto-reload mode following each overflow. If the bit is 0 then auto-reload will occur when timer 2 overflows or a falling edge is detected on T2EX pin if EXEN2 = 1. If this bit is 1, then timer 2 captures will occur when a falling edge is detected on T2EX pin if EXEN2 = 1.

#### **Timer 2 Mode Control**

| Bit:     | 7       | 6   | 5            | 4   | 3    | 2 | 1    | 0    |  |

|----------|---------|-----|--------------|-----|------|---|------|------|--|

|          | HC5     | HC4 | HC3          | HC2 | T2CR | - | T2OE | DCEN |  |

| Mnemonio | : T2MOD | )   | Address: C9h |     |      |   |      |      |  |

- HC5: Hardware Clear INT5 flag. Setting this bit allows the flag of external interrupt 5 to be automatically cleared by hardware while entering the interrupt service routine.

- HC4: Hardware Clear INT4 flag. Setting this bit allows the flag of external interrupt 4 to be automatically cleared by hardware while entering the interrupt service routine.

- HC3: Hardware Clear INT3 flag. Setting this bit allows the flag of external interrupt 3 to be automatically cleared by hardware while entering the interrupt service routine.

- HC3: Hardware Clear INT2 flag. Setting this bit allows the flag of external interrupt 3 to be automatically cleared by hardware while entering the interrupt service routine.

- T2CR: Timer 2 Capture Reset. In the Timer 2 Capture Mode this bit enables/disables hardware automatically reset Timer 2 while the value in TL2 and TH2 have been transferred into the capture register.

- T2OE: Timer 2 Output Enable. This bit enables/disables the Timer 2 clock out function.

- DCEN: Down Count Enable: This bit, in conjunction with the T2EX pin, controls the direction that timer 2 counts in 16-bit auto-reload mode.

| RS1 | RS0 | Register bank | Address |

|-----|-----|---------------|---------|

| 0   | 0   | 0             | 00-07h  |

| 0   | 1   | 1             | 08-0Fh  |

| 1   | 0   | 2             | 10-17h  |

| 1   | 1   | 3             | 18-1Fh  |

|     |     |               |         |

OV: Overflow flag: Set when a carry was generated from the seventh bit but not from the 8th bit as a result of the previous operation, or vice-versa.

F1: User Flag 1: General purpose flag that can be set or cleared by the user by software.

P: Parity flag: Set/cleared by hardware to indicate odd/even number of 1's in the accumulator.

#### Watchdog Control

| Bit: | 7      | 6   | 5 | 4 | 3    | 2        | 0,15  | 0   |

|------|--------|-----|---|---|------|----------|-------|-----|

|      | SMOD_1 | POR | - | - | WDIF | WTRF     | EWT   | RWT |

| Maam |        | NI  |   |   |      | Adress F | NOP 1 |     |

Mnemonic: WDCON

Address: D8h

SMOD\_1: This bit doubles the Serial Port 1 baud rate in mode 1, 2, and 3 when set to 1.

- POR: Power-on reset flag. Hardware will set this flag on a power up condition. This flag can be read or written by software. A write by software is the only way to clear this bit once it is set.

- WDIF: Watchdog Timer Interrupt Flag. If the watchdog interrupt is enabled, hardware will set this bit to indicate that the watchdog interrupt has occurred. If the interrupt is not enabled, then this bit indicates that the time-out period has elapsed. This bit must be cleared by software.

- WTRF: Watchdog Timer Reset Flag. Hardware will set this bit when the watchdog timer causes a reset. Software can read it but must clear it manually. A power-fail reset will also clear the bit. This bit helps software in determining the cause of a reset. If EWT = 0, the watchdog timer will have no affect on this bit.

- EWT: Enable Watchdog timer Reset. Setting this bit will enable the Watchdog timer Reset function.

- RWT: Reset Watchdog Timer. This bit helps in putting the watchdog timer into a know state. It also helps in resetting the watchdog timer before a time-out occurs. Failing to set the RWT before time-out will cause an interrupt, if EWDI (EIE.4) is set, and 512 clocks after that a watchdog timer reset will be generated if EWT is set. This bit is self-clearing by hardware.

The WDCON SFR is set to a 0x0x0xx0b on an external reset. WTRF is set to a 1 on a Watchdog timer reset, but to a 0 on power on/down resets. WTRF is not altered by an external reset. POR is set to 1 by a power-on reset. EWT is set to 0 on a Power-on reset and unaffected by other resets.

All the bits in this SFR have unrestricted read access. POR, EWT, WDIF and RWT require Timed Access procedure to write. The remaining bits have unrestricted write accesses.

#### Accumulator

| Bit:   | 7       | 6     | 5     | 4     | 3     | 2          | 1     | 0     |

|--------|---------|-------|-------|-------|-------|------------|-------|-------|

|        | ACC.7   | ACC.6 | ACC.5 | ACC.4 | ACC.3 | ACC.2      | ACC.1 | ACC.0 |

| Mnemon | ic: ACC |       |       |       | Å     | Address: E | =0h   |       |

ACC.7-0:The A (or ACC) register is the standard 8052 accumulator.

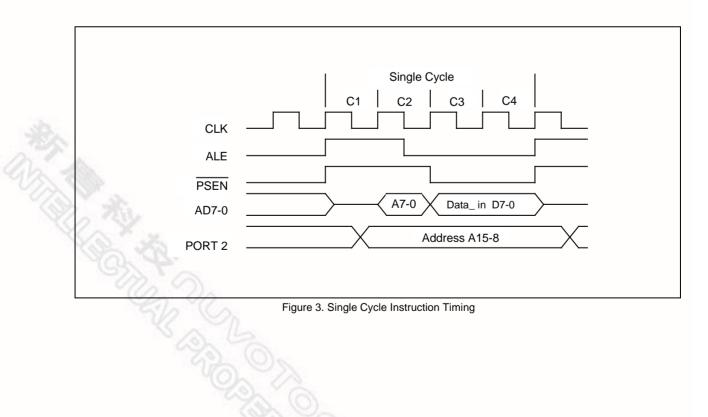

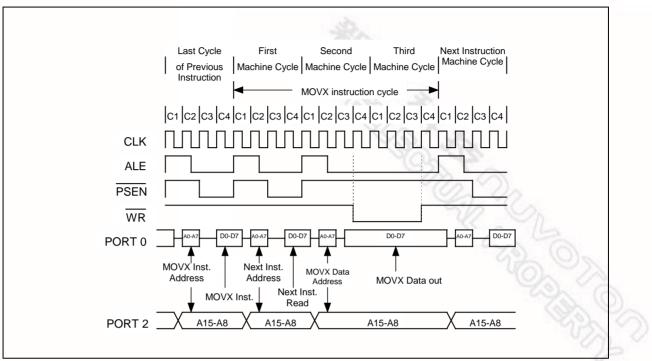

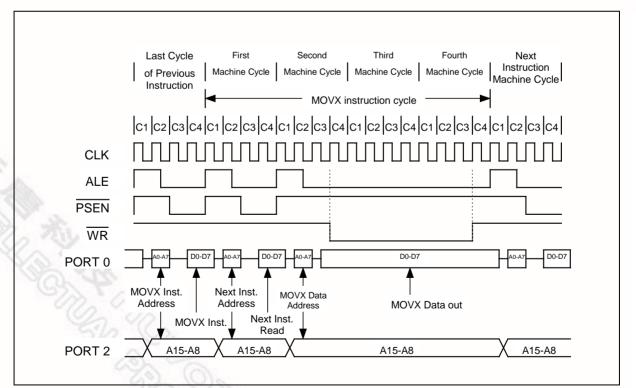

### 8.1 Instruction Timing

The instruction timing for the W77E058 is an important aspect, especially for those users who wish to use software instructions to generate timing delays. Also, it provides the user with an insight into the timing differences between the W77E058 and the standard 8032. In the W77E058 each machine cycle is four clock periods long. Each clock period is designated a state. Thus each machine cycle is made up of four states, C1, C2 C3 and C4, in that order. Due to the reduced time for each instruction execution, both the clock edges are used for internal timing. Hence it is important that the duty cycle of the clock be as close to 50% as possible to avoid timing conflicts. As mentioned earlier, the W77E058 does one op-code fetch per machine cycle. Therefore, in most of the instructions, the number of machine cycles needed to execute the instruction is equal to the number of bytes in the instruction. Of the 256 available op-codes, 128 of them are single cycle instructions. Thus more than half of all opcodes in the W77E058 are executed in just four clock periods. Most of the two-cycle instructions are those that have two byte instruction codes. However there are some instructions that have only one byte instructions, yet they are two cycle instructions. One instruction which is of importance is the MOVX instruction. In the standard 8032, the MOVX instruction is always two machine cycles long. However in the W77E058, the user has a facility to stretch the duration of this instruction from 2 machine cycles to 9 machine cycles. The RD and WR strobe lines are also proportionately elongated. This gives the user flexibility in accessing both fast and slow peripherals without the use of external circuitry and with minimum software overhead. The rest of the instructions are either three, four or five machine cycle instructions. Note that in the W77E058, based on the number of machine cycles, there are five different types, while in the standard 8032 there are only three. However, in the W77E058 each machine cycle is made of only 4 clock periods compared to the 12 clock periods for the standard 8032. Therefore, even though the number of categories has increased, each instruction is at least 1.5 to 3 times faster than the standard 8032 in terms of clock periods.

- 36 -

Figure 9. Data Memory Write with Stretch Value = 1

Figure 10. Data Memory Write with Stretch Value = 2

- 42 -

The selection of instruction rate is going to take effect after a delay of one instruction cycle. Switching to divide by 64 or 1024 mode must first go from divide by 4 mode. This means software can not switch directly between clock/64 and clock/1024 mode. The CPU has to return clock/4 mode first, then go to clock/64 or clock/1024 mode.

The W77E058 allows the user to use internal RC oscillator instead of external crystal. Setting the XT/ $\overline{\text{RG}}$  bit (EXIF.3) selects the crystal or RC oscillator as the clock source. When invoking RC oscillator in Economy mode, software may set the XTOFF bit to turn off the crystal amplifier for saving power. The CPU would run at the clock rate of approximately 2–4 MHz divided by 4, 64 or 1024. The RC oscillator is not precise so that can not be invoked to the operation which needs the accurate time-base such as serial communication. The RGMD(EXIF.2) indicates current clock source. When switching the clock source, CPU needs one instruction cycle delay to take effect new setting. If crystal amplifier is disabled and RC oscillator is present clock source, software must first clear the XTOFF bit to turn on crystal amplifier before switch to crystal operation. Hardware will set the XTUP bit (STATUS.4) once the crystal is warm-up and ready for use. It is unable to set XT/ $\overline{\text{RG}}$  bit to 1 if XTUP = 0.

In Economy mode, the serial port can not receive/transmit data correctly because the baud rate is changed. In some systems, the external interrupts may require the fastest process such that the reducing of operating speed is restricted. In order to solve these dilemmas, the W77E058 offers a switchback feature which allows the CPU back to clock/4 mode immediately when triggered by serial operation or external interrupts. The switchback feature is enabled by setting the SWB bit (PMR.5). A serial port reception/transmission or qualified external interrupt which is enabled and acknowledged without block conditions will cause CPU to return to divide by 4 mode. For the serial port reception, a switchback is generated by a falling edge associated with start bit if the serial port reception is enabled. When a serial port transmission, an instruction which writes a byte of data to serial port buffer will cause a switchback to ensure the correct transmission. The switchback feature is unaffected by serial port interrupt flags. After a switchback is generated, the software can manually return the CPU to Economy mode. Note that the modification of clock control bits CD0 and CD1 will be ignored during serial port transmit/receive when switchback is enabled. The Watchdog timer reset, power-on/fail reset or external reset will force the CPU to return to divide by 4 mode.

### 9.3 Power Down Mode

The device can be put into Power Down mode by writing 1 to bit PCON.1. The instruction that does this will be the last instruction to be executed before the device goes into Power Down mode. In the Power Down mode, all the clocks are stopped and the device comes to a halt. All activity is completely stopped and the power consumption is reduced to the lowest possible value. In this state the ALE and PSEN pins are pulled low. The port pins output the values held by their respective SFRs.

The W77E058 will exit the Power Down mode with a reset or by an external interrupt pin enabled as either level or edge detect. An external reset can be used to exit the Power down state. The high on RST pin terminates the Power Down mode, and restarts the clock. The program execution will restart from 0000h. In the Power down mode, the clock is stopped, so the Watchdog timer cannot be used to provide the reset to exit Power down mode.

The W77E058 can be woken from the Power Down mode by forcing an external interrupt pin activated, provided the corresponding interrupt is enabled, while the global enable(EA) bit is set. If these conditions are met, then the low level on the external pin re-starts the oscillator. Then device executes the interrupt service routine for the corresponding external interrupt. After the interrupt service routine is completed, the program execution returns to the instruction after the one which put the device into

When the 13 bit count reaches 1FFFh the next count will cause it to roll-over to 0000h. The timer overflow flag TFx of the relevant timer is set and if enabled an interrupts will occur. Note that when used as a timer, the time-base may be either clock cycles/12 or clock cycles/4 as selected by the bits TxM of the CKCON SFR.

### 12.3 Timer/Counter 2

Timer/Counter 2 is a 16 bit up/down counter which is configured by the T2MOD register and controlled by the T2CON register. Timer/Counter 2 is equipped with a capture/reload capability. As with the Timer 0 and Timer 1 counters, there exists considerable flexibility in selecting and controlling the clock, and in defining the operating mode. The clock source for Timer/Counter 2 may be selected for either the external T2 pin (C/T2 = 1) or the crystal oscillator, which is divided by 12 or 4 (C/T2 = 0). The clock is then enabled when TR2 is a 1, and disabled when TR2 is a 0.

Figure 13. Timer/Counter 0 Mode 3

#### 12.3.1 Capture Mode

The capture mode is enabled by setting the CP /  $\overline{RL2}$  bit in the T2CON register to a 1. In the capture mode, Timer/Counter 2 serves as a 16 bit up counter. When the counter rolls over from FFFFh to 0000h, the TF2 bit is set, which will generate an interrupt request. If the EXEN2 bit is set, then a negative transition of T2EX pin will cause the value in the TL2 and TH2 register to be captured by the RCAP2L and RCAP2H registers. This action also causes the EXF2 bit in T2CON to be set, which will also generate an interrupt. Setting the T2CR bit (T2MOD.3), the W77E058 allows hardware to reset timer 2 automatically after the value of TL2 and TH2 have been captured.

#### 13.1 Watchdog Control

- WDIF: WDCON.3 Watchdog Timer Interrupt flag. This bit is set whenever the time-out occurs in the watchdog timer. If the Watchdog interrupt is enabled (EIE.4), then an interrupt will occur (if the global interrupt enable is set and other interrupt requirements are met). Software or any reset can clear this bit.

- WTRF: WDCON.2 Watchdog Timer Reset flag. This bit is set whenever a watchdog reset occurs. This bit is useful for determined the cause of a reset. Software must read it, and clear it manually. A Power-fail reset will clear this bit. If EWT = 0, then this bit will not be affected by the watchdog timer.

- EWT: WDCON.1 Enable Watchdog timer Reset. This bit when set to 1 will enable the Watchdog timer reset function. Setting this bit to 0 will disable the Watchdog timer reset function, but will leave the timer running.

- RWT: WDCON.0 Reset Watchdog Timer. This bit is used to clear the Watchdog timer and to restart it. This bit is self-clearing, so after the software writes 1 to it the hardware will automatically clear it. If the Watchdog timer reset is enabled, then the RWT has to be set by the user within 512 clocks of the time-out. If this is not done then a Watchdog timer reset will occur.

### 13.2 Clock Control

WD1, WD0: CKCON.7, CKCON.6 - Watchdog Timer Mode select bits. These two bits select the timeout interval for the watchdog timer. The reset time is 512 clock longer than the interrupt time-out value.

The default Watchdog time-out is 2<sup>17</sup> clocks, which is the shortest time-out period. The EWT, WDIF and RWT bits are protected by the Timed Access procedure. This prevents software from accidentally enabling or disabling the watchdog timer. More importantly, it makes it highly improbable that errant code can enable or disable the watchdog timer.

The 16 states of the counter effectively divide the bit time into 16 slices. The bit detection is done on a best of three basis. The bit detector samples the RxD pin, at the 8th, 9th and 10th counter states. By using a majority 2 of 3 voting system, the bit value is selected. This is done to improve the noise rejection feature of the serial port. If the first bit detected after the falling edge of RxD pin is not 0, then this indicates an invalid start bit, and the reception is immediately aborted. The serial port again looks for a falling edge in the RxD line. If a valid start bit is detected, then the rest of the bits are also detected and shifted into the SBUF.

After shifting in 8 data bits, there is one more shift to do, after which the SBUF and RB8 are loaded and RI is set. However certain conditions must be met before the loading and setting of RI can be done.

- 1. RI must be 0 and

- 2. Either SM2 = 0, or the received stop bit = 1.

If these conditions are met, then the stop bit goes to RB8, the 8 data bits go into SBUF and RI is set. Otherwise the received frame may be lost. After the middle of the stop bit, the receiver goes back to looking for a 1-to-0 transition on the RxD pin.

Publication Release Date: April 17, 2007 Revision A10

shifting in 9 data bits, there is one more shift to do, after which the SBUF and RB8 are loaded and RI is set. However certain conditions must be met before the loading and setting of RI can be done.

- 1. RI must be 0 and

- 2. Either SM2 = 0, or the received stop bit = 1.

If these conditions are met, then the stop bit goes to RB8, the 8 data bits go into SBUF and RI is set. Otherwise the received frame may be lost. After the middle of the stop bit, the receiver goes back to looking for a 1-to-0 transition on the RxD pin.

#### 14.4 Mode 3

This mode is similar to Mode 2 in all respects, except that the baud rate is programmable. The user must first initialize the Serial related SFR SCON before any communication can take place. This involves selection of the Mode and baud rate. The Timer 1 should also be initialized if modes 1 and 3 are used. In all four modes, transmission is started by any instruction that uses SBUF as a destination register. Reception is initiated in Mode 0 by the condition RI = 0 and REN = 1. This will generate a clock on the TxD pin and shift in 8 bits on the RxD pin. Reception is initiated in the other modes by the incoming start bit if REN = 1. The external device will start the communication by transmitting the start bit.

Publication Release Date: April 17, 2007 Revision A10

| SM1 | SM0 | MODE | TYPE    | BAUD CLOCK     | FRAME<br>SIZE | START<br>BIT | STOP<br>BIT | 9TH BIT<br>FUNCTION |

|-----|-----|------|---------|----------------|---------------|--------------|-------------|---------------------|

| 0   | 0   | 0    | Synch.  | 4 or 12 TCLKS  | 8 bits        | No           | No          | None                |

| 0   | 1   | 1    | Asynch. | Timer 1 or 2   | 10 bits       | 1            | 1           | None                |

| 1   | 0   | 2    | Asynch. | 32 or 64 TCLKS | 11 bits       | 1            | 1           | 0, 1                |

| 1   | 1   | 3    | Asynch. | Timer 1 or 2   | 11 bits       | 1            | 1           | 0, 1                |

Table 10. Serial Ports Modes

### 14.5 Framing Error Detection

A Frame Error occurs when a valid stop bit is not detected. This could indicate incorrect serial data communication. Typically the frame error is due to noise and contention on the serial communication line. The W77E058 has the facility to detect such framing errors and set a flag which can be checked by software.

The Frame Error FE(FE\_1) bit is located in SCON.7(SCON1.7). This bit is normally used as SM0 in the standard 8051 family. However, in the W77E058 it serves a dual function and is called SM0/FE (SM0\_1/FE\_1). There are actually two separate flags, one for SM0 and the other for FE. The flag that is actually accessed as SCON.7(SCON1.7) is determined by SMOD0 (PCON.6) bit. When SMOD0 is set to 1, then the FE flag is indicated in SM0/FE. When SMOD0 is set to 0, then the SM0 flag is indicated in SM0/FE.

The FE bit is set to 1 by hardware but must be cleared by software. Note that SMOD0 must be 1 while reading or writing to FE or FE\_1. If FE is set, then any following frames received without any error will not clear the FE flag. The clearing has to be done by software.

### 14.6 Multiprocessor Communications

Multiprocessor communications makes use of the 9th data bit in modes 2 and 3. In the W77E058, the RI flag is set only if the received byte corresponds to the Given or Broadcast address. This hardware feature eliminates the software overhead required in checking every received address, and greatly simplifies the software programmer task.

In the multiprocessor communication mode, the address bytes are distinguished from the data bytes by transmitting the address with the 9th bit set high. When the master processor wants to transmit a block of data to one of the slaves, it first sends out the address of the targeted slave (or slaves). All the slave processors should have their SM2 bit set high when waiting for an address byte. This ensures that they will be interrupted only by the reception of a address byte. The Automatic address recognition feature ensures that only the addressed slave will be interrupted. The address comparison is done in hardware not software.

The addressed slave clears the SM2 bit, thereby clearing the way to receive data bytes. With SM2 = 0, the slave will be interrupted on the reception of every single complete frame of data. The unaddressed slaves will be unaffected, as they will be still waiting for their address. In Mode 1, the 9th bit is the stop bit, which is 1 in case of a valid frame. If SM2 is 1, then RI is set only if a valid frame is received and the received byte matches the Given or Broadcast address.

The Master processor can selectively communicate with groups of slaves by using the Given Address. All the slaves can be addressed together using the Broadcast Address. The addresses for each slave are defined by the SADDR and SADEN SFRs. The slave address is an 8-bit value specified in the SADDR SFR. The SADEN SFR is actually a mask for the byte value in SADDR. If a bit position in

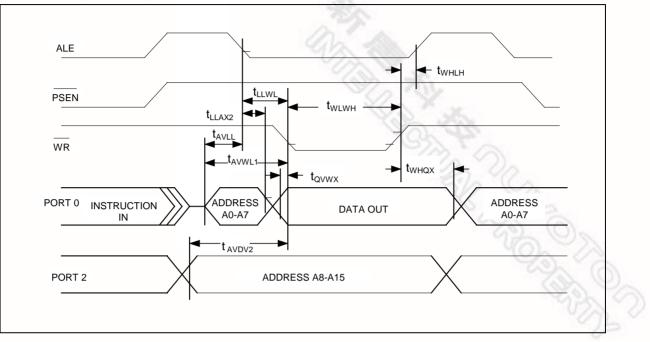

### **Data Memory Write Cycle**

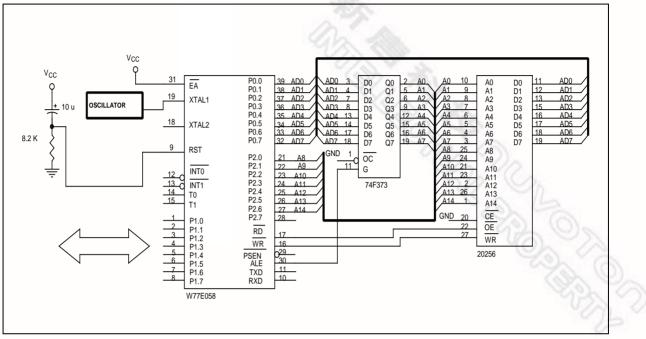

#### 18.2 Expanded External Data Memory and Oscillator

Figure B

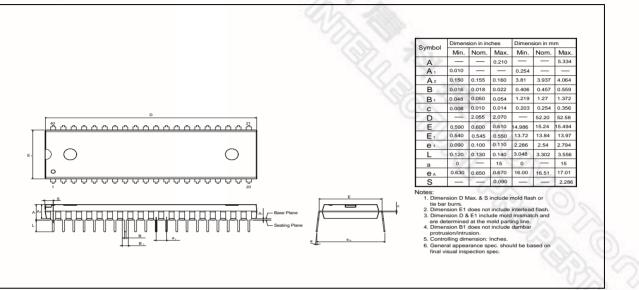

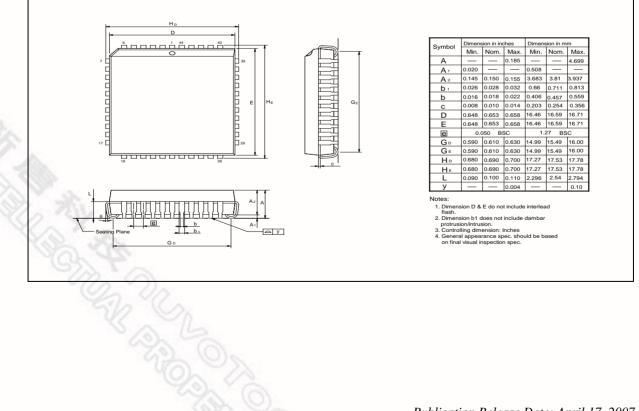

### **19. PACKAGE DIMENSIONS**

### 19.1 40-pin DIP

### 19.2 44-pin PLCC

Publication Release Date: April 17, 2007 Revision A10