# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                              |

| Core Size                  | 32-Bit Single-Core                                                           |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                         |

| Peripherals                | Brown-out Detect/Reset, Cap Sense, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT |

| Number of I/O              | 83                                                                           |

| Program Memory Size        | 384KB (384K x 8)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 12К х 8                                                                      |

| RAM Size                   | 48K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 25x12b; D/A 2x12b                                                        |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 100-LQFP                                                                     |

| Supplier Device Package    | 100-LQFP (14x14)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l152vdt6x       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Contents

| 1 Introduction                                             | 8  |

|------------------------------------------------------------|----|

| 2 Description                                              | 9  |

| 2.1 Device overview                                        |    |

| 2.2 Ultra-low-power device continuum                       |    |

| 2.2.1 Performance                                          |    |

| 2.2.2 Shared peripherals                                   |    |

| 2.2.3 Common system strategy                               |    |

| 2.2.4 Features                                             | 11 |

| 3 Functional overview                                      | 12 |

| 3.1 Low-power modes                                        | 13 |

| 3.2 ARM <sup>®</sup> Cortex <sup>®</sup> -M3 core with MPU |    |

| 3.3 Reset and supply management                            |    |

| 3.3.1 Power supply schemes                                 |    |

| 3.3.2 Power supply supervisor                              |    |

| 3.3.3 Voltage regulator                                    |    |

| 3.3.4 Boot modes                                           |    |

| 3.4 Clock management                                       | 20 |

| 3.5 Low-power real-time clock and backup registers         | 22 |

| 3.6 GPIOs (general-purpose inputs/outputs)                 |    |

| 3.7 Memories                                               |    |

| 3.8 DMA (direct memory access)                             |    |

| 3.9 LCD (liquid crystal display)                           |    |

| 3.10 ADC (analog-to-digital converter)                     |    |

| 3.10.1 Temperature sensor                                  |    |

| 3.10.2 Internal voltage reference (V <sub>REFINT</sub> )   |    |

| 3.11 DAC (digital-to-analog converter)                     | 25 |

| 3.12 Operational amplifier                                 |    |

| 3.13 Ultra-low-power comparators and reference voltage     |    |

| 3.14 System configuration controller and routing interface |    |

| 3.15 Touch sensing                                         |    |

DocID027267 Rev 3

## 2.1 Device overview

# Table 1. Ultra-low-power STM32L151VD-X and STM32L152VD-X device features and peripheral counts

| Periphe                              | eral                | STM32L151VD-X STM32L152VD-X                                                                                |

|--------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------|

| Flash (Kbytes)                       |                     | 384                                                                                                        |

| Data EEPROM (K                       | (bytes)             | 16                                                                                                         |

| RAM (Kbytes)                         |                     | 80                                                                                                         |

| 32 bit                               |                     | 1                                                                                                          |

| Timers                               | General-<br>purpose | 6                                                                                                          |

|                                      | Basic               | 2                                                                                                          |

|                                      | SPI                 | 8(3) <sup>(1)</sup>                                                                                        |

|                                      | l <sup>2</sup> S    | 2                                                                                                          |

| Communication interfaces             | l <sup>2</sup> C    | 2                                                                                                          |

|                                      | USART               | 5                                                                                                          |

|                                      | USB                 | 1                                                                                                          |

| GPIOs                                |                     | 83                                                                                                         |

| Operational amp                      | lifiers             | 2                                                                                                          |

| 12-bit synchroniz<br>Number of chanr |                     | 1<br>25                                                                                                    |

| 12-bit DAC<br>Number of chanr        | nels                | 2<br>2                                                                                                     |

| LCD <sup>(2)</sup><br>COM x SEG      |                     | 1<br>4x44 or 8x40                                                                                          |

| Comparators                          |                     | 2                                                                                                          |

| Capacitive sensi                     | ng channels         | 23                                                                                                         |

| Max. CPU freque                      | ncy                 | 32 MHz                                                                                                     |

| Operating voltage                    |                     | 1.8 V to 3.6 V (down to 1.65 V at power-down) with BOR option<br>1.65 V to 3.6 V without BOR option        |

| Operating tempe                      | ratures             | Ambient operating temperature: -40 °C to 85 °C / -40 °C to 105 °C<br>Junction temperature: -40 to + 110 °C |

| Packages                             |                     | LQFP100,<br>WLCSP104                                                                                       |

1. 5 SPIs are USART configured in synchronous mode emulating SPI master.

2. STM32L152VD-X device only.

| Functionalities depending on the operating power supply range |                                   |                           |                                  |                      |  |  |  |  |

|---------------------------------------------------------------|-----------------------------------|---------------------------|----------------------------------|----------------------|--|--|--|--|

| Operating power supply range                                  | DAC and ADC operation             | USB                       | Dynamic voltage<br>scaling range | I/O operation        |  |  |  |  |

| $V_{DD} = V_{DDA} = 2.0$ to 2.4 V                             | Conversion time up<br>to 500 Ksps | Functional <sup>(2)</sup> | Range 1, Range 2<br>or Range 3   | Full speed operation |  |  |  |  |

| $V_{DD} = V_{DDA} = 2.4 \text{ to } 3.6 \text{ V}$            | Conversion time up<br>to 1 Msps   | Functional <sup>(2)</sup> | Range 1, Range 2<br>or Range 3   | Full speed operation |  |  |  |  |

#### Table 2. Functionalities depending on the operating power supply range (continued)

CPU frequency changes from initial to final must respect "F<sub>CPU</sub> initial < 4\*F<sub>CPU</sub> final" to limit V<sub>CORE</sub> drop due to current consumption peak when frequency increases. It must also respect 5 μs delay between two changes. For example to switch from 4.2 MHz to 32 MHz, the user can switch from 4.2 MHz to 16 MHz, wait 5 μs, then switch from 16 MHz to 32 MHz.

2. Should be USB compliant from I/O voltage standpoint, the minimum  $\rm V_{DD}$  is 3.0 V.

| CPU frequency range                                | Dynamic voltage scaling range |

|----------------------------------------------------|-------------------------------|

| 16 MHz to 32 MHz (1ws)<br>32 kHz to 16 MHz (0ws)   | Range 1                       |

| 8 MHz to 16 MHz (1ws)<br>32 kHz to 8 MHz (0ws)     | Range 2                       |

| 2.1MHz to 4.2 MHz (1ws)<br>32 kHz to 2.1 MHz (0ws) | Range 3                       |

#### Table 3. CPU frequency range depending on dynamic voltage scaling

power ramp-up should guarantee that 1.65 V is reached on  $V_{\text{DD}}$  at least 1 ms after it exits the POR area.

Five BOR thresholds are available through option bytes, starting from 1.8 V to 3 V. To reduce the power consumption in Stop mode, it is possible to automatically switch off the internal reference voltage ( $V_{REFINT}$ ) in Stop mode. The device remains in reset mode when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$  or  $V_{BOR}$ , without the need for any external reset circuit.

Note: The start-up time at power-on is typically 3.3 ms when BOR is active at power-up, the startup time at power-on can be decreased down to 1 ms typically for devices with BOR inactive at power-up.

The device features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}/V_{DDA}$  power supply and compares it to the  $V_{PVD}$  threshold. This PVD offers 7 different levels between 1.85 V and 3.05 V, chosen by software, with a step around 200 mV. An interrupt can be generated when  $V_{DD}/V_{DDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}/V_{DDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

### 3.3.3 Voltage regulator

The regulator has three operation modes: main (MR), low-power (LPR) and power down.

- MR is used in Run mode (nominal regulation)

- LPR is used in the Low-power run, Low-power sleep and Stop modes

- Power down is used in Standby mode. The regulator output is high impedance, the kernel circuitry is powered down, inducing zero consumption but the contents of the registers and RAM are lost except for the standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE crystal 32K osc, RCC\_CSR).

### 3.3.4 Boot modes

At startup, boot pins are used to select one of three boot options:

- Boot from Flash memory

- Boot from System memory

- Boot from embedded RAM

The boot from Flash usually boots at the beginning of the Flash (bank 1). An additional boot mechanism is available through user option byte, to allow booting from bank 2 when bank 2 contains valid code. This dual boot capability can be used to easily implement a secure field software update mechanism.

The boot loader is located in System memory. It is used to reprogram the Flash memory by using USART1, USART2 or USB. See Application note "STM32 microcontroller system memory boot mode" (AN2606) for details.

## 3.4 Clock management

The clock controller distributes the clocks coming from different oscillators to the core and the peripherals. It also manages clock gating for low-power modes and ensures clock robustness. It features:

- Clock prescaler: to get the best trade-off between speed and current consumption, the clock frequency to the CPU and peripherals can be adjusted by a programmable prescaler.

- **Safe clock switching**: clock sources can be changed safely on the fly in run mode through a configuration register.

- **Clock management**: to reduce power consumption, the clock controller can stop the clock to the core, individual peripherals or memory.

- **System clock source**: three different clock sources can be used to drive the master clock SYSCLK:

- 1-24 MHz high-speed external crystal (HSE), that can supply a PLL

- 16 MHz high-speed internal RC oscillator (HSI), trimmable by software, that can supply a PLL

- Multispeed internal RC oscillator (MSI), trimmable by software, able to generate 7 frequencies (65 kHz, 131 kHz, 262 kHz, 524 kHz, 1.05 MHz, 2.1 MHz, 4.2 MHz).

When a 32.768 kHz clock source is available in the system (LSE), the MSI frequency can be trimmed by software down to a ±0.5% accuracy.

- **Auxiliary clock source**: two ultra-low-power clock sources that can be used to drive the LCD controller and the real-time clock:

- 32.768 kHz low-speed external crystal (LSE)

- 37 kHz low-speed internal RC (LSI), also used to drive the independent watchdog. The LSI clock can be measured using the high-speed internal RC oscillator for greater precision.

- **RTC and LCD clock sources:** the LSI, LSE or HSE sources can be chosen to clock the RTC and the LCD, whatever the system clock.

- **USB clock source:** the embedded PLL has a dedicated 48 MHz clock output to supply the USB interface.

- **Startup clock:** after reset, the microcontroller restarts by default with an internal 2 MHz clock (MSI). The prescaler ratio and clock source can be changed by the application program as soon as the code execution starts.

- Clock security system (CSS): this feature can be enabled by software. If a HSE clock failure occurs, the master clock is automatically switched to HSI and a software interrupt is generated if enabled.

- **Clock-out capability (MCO: microcontroller clock output):** it outputs one of the internal clocks for external use by the application.

Several prescalers allow the configuration of the AHB frequency, each APB (APB1 and APB2) domains. The maximum frequency of the AHB and the APB domains is 32 MHz. See *Figure 2* for details on the clock tree.

## 3.7 Memories

The STM32L151VD-X and STM32L152VD-X devices have the following features:

- 80 Kbytes of embedded RAM accessed (read/write) at CPU clock speed with 0 wait states. With the enhanced bus matrix, operating the RAM does not lead to any performance penalty during accesses to the system bus (AHB and APB buses).

- The non-volatile memory is divided into three arrays:

- 384 Kbytes of embedded Flash program memory

- 16 Kbytes of data EEPROM

- Options bytes

Flash program and data EEPROM are divided into two banks, this enables writing in one bank while running code or reading data in the other bank.

The options bytes are used to write-protect or read-out protect the memory (with 4 Kbytes granularity) and/or readout-protect the whole memory with the following options:

- Level 0: no readout protection

- Level 1: memory readout protection, the Flash memory cannot be read from or written to if either debug features are connected or boot in RAM is selected

- Level 2: chip readout protection, debug features (ARM Cortex-M3 JTAG and serial wire) and boot in RAM selection disabled (JTAG fuse)

The whole non-volatile memory embeds the error correction code (ECC) feature.

## 3.8 DMA (direct memory access)

The flexible 12-channel, general-purpose DMA is able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers. The DMA controller supports circular buffer management, avoiding the generation of interrupts when the controller reaches the end of the buffer.

Each channel is connected to dedicated hardware DMA requests, with software trigger support for each channel. Configuration is done by software and transfer sizes between source and destination are independent.

The DMA can be used with the main peripherals: SPI, I<sup>2</sup>C, USART, general-purpose timers, DAC and ADC.

| Pi      |          |          |                         |                 |                                                     | 2VD-X pin definitions (<br>Pin functio        | •                                                  |

|---------|----------|----------|-------------------------|-----------------|-----------------------------------------------------|-----------------------------------------------|----------------------------------------------------|

| LQFP100 | WLCSP104 | Pin name | Pin Type <sup>(1)</sup> | I / O structure | Main<br>function <sup>(2)</sup><br>(after<br>reset) | Alternate functions                           | Additional<br>functions                            |

| 31      | H6       | PA6      | I/O                     | FT              | PA6                                                 | TIM3_CH1/TIM10_CH1/S<br>PI1_MISO/<br>LCD_SEG3 | ADC_IN6/<br>COMP1_INP/<br>OPAMP2_VINP              |

| 32      | К7       | PA7      | I/O                     | FT              | PA7                                                 | TIM3_CH2/TIM11_CH1/<br>SPI1_MOSI/<br>LCD_SEG4 | ADC_IN7/<br>COMP1_INP/<br>OPAMP2_VINM              |

| 33      | L7       | PC4      | I/O                     | FT              | PC4                                                 | LCD_SEG22                                     | ADC_IN14/<br>COMP1_INP                             |

| 34      | M7       | PC5      | I/O                     | FT              | PC5                                                 | LCD_SEG23                                     | ADC_IN15/<br>COMP1_INP                             |

| 35      | J6       | PB0      | I/O                     | тс              | PB0                                                 | TIM3_CH3/LCD_SEG5                             | ADC_IN8/<br>COMP1_INP/<br>OPAMP2_VOUT/<br>VREF_OUT |

| 36      | K6       | PB1      | I/O                     | FT              | PB1                                                 | TIM3_CH4/LCD_SEG6                             | ADC_IN9/<br>COMP1_INP/<br>VREF_OUT                 |

| 37      | M6       | PB2      | I/O                     | FT              | PB2/<br>BOOT1                                       | BOOT1                                         | ADC_IN0b                                           |

| 38      | L6       | PE7      | I/O                     | тс              | PE7                                                 | -                                             | ADC_IN22/<br>COMP1_INP                             |

| 39      | M5       | PE8      | I/O                     | тс              | PE8                                                 | -                                             | ADC_IN23/<br>COMP1_INP                             |

| 40      | M4       | PE9      | I/O                     | тс              | PE9                                                 | TIM2_CH1_ETR                                  | ADC_IN24/<br>COMP1_INP                             |

| 41      | J5       | PE10     | I/O                     | тс              | PE10                                                | TIM2_CH2                                      | ADC_IN25/<br>COMP1_INP                             |

| 42      | L5       | PE11     | I/O                     | FT              | PE11                                                | TIM2_CH3                                      | -                                                  |

| 43      | M3       | PE12     | I/O                     | FT              | PE12                                                | TIM2_CH4/SPI1_NSS                             | -                                                  |

| 44      | K5       | PE13     | I/O                     | FT              | PE13                                                | SPI1_SCK                                      | -                                                  |

| 45      | L4       | PE14     | I/O                     | FT              | PE14                                                | SPI1_MISO                                     | -                                                  |

| 46      | K4       | PE15     | I/O                     | FT              | PE15                                                | SPI1_MOSI                                     | -                                                  |

| 47      | M2       | PB10     | I/O                     | FT              | PB10                                                | TIM2_CH3/I2C2_SCL/<br>USART3_TX/<br>LCD_SEG10 | -                                                  |

## Table 7. STM32L151VD-X and STM32L152VD-X pin definitions (continued)

| P  |

|----|

| Б  |

| ð  |

| ß  |

| õ  |

| Ē  |

| ĕ  |

| 0  |

| su |

|            |        |                                   | Tat          | ole 8. Alte    | rnate fur | nction inp | ut/output | t (continued   | l)          |   |        |   |        |              |

|------------|--------|-----------------------------------|--------------|----------------|-----------|------------|-----------|----------------|-------------|---|--------|---|--------|--------------|

|            |        | Digital alternate function number |              |                |           |            |           |                |             |   |        |   |        |              |

|            | AFIO0  | AFIO1                             | AFIO2        | AFIO3          | AFIO4     | AFIO5      | AFIO6     | AFIO7          | AFIO8       | • | AFIO11 |   | AFIO14 | AFIO15       |

| Port name  |        | Alternate function                |              |                |           |            |           |                |             |   |        |   |        |              |

|            | SYSTEM | TIM2                              | TIM3/4/<br>5 | TIM9/<br>10/11 | I2C1/2    | SPI1/2     | SPI3      | USART1/2/<br>3 | UART4/<br>5 | - | LCD    | - | CPRI   | SYSTEM       |

| PG12       | -      | -                                 | -            | -              | -         | -          | -         | -              | -           | - | -      | - | -      | EVENT<br>OUT |

| PG13       | -      | -                                 | -            | -              | -         | -          | -         | -              | -           | - | -      | - | -      | EVENT<br>OUT |

| PG14       | -      | -                                 | -            | -              | -         | -          | -         | -              | -           | - | -      | - | -      | EVENT<br>OUT |

| PG15       | -      | -                                 | -            | -              | -         | -          | -         | -              | -           | - | -      | - | -      | EVENT<br>OUT |

| PH0OSC_IN  | -      | -                                 | -            | -              | -         | -          | -         | -              | -           | - | -      | - | -      | -            |

| PH1OSC_OUT | -      | -                                 | -            | -              | -         | -          | -         | -              | -           | - | -      | - | -      | -            |

| PH2        | -      | -                                 | -            | -              | -         | -          | -         | -              | -           | - | -      | - | -      | -            |

48/118

DocID027267 Rev 3

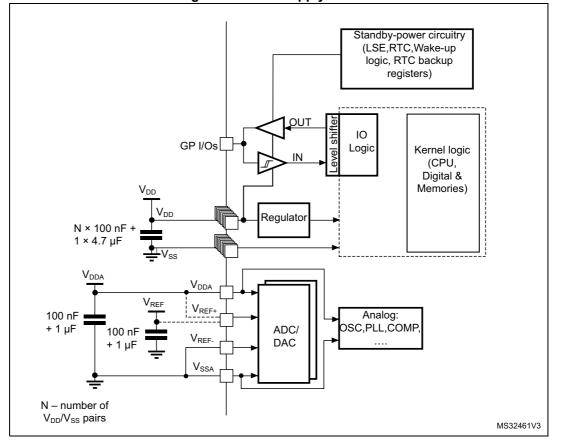

## 6.1.6 Power supply scheme

Figure 8. Power supply scheme

- Positive current injection is not possible on these I/Os. A negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>. I<sub>INJ(PIN)</sub> must never be exceeded. Refer to *Table 9* for maximum allowed input voltage values.

- A positive injection is induced by V<sub>IN</sub> > V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub> < V<sub>SS</sub>. I<sub>INJ(PIN)</sub> must never be exceeded. Refer to *Table 9: Voltage characteristics* for the maximum allowed input voltage values.

- When several inputs are submitted to a current injection, the maximum ΣI<sub>INJ(PIN)</sub> is the absolute sum of the positive and negative injected currents (instantaneous values).

| Symbol           | Ratings                      | Value       | Unit |

|------------------|------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range    | –65 to +150 | °C   |

| TJ               | Maximum junction temperature | 150         | °C   |

#### Table 11. Thermal characteristics

## 6.3 Operating conditions

## 6.3.1 General operating conditions

| Symbol                          | Parameter                                          | Conditions                               | Min  | Max                  | Unit      |  |

|---------------------------------|----------------------------------------------------|------------------------------------------|------|----------------------|-----------|--|

| f <sub>HCLK</sub>               | Internal AHB clock frequency                       | -                                        | 0    | 32                   |           |  |

| f <sub>PCLK1</sub>              | Internal APB1 clock frequency                      | -                                        | 0    | 32                   | MHz       |  |

| f <sub>PCLK2</sub>              | Internal APB2 clock frequency                      | -                                        | 0    | 32                   |           |  |

|                                 |                                                    | BOR detector disabled                    | 1.65 | 3.6                  |           |  |

| V <sub>DD</sub>                 | Standard operating voltage                         | BOR detector enabled, at power on        | 1.8  | 3.6                  | V         |  |

|                                 |                                                    | BOR detector disabled, after power on    | 1.65 | 3.6                  |           |  |

| V <sub>DDA</sub> <sup>(1)</sup> | Analog operating voltage<br>(ADC and DAC not used) | Must be the same voltage as              | 1.65 | 3.6                  | V         |  |

| VDDA` ∕                         | Analog operating voltage<br>(ADC or DAC used)      | V <sub>DD</sub> <sup>(2)</sup>           | 1.8  | 3.6                  | v         |  |

|                                 |                                                    | FT pins; 2.0 V ⊴V <sub>DD</sub>          | -0.3 | 5.5 <sup>(3)</sup>   |           |  |

| V                               |                                                    | FT pins; V <sub>DD</sub> < 2.0 V         | -0.3 | 5.25 <sup>(3)</sup>  | v         |  |

| V <sub>IN</sub>                 | I/O input voltage                                  | BOOT0 pin                                | 0    | 5.5                  | v         |  |

|                                 |                                                    | Any other pin                            | -0.3 | V <sub>DD</sub> +0.3 |           |  |

| Р                               | Power dissipation at TA = 85 °C for                | LQFP100 package                          | -    | 465                  | mW        |  |

| P <sub>D</sub>                  | suffix 6 or TA = 105 °C for suffix $7^{(4)}$       | WLCSP104 package                         | -    | 435                  | 11100     |  |

| Та                              | Ambient temperature for 6 suffix version           | Maximum power dissipation <sup>(5)</sup> | -40  | 85                   | °C        |  |

| IA                              | Ambient temperature for 7 suffix version           | Maximum power dissipation                | -40  | 105                  |           |  |

| TJ                              | Junction temperature range                         | 6 suffix version                         | -40  | 105                  | <b>J°</b> |  |

| IJ                              |                                                    | 7 suffix version                         | -40  | 110                  |           |  |

#### Table 12. General operating conditions

1. When the ADC is used, refer to Table 54: ADC characteristics.

| Symbol          | Parameter                                 | Cond                                                           | litions                                            | f <sub>HCLK</sub> | Тур  | Max <sup>(1)</sup> | Unit |

|-----------------|-------------------------------------------|----------------------------------------------------------------|----------------------------------------------------|-------------------|------|--------------------|------|

|                 |                                           |                                                                |                                                    |                   | -    |                    | •    |

|                 |                                           |                                                                | Range 3, V <sub>CORE</sub> =1.2                    | 1 MHz             | 225  | 500                |      |

|                 |                                           |                                                                | V VOS[1:0] = 11                                    | 2 MHz             | 420  | 750                | μA   |

|                 |                                           |                                                                |                                                    | 4 MHz             | 780  | 1200               |      |

|                 |                                           | f <sub>HSE</sub> = f <sub>HCLK</sub> up to<br>16 MHz included, |                                                    | 4 MHz             | 0.98 | 1.6                |      |

|                 |                                           | f <sub>HSE</sub> = f <sub>HCLK</sub> /2                        | Range 2, V <sub>CORE</sub> =1.5<br>V VOS[1:0] = 10 | 8 MHz             | 1.85 | 2.9                | mA   |

|                 | Supply<br>current in<br>Run mode,<br>code | nt in<br>mode,<br>uted                                         |                                                    | 16 MHz            | 3.6  | 5.2                |      |

| I <sub>DD</sub> |                                           |                                                                | Range 1, V <sub>CORE</sub> =1.8<br>V VOS[1:0] = 01 | 8 MHz             | 2.2  | 3.5                |      |

| (Run<br>from    |                                           |                                                                |                                                    | 16 MHz            | 4.4  | 6.5                |      |

| Flash)          | executed                                  |                                                                |                                                    | 32 MHz            | 8.6  | 12                 |      |

| from FI         | from Flash                                |                                                                | Range 2, V <sub>CORE</sub> =1.5<br>V VOS[1:0] = 10 | 16 MHz            | 3.6  | 5.2                |      |

|                 |                                           |                                                                | Range 1, V <sub>CORE</sub> =1.8<br>V VOS[1:0] = 01 | 32 MHz            | 8.7  | 12.3               |      |

|                 |                                           | MSI clock, 65 kHz                                              | _                                                  | 65 kHz            | 42   | 145                |      |

|                 |                                           | MSI clock, 524 kHz                                             | Range 3, V <sub>CORE</sub> =1.2<br>V VOS[1:0] = 11 | 524 kHz           | 135  | 250                | μA   |

|                 |                                           | MSI clock, 4.2 MHz                                             |                                                    | 4.2 MHz           | 820  | 1200               |      |

#### Table 16. Current consumption in Run mode, code with data processing running from Flash

1. Guaranteed by characterization results, unless otherwise specified.

2. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register).

| Symbol                | Parameter               | Conc                                                                                                                | Conditions                                            |         |      | Max <sup>(1)</sup> | Unit           |

|-----------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|---------|------|--------------------|----------------|

|                       |                         |                                                                                                                     | Range 3,                                              | 1 MHz   | 51   | 220                |                |

|                       |                         |                                                                                                                     | V <sub>CORE</sub> =1.2 V                              | 2 MHz   | 81   | 300                |                |

|                       |                         |                                                                                                                     | VOS[1:0] = 11                                         | 4 MHz   | 140  | 380                | -              |

|                       |                         | $f_{HSE} = f_{HCLK}$ up to                                                                                          | Banga 2                                               | 4 MHz   | 175  | 500                |                |

|                       |                         | 16 MHz included,<br>f <sub>HSE</sub> = f <sub>HCLK</sub> /2                                                         | Range 2,<br>V <sub>CORE</sub> =1.5 V                  | 8 MHz   | 330  | 700                |                |

|                       |                         | above 16 MHz (PLL ON) <sup>(2)</sup>                                                                                | VOS[1:0] = 10                                         | 16 MHz  | 625  | 1100               |                |

|                       |                         |                                                                                                                     | Panga 1                                               | 8 MHz   | 395  | 800                |                |

|                       | Supply current          |                                                                                                                     | Range 1,<br>V <sub>CORE</sub> =1.8 V                  | 16 MHz  | 760  | 1250               |                |

|                       | in Sleep<br>mode, Flash |                                                                                                                     | VOS[1:0] = 01                                         | 32 MHz  | 1700 | 2700               |                |

|                       | OFF                     | HSI clock source                                                                                                    | Range 2,<br>V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10 | 16 MHz  | 670  | 1100               | -              |

|                       |                         | (16 MHz)                                                                                                            | Range 1,<br>V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01 | 32 MHz  | 1750 | 2700               |                |

|                       |                         | MSI clock, 65 kHz                                                                                                   | Range 3,<br>V <sub>CORE</sub> =1.2 V                  | 65 kHz  | 19   | 92                 |                |

|                       |                         | MSI clock, 524 kHz                                                                                                  |                                                       | 524 kHz | 33   | 110                |                |

| (Clean)               |                         | MSI clock, 4.2 MHz                                                                                                  | VOS[1:0] = 11                                         | 4.2 MHz | 150  | 273                |                |

| <sub>DD</sub> (Sleep) |                         | $f_{HSE} = f_{HCLK}$ up to<br>16 MHz included,<br>$f_{HSE} = f_{HCLK}/2$<br>above 16 MHz (PLL<br>ON) <sup>(2)</sup> | Range 3,<br>V <sub>CORE</sub> =1.2 V<br>VOS[1:0] = 11 | 1 MHz   | 63   | 250                | - μΑ<br>-<br>- |

|                       |                         |                                                                                                                     |                                                       | 2 MHz   | 93   | 300                |                |

|                       |                         |                                                                                                                     |                                                       | 4 MHz   | 155  | 380                |                |

|                       |                         |                                                                                                                     | Range 2,<br>V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10 | 4 MHz   | 190  | 500                |                |

|                       |                         |                                                                                                                     |                                                       | 8 MHz   | 340  | 700                |                |

|                       | Supply current          |                                                                                                                     |                                                       | 16 MHz  | 640  | 1120               |                |

|                       | in Sleep                |                                                                                                                     | Range 1,                                              | 8 MHz   | 410  | 800                |                |

|                       | mode, Flash<br>ON       |                                                                                                                     | V <sub>CORE</sub> =1.8 V                              | 16 MHz  | 770  | 1300               |                |

|                       |                         |                                                                                                                     | VOS[1:0] = 01                                         | 32 MHz  | 1750 | 2700               |                |

|                       |                         | HSI clock source                                                                                                    | Range 2,<br>V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10 | 16 MHz  | 690  | 1160               |                |

|                       |                         | (16 MHz)                                                                                                            | Range 1,<br>V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01 | 32 MHz  | 1750 | 2800               |                |

|                       | Supply current          | MSI clock, 65 kHz                                                                                                   | Range 3,                                              | 65 kHz  | 31   | 105                | 1              |

|                       | in Sleep<br>mode, Flash | MSI clock, 524 kHz                                                                                                  | V <sub>CORE</sub> =1.2V                               | 524 kHz | 45   | 125                | 1              |

|                       | ON                      | MSI clock, 4.2 MHz                                                                                                  | VOS[1:0] = 11                                         | 4.2 MHz | 160  | 290                | 1              |

1. Guaranteed by characterization results, unless otherwise specified.

2. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register)

#### 6.3.6 **External clock source characteristics**

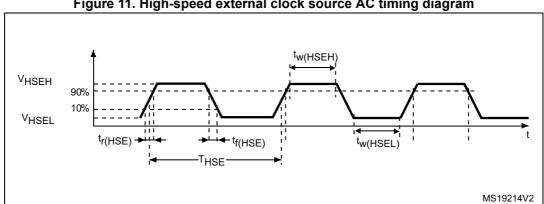

## High-speed external user clock generated from an external source

In bypass mode the HSE oscillator is switched off and the input pin is a standard GPIO.The external clock signal has to respect the I/O characteristics in Section 6.3.12. However, the recommended clock input waveform is shown in Figure 11.

| Symbol                                       | Parameter                           | Conditions                  | Min             | Тур | Max                | Unit |

|----------------------------------------------|-------------------------------------|-----------------------------|-----------------|-----|--------------------|------|

| f                                            | User external clock source          | CSS is on or<br>PLL is used | 1               | 8   | 32                 | MHz  |

| f <sub>HSE_ext</sub>                         | requency                            | CSS is off, PLL<br>not used | 0               | 8   | 32                 | MHz  |

| V <sub>HSEH</sub>                            | OSC_IN input pin high level voltage |                             | $0.7V_{DD}$     | -   | V <sub>DD</sub>    | v    |

| V <sub>HSEL</sub>                            | OSC_IN input pin low level voltage  |                             | V <sub>SS</sub> | -   | $0.3V_{\text{DD}}$ | v    |

| t <sub>w(HSEH)</sub><br>t <sub>w(HSEL)</sub> | OSC_IN high or low time             | -                           | 12              | -   | -                  | ns   |

| t <sub>r(HSE)</sub><br>t <sub>f(HSE)</sub>   | OSC_IN rise or fall time            |                             | -               | -   | 20                 | 113  |

| C <sub>in(HSE)</sub>                         | OSC_IN input capacitance            |                             | -               | 2.6 | -                  | pF   |

1. Guaranteed by design.

Figure 11. High-speed external clock source AC timing diagram

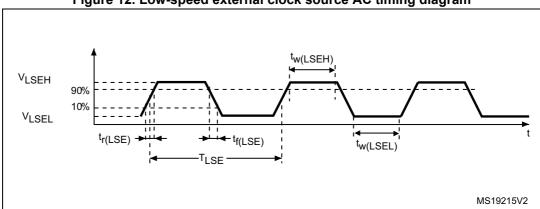

#### Low-speed external user clock generated from an external source

The characteristics given in the following table result from tests performed using a low-speed external clock source, and under the conditions summarized in *Table 12*.

| Symbol                                       | Parameter                               | Conditions | Min                | Тур    | Max                | Unit |

|----------------------------------------------|-----------------------------------------|------------|--------------------|--------|--------------------|------|

| f <sub>LSE_ext</sub>                         | User external clock source<br>frequency |            | 1                  | 32.768 | 1000               | kHz  |

| V <sub>LSEH</sub>                            | OSC32_IN input pin high level voltage   |            | 0.7V <sub>DD</sub> | -      | V <sub>DD</sub>    | v    |

| V <sub>LSEL</sub>                            | OSC32_IN input pin low level voltage    | -          | V <sub>SS</sub>    | -      | 0.3V <sub>DD</sub> | v    |

| t <sub>w(LSEH)</sub><br>t <sub>w(LSEL)</sub> | OSC32_IN high or low time               |            | 465                | -      | -                  | ns   |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub>   | OSC32_IN rise or fall time              |            | -                  | -      | 10                 | 115  |

| C <sub>IN(LSE)</sub>                         | OSC32_IN input capacitance              | -          | -                  | 0.6    | -                  | pF   |

Table 26. Low-speed external user clock characteristics<sup>(1)</sup>

1. Guaranteed by design.

Figure 12. Low-speed external clock source AC timing diagram

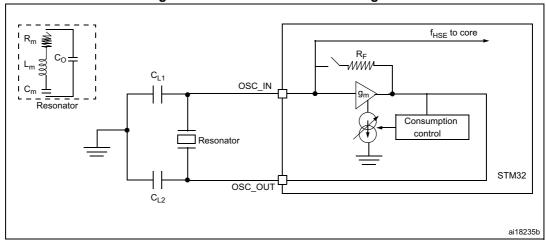

## High-speed external clock generated from a crystal/ceramic resonator

The high-speed external (HSE) clock can be supplied with a 1 to 24 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 27*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

Figure 13. HSE oscillator circuit diagram

1. R<sub>EXT</sub> value depends on the crystal characteristics.

#### Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 28*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| r                     |                                                                                               |                                       |     |        |     |      |  |  |

|-----------------------|-----------------------------------------------------------------------------------------------|---------------------------------------|-----|--------|-----|------|--|--|

| Symbol                | Parameter                                                                                     | Conditions                            | Min | Тур    | Max | Unit |  |  |

| f <sub>LSE</sub>      | Low speed external oscillator<br>frequency                                                    | -                                     | -   | 32.768 | -   | kHz  |  |  |

| R <sub>F</sub>        | Feedback resistor -                                                                           |                                       | -   | 1.2    | -   | MΩ   |  |  |

| C <sup>(2)</sup>      | Recommended load capacitance versus equivalent serial resistance of the crystal $(R_S)^{(3)}$ | R <sub>S</sub> = 30 kΩ                | -   | 8      | -   | pF   |  |  |

| I <sub>LSE</sub>      | LSE driving current                                                                           | $V_{DD}$ = 3.3 V, $V_{IN}$ = $V_{SS}$ | -   | -      | 1.1 | μA   |  |  |

|                       |                                                                                               | V <sub>DD</sub> = 1.8 V               | -   | 450    | -   |      |  |  |

| I <sub>DD (LSE)</sub> | LSE oscillator current<br>consumption                                                         | V <sub>DD</sub> = 3.0 V               | -   | 600    | -   | nA   |  |  |

|                       |                                                                                               | V <sub>DD</sub> = 3.6V                | -   | 750    | -   |      |  |  |

| 9 <sub>m</sub>        | Oscillator transconductance                                                                   | -                                     | 3   | -      | -   | µA/V |  |  |

| $t_{SU(LSE)}^{(4)}$   | Startup time                                                                                  | $V_{\text{DD}}$ is stabilized         | -   | 1      | -   | S    |  |  |

| Table 28. LSE oscillator characterist | ics (f <sub>LSE</sub> = 32.768 kHz) <sup>(1)</sup> |

|---------------------------------------|----------------------------------------------------|

|---------------------------------------|----------------------------------------------------|

1. Guaranteed by characterization results.

2. Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

The oscillator selection can be optimized in terms of supply current using an high quality resonator with small R<sub>S</sub> value for example MSIV-TIN32.768kHz. Refer to crystal manufacturer for more details.

| Driver characteristics <sup>(1)</sup> |                                 |                                |     |     |   |  |  |

|---------------------------------------|---------------------------------|--------------------------------|-----|-----|---|--|--|

| Symbol Parameter Conditions Min Max   |                                 |                                |     |     |   |  |  |

| t <sub>rfm</sub>                      | Rise/ fall time matching        | t <sub>r</sub> /t <sub>f</sub> | 90  | 110 | % |  |  |

| V <sub>CRS</sub>                      | Output signal crossover voltage |                                | 1.3 | 2.0 | V |  |  |

#### Table 51. USB: full speed electrical characteristics (continued)

1. Guaranteed by design.

2. Measured from 10% to 90% of the data signal. For more detailed informations, please refer to USB Specification - Chapter 7 (version 2.0).

## **I2S characteristics**

| Symbol                | Parameter                                           | Conditions                                | Min      | Max                   | Unit   |

|-----------------------|-----------------------------------------------------|-------------------------------------------|----------|-----------------------|--------|

| f <sub>MCK</sub>      | I2S Main Clock Output                               |                                           | 256 x 8K | 256xFs <sup>(1)</sup> | MHz    |

| £                     | 120 alask fraguerau                                 | Master data: 32 bits                      | -        | 64xFs                 | N 41 I |

| f <sub>CK</sub>       | I2S clock frequency                                 | Slave data: 32 bits                       | -        | 64xFs                 | MHz    |

| D <sub>CK</sub>       | I2S clock frequency duty cycle Slave receiver, 48KH |                                           | 30       | 70                    | %      |

| t <sub>r(CK)</sub>    | I2S clock rise time                                 | Consoltive load CL = 20nE                 |          | 8                     |        |

| t <sub>f(CK)</sub>    | I2S clock fall time                                 | Capacitive load CL=30pF                   | -        | 8                     |        |

| t <sub>v(WS)</sub>    | WS valid time                                       | Master mode                               | 4        | 24                    |        |

| t <sub>h(WS)</sub>    | WS hold time                                        | Master mode                               | 0        | -                     |        |

| t <sub>su(WS)</sub>   | WS setup time                                       | Slave mode                                | 15       | -                     |        |

| t <sub>h(WS)</sub>    | WS hold time                                        | Slave mode                                | 0        | -                     |        |

| $t_{su(SD_MR)}$       | Data input setup time                               | Master receiver                           | 8        | -                     |        |

| $t_{su(SD\_SR)}$      | Data input setup time                               | Slave receiver                            | 9        | -                     |        |

| t <sub>h(SD_MR)</sub> | Data input hold time                                | Master receiver                           | 5        | -                     | ns     |

| t <sub>h(SD_SR)</sub> |                                                     | Slave receiver                            | 4        | -                     |        |

| t <sub>v(SD_ST)</sub> | Data output valid time                              | Slave transmitter<br>(after enable edge)  | -        | 64                    |        |

| t <sub>h(SD_ST)</sub> | Data output hold time                               | Slave transmitter<br>(after enable edge)  | 22       | -                     |        |

| t <sub>v(SD_MT)</sub> | Data output valid time                              | Master transmitter<br>(after enable edge) | -        | 12                    |        |

| t <sub>h(SD_MT)</sub> | Data output hold time                               | Master transmitter<br>(after enable edge) | 8        | -                     |        |

#### Table 52. I2S characteristics

1. The maximum for 256xFs is 8 MHz

Note: Refer to the I2S section of the product reference manual for more details about the sampling frequency (Fs),  $f_{MCK}$ ,  $f_{CK}$  and  $D_{CK}$  values. These values reflect only the digital peripheral behavior, source clock precision might slightly change them. DCK depends mainly on the

## 6.3.18 DAC electrical specifications

Data guaranteed by design, unless otherwise specified.

| Symbol                              | Parameter                                             | Conditions                                                                         | Min | Тур              | Мах                         | Unit |

|-------------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------|-----|------------------|-----------------------------|------|

| V <sub>DDA</sub>                    | Analog supply voltage                                 | -                                                                                  | 1.8 | -                | 3.6                         |      |

| V <sub>REF+</sub>                   | Reference supply voltage                              | V <sub>REF+</sub> must always be below<br>V <sub>DDA</sub>                         | 1.8 | -                | 3.6                         | V    |

| V <sub>REF-</sub>                   | Lower reference voltage                               | -                                                                                  |     | V <sub>SSA</sub> |                             |      |

| . (1)                               | Current consumption on                                | No load, middle code (0x800)                                                       | -   | 130              | 220                         |      |

| I <sub>DDVREF+</sub> <sup>(1)</sup> | V <sub>REF+</sub> supply<br>V <sub>REF+</sub> = 3.3 V | No load, worst code (0x000)                                                        | -   | 220              | 350                         |      |

| . (1)                               | Current consumption on                                | No load, middle code (0x800)                                                       | -   | 210              | 320                         | μA   |

| I <sub>DDA</sub> <sup>(1)</sup>     | V <sub>DDA</sub> supply<br>V <sub>DDA</sub> = 3.3 V   | No load, worst code (0xF1C)                                                        | -   | 320              | 520                         |      |

| $R_L^{(2)}$                         | Resistive load                                        |                                                                                    | 5   | -                | -                           | kΩ   |

| C <sub>L</sub> <sup>(2)</sup>       | Capacitive load                                       | DAC output buffer ON                                                               | -   | -                | 50                          | pF   |

| R <sub>O</sub>                      | Output impedance                                      | DAC output buffer OFF                                                              | 12  | 16               | 20                          | kΩ   |

| V <sub>DAC_OUT</sub>                | Voltage on DAC_OUT output                             | DAC output buffer ON                                                               | 0.2 | -                | V <sub>DDA</sub> – 0.2      | v    |

|                                     |                                                       | DAC output buffer OFF                                                              | 0.5 | -                | V <sub>REF+</sub> –<br>1LSB | mV   |

| DNL <sup>(1)</sup>                  |                                                       | $C_L \le 50 \text{ pF}, \text{ R}_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON | -   | 1.5              | 3                           |      |

|                                     | linearity <sup>(3)</sup>                              | No R <sub>L</sub> , C <sub>L</sub> $\leq$ 50 pF<br>DAC output buffer OFF           | -   | 1.5              | 3                           |      |

| INL <sup>(1)</sup>                  | Integral non linearity <sup>(4)</sup>                 | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON         | -   | 2                | 4                           |      |

|                                     | integral non intearity.                               | No R <sub>L</sub> , C <sub>L</sub> ≤50 pF<br>DAC output buffer OFF                 | -   | 2                | 4                           | LSB  |

| Offset <sup>(1)</sup>               | Offset error at code                                  | $C_{L} \le 50 \text{ pF}, R_{L} \ge 5 \text{ k}\Omega$<br>DAC output buffer ON     | -   | ±10              | ±25                         |      |

| Unset /                             | 0x800 <sup>(5)</sup>                                  | No R <sub>L</sub> , C <sub>L</sub> $\leq$ 50 pF<br>DAC output buffer OFF           | -   | ±5               | ±8                          |      |

| Offset1 <sup>(1)</sup>              | Offset error at code 0x001 <sup>(6)</sup>             | No $R_L$ , $C_L \le 50 \text{ pF}$<br>DAC output buffer OFF                        | -   | ±1.5             | ±5                          |      |

## 7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

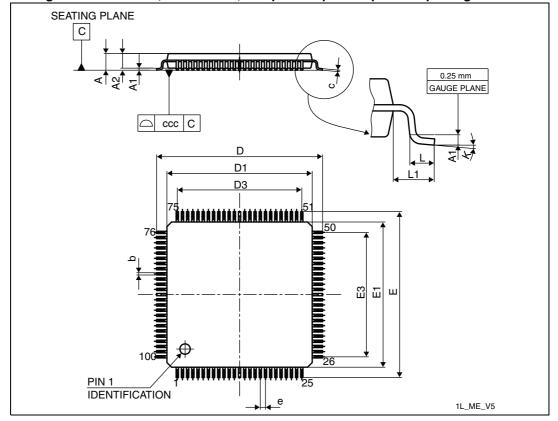

# 7.1 LQFP100, 14 x 14 mm, 100-pin low-profile quad flat package information

Figure 28. LQFP100, 14 x 14 mm, 100-pin low-profile quad flat package outline

1. Drawing is not to scale.

| Symbol |       | millimeters |       |        | inches <sup>(1)</sup> |        |

|--------|-------|-------------|-------|--------|-----------------------|--------|

| Symbol | Min   | Тур         | Max   | Min    | Тур                   | Max    |

| А      | -     | -           | 1.600 | -      | -                     | 0.0630 |

| A1     | 0.050 | -           | 0.150 | 0.0020 | -                     | 0.0059 |

| A2     | 1.350 | 1.400       | 1.450 | 0.0531 | 0.0551                | 0.0571 |

DocID027267 Rev 3

| 0k.al              |       | millimeters |       | inches <sup>(1)</sup> |        |        |  |

|--------------------|-------|-------------|-------|-----------------------|--------|--------|--|

| Symbol             | Min   | Тур         | Max   | Min                   | Тур    | Max    |  |

| А                  | 0.525 | 0.555       | 0.585 | 0.0207                | 0.0219 | 0.023  |  |

| A1                 | -     | 0.175       | -     | -                     | 0.0069 | -      |  |

| A2                 | -     | 0.38        | -     | -                     | 0.015  | -      |  |

| A3 <sup>(2)</sup>  | -     | 0.025       | -     | -                     | 0.001  | -      |  |

| ø b <sup>(3)</sup> | 0.22  | 0.25        | 0.28  | 0.0087                | 0.0098 | 0.011  |  |

| D                  | 4.06  | 4.095       | 4.13  | 0.1598                | 0.1612 | 0.1626 |  |

| E                  | 5.059 | 5.094       | 5.129 | 0.1992                | 0.2006 | 0.2019 |  |

| е                  | -     | 0.4         | -     | -                     | 0.0157 | -      |  |

| e1                 | -     | 3.2         | -     | -                     | 0.126  | -      |  |

| e2                 | -     | 4.4         | -     | -                     | 0.1732 | -      |  |

| F                  | -     | 0.447       | -     | -                     | 0.0176 | -      |  |

| G                  | -     | 0.347       | -     | -                     | 0.0137 | -      |  |

| aaa                | -     | -           | 0.1   | -                     | -      | 0.0039 |  |

| bbb                | -     | -           | 0.1   | -                     | -      | 0.0039 |  |

| CCC                | -     | -           | 0.1   | -                     | -      | 0.0039 |  |

| ddd                | -     | -           | 0.05  | -                     | -      | 0.002  |  |

| eee                | -     | -           | 0.05  | -                     | -      | 0.002  |  |

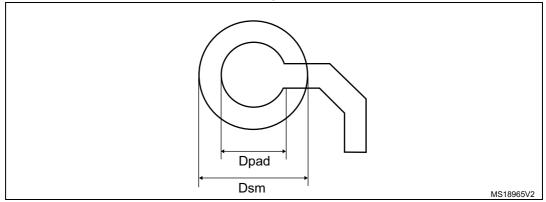

Table 65. WLCSP104, 0.4 mm pitch wafer level chip scale package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

2. Back side coating.

3. Dimension is measured at the maximum bump diameter parallel to primary datum Z.

## Figure 32. WLCSP104, 0.4 mm pitch wafer level chip scale package recommended footprint

#### IMPORTANT NOTICE – PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics – All rights reserved

DocID027267 Rev 3