#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | H8S/2600                                                                       |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, SCI, SSU, UART/USART, USB                     |

| Peripherals                | DMA, POR, PWM, WDT                                                             |

| Number of I/O              | 96                                                                             |

| Program Memory Size        | 128KB (128K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 48K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b; D/A 2x8b                                                           |

| Oscillator Type            | External                                                                       |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 144-LQFP                                                                       |

| Supplier Device Package    | 144-LFQFP (20x20)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r4f24565nvfqv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                      | Pin No.                     |                         |                                 |                             |        |                                                                                         |

|----------------------|-----------------------------|-------------------------|---------------------------------|-----------------------------|--------|-----------------------------------------------------------------------------------------|

|                      |                             | H8S/2456,               | H8S/2456R                       | H8S/2454                    | -      |                                                                                         |

|                      |                             |                         |                                 | PLQP0120LA-A,               | -      |                                                                                         |

| Туре                 | Symbol                      | PLQP0144KA-A            | PTLG0145JB-A                    | PLQP0120KA-A                | I/O    | Function                                                                                |

| Bus                  | WAIT-A                      | 84                      | J11                             | 69                          | Input  | Requests insertion of a wait state in                                                   |

| control              | WAIT-B                      | 56                      | N7                              | 47                          |        | the bus cycles when accessing an external 3-state address space.                        |

|                      | OE-A                        | 38                      | M2                              | 69                          | Output | Output enable signal when                                                               |

|                      | OE-B                        | 137                     | A5                              | 113                         |        | accessing the DRAM space.                                                               |

|                      | CKE-A*1                     | 38                      | M2                              |                             | Output | Clock enable signal when the                                                            |

|                      | CKE-B*1                     | 137                     | A5                              | —                           |        | synchronous DRAM interface is set.                                                      |

| Interrupts           | NMI                         | 40                      | N1                              | 32                          | Input  | Nonmaskable interrupt request pin.<br>This pin should be fixed high when<br>not used.   |

|                      | IRQ15-A                     | 86, 85,                 | H10, H12, C13,                  | D12, —                      |        | These pins request a maskable                                                           |

|                      | to<br>IRQ8-A* <sup>2</sup>  | 106 to 104,<br>83 to 81 | D10, J10, K13, J                | 112                         |        | interrupt.                                                                              |

|                      |                             |                         |                                 |                             | -      | The input pins of IRQn-A and IRQn-                                                      |

|                      | IRQ7-A to<br>IRQ0-A         | 31 to 28,<br>136 to 133 | J3, K2, J1, K4, E<br>C6, B5, A6 | 04, 29 to 26,<br>112 to 109 | _      | B are selected by the IRQ pin select<br>register (ITSR) of the interrupt<br>controller. |

|                      | IRQ15-B                     | 58 to 56                | K7, L8, N7, L6                  |                             |        | (n = 0  to  15, m = 0  to  8, 13  to  15  for                                           |

|                      | to<br>IRQ13-B* <sup>2</sup> | 51                      |                                 |                             |        | the H8S/2456R Group and                                                                 |

|                      | IRQ8-B*2                    |                         |                                 |                             |        | H8S/2456)<br>(n = 0 to 7 for the H8S/2454 Group)                                        |

|                      | IRQ7-B to                   | 38, 37,                 | M2, N2, M8, N8,                 | K8, 102 to 95               | _      |                                                                                         |

|                      | IRQ0-B                      | 61 to 59,<br>34, 33, 3  | K3, L2, C2                      |                             |        |                                                                                         |

| DMA                  | DREQ1                       | 82                      | K13, J12                        | 35                          | Input  | These signals request DMAC                                                              |

| controller<br>(DMAC) | DREQ0                       | 81                      |                                 | 34                          |        | activation.                                                                             |

| (DNAO)               | TEND1                       | 104                     | D10                             | 37                          | Output | These signals indicate the end of                                                       |

|                      | TEND0                       | 83                      | J10                             | 36                          |        | DMAC data transfer.                                                                     |

|                      | DACK1                       | 106                     | C13                             | 39                          | Output | DMAC single address transfer                                                            |

|                      | DACK0                       | 105                     | D12                             | 38                          |        | acknowledge signals.                                                                    |

| EXDMA                | EDREQ3                      | 33                      | L2                              | _                           | Input  | These signals request EXDMAC                                                            |

| controller           | EDREQ2                      | 3                       | C2                              |                             |        | activation.                                                                             |

| (EXDMAC)<br>*2       | ETEND3                      | 59                      | K8                              | _                           | Output | These signals indicate the end of                                                       |

|                      | ETEND2                      | 34                      | K3                              |                             |        | EXDMAC data transfer.                                                                   |

|                      | EDACK3                      | 61                      | M8                              | _                           | Output | EXDMAC single address transfer                                                          |

|                      | EDACK2                      | 60                      | N8                              |                             |        | acknowledge signals.                                                                    |

|                      |                             |                         |                                 |                             |        |                                                                                         |

| (1) Operation field                                                   | only                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                              |                                                                                                                                                                                                                |  |  |  |

|-----------------------------------------------------------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                                                       | ot                                                                    | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | NOP, RTS, etc.                                                                                                                                               |                                                                                                                                                                                                                |  |  |  |

| (2) Operation field a                                                 | and register field                                                    | ds                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                              |                                                                                                                                                                                                                |  |  |  |

| C                                                                     | р                                                                     | rn                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ADD.B Rn, Rm, etc.                                                                                                                                           |                                                                                                                                                                                                                |  |  |  |

| (3) Operation field, register fields, and effective address extension |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                              |                                                                                                                                                                                                                |  |  |  |

|                                                                       | -                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | MOV.B @(d:16, Rn), Rm, etc.                                                                                                                                  |                                                                                                                                                                                                                |  |  |  |

| (4) Operation field, effective address extension, and condition field |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                              |                                                                                                                                                                                                                |  |  |  |

| ор                                                                    | сс                                                                    | EA (disp)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                              | BRA d:16, etc.                                                                                                                                                                                                 |  |  |  |

|                                                                       | (2) Operation field a<br>(3) Operation field,<br>(4) Operation field, | <ul> <li>(2) Operation field and register field op</li> <li>(3) Operation field, register fields, a</li> <li>op</li> <li>EA (control of the control of the</li></ul> | op       (2) Operation field and register fields       op     rn       (3) Operation field, register fields, and effective a       op     rn       EA (disp) | op         (2) Operation field and register fields         op       rn         (3) Operation field, register fields, and effective address extension         op       rn         rn       rm         EA (disp) |  |  |  |

Figure 2.11 Instruction Formats (Examples)

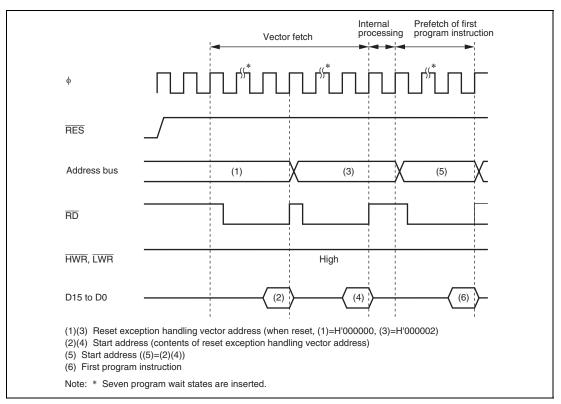

Figure 4.2 Reset Sequence (Advanced Mode with On-chip ROM Disabled)

#### 4.3.2 Interrupts after Reset

If an interrupt is accepted after a reset but before the stack pointer (SP) is initialized, the PC and CCR will not be saved correctly, leading to a program crash. To prevent this, all interrupt requests, including NMI, are disabled immediately after a reset. Since the first instruction of a program is always executed immediately after the reset state ends, make sure that this instruction initializes the stack pointer (example: MOV.L #xx: 32, SP).

#### 4.3.3 On-Chip Peripheral Functions after Reset Release

After reset release, MSTPCR is initialized to H'0FFF, EXMSTPCR is initialized to H'FFFF, and all modules except the DMAC, EXDMAC, and DTC enter the module stop state.

Consequently, on-chip peripheral module registers cannot be read or written to. Register reading and writing is enabled when the module stop state is exited.

1

0

Section 6 Bus Controller (BSC) **Initial Value** Bit Bit Name R/W Description 10 0 R/W Reserved This bit can be read from or written to. However, the write value should always be 0. 9 RCD1 0 R/W **RAS-CAS Wait Control** 8 RCD0 0 R/W These bits select a wait cycle to be inserted between the  $\overline{RAS}$  assert cycle and  $\overline{CAS}$  assert cycle. A 1- to 4-state wait cycle can be inserted. 00: Wait cycle not inserted 01: 1-state wait cycle inserted 10: 2-state wait cycle inserted 11: 3-state wait cycle inserted 7 to 4 — All 0 R/W Reserved These bits can be read from or written to. However, the write value should always be 0. CKSPE\* 3 0 R/W **Clock Suspend Enable** Enables clock suspend mode for extend read data during DMAC and EXDMAC single address transfer with the synchronous DRAM interface. 0: Disables clock suspend mode 1: Enables clock suspend mode 2 0 R/W Reserved

This bit can be read from or written to. However, the write value should always be 0. RDXC1\* 0 R/W Read Data Extension Cycle Number Selection **RDXC0\*** 0 R/W Selects the number of read data extension cycle (Tsp) insertion state in clock suspend mode. These bits are valid when the CKSPE bit is set to 1.

00: Inserts 1 state 01: Inserts 2 state 10: Inserts 3 state 11: Inserts 4 state

Note: Not supported by the H8S/2456 Group and H8S/2454 Group.

RENESAS

#### 6.8.8 Row Address Output State Control

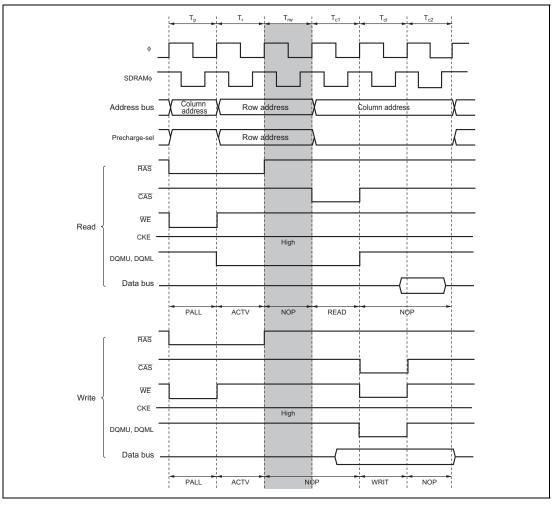

When the command interval specification from the ACTV command to the next READ/WRIT command cannot be satisfied, 1 to 3 states (Trw) that output the NOP command can be inserted between the Tr cycle that outputs the ACTV command and the Tc1 cycle that outputs the column address by setting the RCD1 and RCD0 bits of DRACCR. Use the optimum setting for the wait time according to the synchronous DRAM connected and the operating frequency of this LSI. Figure 6.58 shows an example of the timing when the one Trw state is set.

Figure 6.58 Example of Access Timing when Row Address Output Hold State Is 1 State (RCD1 = 0, RCD0 = 1, SDWCD = 0, CAS Latency 2)

#### 7.3.4 DMA Control Registers (DMACRA and DMACRB)

DMACR controls the operation of each DMAC channel.

The DMA has four DMACR registers: DMACR\_0A in channel 0 (channel 0A), DMACR\_0B in channel 0 (channel 0B), DMACR\_1A in channel 1 (channel 1A), and DMACR\_1B in channel 1 (channel 1B). In short address mode, channels A and B operate independently, and in full address mode, channels A and B operate together. The bit functions in the DMACR registers differ according to the transfer mode.

#### (1) Short Address Mode:

| Bit | Bit Name | Initial Value | R/W | Description                                                                                                                                                                 |

|-----|----------|---------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | DTSZ     | 0             | R/W | Data Transfer Size                                                                                                                                                          |

|     |          |               |     | Selects the size of data to be transferred at one time.                                                                                                                     |

|     |          |               |     | 0: Byte-size transfer                                                                                                                                                       |

|     |          |               |     | 1: Word-size transfer                                                                                                                                                       |

| 6   | DTID     | 0             | R/W | Data Transfer Increment/Decrement                                                                                                                                           |

|     |          |               |     | Selects incrementing or decrementing of MAR<br>after every data transfer in sequential mode or<br>repeat mode. In idle mode, MAR is neither<br>incremented nor decremented. |

|     |          |               |     | 0: MAR is incremented after a data transfer<br>(Initial value)                                                                                                              |

|     |          |               |     | • When DTSZ = 0, MAR is incremented by 1                                                                                                                                    |

|     |          |               |     | • When DTSZ = 1, MAR is incremented by 2                                                                                                                                    |

|     |          |               |     | 1: MAR is decremented after a data transfer                                                                                                                                 |

|     |          |               |     | • When DTSZ = 0, MAR is decremented by 1                                                                                                                                    |

|     |          |               |     | • When DTSZ = 1, MAR is decremented by 2                                                                                                                                    |

• DMACR\_0A, DMACR\_0B, DMACR\_1A, and DMARC\_1B

| Bit | Bit Name | Initial Value | R/W | Description                                                                                                                                                                                                                                                                     |

|-----|----------|---------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3   | DTIE1B   | 0             | R/W | Data Transfer End Interrupt Enable 1B                                                                                                                                                                                                                                           |

| 2   | DTIE1A   | 0             | R/W | Data Transfer End Interrupt Enable 1A                                                                                                                                                                                                                                           |

| 1   | DTIE0B   | 0             | R/W | Data Transfer End Interrupt Enable 0B                                                                                                                                                                                                                                           |

| 0   | DTIE0A   | 0             | R/W | Data Transfer End Interrupt Enable 0A                                                                                                                                                                                                                                           |

|     |          |               |     | These bits enable or disable an interrupt to the CPU or DTC when transfer ends. If the DTIE bit is set to 1 when DTE = 0, the DMAC regards this as indicating the end of a transfer, and issues a transfer end interrupt request to the CPU or DTC.                             |

|     |          |               |     | A transfer end interrupt can be canceled either by<br>clearing the DTIE bit to 0 in the interrupt handling<br>routine, or by performing processing to continue<br>transfer by setting the transfer counter and<br>address register again, and then setting the DTE<br>bit to 1. |

#### (2) Full Address Mode:

• DMABCRH

| Bit | Bit Name | Initial Value | R/W | Description                                                                           |

|-----|----------|---------------|-----|---------------------------------------------------------------------------------------|

| 15  | FAE1     | 0             | R/W | Full Address Enable 1                                                                 |

|     |          |               |     | Specifies whether channel 1 is to be used in short address mode or full address mode. |

|     |          |               |     | In full address mode, channels 1A and 1B are used together as channel 1.              |

|     |          |               |     | 0: Short address mode                                                                 |

|     |          |               |     | 1: Full address mode                                                                  |

| 14  | FAE0     | 0             | R/W | Full Address Enable 0                                                                 |

|     |          |               |     | Specifies whether channel 0 is to be used in short address mode or full address mode. |

|     |          |               |     | In full address mode, channels 0A and 0B are used together as channel 0.              |

|     |          |               |     | 0: Short address mode                                                                 |

|     |          |               |     | 1: Full address mode                                                                  |

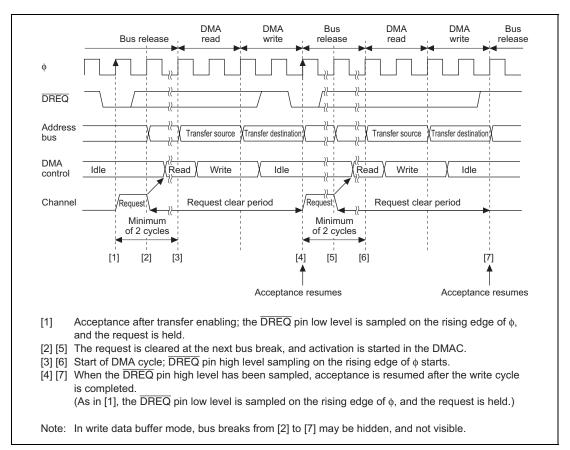

### (5) **DREQ** Pin Falling Edge Activation Timing

Set the DTA bit in DMABCRH to 1 for the channel for which the  $\overline{\text{DREQ}}$  pin is selected.

Figure 7.22 shows an example of normal mode transfer activated by the  $\overline{\text{DREQ}}$  pin falling edge.

Figure 7.22 Example of DREQ Pin Falling Edge Activated Normal Mode Transfer

## 7.5.14 DMAC and NMI Interrupts

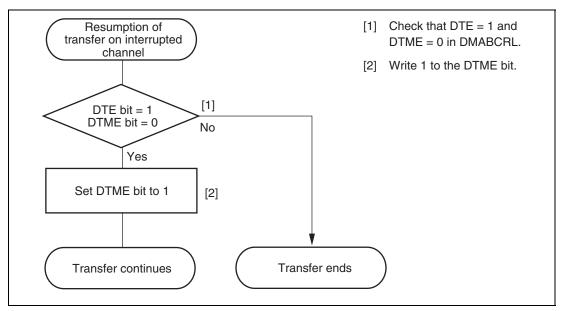

When an NMI interrupt is requested, burst mode transfer in full address mode is interrupted. An NMI interrupt does not affect the operation of the DMAC in other modes.

In full address mode, transfer is enabled for a channel when both the DTE bit and DTME bit in DMABCRL are set to 1. With burst mode setting, the DTME bit is cleared when an NMI interrupt is requested.

If the DTME bit is cleared during burst mode transfer, the DMAC discontinues transfer on completion of the 1-byte or 1-word transfer in progress, then releases the bus, which passes to the CPU.

The channel on which transfer was interrupted can be restarted by setting the DTME bit to 1 again. Figure 7.35 shows the procedure for continuing transfer when it has been interrupted by an NMI interrupt on a channel designated for burst mode transfer.

Figure 7.35 Example of Procedure for Continuing Transfer on Channel Interrupted by NMI Interrupt

| Bit | Bit Name | Initial Value | R/W | Description                                                                                                                                                                                                    |

|-----|----------|---------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10  | AMS      | 0             | R/W | Address Mode Select                                                                                                                                                                                            |

|     |          |               |     | Selects single address mode or dual address<br>mode. When single address mode is selected, the<br>EDACK pin is valid.                                                                                          |

|     |          |               |     | 0: Dual address mode                                                                                                                                                                                           |

|     |          |               |     | 1: Single address mode                                                                                                                                                                                         |

| 9   | MDS1     | 0             | R/W | Mode Select 1 and 0                                                                                                                                                                                            |

| 8   | MDS0     | 0             | R/W | These bits specify the activation source, bus mode, and transfer mode.                                                                                                                                         |

|     |          |               |     | 00: Auto request, cycle steal mode, normal<br>transfer mode                                                                                                                                                    |

|     |          |               |     | 01: Auto request, burst mode, normal transfer mode                                                                                                                                                             |

|     |          |               |     | 10: External request, cycle steal mode, normal<br>transfer mode                                                                                                                                                |

|     |          |               |     | 11: External request, cycle steal mode, block<br>transfer mode                                                                                                                                                 |

| 7   | EDIE     | 0             | R/W | EXDMA Interrupt Enable                                                                                                                                                                                         |

|     |          |               |     | Enables or disables interrupt requests. When this<br>bit is set to 1, an interrupt is requested when the<br>IRF bit is set to 1. The interrupt request is cleared<br>by clearing this bit or the IRF bit to 0. |

|     |          |               |     | 0: Interrupt request is not generated                                                                                                                                                                          |

|     |          |               |     | 1: Interrupt request is generated                                                                                                                                                                              |

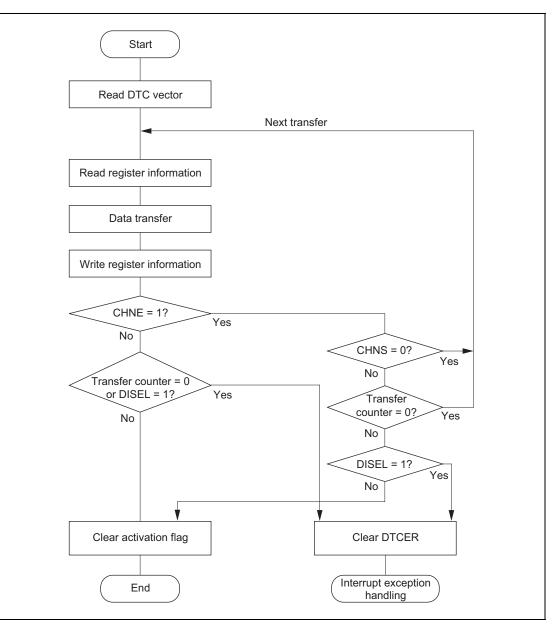

Figure 9.5 Flowchart of DTC Operation

|        |                                                                  |                       | Mode       |                              | de 3, 7    |                        | Input                               | Open                         |                                    |                  |

|--------|------------------------------------------------------------------|-----------------------|------------|------------------------------|------------|------------------------|-------------------------------------|------------------------------|------------------------------------|------------------|

| Port   | Description                                                      | Mode 1                | Mode 2     | Mode 4                       | EXPE = 1   | EXPE = 0               | Schmitt-<br>triggered<br>input Pin* | Pull-up<br>MOS<br>Capability | Drain<br>Output<br>Capability      | 5-V<br>Tolerance |

| Port A | General I/O port also<br>functioning as                          | PA7/A23/C<br>SSO0-B   | S7/IRQ7-A/ | PA7/A23/C<br>SSO0-B          | S7/IRQ7-A/ | PA7/IRQ7-A/<br>SSO0-B  | IRQ7-A                              | 0                            | All output<br>pin                  |                  |

|        | address outputs,<br>interrupt inputs, SSU<br>I/Os, SCI I/Os, and | PA6/A22/IR<br>SSI0-B  | Q6-A/      | PA6/A22/IF<br>SSI0-B         | RQ6-A/     | PA6/IRQ6-A/<br>SSI0-B  | IRQ6-A                              |                              | functions<br>other than<br>address |                  |

|        | bus control signal<br>outputs                                    | PA5/A21/IR<br>SSCK0-B | Q5-A/      | PA5/A21/IF<br>SSCK0-B        | RQ5-A/     | PA5/IRQ5-A/<br>SSCK0-B | IRQ5-A                              |                              | outputs<br>and CS7                 |                  |

|        |                                                                  | A20/IRQ4-A            | Ā          | PA4/A20/IF<br>SCS0-B         | 1Q4-A/     | PA4/IRQ4-A/<br>SCS0-B  | IRQ4-A                              |                              |                                    |                  |

|        |                                                                  | A19                   |            | PA3/A19/S                    | CK4-B      | PA3/SCK4-B             | _                                   |                              |                                    |                  |

|        |                                                                  | A18                   |            | PA2/A18/R                    | xD4-B      | PA2/RxD4-B             |                                     |                              |                                    |                  |

|        |                                                                  | A17                   |            | PA1/A17/T                    | vD4-B      | PA1/TxD4-B             |                                     |                              |                                    |                  |

|        |                                                                  | A16                   |            | PA0/A16                      |            | PA0                    |                                     |                              |                                    |                  |

| Port B | General I/O port also<br>functioning as                          | A15                   | A15 PB7/A1 |                              |            | PB7/TIOCB8<br>/TCLKH   | TIOCB8/<br>TCLKH                    | 0                            | All output -<br>pin                | —                |

|        | address outputs and<br>TPU I/Os                                  | A14                   |            |                              | PB6/A14    |                        | TIOCA8                              |                              | functions other than               |                  |

|        | 100 1/05                                                         | A13                   |            | PB5/A13                      |            | PB5/TIOCB7<br>/TCLKG   | TIOCB7/<br>TCLKG                    |                              | address<br>outputs                 |                  |

|        |                                                                  | A12                   | A12        |                              |            | PB4/TIOCA7             | TIOCA7                              |                              |                                    |                  |

|        |                                                                  | A11<br>A10<br>A9      |            | PB3/A11<br>PB2/A10<br>PB1/A9 |            | PB3/TIOCD<br>6/TCLKF   | TIOCD6/<br>TCLKF                    |                              |                                    |                  |

|        |                                                                  |                       |            |                              |            | PB2/TIOCC<br>6/TCLKE   | TIOCC6/<br>TCLKE                    |                              |                                    |                  |

|        |                                                                  |                       |            |                              |            | PB1/TIOCB6             | TIOCB6                              |                              |                                    |                  |

|        |                                                                  | A8                    |            | PB0/A8                       |            | PB0/TIOCA6             | TIOCA6                              |                              |                                    |                  |

| Port C | General I/O port also<br>functioning as                          | A7                    |            | PC7/A7                       |            | PC7/<br>TIOCB11        | TIOCB11                             | 0                            | All output<br>pin                  | —                |

|        | address outputs and TPU I/Os                                     | A6                    |            | PC6/A6                       |            | PC6/<br>TIOCA11        | TIOCA11                             |                              | functions<br>other than<br>address |                  |

|        |                                                                  | A5                    | PC5/A      |                              | PC5/A5     |                        | TIOCB10                             |                              | outputs                            |                  |

|        |                                                                  | A4                    |            | PC4/A4                       |            | PC4/<br>TIOCA10        |                                     |                              |                                    |                  |

|        |                                                                  | A3                    |            | PC3/A3                       |            | PC3/<br>TIOCD9         | TIOCD9                              |                              |                                    |                  |

|        |                                                                  | A2                    |            | PC2/A2                       |            | PC2/<br>TIOCC9         | TIOCC9                              |                              |                                    |                  |

|        |                                                                  | A1                    |            | PC1/A1                       |            | PC1/<br>TIOCB9         | TIOCB9                              |                              |                                    |                  |

|        |                                                                  | A0                    |            | PC0/A0                       |            | PC0/<br>TIOCA9         | TIOCA9                              |                              |                                    |                  |

| TPU channel 4 settings | (2)                          | (1)                                         | (2)    | (2)    | (1)                  | (2)       |

|------------------------|------------------------------|---------------------------------------------|--------|--------|----------------------|-----------|

| MD3 to MD0             | B'0000,                      | B'01xx                                      | B'0010 |        | B'0011               |           |

| IOB3 to IOB0           | B'0000,<br>B'0100,<br>B'1xxx | B'0001 to<br>B'0011,<br>B'0101 to<br>B'0111 |        | B'xx00 | Other tha            | ın B'xx00 |

| CCLR1,<br>CCLR0        | —                            | —                                           | —      | _      | Other than<br>B'10   | B'10      |

| Output function        | _                            | Output<br>compare<br>output                 |        | _      | PWM mode<br>2 output | —         |

[Legend]

x: Don't care

#### • P20/PO0-A/TIOCA3-A/TMRI0-A/PUPD+

The pin function is switched as shown below according to the combination of the TPU channel 3 settings (by bits MD3 to MD0 in TMDR\_3, bits IOA3 to IOA0 in TIOR H\_3, and bits CCLR2 to CCLR0 in TCR\_3), bit NDER0 in NDERL of the PPG, bit PULLUP\_E in CTLR of the USB, bits PPGS, TPUS and TMRS in PFCR3, and bit P20DDR.

| PULLUP_E               |                                             | 1         |            |                |              |

|------------------------|---------------------------------------------|-----------|------------|----------------|--------------|

| TPU channel 3 settings | (1) in table<br>below                       |           |            |                |              |

| P20DDR                 |                                             | 0 1       |            |                | —            |

| NDER0                  |                                             |           | 0          | 1              | —            |

| Pin function           | TIOCA3-A                                    | P20 input | P20 output | PO0-A output*4 | PUPD+ output |

|                        | output*⁵                                    | -         |            |                |              |

|                        | IRQ8-B-A input* <sup>2</sup> * <sup>6</sup> |           |            |                |              |

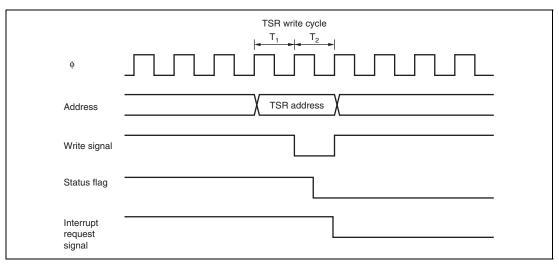

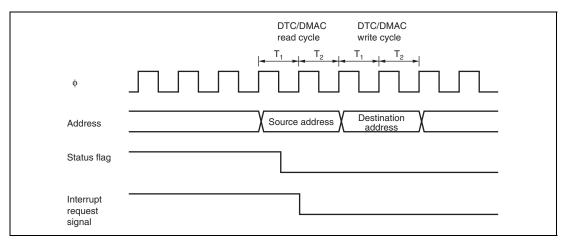

#### (4) Status Flag Clearing Timing

After a status flag is read as 1 by the CPU, it is cleared by writing 0 to it. When the DTC or DMAC is activated, the flag is cleared automatically. Figure 11.43 shows the timing for status flag clearing by the CPU, and figure 11.44 shows the timing for status flag clearing by the DTC or DMAC.

Figure 11.43 Timing for Status Flag Clearing by CPU

Figure 11.44 Timing for Status Flag Clearing by DTC/DMAC Activation

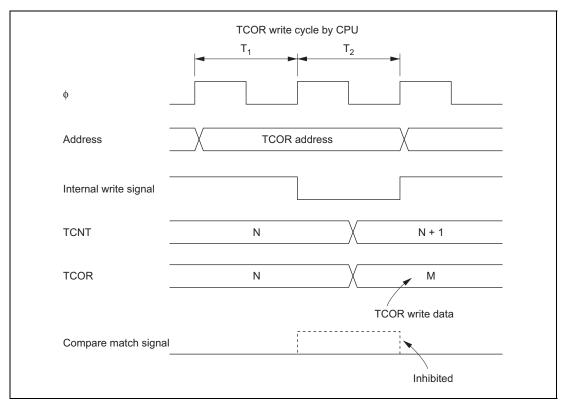

#### 13.8.3 Contention between TCOR Write and Compare Match

During the  $T_2$  state of a TCOR write cycle, the TCOR write has priority and the compare match signal is inhibited even if a compare match event occurs as shown in figure 13.13.

Figure 13.13 Contention between TCOR Write and Compare Match

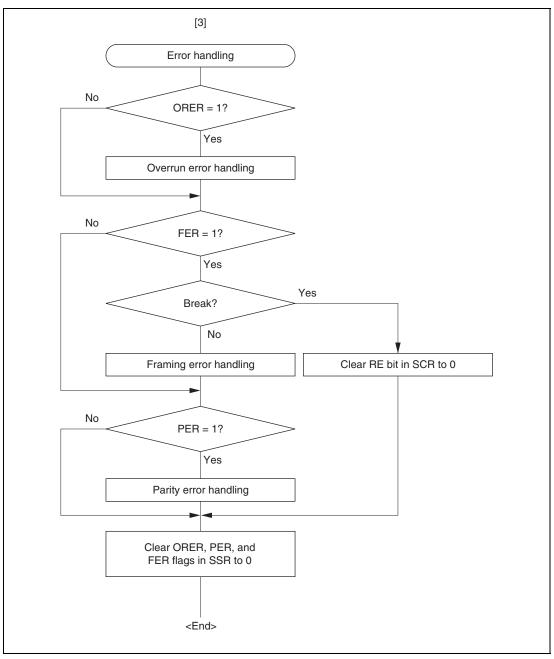

Figure 15.9 Sample Serial Reception Data Flowchart (2)

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                                                                                                                         |

|-----|----------|------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4   | RWUPS    | 0                | R   | Remote Wakeup Status                                                                                                                                                                                                                                                                |

|     |          |                  |     | This status bit indicates remote wakeup command from USB host is enabled or disabled.                                                                                                                                                                                               |

|     |          |                  |     | This bit is set to 0 when remote wakeup command<br>from UBM host is disabled by<br>Device_Remote_Wakeup due to Set Feature or Clear<br>Feature request. This bit is set to 1 when remote<br>wakeup command is enabled.                                                              |

| 3   | RSME     | 0                | R/W | Resume Enable                                                                                                                                                                                                                                                                       |

|     |          |                  |     | This bit releases the suspend state (or executes remote wakeup). When RSME is set to 1, resume request starts. If RSME is once set to 1, clear this bit to 0 again afterwards. In this case, the value 1 set to RSME must be kept for at least one clock period of 12-MHz clock.    |

| 2   | PWMD     | 0                | R/W | Bus Power Mode                                                                                                                                                                                                                                                                      |

|     |          |                  |     | This bit specifies the USB power mode. When PWMD is set to 0, the self-power mode is selected for this module. When set to 1, the bus-power mode is selected.                                                                                                                       |

| 1   | EP0 ASCE | 0                | R/W | EP0 Automatic Stall Clear Enable                                                                                                                                                                                                                                                    |

|     |          |                  |     | Setting the EP0 ASCE bit to 1 automatically clears the EP0 stall setting bit (the EP0 STLS bit in EPSTL0) after the stall handshake is returned to the host.                                                                                                                        |

|     |          |                  |     | When the EP0 ASCE bit is set to 0, the stall setting bit<br>is not automatically cleared and must be cleared by<br>the users. To enable the automatic stall clear function,<br>make sure that the EP0 ASCE bit should be set to 1<br>before the EP0 STLS bit in EPSTL0 is set to 1. |

| 0   | PRTRST   | 1                | R/W | Protocol Processing Block Reset                                                                                                                                                                                                                                                     |

|     |          |                  |     | <ol> <li>The protocol processing block is placed in<br/>operation state.</li> </ol>                                                                                                                                                                                                 |

|     |          |                  |     | 1: The protocol processing block is placed in reset state.                                                                                                                                                                                                                          |

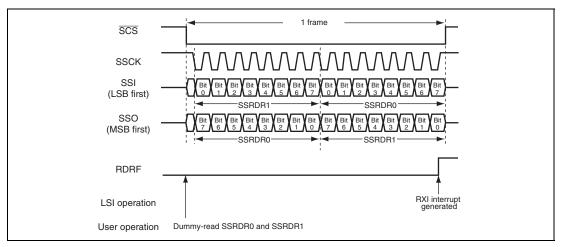

# Figure 20.7 (2) Example of Reception Operation (SSU Mode) When 16-bit data length is selected (SSRDR0 and SSRDR1 are valid) with CPOS = 0 and CPHS = 0

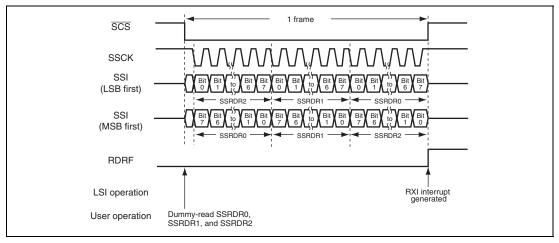

Figure 20.7 Example of Reception Operation (SSU Mode) When 24-bit data length is selected (SSRDR0, SSRDR1, and SSRDR2 are valid) with CPOS = 0 and CPHS = 0 (3)

## (a) Erasure Selection

The boot program will transfer the erasure program. User ROM data is erased by the transferred erasure program.

Command

Command, H'48, (1 byte): Erasure selection

| Response | H'06 |

|----------|------|

|          |      |

• Response, H'06, (1 byte): Response for erasure selection

After the erasure program has been transferred, the boot program will return ACK.

Error response H'C8 ERROR

- Error response, H'C8, (1 byte): Response to erasure selection

- ERROR (1 byte): Error code

H'48

H'54: Selection processing error (transfer error occurs and processing is not completed)

#### (b) Block Erasure

The boot program will erase the contents of the specified block.

| Command | H'58 | Size | Block number | SUM |

|---------|------|------|--------------|-----|

|---------|------|------|--------------|-----|

- Command, H'58, (1 byte): Block erasure

- Size (1 byte): The number of bytes that represents the erasure block number This is fixed to 1.

- Block number (1 byte): Number of the block to be erased

- SUM (1 byte): Checksum

Response

H'06

• Response, H'06, (1 byte): Response to Erasure

After erasure has been completed, the boot program will return ACK.

Error Response H'D8 ER

B ERROR

- Error Response, H'D8, (1 byte): Response to block erasure

- ERROR (1 byte): Error code

- H'11: Sum check error

- H'29: Block number error

Block number is incorrect.

H'51: Erasure error

An error has occurred during erasure.

| PGDR          |

|---------------|

| PHDDR         |

| PHDR          |

| PLLCR         |

| PMR           |

| PODR          |

| PORT1         |

| PORT2         |

| PORT3         |

| PORT4         |

| PORT5         |

| PORT6         |

| PORT8         |

| PORT9         |

| PORTA         |

| PORTB         |

| PORTC         |

| PORTD         |

| PORTE         |

| PORTF         |

| PORTG         |

| PORTH         |

| RDNCR         |

| RDR           |

| REFCR         |

| RMMSTPCR 1221 |

| RSR           |

| RSTCSR        |

| RTCNT         |

| RTCOR         |

| SAR           |

| SBYCR         |

| SCKCR         |

| SCMR          |

| SCR           |

| SEMR          |

| SMR           |

| SSCR2 1114    |

| SSCRH 1107    |

| SSCRL         |

|               |

| SSER                     | 1111       |

|--------------------------|------------|

| SSIER                    |            |

| SSMR                     | 1110       |

| SSR                      |            |

| SSRDR                    | 1117       |

| SSSR                     | 1112       |

| SSTDR                    | 1116       |

| SSTRSR                   | 1117       |

| SYSCR                    |            |

| TCNT                     |            |

| TCORA                    |            |

| TCORB                    |            |

| TCR                      | . 708, 826 |

| TCSR                     |            |

| TDR                      |            |

| TGR                      | .729,737   |

| TIER                     | 732        |

| TIOR                     | 715        |

| TMDR                     | 713        |

| TRG                      | .967,968   |

| TRNTREG                  |            |

| TSR                      | 734        |

| TSTR                     | . 737, 739 |

| TSYR                     | .738,740   |

| WTCR                     | 159        |

| Repeat area function     |            |

| Repeat mode              | . 361, 495 |

| Reset                    |            |

| Reset exception handling |            |

| Resolution               | 1086       |

| RXI0                     |            |

| RXI1                     | 134        |

| RXI2                     | 134        |

| RXI3                     | 134        |

| RXI4                     | 134        |

## S

| Sample-and-hold circuit | 1082 |

|-------------------------|------|

| Scan mode               | 1078 |