Welcome to E-XFL.COM

**Renesas Electronics America Inc - R4F24569DVRFQV Datasheet**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                             |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | H8S/2600                                                                        |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, SCI, SSU, UART/USART, USB                      |

| Peripherals                | DMA, POR, PWM, WDT                                                              |

| Number of I/O              | 96                                                                              |

| Program Memory Size        | 256KB (256K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 64K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b; D/A 2x8b                                                            |

| Oscillator Type            | External                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 144-LQFP                                                                        |

| Supplier Device Package    | 144-LFQFP (20x20)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r4f24569dvrfqv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin          | No.          |                                                                   | Pin Name                                                          |                                                                   |                                                                   |                                                                   |                               |  |  |

|--------------|--------------|-------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------|--|--|

|              |              |                                                                   |                                                                   |                                                                   | Mod                                                               | e 3, 7                                                            | Flash<br>Memory<br>Programmer |  |  |

| PLQP0144KA-A | PTLG0145JB-A | Mode 1                                                            | Mode 2                                                            | Mode 4                                                            | EXPE = 1                                                          | EXPE = 0                                                          | Mode                          |  |  |

| 18           | F4           | Vss                                                               | Vss                                                               | Vss                                                               | Vss                                                               | Vss                                                               | Vss                           |  |  |

| 19           | G4           | A12                                                               | A12                                                               | PB4/A12                                                           | PB4/A12                                                           | PB4/TIOCA7                                                        | A12                           |  |  |

| 20           | H4           | A13                                                               | A13                                                               | PB5/A13                                                           | PB5/A13                                                           | PB5/<br>TIOCB7/<br>TCLKG                                          | A13                           |  |  |

| 21           | G1           | A14                                                               | A14                                                               | PB6/A14                                                           | PB6/A14                                                           | PB6/TIOCA8                                                        | A14                           |  |  |

| 22           | H2           | A15                                                               | A15                                                               | PB7/A15                                                           | PB7/A15                                                           | PB7/<br>TIOCB8/<br>TCLKH                                          | A15                           |  |  |

| 23           | G3           | A16                                                               | A16                                                               | PA0/A16                                                           | PA0/A16                                                           | PA0                                                               | A16                           |  |  |

| 24           | J4           | A17                                                               | A17                                                               | PA1/A17/<br>TxD4_B                                                | PA1/A17/<br>TxD4_B                                                | PA1/TxD4_B                                                        | A17                           |  |  |

| 25           | H1           | Vss                                                               | Vss                                                               | Vss                                                               | Vss                                                               | Vss                                                               | Vss                           |  |  |

| 26           | J2           | A18                                                               | A18                                                               | PA2/A18/<br>RxD4-B                                                | PA2/A18/<br>RxD4-B                                                | PA2/RxD4-B                                                        | A18                           |  |  |

| 27           | НЗ           | A19                                                               | A19                                                               | PA3/A19/<br>SCK4-B                                                | PA3/A19/<br>SCK4-B                                                | PA3/SCK4-B                                                        | NC                            |  |  |

| 28           | К4           | A20/IRQ4-A                                                        | A20/IRQ4-A                                                        | PA4/A20/<br>IRQ4-A/<br>SCS0-B                                     | PA4/A20/<br>IRQ4-A/<br>SCS0-B                                     | PA4/IRQ4-A/<br>SCS0-B                                             | NC                            |  |  |

| 29           | J1           | PA5/A21/<br>IRQ5-A/<br>SSCK0-B                                    | PA5/A21/<br>IRQ5-A/<br>SSCK0-B                                    | PA5/A21/<br>IRQ5-A/<br>SSCK0-B                                    | PA5/A21/<br>IRQ5-A/<br>SSCK0-B                                    | PA5/<br>IRQ5-A/<br>SSCK0-B                                        | NC                            |  |  |

| 30           | K2           | PA6/A22/<br>IRQ6-A/<br>SSI0-B                                     | PA6/A22/<br>IRQ6-A/<br>SSI0-B                                     | PA6/A22/<br>IRQ6-A/<br>SSI0-B                                     | PA6/A22/<br>IRQ6-A/<br>SSI0-B                                     | PA6/<br>IRQ6-A/<br>SSI0-B                                         | NC                            |  |  |

| 31           | J3           | PA7/A23/<br>IRQ7-A/<br>SSO0-B                                     | PA7/A23/<br>IRQ7-A/<br>SSO0-B                                     | PA7/A23/<br>IRQ7-A/<br>SSO0-B                                     | PA7/A23/<br>IRQ7-A/<br>SSO0-B                                     | PA7/<br>IRQ7-A/<br>SSO0-B                                         | NC                            |  |  |

| 32           | K1           | EMLE                                                              | EMLE                                                              | EMLE                                                              | EMLE                                                              | EMLE                                                              | Vss                           |  |  |

| 33           | L2           | P81/IRQ1-B/<br>PO1-B/<br>TIOCB3-B/<br>TMRI1-B/<br>TxD3/<br>EDREQ3 | P81/IRQ1-B/<br>PO1-B/<br>TIOCB3-B/<br>TMRI1-B/<br>TxD3/<br>EDREQ3 | P81/IRQ1-B/<br>PO1-B/<br>TIOCB3-B/<br>TMRI1-B/<br>TxD3/<br>EDREQ3 | P81/ĪRQ1-B/<br>PO1-B/<br>TIOCB3-B/<br>TMRI1-B/<br>TxD3/<br>EDREQ3 | P81/IRQ1-B/<br>PO1-B/<br>TIOCB3-B/<br>TMRI1-B/<br>TxD3/<br>EDREQ3 | NC                            |  |  |

| Bit | Bit Name       | Initial Value | R/W | Description                                                                    |

|-----|----------------|---------------|-----|--------------------------------------------------------------------------------|

| 9   | IRQ4SCB        | 0             | R/W | IRQ4 Sense Control B                                                           |

| 8   | IRQ4SCA        | 0             | R/W | IRQ4 Sense Control A                                                           |

|     |                |               |     | 00: Interrupt request generated at IRQ4 input low level                        |

|     |                |               |     | 01: Interrupt request generated at falling edge of IRQ4 input                  |

|     |                |               |     | 10: Interrupt request generated at rising edge of IRQ4 input                   |

|     |                |               |     | 11: Interrupt request generated at both falling and rising edges of IRQ4 input |

| 7   | <b>IRQ3SCB</b> | 0             | R/W | IRQ3 Sense Control B                                                           |

| 6   | <b>IRQ3SCA</b> | 0             | R/W | IRQ3 Sense Control A                                                           |

|     |                |               |     | 00: Interrupt request generated at IRQ3 input low level                        |

|     |                |               |     | 01: Interrupt request generated at falling edge of IRQ3 input                  |

|     |                |               |     | 10: Interrupt request generated at rising edge of IRQ3 input                   |

|     |                |               |     | 11: Interrupt request generated at both falling and rising edges of IRQ3 input |

| 5   | IRQ2SCB        | 0             | R/W | IRQ2 Sense Control B                                                           |

| 4   | IRQ2SCA        | 0             | R/W | IRQ2 Sense Control A                                                           |

|     |                |               |     | 00: Interrupt request generated at IRQ2 input low level                        |

|     |                |               |     | 01: Interrupt request generated at falling edge of IRQ2 input                  |

|     |                |               |     | 10: Interrupt request generated at rising edge of IRQ2 input                   |

|     |                |               |     | 11: Interrupt request generated at both falling and rising edges of IRQ2 input |

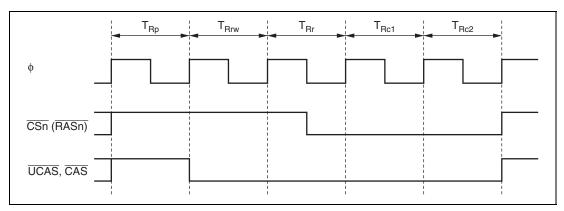

A setting can be made in bits RCW1 and RCW0 in REFCR to delay  $\overline{RAS}$  signal output by one to three cycles. Use bits RLW1 and RLW0 in REFCR to adjust the width of the  $\overline{RAS}$  signal. The settings of bits RCW1, RCW0, RLW1, and RLW0 are valid only in refresh operations.

Figure 6.49 shows the timing when bits RCW1 and RCW0 are set.

Depending on the DRAM used, modification of the  $\overline{WE}$  signal may not be permitted during the refresh period. In this case, the CBRM bit in REFCR should be set to 1. The bus controller will then insert refresh cycles in appropriate breaks between bus cycles. Figure 6.50 shows an example of the timing when the CBRM bit is set to 1. In this case the  $\overline{CS}$  signal is not controlled, and retains its value prior to the start of the refresh period.

# 6.8.15 DMAC and EXDMAC Single Address Transfer Mode and Synchronous DRAM Interface

When burst mode is selected on the synchronous DRAM interface, the  $\overline{DACK}$  and  $\overline{EDACK}$  output timing can be selected with the DDS and EDDS bits in DRAMCR. When continuous synchronous DRAM space is accessed in DMAC/EXDMAC single address mode at the same time, these bits select whether or not burst access is to be performed. The establishment time for the read data can be extended in the clock suspend mode irrespective of the settings of the DDS and EDDS bits.

# (1) Output Timing of DACK or EDACK

When DDS = 1 or EDDS = 1: Burst access is performed by determining the address only, irrespective of the bus master. With the synchronous DRAM interface, the  $\overline{DACK}$  or  $\overline{EDACK}$  output goes low from the T<sub>c1</sub> state.

Figure 6.72 shows the  $\overline{DACK}$  or  $\overline{EDACK}$  output timing for the synchronous DRAM interface when DDS = 1 or EDDS = 1.

#### (2) Write after Read

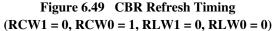

If an external write occurs after an external read while the ICIS0 bit is set to 1 in BCR, an idle cycle is inserted at the start of the write cycle.

Figure 6.78 shows an example of the operation in this case. In this example, bus cycle A is a read cycle for ROM with a long output floating time, and bus cycle B is a CPU write cycle. In (a), an idle cycle is not inserted, and a collision occurs in bus cycle B between the read data from ROM and the CPU write data. In (b), an idle cycle is inserted, and a data collision is prevented.

Figure 6.78 Example of Idle Cycle Operation (Write after Read)

# 6.14 Bus Controller Operation in Reset

In a reset, this LSI, including the bus controller, enters the reset state immediately, and any executing bus cycle is aborted.

# 6.15 Usage Notes

#### 6.15.1 External Bus Release Function and All-Module-Clocks-Stopped Mode

In this LSI, if the ACSE bit is set to 1 in MSTPCR, and then a SLEEP instruction is executed with the setting for all peripheral module clocks to be stopped (MSTPCR = H'FFFF, EXMSTPCR = H'FFFF) or for operation of the 8-bit timer module alone (MSTPCR = H'FFFE, EXMSTPCR = H'FFFF), and a transition is made to the sleep state, the all-module-clocks-stopped mode is entered in which the clock is also stopped for the bus controller and I/O ports. In this state, the external bus release function is halted. To use the external bus release function in sleep mode, the ACSE bit in MSTPCR must be cleared to 0. Conversely, if a SLEEP instruction to place the chip in all-module-clocks-stopped mode is executed in the external bus released state, the transition to all-module-clocks-stopped mode is deferred and performed until after the bus is recovered.

### 6.15.2 External Bus Release Function and Software Standby

In this LSI, internal bus master operation does not stop even while the bus is released, as long as the program is running in on-chip ROM, etc., and no external access occurs. If a SLEEP instruction to place the chip in software standby mode is executed while the external bus is released, the transition to software standby mode is deferred and performed after the bus is recovered.

Also, since clock oscillation halts in software standby mode, if BREQ goes low in this mode, indicating an external bus release request, the request cannot be answered until the chip has recovered from the software standby state.

# 6.15.3 External Bus Release Function and CBR Refreshing/Auto Refreshing

CBR refreshing/auto refreshing cannot be executed while the external bus is released. Setting the BREQOE bit to 1 in BCR beforehand enables the  $\overline{BREQO}$  signal to be output when a CBR refresh/auto refresh request is issued.

Note: The auto refresh control function is not supported by the H8S/2456 Group and H8S/2454 Group.

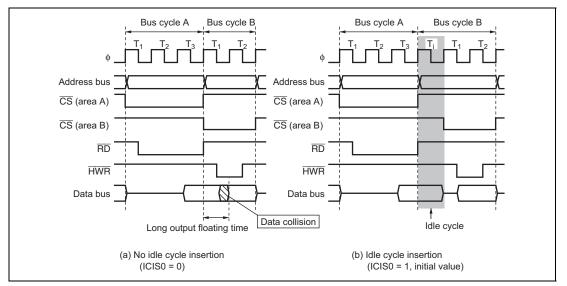

Figure 8.3 shows the data flow in single address mode, and figure 8.4 shows an example of the timing.

Figure 8.3 Data Flow in Single Address Mode

#### P50/TxD2/IRQ0-A/SDA3/BREQO-B/PO0-B/TIOCA3-B/TMRI0-B

The pin function is switched as shown below according to the combination of the operating mode, bit EXPE, bit BRLE of the bus controller, bit BREQOE, bit ICE in ICCRA\_3 of the I2C, bits MD3 to MD0 in TMDR\_3 of TPU, bits IOA3 to IOA0 in TIORH\_3, TPU channel 3 settings by bits CCLR2 to CCLR0 in TCR\_3, bit NDER0 in NDERL of PPG, bit TE in SCR\_2 of the SCI, bits PPGS, TPUS, and TMRS in PFCR3, bit BREQOS in PFCR4, bit P50DDR, and bit ITS0 in ITSR of the interrupt controller.

| BRLE<br>BREQOE<br>BREQOS |                                  | BRLE = 0, or BRLE = 1 and BREQOE = 0,<br>or BRLE = 1, BREQOE = 1 and BREQOS = 0<br>ar<br>BREQU |            |                               |                          |                        |                   |  |  |

|--------------------------|----------------------------------|------------------------------------------------------------------------------------------------|------------|-------------------------------|--------------------------|------------------------|-------------------|--|--|

| ICE                      |                                  |                                                                                                | 0          |                               |                          | 1                      | —                 |  |  |

| TPU channel 3 settings   | (1) in table<br>below            |                                                                                                | (2) in tab | —                             | —                        |                        |                   |  |  |

| TE                       | _                                |                                                                                                | 0          |                               | 1                        | —                      | —                 |  |  |

| P50DDR                   | _                                | 0                                                                                              | 1          | 1                             | —                        | —                      | —                 |  |  |

| NDER0                    | —                                | _                                                                                              | 0          | 1                             | —                        | —                      | —                 |  |  |

| Pin function             | TIOCA3-B<br>output* <sup>7</sup> | P50 input                                                                                      | P50 output | PO0-B<br>output* <sup>6</sup> | TxD2 output              | SDA3* <sup>5</sup> I/O | BREQO-B<br>output |  |  |

|                          |                                  |                                                                                                |            | TIOCA3-I                      | B input* <sup>1</sup> *7 |                        |                   |  |  |

|                          |                                  |                                                                                                |            | -A interrupt ir               | •                        |                        |                   |  |  |

|                          |                                  |                                                                                                | TN         | /IRI0-B input*                | 3*8                      |                        |                   |  |  |

#### • Modes 1, 2, and 4 Modes 3 and 7 (EXPE = 1)

#### • P82/IRQ2-B/ETEND2

The pin function is switched as shown below according to the combination of bit ETENDE in EDMDR\_2 of EXDMAC, bit P82DDR, and bit ITS2 in ITSR of the interrupt controller.

| Operating mode | 1, 2      | , 4 3, 7 (EXPI | 3, 7 (EXPE = 0)     |                    |   |

|----------------|-----------|----------------|---------------------|--------------------|---|

| ETENDE         | 0         |                | 1                   |                    |   |

| P82DDR         | 0         | 1              | —                   | 0                  | 1 |

| Pin function   | P82 input | P82 output     | ETEND2 output       | tput P82 input P82 |   |

|                |           | ĪRO            | 22-B interrupt inpu | ıt*                |   |

Note: \* IRQ2-B input when the ITS2 bit in ITSR is 1.

#### • P81/EDREQ3/IRQ1-B/TxD3/PO1-B/TIOCB3-B/TMRI1-B

The pin function is switched as shown below according to the combination of bit TE in SCR\_3 of SCI, TPU channel 3 settings (by bits MD3 to MD0 in TMDR\_3, bits IOB3 to IOB0 in TIORH\_3, and bits CCLR2 to CCLR0 in TCR\_3), bit NDER1 in NDERL of PPG, bits PPGS, TPUS, and TMRS in PFCR3, bit P81DDR, and bit ITS1 in ITSR of the interrupt controller.

| TPU channel 3 settings | (1) in table<br>below | (2) in table below                          |                              |                |             |  |  |  |

|------------------------|-----------------------|---------------------------------------------|------------------------------|----------------|-------------|--|--|--|

| TE                     |                       |                                             | 1                            |                |             |  |  |  |

| P81DDR                 | _                     | 0                                           | 1                            | 1              | _           |  |  |  |

| NDER1                  |                       |                                             | 0                            | 1              |             |  |  |  |

| Pin function           | TIOCB3-B              | P81 input                                   | P81 output                   | PO1-B output*4 | TxD3 output |  |  |  |

|                        | output*⁵              | TIOCB3-B input* <sup>2</sup> * <sup>5</sup> |                              |                |             |  |  |  |

|                        | EDREQ3 input          |                                             |                              |                |             |  |  |  |

|                        |                       | IRC                                         | Q1-B interrupt inp           | out*1          |             |  |  |  |

|                        |                       | 7                                           | FMRI1-B input* <sup>3,</sup> | <sub>к</sub> 6 |             |  |  |  |

Notes: 1. IRQ1-B input when the ITS1 bit in ITSR is 1.

- 2. TIOCB3-B input when MD3 to MD0 = B'0000 and IOB3 to IOB0 = B'10xx.

- 3. When used as the counter reset input pin for the TMR, the external reset should be selected using the CCLR1 and CCLR0 bits in TCR\_1 and TMRIS bit in TCCR\_1 after the TMRS bit in PFCR3 is set to 1.

- 4. When using as PO1-B output, set PPGS in PFCR3 to 1 before other register setting.

- 5. When using as TIOCB3-B input/output, set TPUS in PFCR3 to 1 before other register setting.

- 6. When using as TMRI1-B input, set TMRS in PFCR3 to 1 before other register setting.

• Modes 3 and 7 (EXPE = 0)

| WAITE        | —                  |            |                                           |                |                    |  |  |  |

|--------------|--------------------|------------|-------------------------------------------|----------------|--------------------|--|--|--|

| SSU settings | (1) in table below |            | (1) in table below (2) in table below     |                | (3) in table below |  |  |  |

| PF0DDR       | 0                  | 1          | 0*5                                       | 0*5            | —                  |  |  |  |

| Pin function | PF0 input          | PF0 output | SCS0-C input* <sup>2</sup> * <sup>6</sup> | SCS0-C I/O*4*6 | SCS0-C output*3*6  |  |  |  |

|              |                    |            | ADTRG0-B i                                | input*1        |                    |  |  |  |

- Notes: 1. ADTRG0-B input when the ADTRG0S bit in PFCR4 is 1, TRGS1 = TRGS0 = 0, and EXTRGS = 1

- 2. When using as SCS0-C input, set SCS0S1 and SCS0S0 in PFCR5 to B'10 before other register setting.

- 3. When using as SCS0-C output, set SCS0S1 and SCS0S0 in PFCR5 to B'10 before other register setting.

- 4. When using as SCS0-C input/output, set SCS0S1 and SCS0S0 in PFCR5 to B'10 before other register setting.

- 5. PF0DDR = 0 when the SSU pin is used as input.

- Do not set up for SSU unless SCS0S1 and SCS0S0 = B'10 in PFCR5. Use as I/O port.

| SSU settings | (2)       | (1) | (2)       | (4)                  | (3)        | (1) |  |  |

|--------------|-----------|-----|-----------|----------------------|------------|-----|--|--|

| SSUMS        |           | 0   |           |                      |            |     |  |  |

| MSS          | 0         |     | х         |                      |            |     |  |  |

| CSS1         | х         | (   | )         | 1                    | х          |     |  |  |

| CSS0         | х         | 0   | 1         | 0                    | 1          | х   |  |  |

| Pin state    | SCS input |     | SCS input | Automatic SCS<br>I/O | SCS output | —   |  |  |

[Legend]

x: Don't care

—: Not used as the SSU pin (can be used as an I/O port).

Note: See tables 20.4 to 20.6.

| Item                      |                  | Channel 0                                                                                                      | Channel 1                                                                                                     | Channel 2                                                                                                                     | Channel 3                                                                                                                      | Channel 4                                                                                                      | Channel 5                                                                                                                    |

|---------------------------|------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| Count cloo                | k                | <ul> <li>φ/1</li> <li>φ/4</li> <li>φ/64</li> <li>TCLKA</li> <li>TCLKB</li> <li>TCLKC</li> <li>TCLKD</li> </ul> | <ul> <li>φ/1</li> <li>φ/4</li> <li>φ/16</li> <li>φ/64</li> <li>φ/256</li> <li>TCLKA</li> <li>TCLKB</li> </ul> | <ul> <li>φ/1</li> <li>φ/4</li> <li>φ/16</li> <li>φ/64</li> <li>φ/1024</li> <li>TCLKA</li> <li>TCLKB</li> <li>TCLKC</li> </ul> | <ul> <li>φ/1</li> <li>φ/4</li> <li>φ/16</li> <li>φ/64</li> <li>φ/256</li> <li>φ/1024</li> <li>φ/4096</li> <li>TCLKA</li> </ul> | <ul> <li>φ/1</li> <li>φ/4</li> <li>φ/16</li> <li>φ/64</li> <li>φ/1024</li> <li>TCLKA</li> <li>TCLKC</li> </ul> | <ul> <li>φ/1</li> <li>φ/4</li> <li>φ/16</li> <li>φ/64</li> <li>φ/256</li> <li>TCLKA</li> <li>TCLKC</li> <li>TCLKD</li> </ul> |

| General re<br>(TGR)       | gisters          | TGRA_0<br>TGRB_0                                                                                               | TGRA_1<br>TGRB_1                                                                                              | TGRA_2<br>TGRB_2                                                                                                              | TGRA_3<br>TGRB_3                                                                                                               | TGRA_4<br>TGRB_4                                                                                               | TGRA_5<br>TGRB_5                                                                                                             |

| General re<br>buffer regi |                  | TGRC_0<br>TGRD_0                                                                                               | _                                                                                                             | —                                                                                                                             | TGRC_3<br>TGRD_3                                                                                                               | _                                                                                                              | _                                                                                                                            |

| I/O pins                  |                  | TIOCA0<br>TIOCB0<br>TIOCC0<br>TIOCD0                                                                           | TIOCA1<br>TIOCB1                                                                                              | TIOCA2<br>TIOCB2                                                                                                              | TIOCA3<br>TIOCB3<br>TIOCC3<br>TIOCD3                                                                                           | TIOCA4<br>TIOCB4                                                                                               | TIOCA5<br>TIOCB5                                                                                                             |

| Counter cl<br>function    | ear              | TGR<br>compare<br>match or<br>input<br>capture                                                                 | TGR<br>compare<br>match or<br>input<br>capture                                                                | TGR<br>compare<br>match or<br>input<br>capture                                                                                | TGR<br>compare<br>match or<br>input<br>capture                                                                                 | TGR<br>compare<br>match or<br>input<br>capture                                                                 | TGR<br>compare<br>match or<br>input<br>capture                                                                               |

| Compare                   | 0 output         | 0                                                                                                              | 0                                                                                                             | 0                                                                                                                             | 0                                                                                                                              | 0                                                                                                              | 0                                                                                                                            |

| match<br>output           | 1 output         | 0                                                                                                              | 0                                                                                                             | 0                                                                                                                             | 0                                                                                                                              | 0                                                                                                              | 0                                                                                                                            |

| output                    | Toggle<br>output | 0                                                                                                              | 0                                                                                                             | 0                                                                                                                             | 0                                                                                                                              | 0                                                                                                              | 0                                                                                                                            |

| Input captor<br>function  | ure              | 0                                                                                                              | 0                                                                                                             | 0                                                                                                                             | 0                                                                                                                              | 0                                                                                                              | 0                                                                                                                            |

| Synchrono<br>operation    | ous              | 0                                                                                                              | 0                                                                                                             | 0                                                                                                                             | 0                                                                                                                              | 0                                                                                                              | 0                                                                                                                            |

| PWM mod                   | е                | 0                                                                                                              | 0                                                                                                             | 0                                                                                                                             | 0                                                                                                                              | 0                                                                                                              | 0                                                                                                                            |

| Phase cou<br>mode         | inting           | —                                                                                                              | 0                                                                                                             | 0                                                                                                                             | —                                                                                                                              | 0                                                                                                              | 0                                                                                                                            |

| Buffer ope                | ration           | 0                                                                                                              |                                                                                                               | _                                                                                                                             | 0                                                                                                                              |                                                                                                                | _                                                                                                                            |

# Table 11.1 TPU (Unit 0) Functions

### (b) Free-running count operation and periodic count operation

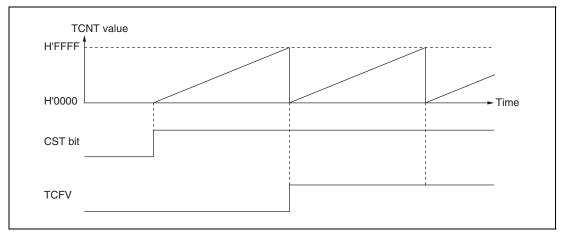

Immediately after a reset, the TPU's TCNT counters are all designated as free-running counters. When the relevant bit in TSTR is set to 1 the corresponding TCNT counter starts upcount operation as a free-running counter. When TCNT overflows (changes from H'FFFF to H'0000), the TCFV bit in TSR is set to 1. If the value of the corresponding TCIEV bit in TIER is 1 at this point, the TPU requests an interrupt. After overflow, TCNT starts counting up again from H'0000.

Figure 11.4 illustrates free-running counter operation.

Figure 11.4 Free-Running Counter Operation

### (3) Input Capture Function

The TCNT value can be transferred to TGR on detection of the TIOC pin input edge.

Rising edge, falling edge, or both edges can be selected as the detection edge. For channels 0, 1, 3, 4, 6, 7, 9, and 10 it is also possible to specify another channel's counter input clock or compare match signal as the input capture source.

Note: When another channel's counter input clock is used as the input capture input for channels 0, 3, 6, and 9,  $\phi/1$  should not be selected as the counter input clock used for input capture input. Input capture will not be generated if  $\phi/1$  is selected.

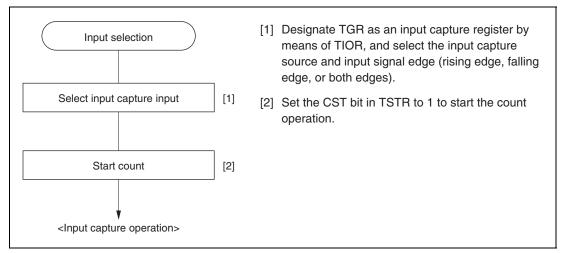

#### (a) Example of setting procedure for input capture operation

Figure 11.9 shows an example of the setting procedure for input capture operation.

Figure 11.9 Example of Setting Procedure for Input Capture Operation

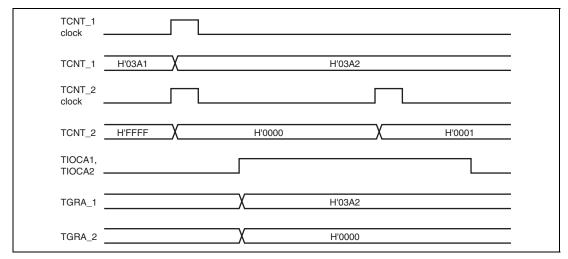

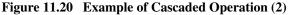

#### (2) Examples of Cascaded Operation

Figure 11.19 illustrates the operation when counting upon TCNT\_2 overflow/underflow has been set for TCNT\_1, TGRA\_1 and TGRA\_2 have been designated as input capture registers, and the TIOC pin rising edge has been selected.

When a rising edge is input to the TIOCA1 and TIOCA2 pins simultaneously, the upper 16 bits of the 32-bit data are transferred to TGRA\_1, and the lower 16 bits to TGRA\_2.

Figure 11.19 Example of Cascaded Operation (1)

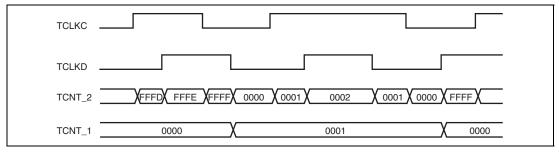

Figure 11.20 illustrates the operation when counting upon TCNT\_2 overflow/underflow has been set for TCNT\_1, and phase counting mode has been designated for channel 2.

TCNT\_1 is incremented by TCNT\_2 overflow and decremented by TCNT\_2 underflow.

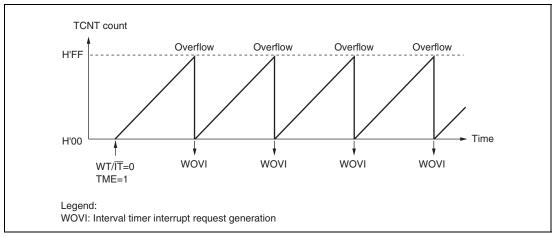

# 14.4.2 Interval Timer Mode

To use the WDT as an interval timer, set the WT/ $\overline{\text{IT}}$  bit to 0 and TME bit in TCSR to 1.

When the WDT is used as an interval timer, an interval timer interrupt (WOVI) is generated each time the TCNT overflows. Therefore, an interrupt can be generated at intervals.

When the TCNT overflows in interval timer mode, an interval timer interrupt (WOVI) is requested at the same time the OVF bit in the TCSR is set to 1.

# Figure 14.3 Operation in Interval Timer Mode

# 14.5 Interrupt Source

During interval timer mode operation, an overflow generates an interval timer interrupt (WOVI). The interval timer interrupt is requested whenever the OVF flag is set to 1 in TCSR. OVF must be cleared to 0 in the interrupt handling routine.

# Table 14.2WDT Interrupt Source

| Name | Interrupt Source | Interrupt Flag | DTC Activation |

|------|------------------|----------------|----------------|

| WOVI | TCNT overflow    | OVF            | Impossible     |

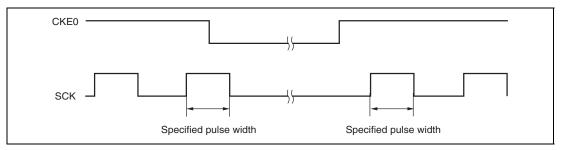

#### 15.7.8 Clock Output Control

When the GM bit in SMR is set to 1, the clock output level can be fixed with bits CKE1 and CKE0 in SCR. At this time, the minimum clock pulse width can be made the specified width.

Figure 15.31 shows the timing for fixing the clock output level. In this example, GM is set to 1, CKE1 is cleared to 0, and the CKE0 bit is controlled.

Figure 15.31 Timing for Fixing Clock Output Level

When turning on the power or switching between Smart Card interface mode and software standby mode, the following procedures should be followed in order to maintain the clock duty cycle.

**Powering On:** To secure the clock duty cycle from power-on, the following switching procedure should be followed.

- 1. The initial state is port input and high impedance. Use a pull-up resistor or pull-down resistor to fix the potential.

- 2. Fix the SCK pin to the specified output level with the CKE1 bit in SCR.

- 3. Set SMR and SCMR, and switch to Smart Card mode operation.

- 4. Set the CKE0 bit in SCR to 1 to start clock output.

# 16.3.15 EP3 Data Register (EPDR3)

EPDR3 is a 16-byte transmit FIFO buffer for endpoint 3. EPDR3 holds one packet of transmit data for the interrupt transfer of endpoint 3. Transmit data is fixed by writing one packet of data and setting EP3 PKTE in trigger register 1. This FIFO buffer can be initialized by means of EP3 CLR in FCLR register 1.

| Bit    | Bit Name | Initial<br>Value | R/W | Description                           |

|--------|----------|------------------|-----|---------------------------------------|

| 7 to 0 | D7 to D0 | Undefine         | d W | Data register for endpoint 3 transfer |

# 16.3.16 EP0o Receive Data Size Register (EPSZ0o)

EPSZ00 indicates the number of bytes received at endpoint 0 from the host.

| Bit    | Bit Name | Initial<br>Value | R/W | Description                           |  |

|--------|----------|------------------|-----|---------------------------------------|--|

| 7 to 5 | —        | All 0            | _   | Reserved                              |  |

|        |          |                  |     | These bits are always read as 0.      |  |

| 4 to 0 | D4 to D0 | All 0            | R   | Number of receive data for endpoint 0 |  |

# 16.3.17 EP1 Receive Data Size Register (EPSZ1)

EPSZ1 is a receive data size resister for endpoint 1. EPSZ1 indicates the number of bytes received from the host. The FIFO for endpoint 1 has a dual-buffer configuration. The size of the received data indicated by this register is the size of the currently selected side (can be read by CPU).

| Bit    | Bit Name | Initial<br>Value | R/W | Description                             |

|--------|----------|------------------|-----|-----------------------------------------|

| 7      | —        | 0                |     | Reserved                                |

|        |          |                  |     | This bit is always read as 0.           |

| 6 to 0 | D6 to D0 | All 0            | R   | Number of received bytes for endpoint 1 |

####

Output of the SDRAM¢ clock can be controlled by the SDPSTP bit in SCKCR. When the SDPSTP bit is set to 1, the SDRAM¢ clock stops at the end of the bus cycle and the pin can be used as a general port. SDRAM¢ clock output is enabled when the SDPSTP bit is cleared to 0 regardless of the DDR value. Table 24.5 shows the state of the SDRAM¢ pin in each processing state.

Note: The SDRAM interface is not supported by the H8S/2456 Group and H8S/2454 Group.

| Register Setting |     |                           |                       |                          |                          | All Module            |

|------------------|-----|---------------------------|-----------------------|--------------------------|--------------------------|-----------------------|

| SDPSTP           | DDR | Normal<br>Operating State | Sleep Mode            | Software<br>Standby Mode | Hardware<br>Standby Mode | Clocks Stop<br>Mode   |

| 0                | х   | SDRAM                     | SDRAM                 | Fixed low                | High impedance           | SDRAMø<br>output      |

| 1                | 0   | High impedance            | High impedance        | High impedance           | High impedance           | High<br>impedance     |

| 1                | 1   | PH1/CS5/RAS5<br>output    | H1/CS5/RAS5<br>output | H1/CS5/RAS5<br>output    | High impedance           | H1/CS5/RAS5<br>output |

Table 24.5

SDRAM\$ Pin State in Each Processing State

Note: SDRAM is not available in the H8S/2456 and H8S/2454 Groups. In these products, this pin functions as a general pin regardless of the SDPSTP bit setting.

| Item                                        | Symbol              | Min.                                       | Max. | Unit | Test Conditions            |

|---------------------------------------------|---------------------|--------------------------------------------|------|------|----------------------------|

| Read command hold time                      | t <sub>RCH</sub>    | $0.5 	imes t_{\scriptscriptstyle cyc}$ -10 | _    | ns   | Figures 26.8 to            |

| CAS delay time 1                            | t <sub>CASD1</sub>  | _                                          | 15   | ns   | 26.23, 26.29, and<br>26.30 |

| CAS delay time 2                            | t <sub>CASD2</sub>  | _                                          | 15   | ns   | _ 20.00                    |

| CAS setup time 1                            | t <sub>csr1</sub>   | $0.5 	imes t_{\scriptscriptstyle cyc}$ -10 |      | ns   |                            |

| CAS setup time 2                            | t <sub>csr2</sub>   | $1.5 	imes t_{_{cyc}} - 10$                |      | ns   |                            |

| CAS pulse width 1                           | t <sub>casw1</sub>  | $1.0 	imes t_{_{cyc}}$ –20                 |      | ns   |                            |

| CAS pulse width 2                           | t <sub>CASW2</sub>  | $1.5 	imes t_{_{cyc}}$ –20                 | _    | ns   | —                          |

| CAS precharge time 1                        | t <sub>CPW1</sub>   | $1.0 	imes t_{_{cyc}}$ –20                 | _    | ns   | —                          |

| CAS precharge time 2                        | t <sub>CPW2</sub>   | $1.5 	imes t_{_{cyc}}$ –20                 | _    | ns   | —                          |

| OE delay time 1*1                           | t <sub>oed1</sub>   | _                                          | 15   | ns   | —                          |

|                                             | t <sub>oed1B</sub>  | _                                          | 19   | ns   | —                          |

| OE delay time 2*1                           | t <sub>OED2</sub>   | _                                          | 15   | ns   | —                          |

|                                             | t <sub>oed2B</sub>  | _                                          | 19   | ns   | —                          |

| Precharge time 1                            | t <sub>PCH1</sub>   | $1.0 	imes t_{_{cyc}}$ –20                 | _    | ns   | —                          |

| Precharge time 2                            | t <sub>PCH2</sub>   | $1.5 	imes t_{_{cyc}}$ –20                 | _    | ns   | —                          |

| Self-refresh precharge time 1               | t <sub>RPS1</sub>   | $2.5 	imes t_{_{cyc}}$ –20                 | _    | ns   | Figures 26.22              |

| Self-refresh precharge time 2               | t <sub>RPS2</sub>   | $3.0 	imes t_{_{cyc}}$ –20                 |      | ns   | and 26.23                  |

| WAIT setup time                             | t <sub>wrs</sub>    | 25                                         | _    | ns   | Figures 26.10,             |

| WAIT hold time                              | t <sub>wth</sub>    | 1                                          | _    | ns   | 26.16, and 26.35           |

| BREQ setup time                             | t <sub>BREQS</sub>  | 30                                         | _    | ns   | Figure 26.24               |

| BACK delay time                             | t <sub>bacd</sub>   | —                                          | 15   | ns   |                            |

| Bus floating time                           | t <sub>BZD</sub>    | _                                          | 40   | ns   |                            |

| BREQO delay time                            | t <sub>brqod</sub>  | _                                          | 25   | ns   | Figure 26.25               |

| Address delay time 2*2                      | t <sub>AD2</sub>    | —                                          | 16.5 | ns   | Figure 26.26               |

| $\overline{\text{CS}}$ delay time $4^{*^2}$ | $t_{_{CSD4}}$       | _                                          | 16.5 | ns   | Figure 26.26               |

| DQM delay time* <sup>2</sup>                | t <sub>dqmd</sub>   | _                                          | 16.5 | ns   | Figure 26.26               |

| CKE delay time *2*3                         | t <sub>cked</sub>   | _                                          | 16.5 | ns   | Figures 26.27              |

|                                             | t <sub>ckedb</sub>  | _                                          | 19   | ns   | and 26.28                  |

| Read data setup time 3*2                    | t <sub>RDS3</sub>   | 15                                         |      | ns   | Figure 26.26               |

| Read data hold time 3*2                     | t <sub>RDH3</sub>   | 0                                          |      | ns   | Figure 26.26               |

| Write data delay time 2*2                   | $\mathbf{t}_{WDD}$  |                                            | 31.5 | ns   | Figure 26.26               |

| Write data hold time 4* <sup>2</sup>        | $\mathbf{t}_{WDH4}$ | 2                                          |      | ns   | Figure 26.26               |

# Appendix

# A. Port States in Each Processing State

#### Table A.1 Port States in Each Processing State (H8S/2456R Group and H8S/2456 Group)

| Port Name<br>Pin Name            | MCU<br>Operating<br>Mode | Reset | Hardware<br>Standby<br>Mode | Software Standby<br>Mode                                                                                                                                                              | Bus Release<br>State                                                          | Program<br>Execution State<br>Sleep Mode                                                    |

|----------------------------------|--------------------------|-------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| Port 1                           | 1, 2, 3, 4, 7            | Т     | Т                           | Keep                                                                                                                                                                                  | Keep                                                                          | I/O port                                                                                    |

| P27 to P26                       | 1, 2, 3, 4, 7            | Т     | Т                           | Keep                                                                                                                                                                                  | Keep                                                                          | I/O port                                                                                    |

| P25/WAIT                         | 1, 2, 3, 4, 7            | Т     | Т                           | [WAIT-B input]<br>T                                                                                                                                                                   | [WAIT-B input]<br>T                                                           | [WAIT-B input]<br>WAIT-B                                                                    |

|                                  |                          |       |                             | [Other than the<br>above]<br>Keep                                                                                                                                                     | [Other than the<br>above]<br>Keep                                             | [Other than the<br>above]<br>I/O port                                                       |

| P20                              | 1, 2, 3, 4, 7            | Т     | Т                           | Keep                                                                                                                                                                                  | Keep                                                                          | I/O port                                                                                    |

| P34 to P30                       | 1, 2, 3, 4, 7            | Т     | Т                           | Keep                                                                                                                                                                                  | Keep                                                                          | I/O port                                                                                    |

| P35/OE-B/<br>CKE-B* <sup>1</sup> | 1, 2, 3, 4, 7            | Т     | Т                           | $\overline{[OE-B]},$ $CKE-B \text{ output},$ $OPE = 0]$ $T$ $\overline{[OE-B} \text{ output},$ $OPE = 1]$ $H$ $[CKE-B \text{ output},$ $OPE = 1]$ $L$ $[Other than the above]$ $Keep$ | [OE-B,<br>CKE-B output,<br>OPE = 0]<br>T<br>[Other than the<br>above]<br>Keep | [OE-B,<br>CKE-B output,<br>OPE = 0]<br>OE-B, CKE-B<br>[Other than the<br>above]<br>I/O port |

| Port 4                           | 1, 2, 3, 4, 7            | Т     | Т                           | Т                                                                                                                                                                                     | Т                                                                             | Input port                                                                                  |

| P53                              | 1, 2, 3, 4, 7            | Т     | Т                           | Кеер                                                                                                                                                                                  | Кеер                                                                          | I/O port                                                                                    |

| P52/<br>BACK-B                   | 1, 2, 3, 4, 7            | Т     | Т                           | [BACK-B output]<br>BACK-B                                                                                                                                                             | [BACK-B output]<br>BACK-B                                                     | [BACK-B output]<br>BACK-B                                                                   |

|                                  |                          |       |                             | [Other than the<br>above]<br>Keep                                                                                                                                                     | [Other than the<br>above]<br>Keep                                             | [Other than the<br>above]<br>I/O port                                                       |