Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | ARM® Cortex®-M4                                                            |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 100MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 50                                                                         |

| Program Memory Size        | 256KB (256K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 104К х 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                               |

| Data Converters            | A/D 12x12b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

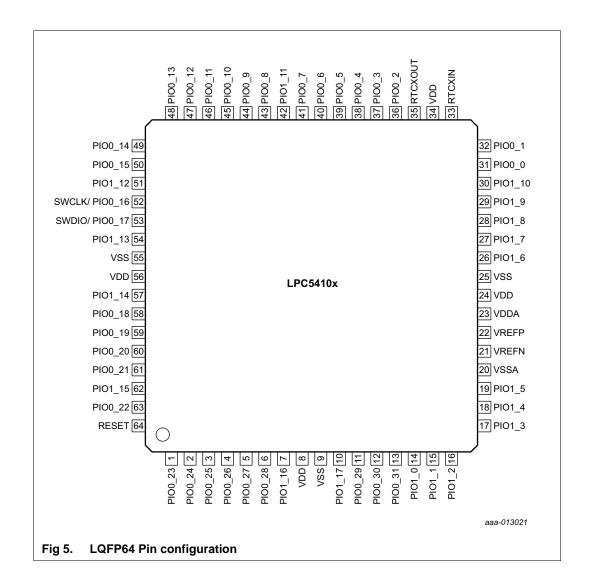

| Package / Case             | 64-LQFP                                                                    |

| Supplier Device Package    | 64-LQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc54101j256bd64ql |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# LPC5410x

#### 32-bit ARM Cortex-M4/M0+ microcontroller

The LPC5410x LQFP64 package has the following top-side marking:

- First line: LPC5410xJyyy

- x: 2 = dual core (M4, M0+), 1 = single core (M4)

- yyy: flash size

- Second line: BD64

- Third line: xxxxxxxxxxx

- Fourth line: xxxyywwx[R]z

- yyww: Date code with yy = year and ww = week.

- xR = boot code version and device revision.

The LPC5410x WLCSP49 package has the following top-side marking:

- First line: LPC5410x

- x: 2 = dual core (M4, M0+), 1 = single core (M4)

- Second line: JxxxUK49

- xxx: flash size

- Third line: xxxxxxx

- Fourth line: xxxyyww

- yyww: Date code with yy = year and ww = week.

- Fifth line: xxxxx

- Sixth line: NXP x[R]z

- xR = boot code version and device revision.

#### Table 3.Device revision table

| Revision identifier (R) | Revision description                                 |

|-------------------------|------------------------------------------------------|

| '1B'                    | Initial device revision with boot code version 17.1. |

| '1C'                    | Second device revision with boot code version 17.1.  |

LPC5410x

| Reserved.         PIO0_12         Fr         47         F2         PIO0_12         F7         47         F2         PIO0_12         F7         47         F2         PIO0_12         F7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Table 4. P        | Pin d | escr | iptio | n   | .conti | nued |                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------|------|-------|-----|--------|------|-----------------------------------------------------------------------------------|

| I/O         SPI0_MOSI — Master Out Slave in for SPI0.           0         U1_TXD — Transmitter output for USART1.           0         CT32B2_MAT3 — 32-bit CT32B2 match output 3.           1         R — Reserved.           PIO0_13         G7         48         I2         PU         I/O         SPI0_MISO — Master in Slave Out for SPI0.           0         CT32B2_MAT3 — 32-bit CT32B2 match output pin.         I/O         SPI0_MISO — Master in Slave Out for SPI0.           0         CT32B2_MAT0 — 32-bit CT32B2 match output 4.         O         CT32B2_MAT0 — 32-bit CT32B2 match output 4.           0         CT32B2_MAT0 — 32-bit CT32B2 match output 0.         I         R — Reserved.           PIO0_14/-CK         F6         49         I2         PU         I/O         SPI0_SSEL0 — Slave Select 0 for SPI0.         O           0         SCT0_OUT5 — SCT0 output 5. PVMM output 5.         O         CT32B2_MAT1 — 32-bit CT32B2 match output 1.         I         R — Reserved.           PIO0_15//TDO         G6         50         I2         PU         I/O         PIO0_15 — General-purpose digital input/output pin.         In boundary scan mode: TDO (Test Data Out).         I/O         SPI0_SSEL1 — Slave Select 1 for SPI0.         I/O         SVIDIO/         O         CT32B2_MAT1 — 32-bit CT32B2 match output 2.         I         R — Reserved. <th>Symbol</th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Symbol            |       |      |       |     |        |      |                                                                                   |

| PIO0_13         G         U1_TXD — Transmitter output for USART1.           0         U1_TXD — Transmitter output for USART1.         0           0         CT32B2_MAT3 — 32-bit CT32B2 match output 3.         1           1         R — Reserved.         1           PIO0_13         G7         48         Z         PU         V/O         PIO0_13 — General-purpose digital input/output pin.           1/0         SPI0_MISO — Master In Slave Out for SPI0.         0         SCT0_OUT4 — SCT0 output 4. PW/M output 4.           0         CT32B2_MAT0 — 32-bit CT32B2 match output 0.         1         R — Reserved.           PIO0_14/TCK         F6         49         Z         PU         V/O         PIO0_14 — General-purpose digital input/output pin.           1         n boundary scan mode: TCK (Test Clock).         V/O         SPI0_SSEL0 — Slave Select 0 for SPI0.         0         SCT0_OUT5 — SCT0 output 5. PW/M output 5.         0         CT32B2_MAT1 — 32-bit CT32B2 match output 1.         I         R — Reserved.           PIO0_15/TDD         G6         50         Z         PIO_15         General-purpose digital input/output pin.         In boundary scan mode: TDO (Test Data Out).         V/O         SPI0_SSEL1 — Slave Select 1 for SPI0.         V/O         SPI0_SSEL1 — Slave Select 1 for SPI0.         V/O         SPI0_SSEL2 — Slave Select 1 for SPI0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | PIO0_12           |       | F7   | 47    | [2] | PU     | I/O  | PIO0_12 — General-purpose digital input/output pin.                               |

| PIO0_13         G7         48         21         PU         I/O         PIO0_13 — General-purpose digital input/output pin.           I/O         SPI0_MISO — Master In Slave Out for SPI0.         0         CT32B2_MAT0 — 32-bit CT32B2 match output 4.           I/O         SPI0_MISO — Master In Slave Out for SPI0.         0         CT32B2_MAT0 — 32-bit CT32B2 match output 4.           I/O         SPI0_MISO — Master In Slave Out for SPI0.         0         CT32B2_MAT0 — 32-bit CT32B2 match output 4.           I/O         PIO0_14 — General-purpose digital input/output pin.         In boundary scan mode: TCK (Test Clock).         I/O           I/O         SPI0_SSEL0 — Slave Select 0 for SPI0.         0         SCT0_OUT5 — SCT0 output 5.         O           O         CT32B2_MAT1 — 32-bit CT32B2 match output 1.         I         R — Reserved.           PIO0_15/TDO         G6         50         I/I         PU         I/O         PIO0_15 — General-purpose digital input/output pin.           In boundary scan mode:         TOX (Test Data Out).         I/O         SPI0_SSEL1 — Slave Select 1 for SPI0.           I/O         SW0_SU_A_A_A_A_A_A_A_A_A_A_A_A_A_A_A_A_A_A_                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                   |       |      |       |     |        | I/O  | SPI0_MOSI — Master Out Slave in for SPI0.                                         |

| PIO0_13         G7         48         21         PU         I/O         PIO0_13 — General-purpose digital input/output pin.           VIO         SPI0_MISO — Master In Slave Out for SPI0.         O         SCT0_OUT4 — SCT0 output 4. PWM output 4.           O         GT32B2_MAT0 — 32-bit CT32B2 match output 0.         I         R — Reserved.           PIO0_14/TCK         F6         49         21         PU         I/O         PIO0_14 — General-purpose digital input/output pin.<br>In boundary scan mode: TCK (Test Clock).           VIO         SPI0_SSEL0 — Slave Select 0 for SPI0.         O         SCT0_OUT5 — SCT0 output 5. PWM output 5.           O         GCT32B2_MAT1 — 32-bit CT32B2 match output 1.         I         R — Reserved.           PIO0_15/TDO         G6         50         21         PU         I/O         PIO0_15 — General-purpose digital input/output pin.<br>In boundary scan mode: TDO (Test Data Out).         I/O         SPI0_SSEL1 — Slave Select 1 for SPI0.           I/O         SWO_SSEL1 — Slave Select 1 for SPI0.         I/O         SWO_SSEL1 — Slave Select 1 for SPI0.           I/O         SWO_SSEL1 — Slave Select 1 for SPI0.         I/O         SWO_SSEL2 — Slave Select 2 for SPI0.           I/O         SWO_SSEL2 — Slave Select 2 for SPI0.         I         R — Reserved.           SWOLO/         G5         52         21 <td< td=""><td></td><td></td><td></td><td></td><td></td><td></td><td>0</td><td>U1_TXD — Transmitter output for USART1.</td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                   |       |      |       |     |        | 0    | U1_TXD — Transmitter output for USART1.                                           |

| PIO0_13         G7         48         21         PU         // 0         Second and any any and any any any and any                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                   |       |      |       |     |        | 0    | CT32B2_MAT3 — 32-bit CT32B2 match output 3.                                       |

| I/O         SPI0_MISO — Master in Slave Out for SPI0.           0         SCT0_OUT4 — SCT0 output 4. PWM output 4.           0         CT32B2_MAT0 — 32-bit CT32B2 match output 0.           1         R — Reserved.           PIO0_14/TCK         F6         49         I/I         PIO0_14 — General-purpose digital input/output pin.           1         n — Reserved.         PIO.         910_SSEL0 — Slave Select 0 for SPI0.         SCT0_OUT5 — SCT0 output 5. PVM output 5.           0         CT32B2_MAT1 — 32-bit CT32B2 match output 1.         I         R — Reserved.           PIO0_15/TD0         G6         50         I/I         PU         PIO_15 — General-purpose digital input/output pin.           1         R — Reserved.         PIO_15 — General-purpose digital input/output pin.         In boundary scan mode: TDO (Test Data Out).           1/O         SPI0_SSEL1 — Slave Select 1 for SPI0.         V/O         SPI0_SSEL2 — Slave Select 1 for SPI0.           1/O         SWO - Serial Wire trace output.         O         CT32B2_MAT2 — 32-bit CT32B2 match output 2.           1         R — Reserved.         V/O         SPI0_SSEL2 — Slave Select 2 for SPI0.           1/O         SVELK// PIO0_16 — General-purpose digital input/output pin. After booting, this pin is connected to the SWCLK.           VIO_SPI0_SSEL2 — Slave Select 2 for SPI0.         I         U_1_                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |       |      |       |     |        | I    | R — Reserved.                                                                     |

| PIO0_14/TCK       F6       49       Z       PU       PO       PO0_14 — General-purpose digital input/output pin.<br>In boundary scan mode: TCK (Test Clock).         PIO0_14/TCK       F6       49       Z       PU       PO       PIO0_15 — General-purpose digital input/output pin.<br>In boundary scan mode: TCK (Test Clock).         PIO0_15/TDO       G6       50       Z       PU       PO       PIO0_15 — General-purpose digital input/output pin.<br>In boundary scan mode: TDO (Test Data Out).         PIO0_15/TDO       G6       50       Z       PU       PO       PIO0_15 — General-purpose digital input/output pin.<br>In boundary scan mode: TDO (Test Data Out).         V/O       SPI0_SSEL1 — Slave Select 1 for SPI0.       V/O       SPI0_SSEL1 — Slave Select 1 for SPI0.         V/O       SPI0_SSEL1 — Slave Select 1 for SPI0.       V/O       SPI0_SSEL2 — Slave Select 2 for SPI0.         V/O       SWOLK/       F5       52       PU       VO       PIO0_16 — General-purpose digital input/output pin. After booting, this pin is connected to the SWCLK.         SWDIO/       F100_15       SUB_SSEL2 — Slave Select 2 for SPI0.       I       IU_1_CTS — Clear To Send input for USART1.       O       CT3283_MAT1 — 32-bit CT32B3 match output 1.       R — Reserved.         SWDIO/       F100_17       General-purpose digital input/output pin. After booting.       V/O       SPI0_SSEL2 — Slave Select 2 fo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PIO0_13           |       | G7   | 48    | [2] | PU     | I/O  | PIO0_13 — General-purpose digital input/output pin.                               |

| O         CT32B2_MAT0 — 32-bit CT32B2 match output 0.           PIO0_14/TCK         F6         49         I/I         PUO_14 — General-purpose digital input/output pin.<br>In boundary scan mode: TCK (Test Clock).           I/O         SPI0_SSEL0 — Slave Select 0 for SPI0.         O         SCT0_OUT5 — SCT0 output 5. PWM output 5.           O         CT32B2_MAT1 — 32-bit CT32B2 match output 1.         I         R — Reserved.           PIO0_15/TDO         G6         50         I/I         PU //O         PIO0_15 — General-purpose digital input/output pin.<br>In boundary scan mode: TDO (Test Data Out).           PIO0_15/TDO         G6         50         I/I         PU //O         PIO0_15 — General-purpose digital input/output pin.<br>In boundary scan mode: TDO (Test Data Out).           V/O         SPI0_SSEL1 — Slave Select 1 for SPI0.         V/O         SWO_15 — General-purpose digital input/output pin. After booting, this pin is<br>connected to the SWCLK.         O         CT32B2_MAT2 — 32-bit CT32B2 match output 2.           I         R — Reserved.         V/O         SPI0_SSEL2 — Slave Select 2 for SPI0.         U           I         U/O         SPI0_SSEL2 — Slave Select 2 for SPI0.         U         U/O           I         U/O         SPI0_SSEL2 — Slave Select 2 for SPI0.         U/O         U/O           I         U/C TS — Clear To Send input for USART1.         O         CT32B3_M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                   |       |      |       |     |        | I/O  | SPI0_MISO — Master In Slave Out for SPI0.                                         |

| PIO0_14/TCK       F6       49       I       R - Reserved.         PIO0_14/TCK       F6       49       I       PU       I/O       PIO0_14 General-purpose digital input/output pin.<br>In boundary scan mode: TCK (Test Clock).         I/O       SPI0_SSEL0 Slave Select 0 for SPI0.       O       CT32B2_MAT1 32-bit CT32B2 match output 1.         I       R Reserved.       O       CT32B2_MAT1 32-bit CT32B2 match output 1.         I       R Reserved.       PIO0_15 General-purpose digital input/output pin.<br>In boundary scan mode: TDO (Test Data Out).         I/O       SPI0_SSEL1 Slave Select 1 for SPI0.         I/O       SPI0_SSEL1 Slave Select 1 for SPI0.         I/O       SWO Serial wire trace output.         O       CT32B2_MAT2 32-bit CT32B2 match output 2.         I       R Reserved.         VIO       PIO0_16 General-purpose digital input/output pin. After booting, this pin is connected to the SWCLK.         VIO0_16       F5       52       I/O       PIO0_16 General-purpose digital input/output pin. After booting, this pin is connected to the SWCLK.         VIO0_16       F5       52       I/O       PIO0_17 Clear To Send input for USART1.         O       CT32B3_MAT1 32-bit CT32B3 match output 1.       I       R Reserved.         SWDIO/       VIO       SWCLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                   |       |      |       |     |        | 0    | SCT0_OUT4 — SCT0 output 4. PWM output 4.                                          |

| PIO0_14/TCK       F6       49       I2       F0       I/O       PIO0_14 — General-purpose digital input/output pin.<br>In boundary scan mode: TCK (Test Clock).         I/O       SPI0_SSEL0 — Slave Select 0 for SPI0.       SCT0_OUT5 — SCT0 output 5. PWM output 5.         O       CT32B2_MAT1 — 32-bit CT32B2 match output 1.         I       R — Reserved.         PIO0_15/TD0       G6       50       I2       PU       I/O       PIO0_15 — General-purpose digital input/output pin.<br>In boundary scan mode: TDO (Test Data Out).         I/O       SPI0_SSEL1 — Slave Select 1 for SPI0.       V/O       SPI0_SSEL1 — Slave Select 1 for SPI0.         I/O       SW0 — Serial wire trace output.       O       CT32B2_MAT2 — 32-bit CT32B2 match output 2.         I       R — Reserved.       V/O       SW0 — Serial wire trace output.       O         O       CT32B2_MAT2 — 32-bit CT32B2 match output 2.       I       R — Reserved.         SWCLK/       F5       52       I/O       PIO0_16 — General-purpose digital input/output pin. After booting, this pin is connected to the SWCLK.         VIO       SPI0_SSEL2 — Slave Select 2 for SPI0.       I       U1_CTS — Clear To Send input for USART1.         O       CT32B3_MAT1 — 32-bit CT32B3 match output 1.       R — Reserved.       V/O         SWDIO/       F00_17 — General-purpose digital input/output pin. After b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                   |       |      |       |     |        | 0    | CT32B2_MAT0 — 32-bit CT32B2 match output 0.                                       |

| SWCLK/       F5       52       22       PU       V/O       PIO0_16 — General-purpose digital input/output pin.<br>In boundary scan mode: TOK (Test Clock).         VIO0_15/TDD       G6       53       22       PU       V/O       PIO0_15 — General-purpose digital input/output pin.<br>In boundary scan mode: TDO (Test Data Out).         VIO0_15/TDD       G6       50       22       PU       V/O       PIO0_15 — General-purpose digital input/output pin.<br>In boundary scan mode: TDO (Test Data Out).         VIO       SPI0_SSEL1 — Slave Select 1 for SPI0.       V/O       SPI0_SSEL1 — Slave Select 1 for SPI0.         V/O       SPI0_SSEL1 — Slave Select 1 for SPI0.       V/O       SWO — Serial wire trace output.         O       CT32B2_MAT2 — 32-bit CT32B2 match output 2.       I       R — Reserved.         SWCLK/       F5       52       22       PU       V/O       SPI0_SSEL2 — Slave Select 2 for SPI0.         I       U/O       SPI0_SSEL2 — Slave Select 2 for SPI0.       I       U1_CTS — Clear To Send input for USART1.         O       CT32B3_MAT1 — 32-bit CT32B3 match output 1.       R — Reserved.       V/O         I/O       SWCLK — Serial Wire Clock. This is the default function after booting.       V/O         SWDIO/       G5       53       PU       V/O       PIO0_17 — General-purpose digital input/output pin. After booting, this                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                   |       |      |       |     |        | I    | R — Reserved.                                                                     |

| I/O       SPI0_SSEL0 — Slave Select 0 for SPI0.         O       SCT0_OUT5 — SCT0 output 5. PVM output 5.         O       CT32B2_MAT1 — 32-bit CT32B2 match output 1.         I       R — Reserved.         PIO0_15/TDO       G6       50       I2       PU       I/O       PIO0_15 — General-purpose digital input/output pin.<br>In boundary scan mode: TDO (Test Data Out).         I/O       SPI0_SSEL1 — Slave Select 1 for SPI0.         I/O       SPI0_SSEL1 — Slave Select 1 for SPI0.         I/O       SWO — Serial wire trace output.         O       CT32B2_MAT2 — 32-bit CT32B2 match output 2.         I       R — Reserved.         SWCLK/       O       CT32B2_MAT2 — 32-bit CT32B2 match output 2.         I       R — Reserved.         SWCLK/       F5       52         PIO0_16       General-purpose digital input/output pin. After booting, this pin is connected to the SWCLK.         I/O       SPI0_SSEL2 — Slave Select 2 for SPI0.         I       U_1_CTS — Clear To Send input for USART1.         O       CT32B3_MAT1 — 32-bit CT32B3 match output 1.         I       R — Reserved.         I/O       SWCLK — Serial Wire Clock. This is the default function after booting.         I/O       SWCLK — Serial Wire Clock. This is the default function after booting.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | PIO0_14/TC        | K     | F6   | 49    | [2] | PU     | I/O  | PIO0_14 — General-purpose digital input/output pin.                               |

| SWDIO/       F5       53       2       PIO       PIO       10       SCT0_OUT5 - SCT0 output 5. PWM output 5.         O       CT32B2_MAT1 - 32-bit CT32B2 match output 1.       R       Reserved.         PIO0_15/TDO       G6       50       12       PU       I/O       PIO0_15 - General-purpose digital input/output pin.<br>In boundary scan mode: TDO (Test Data Out).         I/O       SPI0_SSEL1 - Slave Select 1 for SPI0.       I/O       SPI0_SSEL1 - Slave Select 1 for SPI0.         I/O       SWO - Serial wire trace output.       O       CT32B2_MAT2 - 32-bit CT32B2 match output 2.         R       Reserved.       VI       SWO - Serial wire trace output.       O         O       CT32B2_MAT2 - 32-bit CT32B2 match output pin. After booting, this pin is connected to the SWCLK.       VI         PIO0_16       F00_16 - General-purpose digital input/output pin. After booting, this pin is connected to the SWCLK.       VI         VI       SPI0_SSEL2 - Slave Select 2 for SPI0.       I       U1_CTS - Clear To Send input for USART1.         O       CT32B3_MAT1 - 32-bit CT32B3 match output 1.       R - Reserved.         VI       SWCLK - Serial Wire Clock. This is the default function after booting.         SWDIO/       VI       SWCLK - Serial Wire Clock. This is the default function after booting. this pin is connected to SWDIO.         VIO       SPI0_SSE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |       |      |       |     |        |      |                                                                                   |

| SWDIO/       F5       53       22       PU       VO       PC0_15 — Clarabs_mAT1 — 32-bit CT32B2 match output 1.         R — Reserved.       PIO0_15 — General-purpose digital input/output pin.<br>In boundary scan mode: TDO (Test Data Out).       VO       PIO_15 — General-purpose digital input/output pin.<br>In boundary scan mode: TDO (Test Data Out).         VO       SPI0_SSEL1 — Slave Select 1 for SPI0.       VO       SPI0_SSEL1 — Slave Select 1 for SPI0.         VO       SWO — Serial wire trace output.       O       CT32B2_MAT2 — 32-bit CT32B2 match output 2.         I       R — Reserved.       R       R — Reserved.         SWCLK/       F5       52       I2       PU       VO       PIO0_16 — General-purpose digital input/output pin. After booting, this pin is connected to the SWCLK.         VO       SPI0_SSEL2 — Slave Select 2 for SPI0.       I       U1_CTS — Clear To Send input for USART1.         O       CT32B3_MAT1 — 32-bit CT32B3 match output 1.       I       R — Reserved.         VO       SWCLK — Serial Wire Clock. This is the default function after booting.       VO         PIO0_17       G5       53       I2       PU       VO       PIO0_17 — General-purpose digital input/output pin. After booting, this pin is connected to SWDIO.       VO       SPI0_SSEL3 — Slave Select 3 for SPI0.       VO       SPI0_SSEL3 — Slave Select 3 for SPI0.       VI_RTS — Request To Send output f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                   |       |      |       |     |        | I/O  |                                                                                   |

| PIO0_15/TDO       G6       50       21       PU / PIO0_15 — General-purpose digital input/output pin.<br>In boundary scan mode: TDO (Test Data Out).         VI       SPI0_SSEL1 — Slave Select 1 for SPI0.       VO       SPI0_SSEL1 — Slave Select 1 for SPI0.         VO       SW0 — Serial wire trace output.       O       CT32B2_MAT2 — 32-bit CT32B2 match output 2.         R       R       Reserved.         SW0LK/       PIO_16       General-purpose digital input/output pin. After booting, this pin is connected to the SWCLK.         VIO_16       F0_SSEL2 — Slave Select 2 for SPI0.       VI         VI       SW0_SSEL2 — Slave Select 2 for SPI0.       VI         VI       SW0_SSEL2 — Slave Select 2 for SPI0.       VI         VI       SW0_SSEL2 — Slave Select 2 for SPI0.       VI         VI       SWCLK — Serial Wire Clock. This is the default function after booting.         SWDIO/       F3       S3       VI         PIO_17       General-purpose digital input/output pin. After booting, this pin is connected to SWDIO.         SWDIO/       F3       S3       VI         PIO_17       General-purpose digital input/output pin. After booting, this pin is connected to SWDIO.         VIO       SPI0_SSEL3 — Slave Select 3 for SPI0.         VIO       SPI0_SSEL3 — Slave Select 3 for SPI0.         VI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                   |       |      |       |     |        | 0    | SCT0_OUT5 — SCT0 output 5. PWM output 5.                                          |

| PIO0_15/TDO       G6       50       I2       PU       I/O       PIO0_15 — General-purpose digital input/output pin.<br>In boundary scan mode: TDO (Test Data Out).         I/O       SPI0_SSEL1 — Slave Select 1 for SPI0.         I/O       SWO — Serial wire trace output.         O       CT32B2_MAT2 — 32-bit CT32B2 match output 2.         I       R — Reserved.         SWCLK/<br>PIO0_16       F5       52       I2       PU       I/O       PIO0_16 — General-purpose digital input/output pin. After booting, this pin is connected to the SWCLK.         I/O       SPI0_SSEL2 — Slave Select 2 for SPI0.       I       U1_CTS — Clear To Send input for USART1.         O       CT32B3_MAT1 — 32-bit CT32B3 match output 1.       I       R — Reserved.         SWDIO/<br>PIO0_17       G5       53       I2       PU       I/O       PIO_17 — General-purpose digital input/output pin. After booting, this pin is connected to SWDIO.         SWDIO/<br>PIO0_17       G5       53       I2       PU       I/O       PIO_SEL3 — Slave Select 3 for SPI0.         I/O       SPI0_SSEL3 — Slave Select 3 for SPI0.       I/O       II_R — Reserved.         I/O       SPI0_SSEL3 — Slave Select 3 for SPI0.       II       II_R — Reserved.         I/O       CT32B3_MAT2 — 32-bit CT32B3 match output 2.       I       R — Reserved. <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>0</td> <td>CT32B2_MAT1 — 32-bit CT32B2 match output 1.</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |       |      |       |     |        | 0    | CT32B2_MAT1 — 32-bit CT32B2 match output 1.                                       |

| SWCLK/       F5       52       [2]       PU       I/O       SPI0_SSEL1 — Slave Select 1 for SPI0.         SWCLK/       F5       52       [2]       PU       I/O       PIO0_16 — General-purpose digital input/output pin. After booting, this pin is connected to the SWCLK.         SWCLK/       F5       52       [2]       PU       I/O       PIO0_16 — General-purpose digital input/output pin. After booting, this pin is connected to the SWCLK.         I/O       SPI0_SSEL2 — Slave Select 2 for SPI0.       I       U1_CTS — Clear To Send input for USART1.         O       CT32B3_MAT1 — 32-bit CT32B3 match output 1.       I       R — Reserved.         I/O       SWCLK — Serial Wire Clock. This is the default function after booting.       I/O         SWDIO/       G5       53       [2]       PU       I/O         PIO_17       General-purpose digital input/output pin. After booting.       I/O         VIO_17       G5       53       [2]       PU       I/O         VIO_17       G5       53       [2]       PU       I/O       SPI0_SSEL3 — Slave Select 3 for SPI0.         O       U1_RTS — Request To Send output for USART1.       O       CT32B3_MAT2 — 32-bit CT32B3 match output 2.         I       R — Reserved.       I       R — Reserved.       I <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>I</td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                   |       |      |       |     |        | I    |                                                                                   |

| SWCLK/       F5       52       12       PU       I/O       SPI0_SSEL1 — Slave Select 1 for SPI0.         IVO       SWO — Serial wire trace output.       O       CT32B2_MAT2 — 32-bit CT32B2 match output 2.         I       R — Reserved.         SWCLK/       F5       52       12       PU       I/O       PIO0_16 — General-purpose digital input/output pin. After booting, this pin is connected to the SWCLK.       I/O       SPI0_SSEL2 — Slave Select 2 for SPI0.       I       U1_CTS — Clear To Send input for USART1.       O       CT32B3_MAT1 — 32-bit CT32B3 match output 1.       I       R — Reserved.         I/O       SWCLK — Serial Wire Clock. This is the default function after booting.       I/O       SWCLK — Serial Wire Clock. This is the default function after booting.         SWDIO/       G5       53       I2       PU       I/O       PIO0_17 — General-purpose digital input/output pin. After booting, this pin is connected to SWDIO.         FIO0_17       G5       F3       I2       PU       I/O       PIO0_17 — General-purpose digital input/output pin. After booting, this pin is connected to SWDIO.         I/O       SPI0_SSEL3 — Slave Select 3 for SPI0.       I/O       U1_RTS — Request To Send output for USART1.         O       CT32B3_MAT2 — 32-bit CT32B3 match output 2.       I       R — Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | PIO0_15/TD        | 5/TDO |      | 50    | [2] | PU     | I/O  |                                                                                   |

| Image: Ward Stress of the symbol of the s |                   |       |      |       |     |        |      |                                                                                   |

| SWCLK/       F5       52       I/2       PU       I/O       PIO0_16 — General-purpose digital input/output pin. After booting, this pin is connected to the SWCLK.         PIO0_16       F5       52       I/2       PU       I/O       PIO0_16 — General-purpose digital input/output pin. After booting, this pin is connected to the SWCLK.         I/O       SPI0_SSEL2 — Slave Select 2 for SPI0.       I/O       U1_CTS — Clear To Send input for USART1.         O       CT32B3_MAT1 — 32-bit CT32B3 match output 1.       I       R — Reserved.         I/O       SWCLK — Serial Wire Clock. This is the default function after booting.       VI         SWDIO/       G5       53       I/2       PU       I/O       PIO0_17 — General-purpose digital input/output pin. After booting, this pin is connected to SWDIO.         SWDIO/       G5       53       I/2       PU       I/O       PIO0_17 — General-purpose digital input/output pin. After booting, this pin is connected to SWDIO.         I/O       SPI0_SSEL3 — Slave Select 3 for SPI0.       O       U1_RTS — Request To Send output for USART1.         O       CT32B3_MAT2 — 32-bit CT32B3 match output 2.       I       R — Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                   |       |      |       |     |        |      |                                                                                   |

| SWCLK/       F5       52       I2       PLO_16 — General-purpose digital input/output pin. After booting, this pin is connected to the SWCLK.         PIO0_16       F5       52       I2       PU       I/O       SPI0_SSEL2 — Slave Select 2 for SPI0.         I       U1_CTS — Clear To Send input for USART1.       O       CT32B3_MAT1 — 32-bit CT32B3 match output 1.         I       R — Reserved.       I/O       SWCLK — Serial Wire Clock. This is the default function after booting.         SWDIO/       F100_17       G5       53       I2       PU       I/O       PIO_17 — General-purpose digital input/output pin. After booting, this pin is connected to SWDIO.         PIO0_17       G5       53       I2       PU       I/O       PIO_17 — General-purpose digital input/output pin. After booting, this pin is connected to SWDIO.         I/O       SPI0_SSEL3 — Slave Select 3 for SPI0.       O       U1_RTS — Request To Send output for USART1.         O       CT32B3_MAT2 — 32-bit CT32B3 match output 2.       I       R — Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   |       |      |       |     |        |      |                                                                                   |

| SWCLK/<br>PIO0_16       F5       52       I2       PU       I/O       PIO0_16 — General-purpose digital input/output pin. After booting, this pin is<br>connected to the SWCLK.         I/O       SPI0_SSEL2 — Slave Select 2 for SPI0.         I       U1_CTS — Clear To Send input for USART1.         O       CT32B3_MAT1 — 32-bit CT32B3 match output 1.         I       R — Reserved.         I/O       SWCLK — Serial Wire Clock. This is the default function after booting.         SWDIO/<br>PIO0_17       G5       53       I2       PU         I/O       SWCLK — Serial Wire Clock. This is the default function after booting.         I/O       SWCLK — Serial Wire Clock. This is the default function after booting.         I/O       SWCLK — Serial Wire Clock. This is the default function after booting.         I/O       SWDLO/<br>PIO0_17 — General-purpose digital input/output pin. After booting, this pin is<br>connected to SWDIO.         I/O       SPI0_SSEL3 — Slave Select 3 for SPI0.         O       U1_RTS — Request To Send output for USART1.         O       CT32B3_MAT2 — 32-bit CT32B3 match output 2.         I       R — Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                   |       |      |       |     |        | 0    |                                                                                   |

| PIO0_16       Image: Second connected to the SWCLK.         I/O       SPI0_SSEL2 — Slave Select 2 for SPI0.         I       U1_CTS — Clear To Send input for USART1.         O       CT32B3_MAT1 — 32-bit CT32B3 match output 1.         I       R — Reserved.         I/O       SWCLK — Serial Wire Clock. This is the default function after booting.         SWDIO/       G5       53       Image: Project and the symptote and the symptot and the symptot and the symptot and the symptot and the                                                                                                                                                                                                                                              |                   |       |      |       |     |        | I    |                                                                                   |

| I       U1_CTS — Clear To Send input for USART1.         O       CT32B3_MAT1 — 32-bit CT32B3 match output 1.         I       R — Reserved.         I/O       SWCLK — Serial Wire Clock. This is the default function after booting.         SWDIO/<br>PIO0_17       G5       53       I2       PU       I/O       PIO0_17 — General-purpose digital input/output pin. After booting, this pin is connected to SWDIO.         I/O       SPI0_SSEL3 — Slave Select 3 for SPI0.       O       U1_RTS — Request To Send output for USART1.         O       CT32B3_MAT2 — 32-bit CT32B3 match output 2.       I       R — Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SWCLK/<br>PIO0_16 |       | F5   | 52    | [2] | PU     | I/O  |                                                                                   |

| WDIO/       PIO0_17       G5       53       I       PIO0_17       PIO0_SPIO_SEL3 — Slave Select 3 for SPI0.         O       CT32B3_MAT1 — 32-bit CT32B3 match output 1.       I       R — Reserved.         I/O       SWCLK — Serial Wire Clock. This is the default function after booting.         SWDIO/       PIO0_17       G5       G5         O       CT32B3_MAT1 — 32-bit CT32B3 match output pin. After booting.         I/O       SWCLK — Serial Wire Clock. This is the default function after booting.         VI       PIO0_17 — General-purpose digital input/output pin. After booting, this pin is connected to SWDIO.         I/O       SPI0_SSEL3 — Slave Select 3 for SPI0.         O       U1_RTS — Request To Send output for USART1.         O       CT32B3_MAT2 — 32-bit CT32B3 match output 2.         I       R — Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                   |       |      |       |     |        | I/O  | SPI0_SSEL2 — Slave Select 2 for SPI0.                                             |

| I       R — Reserved.         I/O       SWCLK — Serial Wire Clock. This is the default function after booting.         SWDIO/<br>PIO0_17       G5       53       I       PU       I/O       PIO0_17 — General-purpose digital input/output pin. After booting, this pin is connected to SWDIO.         I/O       SPI0_SSEL3 — Slave Select 3 for SPI0.       O       U1_RTS — Request To Send output for USART1.         O       CT32B3_MAT2 — 32-bit CT32B3 match output 2.       I       R — Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                   |       |      |       |     |        | I    | <b>U1_CTS</b> — Clear To Send input for USART1.                                   |

| SWDIO/       G5       53       I/O       SWCLK — Serial Wire Clock. This is the default function after booting.         SWDIO_17       G5       53       I/O       PIO0_17 — General-purpose digital input/output pin. After booting, this pin is connected to SWDIO.         PIO0_17       G5       53       I/O       PIO0_SSEL3 — Slave Select 3 for SPIO.         O       U1_RTS — Request To Send output for USART1.       O       CT32B3_MAT2 — 32-bit CT32B3 match output 2.         I       R — Reserved.       I       R — Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                   |       |      |       |     |        | 0    | CT32B3_MAT1 — 32-bit CT32B3 match output 1.                                       |

| SWDIO/       G5       53       I       PU       I/O       PIO0_17 — General-purpose digital input/output pin. After booting, this pin is connected to SWDIO.         PIO0_17       I/O       SPI0_SSEL3 — Slave Select 3 for SPI0.         O       U1_RTS — Request To Send output for USART1.         O       CT32B3_MAT2 — 32-bit CT32B3 match output 2.         I       R — Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                   |       |      |       |     |        | I    | R — Reserved.                                                                     |

| PIO0_17       image: connected to SWDIO.         I/O       SPI0_SSEL3 — Slave Select 3 for SPI0.         O       U1_RTS — Request To Send output for USART1.         O       CT32B3_MAT2 — 32-bit CT32B3 match output 2.         I       R — Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                   |       |      |       |     |        | I/O  | <b>SWCLK</b> — Serial Wire Clock. This is the default function after booting.     |

| <ul> <li>O U1_RTS — Request To Send output for USART1.</li> <li>O CT32B3_MAT2 — 32-bit CT32B3 match output 2.</li> <li>I R — Reserved.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SWDIO/<br>PIO0_17 |       | G5   | 53    | [2] | PU     | I/O  |                                                                                   |

| O         CT32B3_MAT2 — 32-bit CT32B3 match output 2.           I         R — Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                   |       |      |       |     |        | I/O  | SPI0_SSEL3 — Slave Select 3 for SPI0.                                             |

| I R — Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                   |       |      |       |     |        | 0    | U1_RTS — Request To Send output for USART1.                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                   |       |      |       |     |        | 0    | CT32B3_MAT2 — 32-bit CT32B3 match output 2.                                       |

| I/O <b>SWDIO</b> — Serial Wire Debug I/O. This is the default function after booting.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                   |       |      |       |     |        | I    | R — Reserved.                                                                     |