Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Obsolete                                                                        |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | C166SV2                                                                         |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 66MHz                                                                           |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI                    |

| Peripherals                | I <sup>2</sup> S, POR, PWM, WDT                                                 |

| Number of I/O              | 75                                                                              |

| Program Memory Size        | 768KB (768K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 82K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                       |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-LQFP Exposed Pad                                                            |

| Supplier Device Package    | PG-LQFP-100-3                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/saf-xe164h-96f66l-ac |

|                            |                                                                                 |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# XE164 16-Bit Single-Chip Real Time Signal Controller

# Microcontrollers

Never stop thinking

#### **Summary of Features**

- 2) Specific inormation about the on-chip Flash memory in Table 2.

- All derivatives additionally provide 1 Kbyte SBRAM, 2 Kbytes DPRAM, and 16 Kbytes DSRAM (12 Kbytes for devices with 192 Kbytes of Flash).

- 4) Specific information about the available channels in Table 3.

Analog input channels are listed for each Analog/Digital Converter module separately (ADC0 + ADC1).

# 2 General Device Information

The XE164 series of real time signal controllers is a part of the Infineon XE166 Family of full-feature single-chip CMOS microcontrollers. These devices extend the functionality and performance of the C166 Family in terms of instructions (MAC unit), peripherals, and speed. They combine high CPU performance (up to 80 million instructions per second) with extended peripheral functionality and enhanced IO capabilities. Optimized peripherals can be adapted flexibly to meet the application requirements. These derivatives utilize clock generation via PLL and internal or external clock sources. On-chip memory modules include program Flash, program RAM, and data RAM.

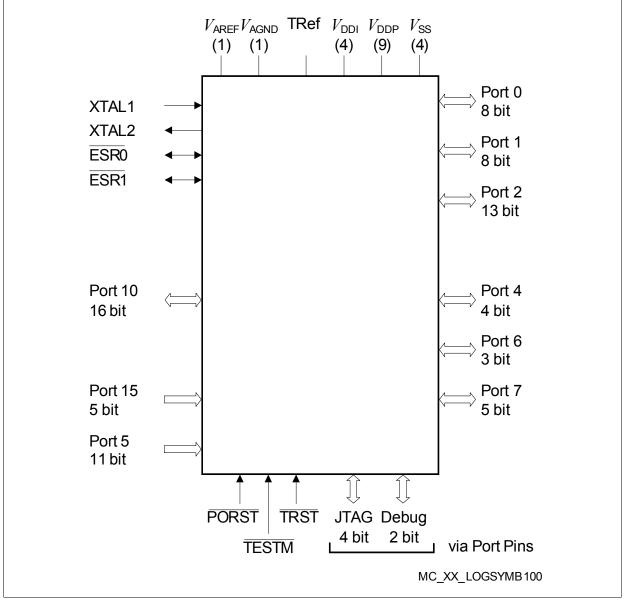

Figure 1 Logic Symbol

#### **Notes to Pin Definitions**

Ctrl.: The output signal for a port pin is selected by bitfield PC in the associated register Px\_IOCRy. Output O0 is selected by setting the respective bitfield PC to 1x00<sub>B</sub>, output O1 is selected by 1x01<sub>B</sub>, etc. Output signal OH is controlled by hardware.

2. **Type**: Indicates the pad type used (St=standard pad, Sp=special pad, DP=double pad, In=input pad, PS=power supply) and its power supply domain (A, B, M, 1).

| Pin | Symbol            | Ctrl.  | Туре | Function                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|-----|-------------------|--------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 3   | TESTM             | 1      | In/B | Testmode EnableEnables factory test modes, must be held HIGH fornormal operation (connect to $V_{\text{DDPB}}$ ).An internal pullup device will hold this pin highwhen nothing is driving it.                                                                                                                                                                   |  |  |  |

| 4   | P7.2              | O0 / I | St/B | Bit 2 of Port 7, General Purpose Input/Output                                                                                                                                                                                                                                                                                                                   |  |  |  |

|     | EMUX0             | 01     | St/B | External Analog MUX Control Output 0 (ADC1)                                                                                                                                                                                                                                                                                                                     |  |  |  |

|     | CCU62_<br>CCPOS0A | I      | St/B | CCU62 Position Input 0                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|     | TDI_C             | I      | St/B | JTAG Test Data Input                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 5   | TRST              | 1      | In/B | <b>Test-System Reset Input</b><br>For normal system operation, pin TRST should be<br>held low. A high level at this pin at the rising edge<br>of PORST activates the XE164's debug system. In<br>this case, pin TRST must be driven low once to<br>reset the debug system.<br>An internal pulldown device will hold this pin low<br>when nothing is driving it. |  |  |  |

| 6   | P7.0              | O0 / I | St/B | Bit 0 of Port 7, General Purpose Input/Output                                                                                                                                                                                                                                                                                                                   |  |  |  |

|     | T3OUT             | 01     | St/B | GPT1 Timer T3 Toggle Latch Output                                                                                                                                                                                                                                                                                                                               |  |  |  |

|     | T6OUT             | O2     | St/B | GPT2 Timer T6 Toggle Latch Output                                                                                                                                                                                                                                                                                                                               |  |  |  |

|     | TDO_A             | OH     | St/B | JTAG Test Data Output                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|     | ESR2_1            | I      | St/B | ESR2 Trigger Input 1                                                                                                                                                                                                                                                                                                                                            |  |  |  |

#### Table 4Pin Definitions and Functions

| Table 4Pin Definitions and Functions (cont'd) |                  |        |      |                                               |  |  |

|-----------------------------------------------|------------------|--------|------|-----------------------------------------------|--|--|

| Pin                                           | Symbol           | Ctrl.  | Туре | Function                                      |  |  |

| 43                                            | P2.3             | O0 / I | St/B | Bit 3 of Port 2, General Purpose Input/Output |  |  |

|                                               | U0C0_DOUT        | 01     | St/B | USIC0 Channel 0 Shift Data Output             |  |  |

|                                               | CC2_16           | O3 / I | St/B | CAPCOM2 CC16IO Capture Inp./ Compare Out.     |  |  |

|                                               | A16              | OH     | St/B | External Bus Interface Address Line 16        |  |  |

|                                               | ESR2_0           | I      | St/B | ESR2 Trigger Input 0                          |  |  |

|                                               | U0C0_DX0E        | I      | St/B | USIC0 Channel 0 Shift Data Input              |  |  |

|                                               | U0C1_DX0D        | I      | St/B | USIC0 Channel 1 Shift Data Input              |  |  |

|                                               | RxDC0A           | I      | St/B | CAN Node 0 Receive Data Input                 |  |  |

| 44                                            | P4.1             | O0 / I | St/B | Bit 1 of Port 4, General Purpose Input/Output |  |  |

|                                               | TxDC2            | 02     | St/B | CAN Node 2 Transmit Data Output               |  |  |

|                                               | CC2_25           | O3 / I | St/B | CAPCOM2 CC25IO Capture Inp./ Compare Out.     |  |  |

|                                               | CS1              | ОН     | St/B | External Bus Interface Chip Select 1 Output   |  |  |

| 45                                            | P2.4             | O0 / I | St/B | Bit 4 of Port 2, General Purpose Input/Output |  |  |

|                                               | U0C1_DOUT        | 01     | St/B | USIC0 Channel 1 Shift Data Output             |  |  |

|                                               | TxDC0            | 02     | St/B | CAN Node 0 Transmit Data Output               |  |  |

|                                               | CC2_17           | O3 / I | St/B | CAPCOM2 CC17IO Capture Inp./ Compare Out.     |  |  |

|                                               | A17              | ОН     | St/B | External Bus Interface Address Line 17        |  |  |

|                                               | ESR1_0           | I      | St/B | ESR1 Trigger Input 0                          |  |  |

|                                               | U0C0_DX0F        | I      | St/B | USIC0 Channel 0 Shift Data Input              |  |  |

|                                               | RxDC1A           | I      | St/B | CAN Node 1 Receive Data Input                 |  |  |

| 46                                            | P2.5             | O0 / I | St/B | Bit 5 of Port 2, General Purpose Input/Output |  |  |

|                                               | U0C0_<br>SCLKOUT | 01     | St/B | USIC0 Channel 0 Shift Clock Output            |  |  |

|                                               | TxDC0            | 02     | St/B | CAN Node 0 Transmit Data Output               |  |  |

|                                               | CC2_18           | O3 / I | St/B | CAPCOM2 CC18IO Capture Inp./ Compare Out.     |  |  |

|                                               | A18              | OH     | St/B | External Bus Interface Address Line 18        |  |  |

|                                               | U0C0_DX1D        | I      | St/B | USIC0 Channel 0 Shift Clock Input             |  |  |

| Tabl | Table 4Pin Definitions and Functions (cont'd) |        |      |                                               |  |  |

|------|-----------------------------------------------|--------|------|-----------------------------------------------|--|--|

| Pin  | Symbol                                        | Ctrl.  | Туре | Function                                      |  |  |

| 54   | P2.7                                          | O0 / I | St/B | Bit 7 of Port 2, General Purpose Input/Output |  |  |

|      | U0C1_<br>SELO0                                | 01     | St/B | USIC0 Channel 1 Select/Control 0 Output       |  |  |

|      | U0C0_<br>SELO1                                | O2     | St/B | USIC0 Channel 0 Select/Control 1 Output       |  |  |

|      | CC2_20                                        | O3 / I | St/B | CAPCOM2 CC20IO Capture Inp./ Compare Out.     |  |  |

|      | A20                                           | OH     | St/B | External Bus Interface Address Line 20        |  |  |

|      | U0C1_DX2C                                     | I      | St/B | USIC0 Channel 1 Shift Control Input           |  |  |

|      | RxDC1C                                        | I      | St/B | CAN Node 1 Receive Data Input                 |  |  |

| 55   | P0.1                                          | 00 / 1 | St/B | Bit 1 of Port 0, General Purpose Input/Output |  |  |

|      | U1C0_DOUT                                     | 01     | St/B | USIC1 Channel 0 Shift Data Output             |  |  |

|      | TxDC0                                         | 02     | St/B | CAN Node 0 Transmit Data Output               |  |  |

|      | CCU61_<br>CC61                                | O3 / I | St/B | CCU61 Channel 1 Input/Output                  |  |  |

|      | A1                                            | OH     | St/B | External Bus Interface Address Line 1         |  |  |

|      | U1C0_DX0B                                     | I      | St/B | USIC1 Channel 0 Shift Data Input              |  |  |

|      | U1C0_DX1A                                     | I      | St/B | USIC1 Channel 0 Shift Clock Input             |  |  |

| 56   | P2.8                                          | O0 / I | DP/B | Bit 8 of Port 2, General Purpose Input/Output |  |  |

|      | U0C1_<br>SCLKOUT                              | 01     | DP/B | USIC0 Channel 1 Shift Clock Output            |  |  |

|      | EXTCLK                                        | O2     | DP/B | Programmable Clock Signal Output              |  |  |

|      | CC2_21                                        | O3 / I | DP/B | CAPCOM2 CC21IO Capture Inp./ Compare Out.     |  |  |

|      | A21                                           | OH     | DP/B | External Bus Interface Address Line 21        |  |  |

|      | U0C1_DX1D                                     | I      | DP/B | USIC0 Channel 1 Shift Clock Input             |  |  |

| 57   | P2.9                                          | O0 / I | St/B | Bit 9 of Port 2, General Purpose Input/Output |  |  |

|      | U0C1_DOUT                                     | 01     | St/B | USIC0 Channel 1 Shift Data Output             |  |  |

|      | TxDC1                                         | 02     | St/B | CAN Node 1 Transmit Data Output               |  |  |

|      | CC2_22                                        | O3 / I | St/B | CAPCOM2 CC22IO Capture Inp./ Compare Out.     |  |  |

|      | A22                                           | OH     | St/B | External Bus Interface Address Line 22        |  |  |

|      | CLKIN1                                        | I      | St/B | Clock Signal Input                            |  |  |

|      | TCK_A                                         | I      | St/B | JTAG Clock Input                              |  |  |

| Table 4Pin Definitions and Functions (cont'd) |                  |        |      |                                                |  |  |

|-----------------------------------------------|------------------|--------|------|------------------------------------------------|--|--|

| Pin                                           | Symbol           | Ctrl.  | Туре | Function                                       |  |  |

| 70                                            | P10.5            | O0 / I | St/B | Bit 5 of Port 10, General Purpose Input/Output |  |  |

|                                               | U0C1_<br>SCLKOUT | 01     | St/B | USIC0 Channel 1 Shift Clock Output             |  |  |

|                                               | CCU60_<br>COUT62 | O2     | St/B | CCU60 Channel 2 Output                         |  |  |

|                                               | AD5              | OH/I   | St/B | External Bus Interface Address/Data Line 5     |  |  |

|                                               | U0C1_DX1B        | I      | St/B | USIC0 Channel 1 Shift Clock Input              |  |  |

| 71                                            | P0.6             | O0 / I | St/B | Bit 6 of Port 0, General Purpose Input/Output  |  |  |

|                                               | U1C1_DOUT        | 01     | St/B | USIC1 Channel 1 Shift Data Output              |  |  |

|                                               | TxDC1            | 02     | St/B | CAN Node 1 Transmit Data Output                |  |  |

|                                               | CCU61_<br>COUT63 | O3     | St/B | CCU61 Channel 3 Output                         |  |  |

|                                               | A6               | OH     | St/B | External Bus Interface Address Line 6          |  |  |

|                                               | U1C1_DX0A        | I      | St/B | USIC1 Channel 1 Shift Data Input               |  |  |

|                                               | CCU61_<br>CTRAPA | I      | St/B | CCU61 Emergency Trap Input                     |  |  |

|                                               | U1C1_DX1B        | 1      | St/B | USIC1 Channel 1 Shift Clock Input              |  |  |

| 72                                            | P10.6            | O0 / I | St/B | Bit 6 of Port 10, General Purpose Input/Output |  |  |

|                                               | U0C0_DOUT        | 01     | St/B | USIC0 Channel 0 Shift Data Output              |  |  |

|                                               | U1C0_<br>SELO0   | O3     | St/B | USIC1 Channel 0 Select/Control 0 Output        |  |  |

|                                               | AD6              | OH/I   | St/B | External Bus Interface Address/Data Line 6     |  |  |

|                                               | U0C0_DX0C        | I      | St/B | USIC0 Channel 0 Shift Data Input               |  |  |

|                                               | U1C0_DX2D        | I      | St/B | USIC1 Channel 0 Shift Control Input            |  |  |

|                                               | CCU60_<br>CTRAPA | I      | St/B | CCU60 Emergency Trap Input                     |  |  |

| Table 4Pin Definitions and Functions (cont'd) |                  |        |      |                                                 |  |  |  |

|-----------------------------------------------|------------------|--------|------|-------------------------------------------------|--|--|--|

| Pin                                           | Symbol           | Ctrl.  | Туре | Function                                        |  |  |  |

| 82                                            | P10.10           | O0 / I | St/B | Bit 10 of Port 10, General Purpose Input/Output |  |  |  |

|                                               | U0C0_<br>SELO0   | 01     | St/B | USIC0 Channel 0 Select/Control 0 Output         |  |  |  |

|                                               | CCU60_<br>COUT63 | O2     | St/B | CCU60 Channel 3 Output                          |  |  |  |

|                                               | AD10             | OH/I   | St/B | External Bus Interface Address/Data Line 10     |  |  |  |

|                                               | U0C0_DX2C        | I      | St/B | USIC0 Channel 0 Shift Control Input             |  |  |  |

|                                               | TDI_B            | I      | St/B | JTAG Test Data Input                            |  |  |  |

|                                               | U0C1_DX1A        | I      | St/B | USIC0 Channel 1 Shift Clock Input               |  |  |  |

| 83                                            | P10.11           | O0 / I | St/B | Bit 11 of Port 10, General Purpose Input/Output |  |  |  |

|                                               | U1C0_<br>SCLKOUT | 01     | St/B | USIC1 Channel 0 Shift Clock Output              |  |  |  |

|                                               | BRKOUT           | 02     | St/B | OCDS Break Signal Output                        |  |  |  |

|                                               | AD11             | OH/I   | St/B | External Bus Interface Address/Data Line 11     |  |  |  |

|                                               | U1C0_DX1D        | I      | St/B | USIC1 Channel 0 Shift Clock Input               |  |  |  |

|                                               | RxDC2B           | I      | St/B | CAN Node 2 Receive Data Input                   |  |  |  |

|                                               | TMS_B            | I      | St/B | JTAG Test Mode Selection Input                  |  |  |  |

| 84                                            | P1.2             | O0 / I | St/B | Bit 2 of Port 1, General Purpose Input/Output   |  |  |  |

|                                               | CCU62_<br>CC62   | 01 / I | St/B | CCU62 Channel 2 Input/Output                    |  |  |  |

|                                               | U1C0_<br>SELO6   | O2     | St/B | USIC1 Channel 0 Select/Control 6 Output         |  |  |  |

|                                               | U2C1_<br>SCLKOUT | O3     | St/B | USIC2 Channel 1 Shift Clock Output              |  |  |  |

|                                               | A10              | ОН     | St/B | External Bus Interface Address Line 10          |  |  |  |

|                                               | ESR1_4           | I      | St/B | ESR1 Trigger Input 4                            |  |  |  |

|                                               | CCU61_<br>T12HRB | I      | St/B | External Run Control Input for T12 of CCU61     |  |  |  |

|                                               | EX2AINA          | I      | St/B | External Interrupt Trigger Input                |  |  |  |

|                                               | U2C1_DX0D        | I      | St/B | USIC2 Channel 1 Shift Data Input                |  |  |  |

|                                               | U2C1_DX1C        | I      | St/B | USIC2 Channel 1 Shift Clock Input               |  |  |  |

# 3.1 Memory Subsystem and Organization

The memory space of the XE164 is configured in the von Neumann architecture. In this architecture all internal and external resources, including code memory, data memory, registers and I/O ports, are organized in the same linear address space.

| Address Area                         | Start Loc.           | End Loc.             | Area Size <sup>1)</sup> | Notes               |

|--------------------------------------|----------------------|----------------------|-------------------------|---------------------|

| IMB register space                   | FF'FF00 <sub>H</sub> | FF'FFFF <sub>H</sub> | 256 Bytes               | -                   |

| Reserved (Access trap)               | F0'0000 <sub>H</sub> | FF'FEFF <sub>H</sub> | <1 Mbyte                | Minus IMB registers |

| Reserved for EPSRAM                  | E9'0000 <sub>H</sub> | EF'FFFF <sub>H</sub> | 448 Kbytes              | Mirrors EPSRAM      |

| Emulated PSRAM                       | E8'0000 <sub>H</sub> | E8'FFFF <sub>H</sub> | 64 Kbytes               | Flash timing        |

| Reserved for PSRAM                   | E1'0000 <sub>H</sub> | E7'FFFF <sub>H</sub> | 448 Kbytes              | Mirrors PSRAM       |

| Program SRAM                         | E0'0000 <sub>H</sub> | E0'FFFF <sub>H</sub> | 64 Kbytes               | Maximum speed       |

| Reserved for pr. mem.                | CC'0000 <sub>H</sub> | DF'FFFF <sub>H</sub> | <1.25 Mbytes            | -                   |

| Program Flash 2                      | C8'0000 <sub>H</sub> | CB'FFFF <sub>H</sub> | 256 Kbytes              | -                   |

| Program Flash 1                      | C4'0000 <sub>H</sub> | C7'FFFF <sub>H</sub> | 256 Kbytes              | -                   |

| Program Flash 0                      | C0'0000 <sub>H</sub> | C3'FFFF <sub>H</sub> | 256 Kbytes              | 2)                  |

| External memory area                 | 40'0000 <sub>H</sub> | BF'FFFF <sub>H</sub> | 8 Mbytes                | -                   |

| Available Ext. IO area <sup>3)</sup> | 20'5800 <sub>H</sub> | 3F'FFFF <sub>H</sub> | < 2 Mbytes              | Minus USIC/CAN      |

| USIC registers                       | 20'4000 <sub>H</sub> | 20'57FF <sub>H</sub> | 6 Kbytes                | Accessed via EBC    |

| MultiCAN registers                   | 20'0000 <sub>H</sub> | 20'3FFF <sub>H</sub> | 16 Kbytes               | Accessed via EBC    |

| External memory area                 | 01'0000 <sub>H</sub> | 1F'FFFF <sub>H</sub> | < 2 Mbytes              | Minus segment 0     |

| SFR area                             | 00'FE00 <sub>H</sub> | 00'FFFF <sub>H</sub> | 0.5 Kbyte               | -                   |

| Dual-Port RAM                        | 00'F600 <sub>H</sub> | 00'FDFF <sub>H</sub> | 2 Kbytes                | -                   |

| Reserved for DPRAM                   | 00'F200 <sub>H</sub> | 00'F5FF <sub>H</sub> | 1 Kbyte                 | -                   |

| ESFR area                            | 00'F000 <sub>H</sub> | 00'F1FF <sub>H</sub> | 0.5 Kbyte               | -                   |

| XSFR area                            | 00'E000 <sub>H</sub> | 00'EFFF <sub>H</sub> | 4 Kbytes                | -                   |

| Data SRAM                            | 00'A000 <sub>H</sub> | 00'DFFF <sub>H</sub> | 16 Kbytes               | -                   |

| Reserved for DSRAM                   | 00'8000 <sub>H</sub> | 00'9FFF <sub>H</sub> | 8 Kbytes                | -                   |

| External memory area                 | 00'000 <sub>H</sub>  | 00'7FFF <sub>H</sub> | 32 Kbytes               | -                   |

#### Table 5XE164 Memory Map

1) The areas marked with "<" are slightly smaller than indicated. See column "Notes".

2) The uppermost 4-Kbyte sector of the first Flash segment is reserved for internal use (C0'F000<sub>H</sub> to C0'FFFF<sub>H</sub>).

3) Several pipeline optimizations are not active within the external IO area. This is necessary to control external peripherals properly.

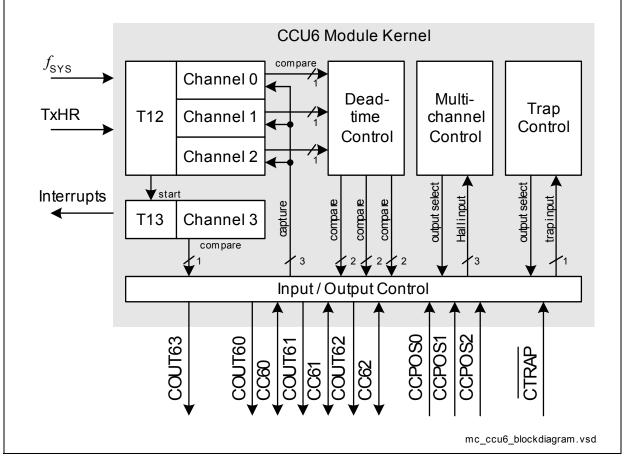

Figure 6 CCU6 Block Diagram

Timer T12 can work in capture and/or compare mode for its three channels. The modes can also be combined. Timer T13 can work in compare mode only. The multi-channel control unit generates output patterns that can be modulated by timer T12 and/or timer T13. The modulation sources can be selected and combined for signal modulation.

# 3.8 General Purpose Timer (GPT12E) Unit

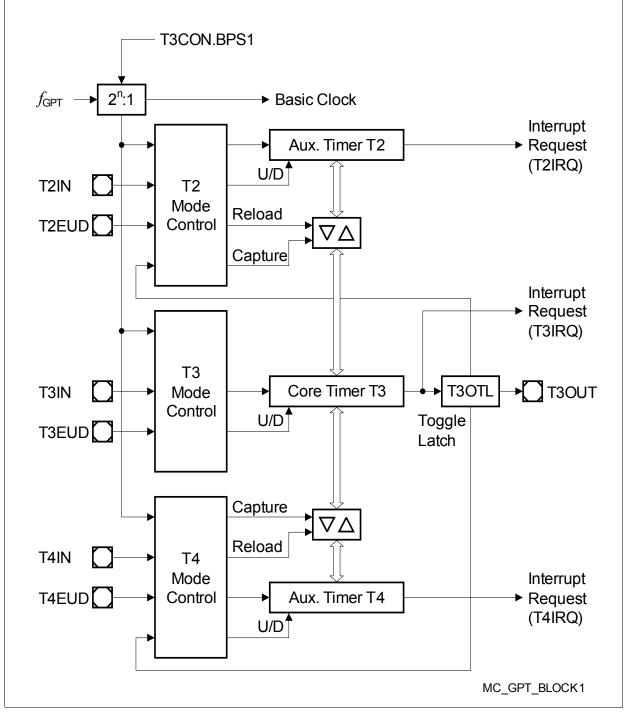

The GPT12E unit is a very flexible multifunctional timer/counter structure which can be used for many different timing tasks such as event timing and counting, pulse width and duty cycle measurements, pulse generation, or pulse multiplication.

The GPT12E unit incorporates five 16-bit timers organized in two separate modules, GPT1 and GPT2. Each timer in each module may either operate independently in a number of different modes or be concatenated with another timer of the same module.

Each of the three timers T2, T3, T4 of **module GPT1** can be configured individually for one of four basic modes of operation: Timer, Gated Timer, Counter, and Incremental Interface Mode. In Timer Mode, the input clock for a timer is derived from the system clock and divided by a programmable prescaler. Counter Mode allows timer clocking in reference to external events.

Pulse width or duty cycle measurement is supported in Gated Timer Mode, where the operation of a timer is controlled by the 'gate' level on an external input pin. For these purposes each timer has one associated port pin  $(TxIN^{1})$  which serves as a gate or clock input. The maximum resolution of the timers in module GPT1 is 4 system clock cycles.

The counting direction (up/down) for each timer can be programmed by software or altered dynamically by an external signal on a port pin (TxEUD<sup>1</sup>), e.g. to facilitate position tracking.

In Incremental Interface Mode the GPT1 timers<sup>1)</sup> can be directly connected to the incremental position sensor signals A and B through their respective inputs TxIN and TxEUD. Direction and counting signals are internally derived from these two input signals, so that the contents of the respective timer Tx corresponds to the sensor position. The third position sensor signal TOP0 can be connected to an interrupt input.

Timer T3 has an output toggle latch (T3OTL) which changes its state on each timer overflow/underflow. The state of this latch may be output on pin T3OUT e.g. for time out monitoring of external hardware components. It may also be used internally to clock timers T2 and T4 for measuring long time periods with high resolution.

In addition to the basic operating modes, T2 may be configured as reload or capture register for timer T3. A timer used as capture or reload register is stopped. The contents of timer T3 is captured into T2 in response to a signal at the associated input pin (TxIN). Timer T3 is reloaded with the contents of T2, triggered either by an external signal or a selectable state transition of its toggle latch T3OTL.

<sup>1)</sup> Exception: Timer T4 is not connected to pins.

Figure 7 Block Diagram of GPT1

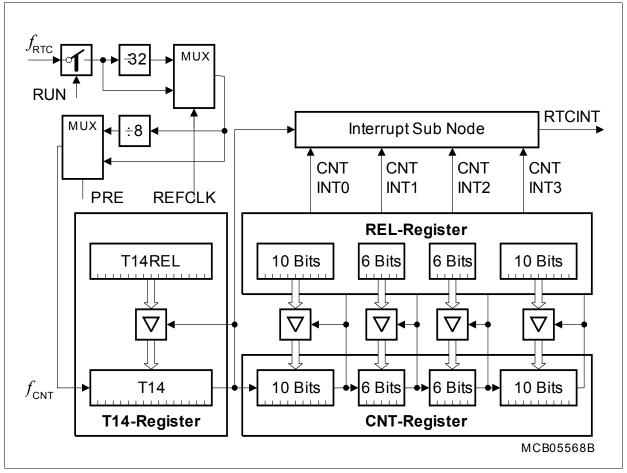

# 3.9 Real Time Clock

The Real Time Clock (RTC) module of the XE164 can be clocked with a clock signal selected from internal sources or external sources (pins).

The RTC basically consists of a chain of divider blocks:

- Selectable 32:1 and 8:1 dividers (on off)

- The reloadable 16-bit timer T14

- The 32-bit RTC timer block (accessible via registers RTCH and RTCL) consisting of: – a reloadable 10-bit timer

- a reloadable 6-bit timer

- a reloadable 6-bit timer

- a reloadable 10-bit timer

All timers count up. Each timer can generate an interrupt request. All requests are combined to a common node request.

#### Figure 9 RTC Block Diagram

Note: The registers associated with the RTC are only affected by a power reset.

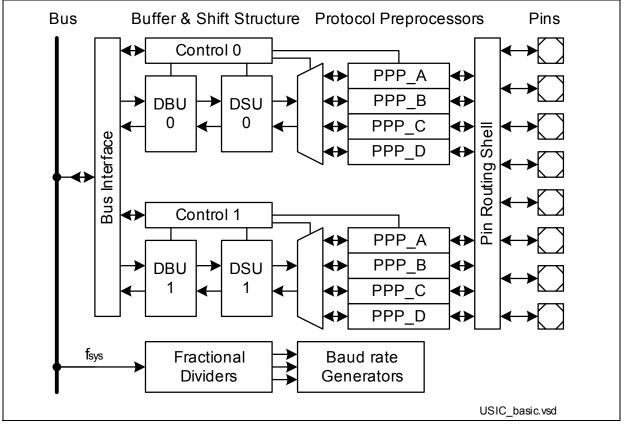

# 3.11 Universal Serial Interface Channel Modules (USIC)

The XE164 includes up to three USIC modules (USIC0, USIC1, USIC2), each providing two serial communication channels.

The Universal Serial Interface Channel (USIC) module is based on a generic data shift and data storage structure which is identical for all supported serial communication protocols. Each channel supports complete full-duplex operation with a basic data buffer structure (one transmit buffer and two receive buffer stages). In addition, the data handling software can use FIFOs.

The protocol part (generation of shift clock/data/control signals) is independent of the general part and is handled by protocol-specific preprocessors (PPPs).

The USIC's input/output lines are connected to pins by a pin routing unit. The inputs and outputs of each USIC channel can be assigned to different interface pins, providing great flexibility to the application software. All assignments can be made during runtime.

#### Figure 10 General Structure of a USIC Module

The regular structure of the USIC module brings the following advantages:

- Higher flexibility through configuration with same look-and-feel for data management

- Reduced complexity for low-level drivers serving different protocols

- Wide range of protocols with improved performances (baud rate, buffer handling)

#### **MultiCAN Features**

- CAN functionality conforming to CAN specification V2.0 B active for each CAN node (compliant to ISO 11898)

- Up to four independent CAN nodes

- 128 independent message objects (shared by the CAN nodes)

- Dedicated control registers for each CAN node

- Data transfer rate up to 1 Mbit/s, individually programmable for each node

- Flexible and powerful message transfer control and error handling capabilities

- Full-CAN functionality for message objects:

- Can be assigned to one of the CAN nodes

- Configurable as transmit or receive objects, or as message buffer FIFO

- Handle 11-bit or 29-bit identifiers with programmable acceptance mask for filtering

- Remote Monitoring Mode, and frame counter for monitoring

- Automatic Gateway Mode support

- 16 individually programmable interrupt nodes

- Analyzer mode for CAN bus monitoring

- 4) As a rule, with decreasing output current the output levels approach the respective supply level ( $V_{OL} \rightarrow V_{SS}$ ,  $V_{OH} \rightarrow V_{DDP}$ ). However, only the levels for nominal output currents are verified.

- 5) This specification is not valid for outputs which are switched to open drain mode. In this case the respective output will float and the voltage is determined by the external circuit.

- 6) An additional error current ( $I_{INJ}$ ) will flow if an overload current flows through an adjacent pin. Please refer to the definition of the overload coupling factor  $K_{OV}$ .

- 7) The given values are worst-case values. In production test, this leakage current is only tested at 125°C; other values are ensured by correlation. For derating, please refer to the following descriptions:

Leakage derating depending on temperature ( $T_1$  = junction temperature [°C]):

$I_{OZ} = 0.05 \times e^{(1.5 + 0.028 \times TJ)} [\mu A]$ . For example, at a temperature of 95°C the resulting leakage current is 3.2  $\mu$ A. Leakage derating depending on voltage level (DV =  $V_{DDP}$  -  $V_{PIN}$  [V]):

$I_{OZ} = I_{OZtempmax} - (1.6 \times DV) [\mu A]$

This voltage derating formula is an approximation which applies for maximum temperature.

Because pin P2.8 is connected to two pads (standard pad and high-speed clock pad), it has twice the normal leakage.

8) Keep current: Limit the current through this pin to the indicated value so that the enabled pull device can keep the default pin level: V<sub>PIN</sub> ≥ V<sub>IH</sub> for a pullup; V<sub>PIN</sub> ≤ V<sub>IL</sub> for a pulldown. Force current: Drive the indicated minimum current through this pin to change the default pin level driven by

the enabled pull device:  $V_{\text{PIN}} \le V_{\text{IL}}$  for a pullup;  $V_{\text{PIN}} \ge V_{\text{IH}}$  for a pulldown. These values apply to the fixed pull-devices in dedicated pins and to the user-selectable pull-devices in

These values apply to the fixed pull-devices in dedicated pins and to the user-selectable pull-devices in general purpose IO pins.

Not subject to production test - verified by design/characterization. Because pin P2.8 is connected to two pads (standard pad and high-speed clock pad), it has twice the normal capacitance.

- 4) As a rule, with decreasing output current the output levels approach the respective supply level ( $V_{OL} \rightarrow V_{SS}$ ,  $V_{OH} \rightarrow V_{DDP}$ ). However, only the levels for nominal output currents are verified.

- 5) This specification is not valid for outputs which are switched to open drain mode. In this case the respective output will float and the voltage is determined by the external circuit.

- 6) An additional error current (*I*<sub>INJ</sub>) will flow if an overload current flows through an adjacent pin. Please refer to the definition of the overload coupling factor *K*<sub>OV</sub>.

The leakage current value is not tested in the lower voltage range but only in the upper voltage range. This parameter is ensured by correlation.

- 7) The given values are worst-case values. In production test, this leakage current is only tested at 125°C; other values are ensured by correlation. For derating, please refer to the following descriptions:

Leakage derating depending on temperature ( $T_{J}$  = junction temperature [°C]):

$I_{OZ} = 0.03 \times e^{(1.35 + 0.028 \times TJ)}$  [µA]. For example, at a temperature of 95°C the resulting leakage current is 1.65 µA. Leakage derating depending on voltage level (DV =  $V_{DDP}$  -  $V_{PIN}$  [V]):

$I_{OZ} = I_{OZtempmax} - (1.3 \times DV) [\mu A]$

This voltage derating formula is an approximation which applies for maximum temperature.

Because pin P2.8 is connected to two pads (standard pad and high-speed clock pad), it has twice the normal leakage.

8) Keep current: Limit the current through this pin to the indicated value so that the enabled pull device can keep the default pin level: V<sub>PIN</sub> ≥ V<sub>IH</sub> for a pullup; V<sub>PIN</sub> ≤ V<sub>IL</sub> for a pulldown. Force current: Drive the indicated minimum current through this pin to change the default pin level driven by

the enabled pull device:  $V_{\text{PIN}} \leq V_{\text{IL}}$  for a pullup;  $V_{\text{PIN}} \geq V_{\text{IH}}$  for a pulldown. These values apply to the fixed pull-devices in dedicated pins and to the user-selectable pull-devices in

general purpose IO pins.9) Not subject to production test - verified by design/characterization.

Because pin P2.8 is connected to two pads (standard pad and high-speed clock pad), it has twice the normal capacitance.

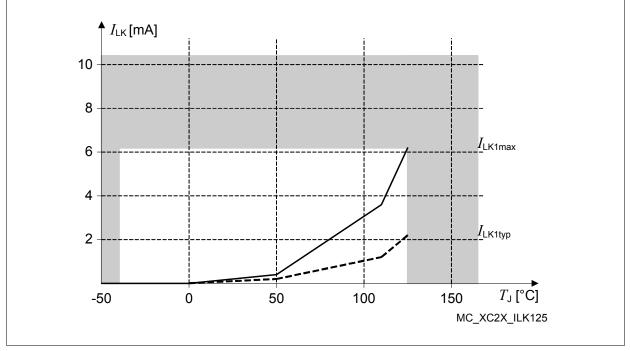

# Table 17Leakage Power Consumption XE164<br/>(Operating Conditions apply)

| Parameter                                                                                                                                                                 | Sym-          | Values |      |      | Unit | Note /                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------|------|------|------|-------------------------------|

|                                                                                                                                                                           | bol           | Min.   | Тур. | Max. |      | Test Condition <sup>1)</sup>  |

| Leakage supply current <sup>2)</sup><br>Formula <sup>3)</sup> : 600,000 × $e^{-\alpha}$ ;<br>$\alpha$ = 5000 / (273 + B×T <sub>J</sub> );<br>Typ.: B = 1.0, Max.: B = 1.3 | $I_{\rm LK1}$ | _      | 0.03 | 0.05 | mA   | <i>T</i> <sub>J</sub> = 25°C  |

|                                                                                                                                                                           |               | _      | 0.5  | 1.3  | mA   | <i>T</i> <sub>J</sub> = 85°C  |

|                                                                                                                                                                           |               | -      | 2.1  | 6.2  | mA   | <i>T</i> <sub>J</sub> = 125°C |

1) All inputs (including pins configured as inputs) are set at 0 V to 0.1 V or at  $V_{DDP}$  - 0.1 V to  $V_{DDP}$  and all outputs (including pins configured as outputs) are disconnected.

2) The supply current caused by leakage depends mainly on the junction temperature (see Figure 14) and the supply voltage. The temperature difference between the junction temperature  $T_J$  and the ambient temperature  $T_A$  must be taken into account. As this fraction of the supply current does not depend on device activity, it must be added to other power consumption values.

3) This formula is valid for temperatures above 0°C. For temperatures below 0°C a value of below 10  $\mu$ A can be assumed.

Figure 14 Leakage Supply Current as a Function of Temperature

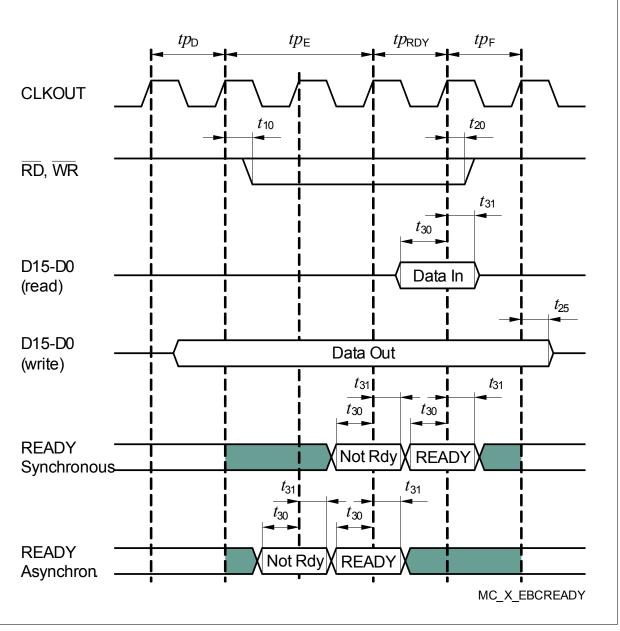

Figure 24 READY Timing

Note: If the READY input is sampled inactive at the indicated sampling point ("Not Rdy") a READY-controlled waitstate is inserted (tpRDY), sampling the READY input active at the indicated sampling point ("Boady")

sampling the READY input active at the indicated sampling point ("Ready") terminates the currently running bus cycle.

Note the different sampling points for synchronous and asynchronous READY. This example uses one mandatory waitstate (see tpE) before the READY input value is used.

www.infineon.com