Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | C166SV2                                                                         |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 66MHz                                                                           |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI            |

| Peripherals                | I <sup>2</sup> S, POR, PWM, WDT                                                 |

| Number of I/O              | 75                                                                              |

| Program Memory Size        | 384KB (384K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 34K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                       |

| Data Converters            | A/D 11x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-LQFP Exposed Pad                                                            |

| Supplier Device Package    | PG-LQFP-100-3                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xe164g48f66lacfxqma1 |

| 1               | Summary of Features 4                                                                |

|-----------------|--------------------------------------------------------------------------------------|

| <b>2</b><br>2.1 | General Device Information       9         Pin Configuration and Definition       10 |

| <b>3</b><br>3.1 | Functional Description                                                               |

| 3. i<br>3.2     | Memory Subsystem and Organization                                                    |

| 3.2<br>3.3      | Central Processing Unit (CPU)                                                        |

| 3.4             | Interrupt System                                                                     |

| 3.5             | On-Chip Debug Support (OCDS)                                                         |

| 3.6             | Capture/Compare Unit (CAPCOM2)                                                       |

| 3.7             | Capture/Compare Units CCU6x                                                          |

| 3.8             | General Purpose Timer (GPT12E) Unit                                                  |

| 3.9             | Real Time Clock 54                                                                   |

| 3.10            | A/D Converters 56                                                                    |

| 3.11            | Universal Serial Interface Channel Modules (USIC) 57                                 |

| 3.12            | MultiCAN Module                                                                      |

| 3.13            | Watchdog Timer                                                                       |

| 3.14            | Clock Generation                                                                     |

| 3.15            | Parallel Ports                                                                       |

| 3.16            | Instruction Set Summary                                                              |

| 4               | Electrical Parameters                                                                |

| 4.1             | General Parameters 67                                                                |

| 4.2             | DC Parameters 71                                                                     |

| 4.2.1           | DC Parameters for Upper Voltage Area                                                 |

| 4.2.2           | DC Parameters for Lower Voltage Area                                                 |

| 4.2.3           | Power Consumption                                                                    |

| 4.3<br>4.4      | Analog/Digital Converter Parameters                                                  |

| 4.4<br>4.5      | System Parameters                                                                    |

| 4.6             | Flash Memory Parameters                                                              |

| 4.6.1           | Testing Waveforms                                                                    |

| 4.6.2           | Definition of Internal Timing                                                        |

| 4.6.3           | External Clock Input Parameters                                                      |

| 4.6.4           | External Bus Timing                                                                  |

| 4.6.5           | Synchronous Serial Interface Timing                                                  |

| 4.6.6           | JTAG Interface Timing                                                                |

| 5               | Package and Reliability                                                              |

| 5.1             | Packaging                                                                            |

| 5.2             | Thermal Considerations 111                                                           |

# **General Device Information**

Table 4

Pin Definitions and Functions (cont'd)

| Pin | Symbol            | Ctrl.  | Type | Function                                       |

|-----|-------------------|--------|------|------------------------------------------------|

| 79  | P10.8             | O0 / I | St/B | Bit 8 of Port 10, General Purpose Input/Output |

|     | U0C0_<br>MCLKOUT  | 01     | St/B | USIC0 Channel 0 Master Clock Output            |

|     | U0C1_<br>SELO0    | O2     | St/B | USIC0 Channel 1 Select/Control 0 Output        |

|     | AD8               | OH/I   | St/B | External Bus Interface Address/Data Line 8     |

|     | CCU60_<br>CCPOS1A | I      | St/B | CCU60 Position Input 1                         |

|     | U0C0_DX1C         | I      | St/B | USIC0 Channel 0 Shift Clock Input              |

|     | BRKIN_B           | I      | St/B | OCDS Break Signal Input                        |

| 80  | P10.9             | O0 / I | St/B | Bit 9 of Port 10, General Purpose Input/Output |

|     | U0C0_<br>SELO4    | 01     | St/B | USIC0 Channel 0 Select/Control 4 Output        |

|     | U0C1_<br>MCLKOUT  | O2     | St/B | USIC0 Channel 1 Master Clock Output            |

|     | AD9               | OH/I   | St/B | External Bus Interface Address/Data Line 9     |

|     | CCU60_<br>CCPOS2A | I      | St/B | CCU60 Position Input 2                         |

|     | TCK_B             | I      | St/B | JTAG Clock Input                               |

| 81  | P1.1              | O0 / I | St/B | Bit 1 of Port 1, General Purpose Input/Output  |

|     | CCU62_<br>COUT62  | 01     | St/B | CCU62 Channel 2 Output                         |

|     | U1C0_<br>SELO5    | O2     | St/B | USIC1 Channel 0 Select/Control 5 Output        |

|     | U2C1_DOUT         | O3     | St/B | USIC2 Channel 1 Shift Data Output              |

|     | A9                | ОН     | St/B | External Bus Interface Address Line 9          |

|     | ESR2_3            | I      | St/B | ESR2 Trigger Input 3                           |

|     | EX1BINA           | I      | St/B | External Interrupt Trigger Input               |

|     | U2C1_DX0C         | I      | St/B | USIC2 Channel 1 Shift Data Input               |

# 3 Functional Description

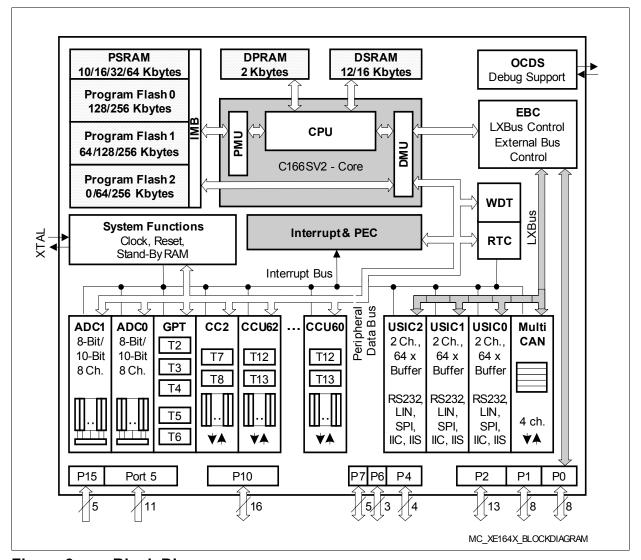

The architecture of the XE164 combines advantages of RISC, CISC, and DSP processors with an advanced peripheral subsystem in a well-balanced design. On-chip memory blocks allow the design of compact systems-on-silicon with maximum performance suited for computing, control, and communication.

The on-chip memory blocks (program code memory and SRAM, dual-port RAM, data SRAM) and the generic peripherals are connected to the CPU by separate high-speed buses. Another bus, the LXBus, connects additional on-chip resources and external resources (see Figure 3). This bus structure enhances overall system performance by enabling the concurrent operation of several subsystems of the XE164.

The block diagram gives an overview of the on-chip components and the advanced internal bus structure of the XE164.

Figure 3 Block Diagram

# XE164x XE166 Family Derivatives

# **Functional Description**

Table 6 XE164 Interrupt Nodes (cont'd)

| Source of Interrupt or PEC<br>Service Request | Control<br>Register | Vector<br>Location <sup>1)</sup> | Trap<br>Number                    |

|-----------------------------------------------|---------------------|----------------------------------|-----------------------------------|

| CAN Request 1                                 | CAN_1IC             | xx'0104 <sub>H</sub>             | 41 <sub>H</sub> / 65 <sub>D</sub> |

| CAN Request 2                                 | CAN_2IC             | xx'0108 <sub>H</sub>             | 42 <sub>H</sub> / 66 <sub>D</sub> |

| CAN Request 3                                 | CAN_3IC             | xx'010C <sub>H</sub>             | 43 <sub>H</sub> / 67 <sub>D</sub> |

| CAN Request 4                                 | CAN_4IC             | xx'0110 <sub>H</sub>             | 44 <sub>H</sub> / 68 <sub>D</sub> |

| CAN Request 5                                 | CAN_5IC             | xx'0114 <sub>H</sub>             | 45 <sub>H</sub> / 69 <sub>D</sub> |

| CAN Request 6                                 | CAN_6IC             | xx'0118 <sub>H</sub>             | 46 <sub>H</sub> / 70 <sub>D</sub> |

| CAN Request 7                                 | CAN_7IC             | xx'011C <sub>H</sub>             | 47 <sub>H</sub> / 71 <sub>D</sub> |

| CAN Request 8                                 | CAN_8IC             | xx'0120 <sub>H</sub>             | 48 <sub>H</sub> / 72 <sub>D</sub> |

| CAN Request 9                                 | CAN_9IC             | xx'0124 <sub>H</sub>             | 49 <sub>H</sub> / 73 <sub>D</sub> |

| CAN Request 10                                | CAN_10IC            | xx'0128 <sub>H</sub>             | 4A <sub>H</sub> / 74 <sub>D</sub> |

| CAN Request 11                                | CAN_11IC            | xx'012C <sub>H</sub>             | 4B <sub>H</sub> / 75 <sub>D</sub> |

| CAN Request 12                                | CAN_12IC            | xx'0130 <sub>H</sub>             | 4C <sub>H</sub> / 76 <sub>D</sub> |

| CAN Request 13                                | CAN_13IC            | xx'0134 <sub>H</sub>             | 4D <sub>H</sub> / 77 <sub>D</sub> |

| CAN Request 14                                | CAN_14IC            | xx'0138 <sub>H</sub>             | 4E <sub>H</sub> / 78 <sub>D</sub> |

| CAN Request 15                                | CAN_15IC            | xx'013C <sub>H</sub>             | 4F <sub>H</sub> / 79 <sub>D</sub> |

| USIC0 Cannel 0, Request 0                     | U0C0_0IC            | xx'0140 <sub>H</sub>             | 50 <sub>H</sub> / 80 <sub>D</sub> |

| USIC0 Cannel 0, Request 1                     | U0C0_1IC            | xx'0144 <sub>H</sub>             | 51 <sub>H</sub> / 81 <sub>D</sub> |

| USIC0 Cannel 0, Request 2                     | U0C0_2IC            | xx'0148 <sub>H</sub>             | 52 <sub>H</sub> / 82 <sub>D</sub> |

| USIC0 Cannel 1, Request 0                     | U0C1_0IC            | xx'014C <sub>H</sub>             | 53 <sub>H</sub> / 83 <sub>D</sub> |

| USIC0 Cannel 1, Request 1                     | U0C1_1IC            | xx'0150 <sub>H</sub>             | 54 <sub>H</sub> / 84 <sub>D</sub> |

| USIC0 Cannel 1, Request 2                     | U0C1_2IC            | xx'0154 <sub>H</sub>             | 55 <sub>H</sub> / 85 <sub>D</sub> |

| USIC1 Cannel 0, Request 0                     | U1C0_0IC            | xx'0158 <sub>H</sub>             | 56 <sub>H</sub> / 86 <sub>D</sub> |

| USIC1 Cannel 0, Request 1                     | U1C0_1IC            | xx'015C <sub>H</sub>             | 57 <sub>H</sub> / 87 <sub>D</sub> |

| USIC1 Cannel 0, Request 2                     | U1C0_2IC            | xx'0160 <sub>H</sub>             | 58 <sub>H</sub> / 88 <sub>D</sub> |

| USIC1 Cannel 1, Request 0                     | U1C1_0IC            | xx'0164 <sub>H</sub>             | 59 <sub>H</sub> / 89 <sub>D</sub> |

| USIC1 Cannel 1, Request 1                     | U1C1_1IC            | xx'0168 <sub>H</sub>             | 5A <sub>H</sub> / 90 <sub>D</sub> |

| USIC1 Cannel 1, Request 2                     | U1C1_2IC            | xx'016C <sub>H</sub>             | 5B <sub>H</sub> / 91 <sub>D</sub> |

| USIC2 Cannel 0, Request 0                     | U2C0_0IC            | xx'0170 <sub>H</sub>             | 5C <sub>H</sub> / 92 <sub>D</sub> |

| USIC2 Cannel 0, Request 1                     | U2C0_1IC            | xx'0174 <sub>H</sub>             | 5D <sub>H</sub> / 93 <sub>D</sub> |

| USIC2 Cannel 0, Request 2                     | U2C0_2IC            | xx'0178 <sub>H</sub>             | 5E <sub>H</sub> / 94 <sub>D</sub> |

# 3.8 General Purpose Timer (GPT12E) Unit

The GPT12E unit is a very flexible multifunctional timer/counter structure which can be used for many different timing tasks such as event timing and counting, pulse width and duty cycle measurements, pulse generation, or pulse multiplication.

The GPT12E unit incorporates five 16-bit timers organized in two separate modules, GPT1 and GPT2. Each timer in each module may either operate independently in a number of different modes or be concatenated with another timer of the same module.

Each of the three timers T2, T3, T4 of **module GPT1** can be configured individually for one of four basic modes of operation: Timer, Gated Timer, Counter, and Incremental Interface Mode. In Timer Mode, the input clock for a timer is derived from the system clock and divided by a programmable prescaler. Counter Mode allows timer clocking in reference to external events.

Pulse width or duty cycle measurement is supported in Gated Timer Mode, where the operation of a timer is controlled by the 'gate' level on an external input pin. For these purposes each timer has one associated port pin (TxIN<sup>1)</sup>) which serves as a gate or clock input. The maximum resolution of the timers in module GPT1 is 4 system clock cycles.

The counting direction (up/down) for each timer can be programmed by software or altered dynamically by an external signal on a port pin (TxEUD<sup>1)</sup>), e.g. to facilitate position tracking.

In Incremental Interface Mode the GPT1 timers<sup>1)</sup> can be directly connected to the incremental position sensor signals A and B through their respective inputs TxIN and TxEUD. Direction and counting signals are internally derived from these two input signals, so that the contents of the respective timer Tx corresponds to the sensor position. The third position sensor signal TOP0 can be connected to an interrupt input.

Timer T3 has an output toggle latch (T3OTL) which changes its state on each timer overflow/underflow. The state of this latch may be output on pin T3OUT e.g. for time out monitoring of external hardware components. It may also be used internally to clock timers T2 and T4 for measuring long time periods with high resolution.

In addition to the basic operating modes, T2 may be configured as reload or capture register for timer T3. A timer used as capture or reload register is stopped. The contents of timer T3 is captured into T2 in response to a signal at the associated input pin (TxIN). Timer T3 is reloaded with the contents of T2, triggered either by an external signal or a selectable state transition of its toggle latch T3OTL.

Data Sheet 50 V2.1, 2008-08

<sup>1)</sup> Exception: Timer T4 is not connected to pins.

#### 3.10 A/D Converters

For analog signal measurement, up to two 10-bit A/D converters (ADC0, ADC1) with 11 + 5 multiplexed input channels and a sample and hold circuit have been integrated on-chip. They use the successive approximation method. The sample time (to charge the capacitors) and the conversion time are programmable so that they can be adjusted to the external circuit. The A/D converters can also operate in 8-bit conversion mode, further reducing the conversion time.

Several independent conversion result registers, selectable interrupt requests, and highly flexible conversion sequences provide a high degree of programmability to meet the application requirements. Both modules can be synchronized to allow parallel sampling of two input channels.

For applications that require more analog input channels, external analog multiplexers can be controlled automatically.

For applications that require fewer analog input channels, the remaining channel inputs can be used as digital input port pins.

The A/D converters of the XE164 support two types of request sources which can be triggered by several internal and external events.

- Parallel requests are activated at the same time and then executed in a predefined sequence.

- Queued requests are executed in a user-defined sequence.

In addition, the conversion of a specific channel can be inserted into a running sequence without disturbing that sequence. All requests are arbitrated according to the priority level assigned to them.

Data reduction features, such as limit checking or result accumulation, reduce the number of required CPU access operations allowing the precise evaluation of analoginputs (high conversion rate) even at a low CPU speed.

The Peripheral Event Controller (PEC) can be used to control the A/D converters or to automatically store conversion results to a table in memory for later evaluation, without requiring the overhead of entering and exiting interrupt routines for each data transfer. Each A/D converter contains eight result registers which can be concatenated to build a result FIFO. Wait-for-read mode can be enabled for each result register to prevent the loss of conversion data.

In order to decouple analog inputs from digital noise and to avoid input trigger noise, those pins used for analog input can be disconnected from the digital input stages under software control. This can be selected for each pin separately with registers P5\_DIDIS and P15\_DIDIS (Port x Digital Input Disable).

The Auto-Power-Down feature of the A/D converters minimizes the power consumption when no conversion is in progress.

Data Sheet 56 V2.1, 2008-08

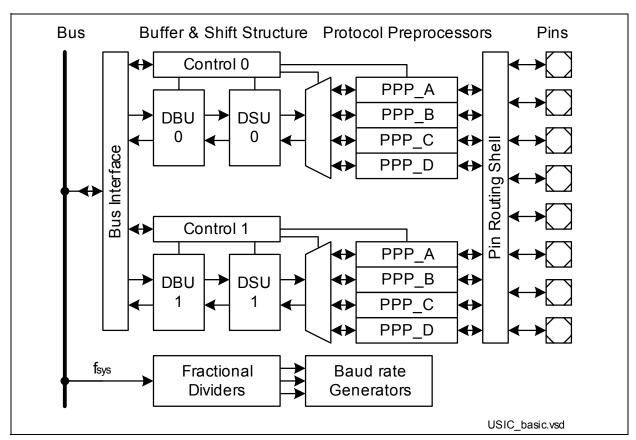

# 3.11 Universal Serial Interface Channel Modules (USIC)

The XE164 includes up to three USIC modules (USIC0, USIC1, USIC2), each providing two serial communication channels.

The Universal Serial Interface Channel (USIC) module is based on a generic data shift and data storage structure which is identical for all supported serial communication protocols. Each channel supports complete full-duplex operation with a basic data buffer structure (one transmit buffer and two receive buffer stages). In addition, the data handling software can use FIFOs.

The protocol part (generation of shift clock/data/control signals) is independent of the general part and is handled by protocol-specific preprocessors (PPPs).

The USIC's input/output lines are connected to pins by a pin routing unit. The inputs and outputs of each USIC channel can be assigned to different interface pins, providing great flexibility to the application software. All assignments can be made during runtime.

Figure 10 General Structure of a USIC Module

The regular structure of the USIC module brings the following advantages:

- Higher flexibility through configuration with same look-and-feel for data management

- Reduced complexity for low-level drivers serving different protocols

- Wide range of protocols with improved performances (baud rate, buffer handling)

Data Sheet 57 V2.1, 2008-08

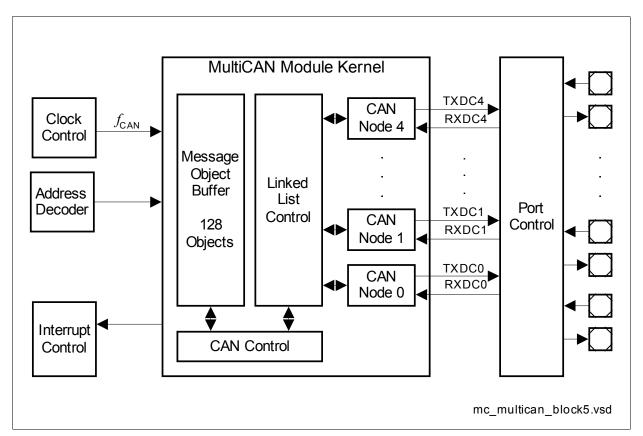

#### 3.12 MultiCAN Module

The MultiCAN module contains up to four independently operating CAN nodes with Full-CAN functionality which are able to exchange Data and Remote Frames using a gateway function. Transmission and reception of CAN frames is handled in accordance with CAN specification V2.0 B (active). Each CAN node can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers.

All CAN nodes share a common set of 128 message objects. Each message object can be individually allocated to one of the CAN nodes. Besides serving as a storage container for incoming and outgoing frames, message objects can be combined to build gateways between the CAN nodes or to set up a FIFO buffer.

The message objects are organized in double-chained linked lists, where each CAN node has its own list of message objects. A CAN node stores frames only into message objects that are allocated to its own message object list and it transmits only messages belonging to this message object list. A powerful, command-driven list controller performs all message object list operations.

Figure 11 Block Diagram of MultiCAN Module

Data Sheet 59 V2.1, 2008-08

# XE164x XE166 Family Derivatives

# **Functional Description**

#### **MultiCAN Features**

- CAN functionality conforming to CAN specification V2.0 B active for each CAN node (compliant to ISO 11898)

- Up to four independent CAN nodes

- 128 independent message objects (shared by the CAN nodes)

- Dedicated control registers for each CAN node

- Data transfer rate up to 1 Mbit/s, individually programmable for each node

- Flexible and powerful message transfer control and error handling capabilities

- Full-CAN functionality for message objects:

- Can be assigned to one of the CAN nodes

- Configurable as transmit or receive objects, or as message buffer FIFO

- Handle 11-bit or 29-bit identifiers with programmable acceptance mask for filtering

- Remote Monitoring Mode, and frame counter for monitoring

- Automatic Gateway Mode support

- 16 individually programmable interrupt nodes

- Analyzer mode for CAN bus monitoring

# 3.13 Watchdog Timer

The Watchdog Timer is one of the fail-safe mechanisms which have been implemented to prevent the controller from malfunctioning for longer periods of time.

The Watchdog Timer is always enabled after an application reset of the chip. It can be disabled and enabled at any time by executing the instructions DISWDT and ENWDT respectively. The software has to service the Watchdog Timer before it overflows. If this is not the case because of a hardware or software failure, the Watchdog Timer overflows, generating a prewarning interrupt and then a reset request.

The Watchdog Timer is a 16-bit timer clocked with the system clock divided by 16,384 or 256. The Watchdog Timer register is set to a prespecified reload value (stored in WDTREL) in order to allow further variation of the monitored time interval. Each time it is serviced by the application software, the Watchdog Timer is reloaded and the prescaler is cleared.

Time intervals between 3.2  $\mu$ s and 13.4 s can be monitored (@ 80 MHz). The default Watchdog Timer interval after power-up is 6.5 ms (@ 10 MHz).

#### 3.14 Clock Generation

The Clock Generation Unit can generate the system clock signal  $f_{SYS}$  for the XE164 from a number of external or internal clock sources:

- External clock signals with pad or core voltage levels

- External crystal using the on-chip oscillator

- On-chip clock source for operation without crystal

- Wake-up clock (ultra-low-power) to further reduce power consumption

The programmable on-chip PLL with multiple prescalers generates a clock signal for maximum system performance from standard crystals or from the on-chip clock source. See also **Section 4.6.2**.

The Oscillator Watchdog (OWD) generates an interrupt if the crystal oscillator frequency falls below a certain limit or stops completely. In this case, the system can be supplied with an emergency clock to enable operation even after an external clock failure.

All available clock signals can be output on one of two selectable pins.

Data Sheet 61 V2.1, 2008-08

#### 4.2 DC Parameters

These parameters are static or average values that may be exceeded during switching transitions (e.g. output current).

The XE164 can operate within a wide supply voltage range from 3.0 V to 5.5 V. However, during operation this supply voltage must remain within 10 percent of the selected nominal supply voltage. It cannot vary across the full operating voltage range.

Because of the supply voltage restriction and because electrical behavior depends on the supply voltage, the parameters are specified separately for the upper and the lower voltage range.

During operation, the supply voltages may only change with a maximum speed of dV/dt < 1 V/ms.

Leakage current is strongly dependent on the operating temperature and the voltage level at the respective pin. The maximum values in the following tables apply under worst case conditions, i.e. maximum temperature and an input level equal to the supply voltage.

The value for the leakage current in an application can be determined by using the respective leakage derating formula (see tables) with values from that application.

The pads of the XE164 are designed to operate in various driver modes. The DC parameter specifications refer to the current limits in **Table 13**.

Table 13 Current Limits for Port Output Drivers

| Port Output Driver<br>Mode | Maximum Out (I <sub>OLmax</sub> , -I <sub>OHmax</sub> | •                   | Nominal Output Current $(I_{OLnom}, -I_{OHnom})$ |                     |  |

|----------------------------|-------------------------------------------------------|---------------------|--------------------------------------------------|---------------------|--|

|                            | $V_{DDP} \geq$ 4.5 V                                  | $V_{DDP}$ $<$ 4.5 V | $V_{DDP} \geq$ 4.5 V                             | $V_{DDP}$ $<$ 4.5 V |  |

| Strong driver              | 10 mA                                                 | 10 mA               | 2.5 mA                                           | 2.5 mA              |  |

| Medium driver              | 4.0 mA                                                | 2.5 mA              | 1.0 mA                                           | 1.0 mA              |  |

| Weak driver                | 0.5 mA                                                | 0.5 mA              | 0.1 mA                                           | 0.1 mA              |  |

<sup>1)</sup> An output current above  $|I_{\rm OXnom}|$  may be drawn from up to three pins at the same time. For any group of 16 neighboring output pins, the total output current in each direction ( $\Sigma I_{\rm OL}$  and  $\Sigma$ - $I_{\rm OH}$ ) must remain below 50 mA.

Data Sheet 71 V2.1, 2008-08

# 4.2.3 Power Consumption

The power consumed by the XE164 depends on several factors such as supply voltage, operating frequency, active circuits, and operating temperature. The power consumption specified here consists of two components:

- The switching current  $I_{\rm S}$  depends on the device activity

- The leakage current  $I_{1K}$  depends on the device temperature

To determine the actual power consumption, always both components, switching current  $I_{\rm S}$  (Table 16) and leakage current  $I_{\rm LK}$  (Table 17) must be added:

$$I_{\text{DDP}} = I_{\text{S}} + I_{\text{LK}}.$$

Note: The power consumption values are not subject to production test. They are verified by design/characterization.

To determine the total power consumption for dimensioning the external power supply, also the pad driver currents must be considered.

The given power consumption parameters and their values refer to specific operating conditions:

#### Active mode:

Regular operation, i.e. peripherals are active, code execution out of Flash.

# Stopover mode:

Crystal oscillator and PLL stopped, Flash switched off, clock in domain DMP\_1 stopped.

Note: The maximum values cover the complete specified operating range of all manufactured devices.

The typical values refer to average devices under typical conditions, such as nominal supply voltage, room temperature, application-oriented activity.

After a power reset, the decoupling capacitors for  $V_{\rm DDI}$  are charged with the maximum possible current, see parameter  $I_{\rm CC}$  in **Table 20**.

For additional information, please refer to Section 5.2, Thermal Considerations.

Data Sheet 77 V2.1, 2008-08

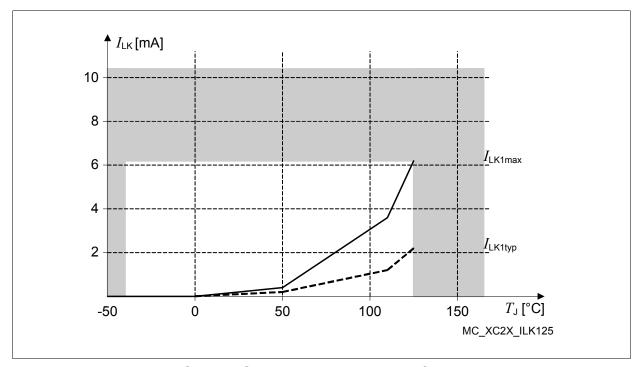

Table 17 Leakage Power Consumption XE164 (Operating Conditions apply)

| Parameter                                                            | Sym-      | Values |      |      | Unit |                              |

|----------------------------------------------------------------------|-----------|--------|------|------|------|------------------------------|

|                                                                      | bol       | Min.   | Тур. | Max. |      | Test Condition <sup>1)</sup> |

| Leakage supply current <sup>2)</sup>                                 | $I_{LK1}$ | _      | 0.03 | 0.05 | mA   | T <sub>J</sub> = 25°C        |

| Formula <sup>3)</sup> : $600,000 \times e^{-\alpha}$ ;               |           | _      | 0.5  | 1.3  | mA   | $T_{\rm J}$ = 85°C           |

| $\alpha$ = 5000 / (273 + B× $T_J$ );<br>Typ.: B = 1.0, Max.: B = 1.3 |           | _      | 2.1  | 6.2  | mA   | T <sub>J</sub> = 125°C       |

- 1) All inputs (including pins configured as inputs) are set at 0 V to 0.1 V or at  $V_{\rm DDP}$  0.1 V to  $V_{\rm DDP}$  and all outputs (including pins configured as outputs) are disconnected.

- 2) The supply current caused by leakage depends mainly on the junction temperature (see Figure 14) and the supply voltage. The temperature difference between the junction temperature  $T_J$  and the ambient temperature  $T_A$  must be taken into account. As this fraction of the supply current does not depend on device activity, it must be added to other power consumption values.

- 3) This formula is valid for temperatures above 0°C. For temperatures below 0°C a value of below 10  $\mu$ A can be assumed.

Figure 14 Leakage Supply Current as a Function of Temperature

Data Sheet 80 V2.1, 2008-08

Table 24 Flash Access Waitstates

| Required Waitstates                | System Frequency Range           |  |  |

|------------------------------------|----------------------------------|--|--|

| 4 WS (WSFLASH = 100 <sub>B</sub> ) | $f_{SYS} \leq f_{SYSmax}$        |  |  |

| 3 WS (WSFLASH = 011 <sub>B</sub> ) | $f_{SYS} \leq$ 17 MHz            |  |  |

| 2 WS (WSFLASH = 010 <sub>B</sub> ) | $f_{SYS} \leq$ 13 MHz            |  |  |

| 1 WS (WSFLASH = 001 <sub>B</sub> ) | $f_{SYS} \leq 8 \; MHz$          |  |  |

| 0 WS (WSFLASH = 000 <sub>B</sub> ) | Forbidden! Must not be selected! |  |  |

Note: The maximum achievable system frequency is limited by the properties of the respective derivative.

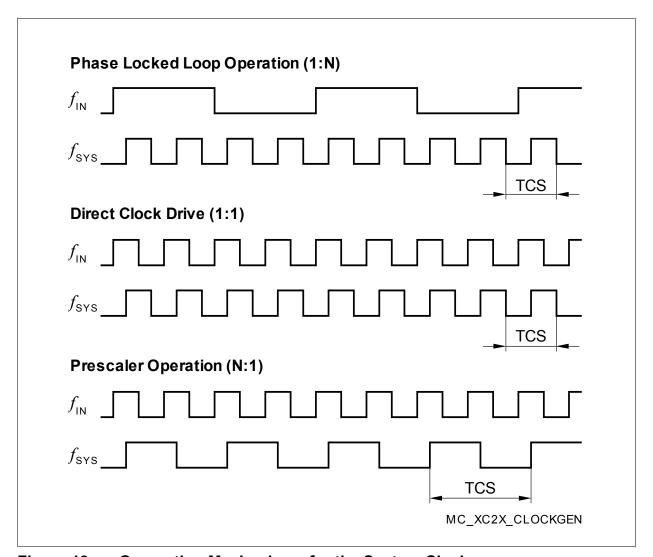

# 4.6.2 Definition of Internal Timing

The internal operation of the XE164 is controlled by the internal system clock  $f_{SYS}$ .

Because the system clock signal  $f_{\rm SYS}$  can be generated from a number of internal and external sources using different mechanisms, the duration of the system clock periods (TCSs) and their variation (as well as the derived external timing) depend on the mechanism used to generate  $f_{\rm SYS}$ . This must be considered when calculating the timing for the XE164.

Figure 18 Generation Mechanisms for the System Clock

Note: The example of PLL operation shown in **Figure 18** uses a PLL factor of 1:4; the example of prescaler operation uses a divider factor of 2:1.

The specification of the external timing (AC Characteristics) depends on the period of the system clock (TCS).

The timing in the AC Characteristics refers to TCSs. Timing must be calculated using the minimum TCS possible under the given circumstances.

The actual minimum value for TCS depends on the jitter of the PLL. Because the PLL is constantly adjusting its output frequency to correspond to the input frequency (from crystal or oscillator), the accumulated jitter is limited. This means that the relative deviation for periods of more than one TCS is lower than for a single TCS (see formulas and Figure 19).

This is especially important for bus cycles using waitstates and for the operation of timers, serial interfaces, etc. For all slower operations and longer periods (e.g. pulse train generation or measurement, lower baudrates, etc.) the deviation caused by the PLL jitter is negligible.

The value of the accumulated PLL jitter depends on the number of consecutive VCO output cycles within the respective timeframe. The VCO output clock is divided by the output prescaler K2 to generate the system clock signal  $f_{\rm SYS}$ . The number of VCO cycles is K2 × **T**, where **T** is the number of consecutive  $f_{\rm SYS}$  cycles (TCS).

The maximum accumulated jitter (long-term jitter) D<sub>Tmax</sub> is defined by:

$$D_{Tmax}$$

[ns] = ±(220 / (K2 ×  $f_{SYS}$ ) + 4.3)

This maximum value is applicable, if either the number of clock cycles T > ( $f_{SYS}$  / 1.2) or the prescaler value K2 > 17.

In all other cases for a timeframe of  $\mathbf{T} \times TCS$  the accumulated jitter  $D_T$  is determined by:

$$\mathbf{D_T}$$

[ns] =  $D_{Tmax} \times [(1 - 0.058 \times K2) \times (T - 1) / (0.83 \times f_{SYS} - 1) + 0.058 \times K2]$

$f_{\rm SYS}$  in [MHz] in all formulas.

Example, for a period of 3 TCSs @ 33 MHz and K2 = 4:

$D_{max}$  = ±(220 / (4 × 33) + 4.3) = 5.97 ns (Not applicable directly in this case!)

$$D_3$$

= 5.97 × [(1 - 0.058 × 4) × (3 - 1) / (0.83 × 33 - 1) + 0.058 × 4] = 5.97 × [0.768 × 2 / 26.39 + 0.232] = 1.7 ns

Example, for a period of 3 TCSs @ 33 MHz and K2 = 2:

$D_{max}$  = ±(220 / (2 × 33) + 4.3) = 7.63 ns (Not applicable directly in this case!)

$$D_3 = 7.63 \times [(1 - 0.058 \times 2) \times (3 - 1) / (0.83 \times 33 - 1) + 0.058 \times 2] = 7.63 \times [0.884 \times 2 / 26.39 + 0.116]$$

= 1.4 ns

Data Sheet 91 V2.1, 2008-08

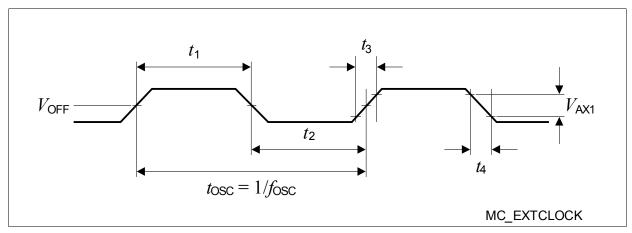

Figure 20 External Clock Drive XTAL1

Note: For crystal/resonator operation, it is strongly recommended to measure the oscillation allowance (negative resistance) in the final target system (layout) to determine the optimum parameters for oscillator operation.

Please refer to the limits specified by the crystal/resonator supplier.

Data Sheet 95 V2.1, 2008-08

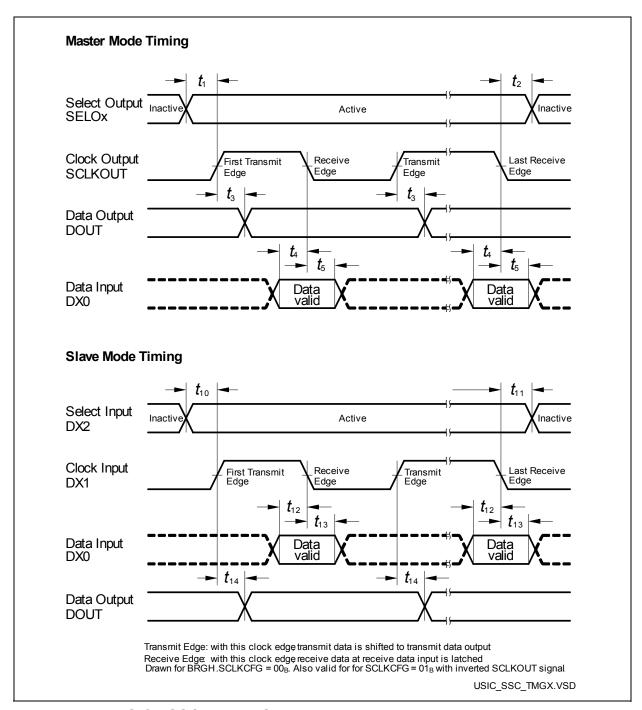

Figure 25 USIC - SSC Master/Slave Mode Timing

Note: This timing diagram shows a standard configuration where the slave select signal is low-active and the serial clock signal is not shifted and not inverted.

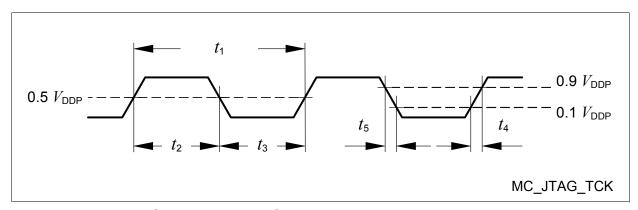

Figure 26 Test Clock Timing (TCK)

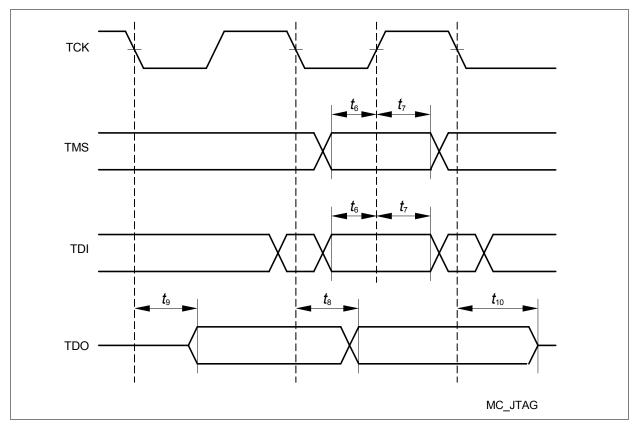

Figure 27 JTAG Timing

Data Sheet 108 V2.1, 2008-08

www.infineon.com

Published by Infineon Technologies AG