Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Not For New Designs                                                             |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | C166SV2                                                                         |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 66MHz                                                                           |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI            |

| Peripherals                | I <sup>2</sup> S, POR, PWM, WDT                                                 |

| Number of I/O              | 75                                                                              |

| Program Memory Size        | 768KB (768K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 82K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                       |

| Data Converters            | A/D 11x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-LQFP Exposed Pad                                                            |

| Supplier Device Package    | PG-LQFP-100-3                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xe164g96f66lacfxqma1 |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Edition 2008-08 Published by Infineon Technologies AG 81726 Munich, Germany © 2008 Infineon Technologies AG All Rights Reserved.

#### Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

## **1** Summary of Features

For a quick overview and easy reference, the features of the XE164 are summarized here.

- High-performance CPU with five-stage pipeline

- 12.5 ns instruction cycle at 80 MHz CPU clock (single-cycle execution)

- One-cycle 32-bit addition and subtraction with 40-bit result

- One-cycle multiplication ( $16 \times 16$  bit)

- Background division (32 / 16 bit) in 21 cycles

- One-cycle multiply-and-accumulate (MAC) instructions

- Enhanced Boolean bit manipulation facilities

- Zero-cycle jump execution

- Additional instructions to support HLL and operating systems

- Register-based design with multiple variable register banks

- Fast context switching support with two additional local register banks

- 16 Mbytes total linear address space for code and data

- 1024 Bytes on-chip special function register area (C166 Family compatible)

- Interrupt system with 16 priority levels for up to 83 sources

- Selectable external inputs for interrupt generation and wake-up

- Fastest sample-rate 12.5 ns

- Eight-channel interrupt-driven single-cycle data transfer with Peripheral Event Controller (PEC), 24-bit pointers cover total address space

- Clock generation from internal or external clock sources, using on-chip PLL or prescaler

- On-chip memory modules

- 1 Kbyte on-chip stand-by RAM (SBRAM)

- 2 Kbytes on-chip dual-port RAM (DPRAM)

- Up to 16 Kbytes on-chip data SRAM (DSRAM)

- Up to 64 Kbytes on-chip program/data SRAM (PSRAM)

- Up to 768 Kbytes on-chip program memory (Flash memory)

- On-Chip Peripheral Modules

- Two Synchronizable A/D Converters with up to 16 channels, 10-bit resolution, conversion time below 1  $\mu$ s, optional data preprocessing (data reduction, range check)

- 16-channel general purpose capture/compare unit (CAPCOM2)

- Up to three capture/compare units for flexible PWM signal generation (CCU6x)

- Multi-functional general purpose timer unit with 5 timers

٠

#### **Summary of Features**

- Up to 6 serial interface channels to be used as UART, LIN, high-speed synchronous channel (SPI/QSPI), IIC bus interface (10-bit addressing, 400 kbit/s), IIS interface

- On-chip MultiCAN interface (Rev. 2.0B active) with up to 128 message objects (Full CAN/Basic CAN) on up to 4 CAN nodes and gateway functionality

On-chip real time clock

- Up to 12 Mbytes external address space for code and data

- Programmable external bus characteristics for different address ranges

- Multiplexed or demultiplexed external address/data buses

- Selectable address bus width

- 16-bit or 8-bit data bus width

- Four programmable chip-select signals

- Single power supply from 3.0 V to 5.5 V

- Programmable watchdog timer and oscillator watchdog

- Up to 75 general purpose I/O lines

- On-chip bootstrap loaders

- Supported by a full range of development tools including C compilers, macroassembler packages, emulators, evaluation boards, HLL debuggers, simulators, logic analyzer disassemblers, programming boards

- On-chip debug support via JTAG interface

- 100-pin Green LQFP package, 0.5 mm (19.7 mil) pitch

#### **Ordering Information**

The ordering code for an Infineon microcontroller provides an exact reference to a specific product. This ordering code identifies:

- the derivative itself, i.e. its function set, the temperature range, and the supply voltage

- the package and the type of delivery.

For ordering codes for the XE164 please contact your sales representative or local distributor.

This document describes several derivatives of the XE164 group. **Table 1** lists these derivatives and summarizes the differences. As this document refers to all of these derivatives, some descriptions may not apply to a specific product.

For simplicity the term **XE164** is used for all derivatives throughout this document.

#### Summary of Features

The XE164 types are offered with several Flash memory sizes. **Table 2** describes the location of the available memory areas for each Flash memory size.

| Total Flash Size | Flash Area A <sup>1)</sup>                   | Flash Area B                                 | Flash Area C                                 |  |  |

|------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|--|--|

| 768 Kbytes       | C0'0000 <sub>H</sub><br>C0'EFFF <sub>H</sub> | C1'0000 <sub>H</sub><br>CB'FFFF <sub>H</sub> | n.a.                                         |  |  |

| 576 Kbytes       | C0'0000 <sub>H</sub><br>C0'EFFF <sub>H</sub> | C1'0000 <sub>H</sub><br>C8'FFFF <sub>H</sub> | n.a.                                         |  |  |

| 384 Kbytes       | C0'0000 <sub>H</sub><br>C0'EFFF <sub>H</sub> | C1'0000 <sub>H</sub><br>C5'FFFF <sub>H</sub> | n.a.                                         |  |  |

| 192 Kbytes       | C0'0000 <sub>H</sub><br>C0'EFFF <sub>H</sub> | C1'0000 <sub>H</sub><br>C1'FFFF <sub>H</sub> | C4'0000 <sub>H</sub><br>C4'FFFF <sub>H</sub> |  |  |

Table 2Flash Memory Allocation

1) The uppermost 4-Kbyte sector of the first Flash segment is reserved for internal use  $(C0'F000_{H} \text{ to } C0'FFF_{H})$ .

The XE164 types are offered with different interface options. **Table 3** lists the available channels for each option.

| Table 3 | Interface Channel Association |

|---------|-------------------------------|

|---------|-------------------------------|

| Total Number      | Available Channels                 |

|-------------------|------------------------------------|

| 11 ADC0 channels  | CH0, CH2 CH5, CH8 CH11, CH13, CH15 |

| 6 ADC0 channels   | CH0, CH2, CH3, CH4, CH5, CH8       |

| 5 ADC1 channels   | CH0, CH2, CH4, CH5, CH6            |

| 4 CAN nodes       | CAN0, CAN1, CAN2, CAN3             |

| 2 CAN nodes       | CAN0, CAN1                         |

| 6 serial channels | U0C0, U0C1, U1C0, U1C1, U2C0, U2C1 |

| 4 serial channels | U0C0, U0C1, U1C0, U1C1             |

#### **Notes to Pin Definitions**

Ctrl.: The output signal for a port pin is selected by bitfield PC in the associated register Px\_IOCRy. Output O0 is selected by setting the respective bitfield PC to 1x00<sub>B</sub>, output O1 is selected by 1x01<sub>B</sub>, etc. Output signal OH is controlled by hardware.

2. **Type**: Indicates the pad type used (St=standard pad, Sp=special pad, DP=double pad, In=input pad, PS=power supply) and its power supply domain (A, B, M, 1).

| Pin | Symbol            | Ctrl.  | Туре | Function                                                                                                                                                                                                                                                                                                                                                        |

|-----|-------------------|--------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3   | TESTM             | 1      | In/B | Testmode EnableEnables factory test modes, must be held HIGH fornormal operation (connect to $V_{\text{DDPB}}$ ).An internal pullup device will hold this pin highwhen nothing is driving it.                                                                                                                                                                   |

| 4   | P7.2              | O0 / I | St/B | Bit 2 of Port 7, General Purpose Input/Output                                                                                                                                                                                                                                                                                                                   |

|     | EMUX0             | 01     | St/B | External Analog MUX Control Output 0 (ADC1)                                                                                                                                                                                                                                                                                                                     |

|     | CCU62_<br>CCPOS0A | I      | St/B | CCU62 Position Input 0                                                                                                                                                                                                                                                                                                                                          |

|     | TDI_C             | 1      | St/B | JTAG Test Data Input                                                                                                                                                                                                                                                                                                                                            |

| 5   | TRST              | 1      | In/B | <b>Test-System Reset Input</b><br>For normal system operation, pin TRST should be<br>held low. A high level at this pin at the rising edge<br>of PORST activates the XE164's debug system. In<br>this case, pin TRST must be driven low once to<br>reset the debug system.<br>An internal pulldown device will hold this pin low<br>when nothing is driving it. |

| 6   | P7.0              | O0 / I | St/B | Bit 0 of Port 7, General Purpose Input/Output                                                                                                                                                                                                                                                                                                                   |

|     | T3OUT             | 01     | St/B | GPT1 Timer T3 Toggle Latch Output                                                                                                                                                                                                                                                                                                                               |

|     | T6OUT             | O2     | St/B | GPT2 Timer T6 Toggle Latch Output                                                                                                                                                                                                                                                                                                                               |

|     | TDO_A             | OH     | St/B | JTAG Test Data Output                                                                                                                                                                                                                                                                                                                                           |

|     | ESR2_1            | I      | St/B | ESR2 Trigger Input 1                                                                                                                                                                                                                                                                                                                                            |

#### Table 4Pin Definitions and Functions

| Table 4Pin Definitions and Functions (cont'd) |                  |        |      |                                               |  |  |

|-----------------------------------------------|------------------|--------|------|-----------------------------------------------|--|--|

| Pin                                           | Symbol           | Ctrl.  | Туре | Function                                      |  |  |

| 43                                            | P2.3             | O0 / I | St/B | Bit 3 of Port 2, General Purpose Input/Output |  |  |

|                                               | U0C0_DOUT        | 01     | St/B | USIC0 Channel 0 Shift Data Output             |  |  |

|                                               | CC2_16           | O3 / I | St/B | CAPCOM2 CC16IO Capture Inp./ Compare Out.     |  |  |

|                                               | A16              | OH     | St/B | External Bus Interface Address Line 16        |  |  |

|                                               | ESR2_0           | I      | St/B | ESR2 Trigger Input 0                          |  |  |

|                                               | U0C0_DX0E        | I      | St/B | USIC0 Channel 0 Shift Data Input              |  |  |

|                                               | U0C1_DX0D        | I      | St/B | USIC0 Channel 1 Shift Data Input              |  |  |

|                                               | RxDC0A           | I      | St/B | CAN Node 0 Receive Data Input                 |  |  |

| 44                                            | P4.1             | O0 / I | St/B | Bit 1 of Port 4, General Purpose Input/Output |  |  |

|                                               | TxDC2            | 02     | St/B | CAN Node 2 Transmit Data Output               |  |  |

|                                               | CC2_25           | O3 / I | St/B | CAPCOM2 CC25IO Capture Inp./ Compare Out.     |  |  |

|                                               | CS1              | ОН     | St/B | External Bus Interface Chip Select 1 Output   |  |  |

| 45                                            | P2.4             | O0 / I | St/B | Bit 4 of Port 2, General Purpose Input/Output |  |  |

|                                               | U0C1_DOUT        | 01     | St/B | USIC0 Channel 1 Shift Data Output             |  |  |

|                                               | TxDC0            | 02     | St/B | CAN Node 0 Transmit Data Output               |  |  |

|                                               | CC2_17           | O3 / I | St/B | CAPCOM2 CC17IO Capture Inp./ Compare Out.     |  |  |

|                                               | A17              | ОН     | St/B | External Bus Interface Address Line 17        |  |  |

|                                               | ESR1_0           | I      | St/B | ESR1 Trigger Input 0                          |  |  |

|                                               | U0C0_DX0F        | I      | St/B | USIC0 Channel 0 Shift Data Input              |  |  |

|                                               | RxDC1A           | I      | St/B | CAN Node 1 Receive Data Input                 |  |  |

| 46                                            | P2.5             | O0 / I | St/B | Bit 5 of Port 2, General Purpose Input/Output |  |  |

|                                               | U0C0_<br>SCLKOUT | 01     | St/B | USIC0 Channel 0 Shift Clock Output            |  |  |

|                                               | TxDC0            | 02     | St/B | CAN Node 0 Transmit Data Output               |  |  |

|                                               | CC2_18           | O3 / I | St/B | CAPCOM2 CC18IO Capture Inp./ Compare Out.     |  |  |

|                                               | A18              | OH     | St/B | External Bus Interface Address Line 18        |  |  |

|                                               | U0C0_DX1D        | I      | St/B | USIC0 Channel 0 Shift Clock Input             |  |  |

| Table            | Table 4Pin Definitions and Functions (cont'd) |        |      |                                                                                                                                                                                                                                                                                    |  |  |

|------------------|-----------------------------------------------|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin              | Symbol                                        | Ctrl.  | Туре | Function                                                                                                                                                                                                                                                                           |  |  |

| 98               | ESR1                                          | O0 / I | St/B | External Service Request 1                                                                                                                                                                                                                                                         |  |  |

|                  | U1C0_DX0F                                     | I      | St/B | USIC1 Channel 0 Shift Data Input                                                                                                                                                                                                                                                   |  |  |

|                  | U1C0_DX2C                                     | I      | St/B | USIC1 Channel 0 Shift Control Input                                                                                                                                                                                                                                                |  |  |

|                  | U1C1_DX0C                                     | I      | St/B | USIC1 Channel 1 Shift Data Input                                                                                                                                                                                                                                                   |  |  |

|                  | U1C1_DX2B                                     | 1      | St/B | USIC1 Channel 1 Shift Control Input                                                                                                                                                                                                                                                |  |  |

|                  | U2C1_DX2C                                     | I      | St/B | USIC2 Channel 1 Shift Control Input                                                                                                                                                                                                                                                |  |  |

|                  | EX0AINB                                       | I      | St/B | External Interrupt Trigger Input                                                                                                                                                                                                                                                   |  |  |

| 99               | ESR0                                          | O0 / I | St/B | External Service Request 0                                                                                                                                                                                                                                                         |  |  |

|                  |                                               |        |      | Note: After power-up, ESR0 operates as open-<br>drain bidirectional reset with a weak pull-up.                                                                                                                                                                                     |  |  |

|                  | U1C0_DX0E                                     | I      | St/B | USIC1 Channel 0 Shift Data Input                                                                                                                                                                                                                                                   |  |  |

|                  | U1C0_DX2B                                     | I      | St/B | USIC1 Channel 0 Shift Control Input                                                                                                                                                                                                                                                |  |  |

| 10               | V <sub>DDIM</sub>                             | -      | PS/M | <b>Digital Core Supply Voltage for Domain M</b><br>Decouple with a ceramic capacitor, see <b>Table 12</b><br>for details.                                                                                                                                                          |  |  |

| 38,<br>64,<br>88 | V <sub>DDI1</sub>                             | -      | PS/1 | <b>Digital Core Supply Voltage for Domain 1</b><br>Decouple with a ceramic capacitor, see <b>Table 12</b><br>for details.<br>All $V_{DDI1}$ pins must be connected to each other.                                                                                                  |  |  |

| 14               | V <sub>DDPA</sub>                             | -      | PS/A | <b>Digital Pad Supply Voltage for Domain A</b><br>Connect decoupling capacitors to adjacent<br>$V_{\text{DDP}}/V_{\text{SS}}$ pin pairs as close as possible to the pins.<br>Note: The A/D_Converters and ports P5, P6, and<br>P15 are fed from supply voltage $V_{\text{DDPA}}$ . |  |  |

| Pin                                                 | Symbol            | Ctrl. | Туре | Function                                                                                                                                                                                                                                                                                                     |

|-----------------------------------------------------|-------------------|-------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2,<br>25,<br>27,<br>50,<br>52,<br>75,<br>77,<br>100 | V <sub>DDPB</sub> | -     | PS/B | <b>Digital Pad Supply Voltage for Domain B</b><br>Connect decoupling capacitors to adjacent<br>$V_{\text{DDP}}/V_{\text{SS}}$ pin pairs as close as possible to the pins.<br>Note: The on-chip voltage regulators and all ports<br>except P5, P6, and P15 are fed from supply<br>voltage $V_{\text{DDPB}}$ . |

| 1,<br>26,<br>51,<br>76                              | V <sub>SS</sub>   | -     | PS/  | <b>Digital Ground</b><br>All $V_{SS}$ pins must be connected to the ground-line<br>or ground-plane.<br>Note: Also the exposed pad is connected to $V_{SS}$ .<br>The respective board area must be<br>connected to ground (if soldered) or left free.                                                         |

#### Table 4Pin Definitions and Functions (cont'd)

1) To generate the reference clock output for bus timing measurement,  $f_{SYS}$  must be selected as source for EXTCLK and P2.8 must be selected as output pin. Also the high-speed clock pad must be enabled. This configuration is referred to as reference clock output signal CLKOUT.

2) Pin TRef was used to control the core voltage generation in step AA. For that step, pin TRef must be connected to V<sub>DDPB</sub>.

This connection is no more required from step AB on. For the current step, pin TRef is logically not connected. Future derivatives will feature an additional general purpose IO pin at this position.

### 3.6 Capture/Compare Unit (CAPCOM2)

The CAPCOM2 unit supports generation and control of timing sequences on up to 16 channels with a maximum resolution of one system clock cycle (eight cycles in staggered mode). The CAPCOM2 unit is typically used to handle high-speed I/O tasks such as pulse and waveform generation, pulse width modulation (PWM), digital to analog (D/A) conversion, software timing, or time recording with respect to external events.

Two 16-bit timers (T7/T8) with reload registers provide two independent time bases for the capture/compare register array.

The input clock for the timers is programmable to a number of prescaled values of the internal system clock. It may also be derived from an overflow/underflow of timer T6 in module GPT2. This provides a wide range for the timer period and resolution while allowing precise adjustments for application-specific requirements. An external count input for CAPCOM2 timer T7 allows event scheduling for the capture/compare registers with respect to external events.

The capture/compare register array contains 16 dual purpose capture/compare registers. Each may be individually allocated to either CAPCOM2 timer T7 or T8 and programmed for a capture or compare function.

12 registers of the CAPCOM2 module have one port pin associated with it. This serves as an input pin to trigger the capture function or as an output pin to indicate the occurrence of a compare event.

| Compare Modes           | Function                                                                                                                        |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Mode 0                  | Interrupt-only compare mode;<br>Several compare interrupts per timer period are possible                                        |

| Mode 1                  | Pin toggles on each compare match;<br>Several compare events per timer period are possible                                      |

| Mode 2                  | Interrupt-only compare mode;<br>Only one compare interrupt per timer period is generated                                        |

| Mode 3                  | Pin set '1' on match; pin reset '0' on compare timer overflow;<br>Only one compare event per timer period is generated          |

| Double Register<br>Mode | Two registers operate on one pin;<br>Pin toggles on each compare match;<br>Several compare events per timer period are possible |

| Single Event Mode       | Generates single edges or pulses;<br>Can be used with any compare mode                                                          |

The RTC module can be used for different purposes:

- System clock to determine the current time and date

- Cyclic time-based interrupt, to provide a system time tick independent of CPU frequency and other resources

- 48-bit timer for long-term measurements

- Alarm interrupt at a defined time

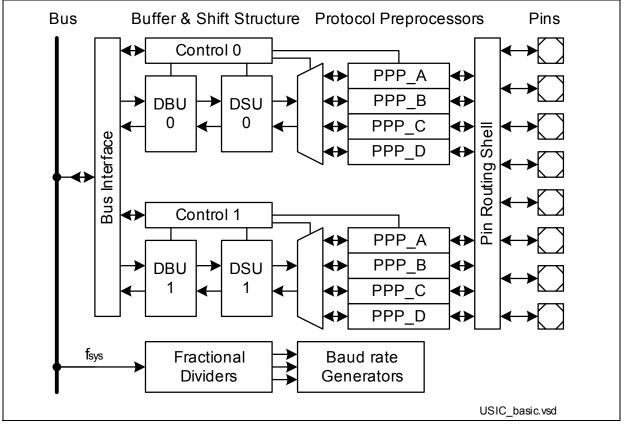

## 3.11 Universal Serial Interface Channel Modules (USIC)

The XE164 includes up to three USIC modules (USIC0, USIC1, USIC2), each providing two serial communication channels.

The Universal Serial Interface Channel (USIC) module is based on a generic data shift and data storage structure which is identical for all supported serial communication protocols. Each channel supports complete full-duplex operation with a basic data buffer structure (one transmit buffer and two receive buffer stages). In addition, the data handling software can use FIFOs.

The protocol part (generation of shift clock/data/control signals) is independent of the general part and is handled by protocol-specific preprocessors (PPPs).

The USIC's input/output lines are connected to pins by a pin routing unit. The inputs and outputs of each USIC channel can be assigned to different interface pins, providing great flexibility to the application software. All assignments can be made during runtime.

#### Figure 10 General Structure of a USIC Module

The regular structure of the USIC module brings the following advantages:

- Higher flexibility through configuration with same look-and-feel for data management

- Reduced complexity for low-level drivers serving different protocols

- Wide range of protocols with improved performances (baud rate, buffer handling)

#### **Target Protocols**

Each USIC channel can receive and transmit data frames with a selectable data word width from 1 to 16 bits in each of the following protocols:

- **UART** (asynchronous serial channel)

- maximum baud rate:  $f_{SYS}$  / 4

- data frame length programmable from 1 to 63 bits

- MSB or LSB first

- LIN Support (Local Interconnect Network)

- maximum baud rate:  $f_{SYS}$  / 16

- checksum generation under software control

- baud rate detection possible by built-in capture event of baud rate generator

- SSC/SPI/QSPI (synchronous serial channel with or without data buffer)

- maximum baud rate in slave mode:  $f_{\rm SYS}$

- maximum baud rate in master mode:  $f_{SYS}$  / 2, limited by loop delay

- number of data bits programmable from 1 to 63, more with explicit stop condition

- MSB or LSB first

- optional control of slave select signals

- IIC (Inter-IC Bus)

- supports baud rates of 100 kbit/s and 400 kbit/s

- **IIS** (Inter-IC Sound Bus)

- maximum baud rate:  $f_{SYS}$  / 2 for transmitter,  $f_{SYS}$  for receiver

- Note: Depending on the selected functions (such as digital filters, input synchronization stages, sample point adjustment, etc.), the maximum achievable baud rate can be limited. Please note that there may be additional delays, such as internal or external propagation delays and driver delays (e.g. for collision detection in UART mode, for IIC, etc.).

#### **MultiCAN Features**

- CAN functionality conforming to CAN specification V2.0 B active for each CAN node (compliant to ISO 11898)

- Up to four independent CAN nodes

- 128 independent message objects (shared by the CAN nodes)

- Dedicated control registers for each CAN node

- Data transfer rate up to 1 Mbit/s, individually programmable for each node

- Flexible and powerful message transfer control and error handling capabilities

- Full-CAN functionality for message objects:

- Can be assigned to one of the CAN nodes

- Configurable as transmit or receive objects, or as message buffer FIFO

- Handle 11-bit or 29-bit identifiers with programmable acceptance mask for filtering

- Remote Monitoring Mode, and frame counter for monitoring

- Automatic Gateway Mode support

- 16 individually programmable interrupt nodes

- Analyzer mode for CAN bus monitoring

| Table 10Instruction Set Summary (cont'd) |                                     |       |  |  |  |  |

|------------------------------------------|-------------------------------------|-------|--|--|--|--|

| Mnemonic                                 | Description                         | Bytes |  |  |  |  |

| NOP                                      | Null operation                      | 2     |  |  |  |  |

| CoMUL/CoMAC                              | Multiply (and accumulate)           | 4     |  |  |  |  |

| CoADD/CoSUB                              | Add/Subtract                        | 4     |  |  |  |  |

| Co(A)SHR                                 | (Arithmetic) Shift right            | 4     |  |  |  |  |

| CoSHL                                    | Shift left                          | 4     |  |  |  |  |

| CoLOAD/STORE                             | Load accumulator/Store MAC register | 4     |  |  |  |  |

| CoCMP                                    | Compare                             | 4     |  |  |  |  |

| CoMAX/MIN                                | Maximum/Minimum                     | 4     |  |  |  |  |

| CoABS/CoRND                              | Absolute value/Round accumulator    | 4     |  |  |  |  |

| CoMOV                                    | Data move                           | 4     |  |  |  |  |

| CoNEG/NOP                                | Negate accumulator/Null operation   | 4     |  |  |  |  |

1) The Enter Power Down Mode instruction is not used in the XE164, due to the enhanced power control scheme. PWRDN will be correctly decoded, but will trigger no action.

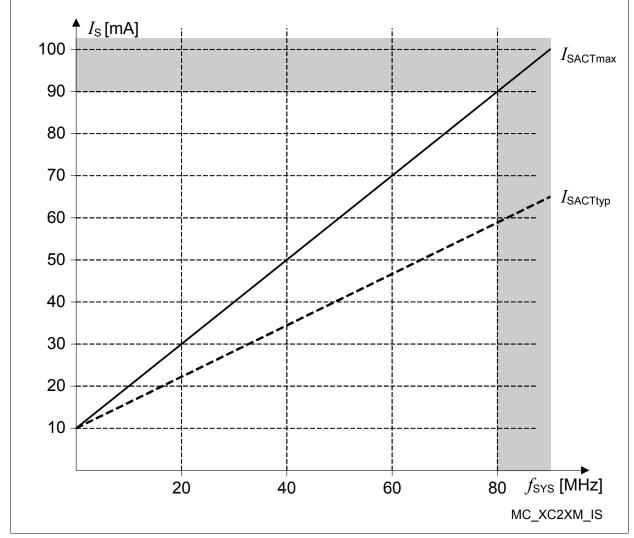

Figure 13 Supply Current in Active Mode as a Function of Frequency

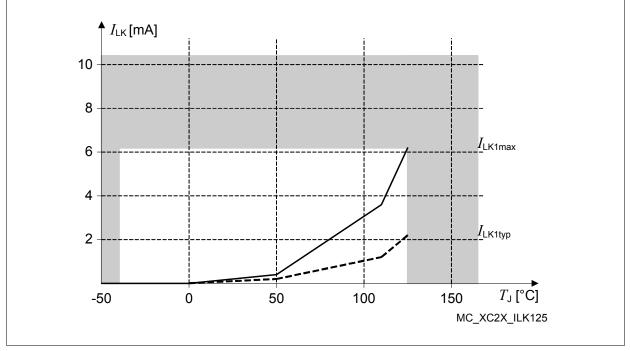

# Table 17Leakage Power Consumption XE164<br/>(Operating Conditions apply)

| Parameter                                                                                      | Sym-<br>bol   | Values |      |      | Unit | Note /                        |

|------------------------------------------------------------------------------------------------|---------------|--------|------|------|------|-------------------------------|

|                                                                                                |               | Min.   | Тур. | Max. |      | Test Condition <sup>1)</sup>  |

| Leakage supply current <sup>2)</sup><br>Formula <sup>3)</sup> : $600,000 \times e^{-\alpha}$ ; | $I_{\rm LK1}$ | _      | 0.03 | 0.05 | mA   | <i>T</i> <sub>J</sub> = 25°C  |

|                                                                                                |               | _      | 0.5  | 1.3  | mA   | <i>T</i> <sub>J</sub> = 85°C  |

| $\alpha$ = 5000 / (273 + B×T <sub>J</sub> );<br>Typ.: B = 1.0, Max.: B = 1.3                   |               | -      | 2.1  | 6.2  | mA   | <i>T</i> <sub>J</sub> = 125°C |

1) All inputs (including pins configured as inputs) are set at 0 V to 0.1 V or at  $V_{DDP}$  - 0.1 V to  $V_{DDP}$  and all outputs (including pins configured as outputs) are disconnected.

2) The supply current caused by leakage depends mainly on the junction temperature (see Figure 14) and the supply voltage. The temperature difference between the junction temperature  $T_J$  and the ambient temperature  $T_A$  must be taken into account. As this fraction of the supply current does not depend on device activity, it must be added to other power consumption values.

3) This formula is valid for temperatures above 0°C. For temperatures below 0°C a value of below 10  $\mu$ A can be assumed.

Figure 14 Leakage Supply Current as a Function of Temperature

| Table 21          | Coding of Bitfields LEVXV in Register SWDCONU |                      |  |  |  |  |

|-------------------|-----------------------------------------------|----------------------|--|--|--|--|

| Code              | Default Voltage Level                         | Notes <sup>1)</sup>  |  |  |  |  |

| 0000 <sub>B</sub> | 2.9 V                                         |                      |  |  |  |  |

| 0001 <sub>B</sub> | 3.0 V                                         | LEV1V: reset request |  |  |  |  |

| 0010 <sub>B</sub> | 3.1 V                                         |                      |  |  |  |  |

| 0011 <sub>B</sub> | 3.2 V                                         |                      |  |  |  |  |

| 0100 <sub>B</sub> | 3.3 V                                         |                      |  |  |  |  |

| 0101 <sub>B</sub> | 3.4 V                                         |                      |  |  |  |  |

| 0110 <sub>B</sub> | 3.6 V                                         |                      |  |  |  |  |

| 0111 <sub>B</sub> | 4.0 V                                         |                      |  |  |  |  |

| 1000 <sub>B</sub> | 4.2 V                                         |                      |  |  |  |  |

| 1001 <sub>B</sub> | 4.5 V                                         | LEV2V: no request    |  |  |  |  |

| 1010 <sub>B</sub> | 4.6 V                                         |                      |  |  |  |  |

| 1011 <sub>B</sub> | 4.7 V                                         |                      |  |  |  |  |

| 1100 <sub>B</sub> | 4.8 V                                         |                      |  |  |  |  |

| 1101 <sub>B</sub> | 4.9 V                                         |                      |  |  |  |  |

| 1110 <sub>B</sub> | 5.0 V                                         |                      |  |  |  |  |

| 1111 <sub>B</sub> | 5.5 V                                         |                      |  |  |  |  |

|                   |                                               |                      |  |  |  |  |

### Table 21 Coding of Bitfields LEVxV in Register SWDCON0

1) The indicated default levels are selected automatically after a power reset.

#### Table 22 Coding of Bitfields LEVxV in Registers PVCyCONz

| Code Default Voltage Level |       | Notes <sup>1)</sup>      |  |  |  |  |

|----------------------------|-------|--------------------------|--|--|--|--|

| 000 <sub>B</sub>           | 0.9 V |                          |  |  |  |  |

| 001 <sub>B</sub>           | 1.0 V |                          |  |  |  |  |

| 010 <sub>B</sub>           | 1.1 V |                          |  |  |  |  |

| 011 <sub>B</sub>           | 1.2 V |                          |  |  |  |  |

| 100 <sub>B</sub>           | 1.3 V | LEV1V: reset request     |  |  |  |  |

| 101 <sub>B</sub>           | 1.4 V | LEV2V: interrupt request |  |  |  |  |

| 110 <sub>B</sub>           | 1.5 V |                          |  |  |  |  |

| 111 <sub>B</sub>           | 1.6 V |                          |  |  |  |  |

1) The indicated default levels are selected automatically after a power reset.

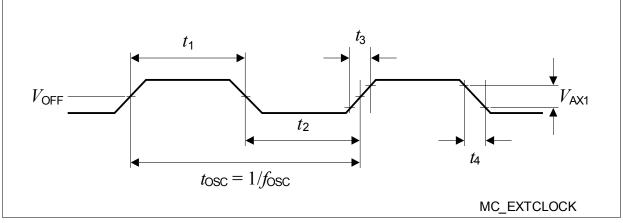

## 4.6.3 External Clock Input Parameters

These parameters specify the external clock generation for the XE164. The clock can be generated in two ways:

- By connecting a crystal or ceramic resonator to pins XTAL1/XTAL2.

- By supplying an **external clock signal**. This clock signal can be supplied either to pin XTAL1 (core voltage domain) or to pin CLKIN1 (IO voltage domain).

If connected to CLKIN1, the input signal must reach the defined input levels  $V_{\rm IL}$  and  $V_{\rm IH}$ . In connected to XTAL1, a minimum amplitude  $V_{\rm AX1}$  (peak-to-peak voltage) is sufficient for the operation of the on-chip oscillator.

Note: The given clock timing parameters  $(t_1 \dots t_4)$  are only valid for an external clock input signal.

| Parameter                                      | Symbol             | Limit Values               |      |      | Unit | Note / Test                                            |

|------------------------------------------------|--------------------|----------------------------|------|------|------|--------------------------------------------------------|

|                                                |                    | Min.                       | Тур. | Max. |      | Condition                                              |

| Input voltage range limits for signal on XTAL1 | $V_{\rm IX1}$ SR   | -1.7 +<br>V <sub>DDI</sub> | -    | 1.7  | V    | 1)                                                     |

| Input voltage (amplitude)<br>on XTAL1          | $V_{AX1}SR$        | $0.3 \times V_{ m DDI}$    | -    | -    | V    | Peak-to-peak<br>voltage <sup>2)</sup>                  |

| XTAL1 input current                            | I <sub>IL</sub> CC | _                          | -    | ±20  | μA   | $0 \vee \langle V_{\rm IN} \langle V_{\rm DI} \rangle$ |

| Oscillator frequency                           | $f_{\rm OSC}$ CC   | 4                          | -    | 40   | MHz  | Clock signal                                           |

|                                                |                    | 4                          | -    | 16   | MHz  | Crystal or<br>Resonator                                |

| High time                                      | $t_1$ SR           | 6                          | -    | -    | ns   |                                                        |

| Low time                                       | t <sub>2</sub> SR  | 6                          | -    | -    | ns   |                                                        |

| Rise time                                      | t <sub>3</sub> SR  | _                          | 8    | 8    | ns   |                                                        |

| Fall time                                      | t <sub>4</sub> SR  | _                          | 8    | 8    | ns   |                                                        |

## Table 26External Clock Input Characteristics<br/>(Operating Conditions apply)

1) Overload conditions must not occur on pin XTAL1.

2) The amplitude voltage  $V_{AX1}$  refers to the offset voltage  $V_{OFF}$ . This offset voltage must be stable during the operation and the resulting voltage peaks must remain within the limits defined by  $V_{IX1}$ .

#### Figure 20 External Clock Drive XTAL1

Note: For crystal/resonator operation, it is strongly recommended to measure the oscillation allowance (negative resistance) in the final target system (layout) to determine the optimum parameters for oscillator operation. Please refer to the limits specified by the crystal/resonator supplier.

### 4.6.6 JTAG Interface Timing

The following parameters are applicable for communication through the JTAG debug interface. The JTAG module is fully compliant with IEEE1149.1-2000.

*Note:* These parameters are not subject to production test but verified by design and/or characterization.

| Parameter                                                       | Symbol                    | Values |      |      | Unit | Note /                 |

|-----------------------------------------------------------------|---------------------------|--------|------|------|------|------------------------|

|                                                                 |                           | Min.   | Тур. | Max. |      | Test Condition         |

| TCK clock period                                                | t <sub>1</sub> SR         | 60     | 50   | _    | ns   | -                      |

| TCK high time                                                   | $t_2$ SR                  | 16     | —    | _    | ns   | -                      |

| TCK low time                                                    | $t_3$ SR                  | 16     | -    | _    | ns   | -                      |

| TCK clock rise time                                             | t <sub>4</sub> SR         | _      | _    | 8    | ns   | -                      |

| TCK clock fall time                                             | t <sub>5</sub> SR         | _      | _    | 8    | ns   | -                      |

| TDI/TMS setup<br>to TCK rising edge                             | $t_6 \mathrm{SR}$         | 6      | -    | -    | ns   | -                      |

| TDI/TMS hold<br>after TCK rising edge                           | t <sub>7</sub> SR         | 6      | -    | -    | ns   | -                      |

| TDO valid                                                       | t <sub>8</sub> CC         | _      | _    | 30   | ns   | C <sub>L</sub> = 50 pF |

| after TCK falling edge <sup>1)</sup>                            | t <sub>8</sub> CC         | 10     | _    | _    | ns   | C <sub>L</sub> = 20 pF |

| TDO high imped. to valid from TCK falling edge <sup>1)2)</sup>  | t <sub>9</sub> CC         | -      | -    | 30   | ns   | C <sub>L</sub> = 50 pF |

| TDO valid to high imped.<br>from TCK falling edge <sup>1)</sup> | <i>t</i> <sub>10</sub> CC | -      | -    | 30   | ns   | C <sub>L</sub> = 50 pF |

## Table 33JTAG Interface Timing Parameters<br/>(Operating Conditions apply)

1) The falling edge on TCK is used to generate the TDO timing.

2) The setup time for TDO is given implicitly by the TCK cycle time.