# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | Z8                                                        |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 8MHz                                                      |

| Connectivity               | -                                                         |

| Peripherals                | HLVD, POR, WDT                                            |

| Number of I/O              | 16                                                        |

| Program Memory Size        | 32KB (32K x 8)                                            |

| Program Memory Type        | OTP                                                       |

| EEPROM Size                | -                                                         |

| RAM Size                   | 237 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                 |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/zgp323lah2032g |

|                            |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

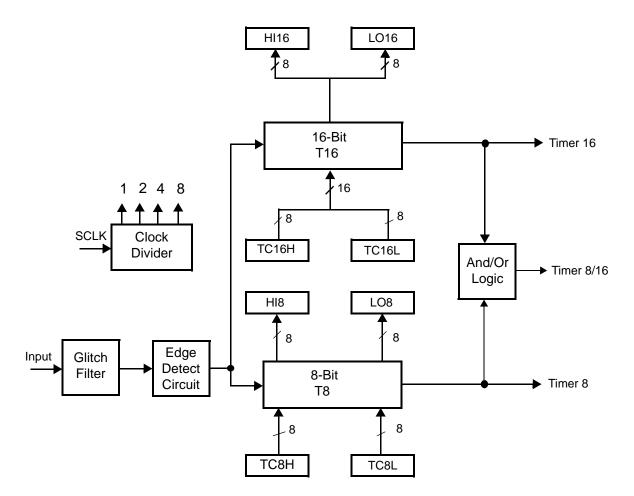

Figure 2. Counter/Timers Diagram

### **Pin Description**

The pin configuration for the 20-pin PDIP/SOIC/SSOP is illustrated in Figure 3 and described in Table 3. The pin configuration for the 28-pin PDIP/SOIC/SSOP are depicted in Figure 4 and described in Table 4. The pin configurations for the 40-pin PDIP and 48-pin SSOP versions are illustrated in Figure 5, Figure 6, and described in Table 5.

For customer engineering code development, a UV eraseable windowed cerdip packaging is offered in 20-pin, 28-pin, and 40-pin configurations. ZiLOG does not recommend nor guarantee these packages for use in production.

| P25 1<br>P26 2<br>P27 3<br>P04 4<br>P05 5<br>P06 6<br>P07 7<br>V <sub>DD</sub> 8<br>XTAL2 9<br>XTAL1 10<br>P31 11<br>P32 12<br>P33 13<br>P34 14 | 28-Pin<br>PDIP<br>SOIC<br>SSOP<br>CDIP* | 28 □ P24<br>27 □ P23<br>26 □ P22<br>25 □ P21<br>24 □ P20<br>23 □ P03<br>22 □ V <sub>SS</sub><br>21 □ P02<br>20 □ P01<br>19 □ P00<br>18 □ Pref1/P30<br>17 □ P36<br>16 □ P37<br>15 □ P35 |

|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

#### Figure 4. 28-Pin PDIP/SOIC/SSOP/CDIP\* Pin Configuration

| Table 4. 28-Pin PDIP/SOIC/SSOP/CDIP* Pin Identifica |

|-----------------------------------------------------|

|-----------------------------------------------------|

| Pin   | Symbol          | Direction    | Description                                              |

|-------|-----------------|--------------|----------------------------------------------------------|

| 1-3   | P25-P27         | Input/Output | Port 2, Bits 5,6,7                                       |

| 4-7   | P04-P07         | Input/Output | Port 0, Bits 4,5,6,7                                     |

| 8     | V <sub>DD</sub> |              | Power supply                                             |

| 9     | XTAL2           | Output       | Crystal, oscillator clock                                |

| 10    | XTAL1           | Input        | Crystal, oscillator clock                                |

| 11-13 | P31-P33         | Input        | Port 3, Bits 1,2,3                                       |

| 14    | P34             | Output       | Port 3, Bit 4                                            |

| 15    | P35             | Output       | Port 3, Bit 5                                            |

| 16    | P37             | Output       | Port 3, Bit 7                                            |

| 17    | P36             | Output       | Port 3, Bit 6                                            |

| 18    | Pref1/P30       | Input        | Analog ref input; connect to V <sub>CC</sub> if not used |

|       | Port 3 Bit 0    |              | Input for Pref1/P30                                      |

| 19-21 | P00-P02         | Input/Output | Port 0, Bits 0,1,2                                       |

| 22    | V <sub>SS</sub> |              | Ground                                                   |

| 23    | P03             | Input/Output | Port 0, Bit 3                                            |

| 24-28 | P20-P24         | Input/Output | Port 2, Bits 0-4                                         |

**Note:** \*Windowed Cerdip. These units are intended to be used for engineering code development only. ZiLOG does not recommend/guarantee this package for production use.

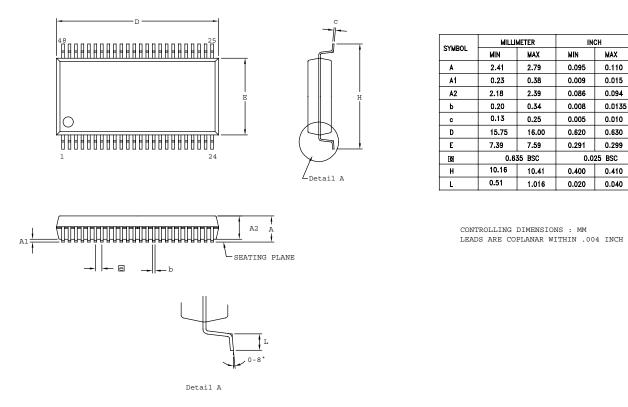

# Z8 GP<sup>TM</sup> OTP MCU Family Product Specification

|       | i |    |                |      |           |

|-------|---|----|----------------|------|-----------|

|       |   |    | $\bigcirc$     | 40   |           |

| NC    |   | 1  |                | 48   | I NC      |

| P25   | С | 2  |                | 47   | I NC      |

| P26   |   | 3  |                | 46   | I P24     |

| P27   |   | 4  |                | 45   | P23       |

| P04   |   | 5  |                | 44   | P22       |

| N/C   |   | 6  |                | 43   | I P21     |

| P05   |   | 7  |                | 42   | I P20     |

| P06   |   | 8  |                | 41   | P03       |

| P14   |   | 9  |                | 40   | I P13     |

| P15   |   | 10 |                | 39   | I P12     |

| P07   |   | 11 | 40 Dia         | 38   | VSS       |

| VDD   |   | 12 | 48-Pin<br>SSOP | 37   | VSS       |

| VDD   |   | 13 | 330F           | 36   | N/C       |

| N/C   |   | 14 |                | 35   | P02       |

| P16   |   | 15 |                | 34   | I P11     |

| P17   |   | 16 |                | 33 = | I P10     |

| XTAL2 |   | 17 |                | 32   | P01       |

| XTAL1 |   | 18 |                | 31   | I P00     |

| P31   |   | 19 |                | 30   | N/C       |

| P32   |   | 20 |                | 29   | PREF1/P30 |

| P33   |   | 21 |                | 28   | P36       |

| P34   |   | 22 |                | 27   | I P37     |

| NC    |   | 23 |                | 26   | I P35     |

| VSS   |   | 24 |                | 25   | RESET     |

Figure 6. 48-Pin SSOP Pin Configuration

Table 5. 40- and 48-Pin Configuration

| 40-Pin PDIP/CDIP* # | 48-Pin SSOP # | Symbol |

|---------------------|---------------|--------|

| 26                  | 31            | P00    |

| 27                  | 32            | P01    |

| 30                  | 35            | P02    |

| 34                  | 41            | P03    |

| 5                   | 5             | P04    |

| 6                   | 7             | P05    |

| 7                   | 8             | P06    |

| 10                  | 11            | P07    |

| 28                  | 33            | P10    |

| 29                  | 34            | P11    |

| 32                  | 39            | P12    |

# Z8 GP<sup>™</sup> OTP MCU Family Product Specification

| 40-Pin PDIP/CDIP* # | 48-Pin SSOP # | Symbol          |

|---------------------|---------------|-----------------|

| 33                  | 40            | P13             |

| 8                   | 9             | P14             |

| 9                   | 10            | P15             |

| 12                  | 15            | P16             |

| 13                  | 16            | P17             |

| 35                  | 42            | P20             |

| 36                  | 43            | P21             |

| 37                  | 44            | P22             |

| 38                  | 45            | P23             |

| 39                  | 46            | P24             |

| 2                   | 2             | P25             |

| 3                   | 3             | P26             |

| 4                   | 4             | P27             |

| 16                  | 19            | P31             |

| 17                  | 20            | P32             |

| 18                  | 21            | P33             |

| 19                  | 22            | P34             |

| 22                  | 26            | P35             |

| 24                  | 28            | P36             |

| 23                  | 27            | P37             |

| 20                  | 23            | NC              |

| 40                  | 47            | NC              |

| 1                   | 1             | NC              |

| 21                  | 25            | RESET           |

| 15                  | 18            | XTAL1           |

| 14                  | 17            | XTAL2           |

| 11                  | 12, 13        | V <sub>DD</sub> |

| 31                  | 24, 37, 38    | V <sub>SS</sub> |

| 25                  | 29            | Pref1/P30       |

|                     | 48            | NC              |

|                     |               |                 |

#### Table 5. 40- and 48-Pin Configuration (Continued)

### **AC Characteristics**

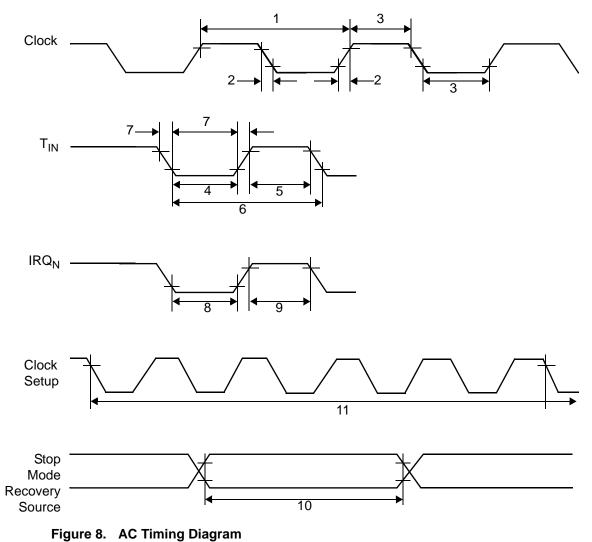

Figure 8 and Table 10 describe the Alternating Current (AC) characteristics.

# Z8 GP<sup>™</sup> OTP MCU Family Product Specification

| Lessting of the                  | 700  | Not Accessible      |

|----------------------------------|------|---------------------|

| Location of 32                   | 2768 | On-Chip             |

| instruction                      |      | ROM                 |

| executed<br>after RESET          |      |                     |

|                                  | 12   | Reset Start Address |

|                                  | 11   | IRQ5                |

|                                  | 10   | IRQ5                |

|                                  | 9    | IRQ4                |

|                                  | 8    | IRQ4                |

| Interrupt Vector                 | 7    | IRQ3                |

| Interrupt Vector<br>(Lower Byte) | 6    | IRQ3                |

|                                  | 5    | IRQ2                |

| Interrupt Vector                 | 4    | ➡ IRQ2              |

| (Upper Byte)                     | 3    | IRQ1                |

|                                  | 2    | IRQ1                |

|                                  | 1    | IRQ0                |

|                                  | 0    | IRQ0                |

Figure 14. Program Memory Map (32K OTP)

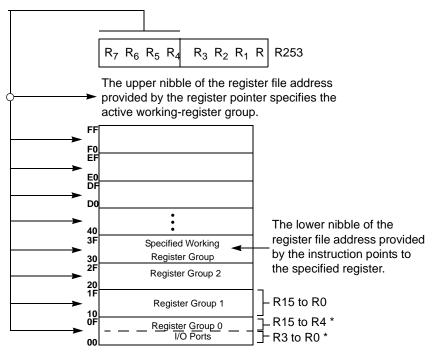

### **Expanded Register File**

The register file has been expanded to allow for additional system control registers and for mapping of additional peripheral devices into the register address area. The Z8<sup>®</sup> register address space (R0 through R15) has been implemented as 16 banks, with 16 registers per bank. These register groups are known as the

\* RP = 00: Selects Register Bank 0, Working Register Group 0

Figure 17. Register Pointer—Detail

#### Stack

The internal register file is used for the stack. An 8-bit Stack Pointer SPL (R255) is used for the internal stack that resides in the general-purpose registers (R4–R239). SPH (R254) can be used as a general-purpose register.

32

#### Table 12. CTR0(D)00H Counter/Timer8 Control Register (Continued)

| Field            | Bit Position |     | Value | Description                |

|------------------|--------------|-----|-------|----------------------------|

| Counter_INT_Mask | 1-           | R/W | 0     | Disable Time-Out Interrupt |

|                  |              |     | 1     | Enable Time-Out Interrupt  |

| P34_Out          | 0            | R/W | 0*    | P34 as Port Output         |

|                  |              |     | 1     | T8 Output on P34           |

#### Note:

\*Indicates the value upon Power-On Reset.

#### T8 Enable

This field enables T8 when set (written) to 1.

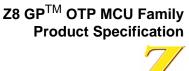

#### Single/Modulo-N

When set to 0 (Modulo-N), the counter reloads the initial value when the terminal count is reached. When set to 1 (single-pass), the counter stops when the terminal count is reached.

#### Timeout

This bit is set when T8 times out (terminal count reached). To reset this bit, write a 1 to its location.

**Caution:** Writing a 1 is the only way to reset the Terminal Count status condition. Reset this bit before using/enabling the counter/timers.

The first clock of T8 might not have complete clock width and can occur any time when enabled.

Note: Take care when using the OR or AND commands to manipulate CTR0, bit 5 and CTR1, bits 0 and 1 (Demodulation Mode). These instructions use a Read-Modify-Write sequence in which the current status from the CTR0 and CTR1 registers is ORed or ANDed with the designated value and then written back into the registers.

#### **T8 Clock**

This bit defines the frequency of the input signal to T8.

34

| Field             | Bit Position |     | Value | Description            |

|-------------------|--------------|-----|-------|------------------------|

| Transmit_Submode/ | 32           | R/W |       | Transmit Mode          |

| Glitch_Filter     |              |     | 00*   | Normal Operation       |

|                   |              |     | 01    | Ping-Pong Mode         |

|                   |              |     | 10    | T16_Out = 0            |

|                   |              |     | 11    | T16_Out = 1            |

|                   |              |     |       | Demodulation Mode      |

|                   |              |     | 00*   | No Filter              |

|                   |              |     | 01    | 4 SCLK Cycle           |

|                   |              |     | 10    | 8 SCLK Cycle           |

|                   |              |     | 11    | Reserved               |

| Initial_T8_Out/   | 1-           |     |       | Transmit Mode          |

| Rising Edge       |              | R/W | 0*    | T8_OUT is 0 Initially  |

|                   |              |     | 1     | T8_OUT is 1 Initially  |

|                   |              |     |       | Demodulation Mode      |

|                   |              | R   | 0*    | No Rising Edge         |

|                   |              |     | 1     | Rising Edge Detected   |

|                   |              | W   | 0     | No Effect              |

|                   |              |     | 1     | Reset Flag to 0        |

| Initial_T16_Out/  | 0            |     |       | Transmit Mode          |

| Falling_Edge      |              | R/W | 0*    | T16_OUT is 0 Initially |

|                   |              |     | 1     | T16_OUT is 1 Initially |

|                   |              |     |       | Demodulation Mode      |

|                   |              | R   | 0*    | No Falling Edge        |

|                   |              |     | 1     | Falling Edge Detected  |

|                   |              | W   | 0     | No Effect              |

|                   |              |     | 1     | Reset Flag to 0        |

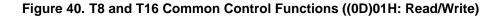

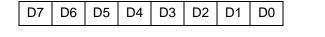

#### Table 13. CTR1(0D)01H T8 and T16 Common Functions (Continued)

#### Note:

\*Default at Power-On Reset.

\*\*Default at Power-On Reset.Not reset with Stop Mode recovery.

#### Mode

If the result is 0, the counter/timers are in TRANSMIT mode; otherwise, they are in DEMODULATION mode.

#### P36\_Out/Demodulator\_Input

In TRANSMIT Mode, this bit defines whether P36 is used as a normal output pin or the combined output of T8 and T16.

In DEMODULATION Mode, this bit defines whether the input signal to the Counter/Timers is from P20 or P31.

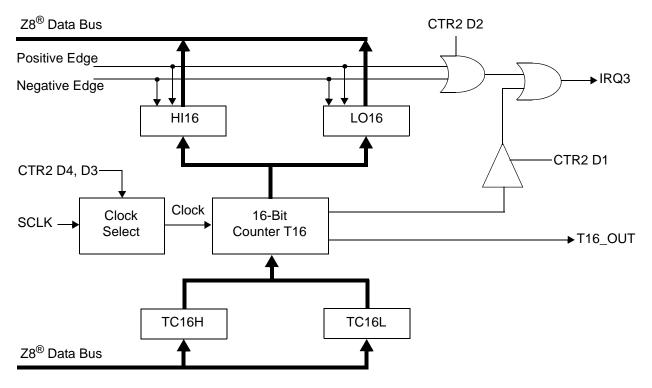

If the input signal is from Port 31, a capture event may also generate an IRQ2 interrupt. To prevent generating an IRQ2, either disable the IRQ2 interrupt by clearing its IMR bit D2 or use P20 as the input.

35

#### T8/T16\_Logic/Edge \_Detect

In TRANSMIT Mode, this field defines how the outputs of T8 and T16 are combined (AND, OR, NOR, NAND).

In DEMODULATION Mode, this field defines which edge should be detected by the edge detector.

#### Transmit\_Submode/Glitch Filter

In Transmit Mode, this field defines whether T8 and T16 are in the PING-PONG mode or in independent normal operation mode. Setting this field to "NORMAL OPERATION Mode" terminates the "PING-PONG Mode" operation. When set to 10, T16 is immediately forced to a 0; a setting of 11 forces T16 to output a 1.

In DEMODULATION Mode, this field defines the width of the glitch that must be filtered out.

#### Initial\_T8\_Out/Rising\_Edge

In TRANSMIT Mode, if 0, the output of T8 is set to 0 when it starts to count. If 1, the output of T8 is set to 1 when it starts to count. When the counter is not enabled and this bit is set to 1 or 0, T8\_OUT is set to the opposite state of this bit. This ensures that when the clock is enabled, a transition occurs to the initial state set by CTR1, D1.

In DEMODULATION Mode, this bit is set to 1 when a rising edge is detected in the input signal. In order to reset the mode, a 1 should be written to this location.

#### Initial\_T16 Out/Falling \_Edge

In TRANSMIT Mode, if it is 0, the output of T16 is set to 0 when it starts to count. If it is 1, the output of T16 is set to 1 when it starts to count. This bit is effective only in Normal or PING-PONG Mode (CTR1, D3; D2). When the counter is not enabled and this bit is set, T16\_OUT is set to the opposite state of this bit. This ensures that when the clock is enabled, a transition occurs to the initial state set by CTR1, D0.

In DEMODULATION Mode, this bit is set to 1 when a falling edge is detected in the input signal. In order to reset it, a 1 should be written to this location.

**Note:** Modifying CTR1 (D1 or D0) while the counters are enabled causes unpredictable output from T8/16\_OUT.

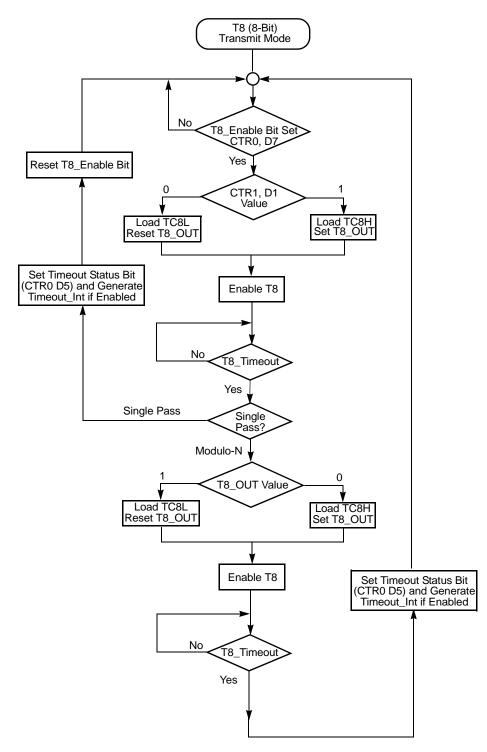

#### CTR2 Counter/Timer 16 Control Register—CTR2(D)02H

Table 14 lists and briefly describes the fields for this register.

Figure 19. Transmit Mode Flowchart

#### **T16 Transmit Mode**

In NORMAL or PING-PONG mode, the output of T16 when not enabled, is dependent on CTR1, D0. If it is a 0, T16\_OUT is a 1; if it is a 1, T16\_OUT is 0. You can force the output of T16 to either a 0 or 1 whether it is enabled or not by programming CTR1 D3; D2 to a 10 or 11.

When T16 is enabled, TC16H \* 256 + TC16L is loaded, and T16\_OUT is switched to its initial value (CTR1, D0). When T16 counts down to 0, T16\_OUT is toggled (in NORMAL or PING-PONG mode), an interrupt (CTR2, D1) is generated (if enabled), and a status bit (CTR2, D5) is set. See Figure 25.

Figure 25. 16-Bit Counter/Timer Circuits

**Note:** Global interrupts override this function as described in "Interrupts" on page 48.

If T16 is in SINGLE-PASS mode, it is stopped at this point (see Figure 26). If it is in Modulo-N Mode, it is loaded with TC16H \* 256 + TC16L, and the counting continues (see Figure 27).

You can modify the values in TC16H and TC16L at any time. The new values take effect when they are loaded.

Figure 30. Interrupt Block Diagram

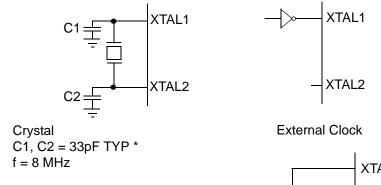

#### Clock

The device's on-chip oscillator has a high-gain, parallel-resonant amplifier, for connection to a crystal, ceramic resonator, or any suitable external clock source (XTAL1 = Input, XTAL2 = Output). The crystal must be AT cut, 1 MHz to 8 MHz maximum, with a series resistance (RS) less than or equal to 100  $\Omega$ . The on-chip oscillator can be driven with a suitable external clock source.

The crystal must be connected across XTAL1 and XTAL2 using the recommended capacitors (capacitance greater than or equal to 22 pF) from each pin to ground.

\* Preliminary value including pin parasitics

Ceramic Resonator f = 8MHz

Figure 31. Oscillator Configuration

| NOP  | ; clear the pipeline |

|------|----------------------|

| Stop | ; enter Stop Mode    |

|      |                      |

| NOP  | ; clear the pipeline |

| HALT | ; enter HALT Mode    |

|      | Stop                 |

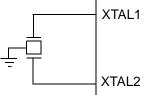

#### Port Configuration Register

The Port Configuration (PCON) register (Figure 32) configures the comparator output on Port 3. It is located in the expanded register 2 at Bank F, location 00.

#### PCON(FH)00H

\* Default setting after reset

#### Figure 32. Port Configuration Register (PCON) (Write Only)

#### Comparator Output Port 3 (D0)

Bit 0 controls the comparator used in Port 3. A 1 in this location brings the comparator outputs to P34 and P37, and a 0 releases the Port to its standard I/O configuration.

#### Port 1 Output Mode (D1)

Bit 1 controls the output mode of port 1. A 1 in this location sets the output to push-pull, and a 0 sets the output to open-drain.

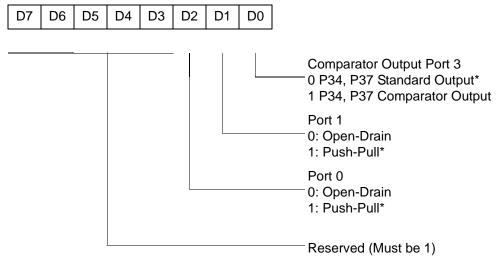

#### SMR(0F)0BH

\* Default after Power On Reset or Watch-Dog Reset

- \* \* Set after STOP Mode Recovery

- \* \* \* At the XOR gate input

\* \* \* \* Default setting after reset. Must be 1 if using a crystal or resonator clock source.

#### Figure 33. STOP Mode Recovery Register

#### SCLK/TCLK Divide-by-16 Select (D0)

D0 of the SMR controls a divide-by-16 prescaler of SCLK/TCLK (Figure 34). This control selectively reduces device power consumption during normal processor execution (SCLK control) and/or Halt Mode (where TCLK sources interrupt logic). After Stop Mode Recovery, this bit is set to a 0.

#### Low-Voltage Detection Register—LVD(D)0Ch

**Note:** Voltage detection does not work at Stop mode. It must be disabled during Stop mode in order to reduce current.

| Field    | Bit Position |     |         | Description                    |

|----------|--------------|-----|---------|--------------------------------|

| LVD      | 76543        |     |         | Reserved<br>No Effect          |

|          | 2            | R   | 1<br>0* | HVD flag set<br>HVD flag reset |

|          | 1-           | R   | 1<br>0* | LVD flag set<br>LVD flag reset |

|          | 0            | R/W | 1<br>0* | Enable VD<br>Disable VD        |

| *Default | after POR    |     |         |                                |

**Note:** Do not modify register P01M while checking a low-voltage condition. Switching noise of both ports 0 and 1 together might trigger the LVD flag.

#### **Voltage Detection and Flags**

The Voltage Detection register (LVD, register 0CH at the expanded register bank 0Dh) offers an option of monitoring the V<sub>CC</sub> voltage. The Voltage Detection is enabled when bit 0 of LVD register is set. Once Voltage Detection is enabled, the the V<sub>CC</sub> level is monitored in real time. The flags in the LVD register valid 20uS after Voltage Detection is enabled. The HVD flag (bit 2 of the LVD register) is set only if V<sub>CC</sub> is higher than V<sub>HVD</sub>. The LVD flag (bit 1 of the LVD register) is set only if V<sub>CC</sub> is lower than the V<sub>LVD</sub>. When Voltage Detection is enabled, the LVD flag also triggers IRQ5. The IRQ bit 5 latches the low voltage condition until it is cleared by instructions or reset. The IRQ5 interrupt is served if it is enabled in the IMR register. Otherwise, bit 5 of IRQ register is latched as a flag only.

**Notes:** If it is necessary to receive an LVD interrupt upon power-up at an operating voltage lower than the low battery detect threshold, enable interrupts using the Enable Interrupt instruction (EI) prior to enabling the voltage detection.

# Z8 GP<sup>™</sup> OTP MCU Family Product Specification

#### CTR1(0D)01H D7 D6 D5 D3 D1 D0 D4 D2 Transmit Mode\* R/W 0 T16\_OUT is 0 initially\* 1 T16\_OUT is 1 initially **Demodulation Mode** R 0 No Falling Edge Detection R 1 Falling Edge Detection W 0 No Effect W 1 Reset Flag to 0 Transmit Mode\* R/W 0 T8\_OUT is 0 initially\* 1 T8\_OUT is 1 initially **Demodulation Mode** R 0 No Rising Edge Detection R 1 Rising Edge Detection W 0 No Effect W 1 Reset Flag to 0 Transmit Mode\* 0 0 Normal Operation\* 0 1 Ping-Pong Mode 1 0 T16\_OUT = 0 1 1 T16\_OUT = 1 **Demodulation Mode** 0 0 No Filter 0 1 4 SCLK Cycle Filter 1 0 8 SCLK Cycle Filter 1 1 Reserved Transmit Mode/T8/T16 Logic 0 0 AND\*\* 0 1 OR 1 0 NOR 1 1 NAND **Demodulation Mode** 0 0 Falling Edge Detection 0 1 Rising Edge Detection 1 0 Both Edge Detection 1 1 Reserved Transmit Mode 0 P36 as Port Output \* 1 P36 as T8/T16\_OUT **Demodulation Mode** 0 P31 as Demodulator Input 1 P20 as Demodulator Input Transmit/Demodulation Mode 0 Transmit Mode \* \* Default setting after reset \*\*Default setting after reset. Not reset with Stop Mode 1 Demodulation Mode recovery

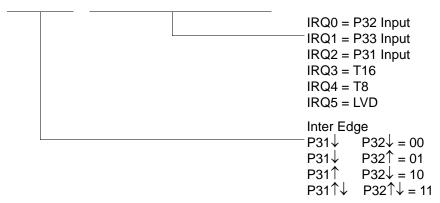

#### R250 IRQ(FAH)

#### Figure 52. Interrupt Request Register (FAH: Read/Write)

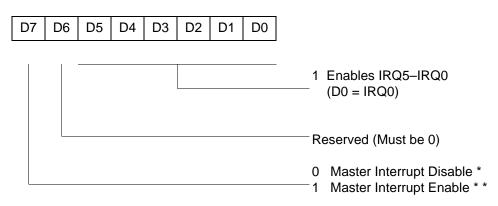

#### R251 IMR(FBH)

\* Default setting after reset

\* \* Only by using EI, DI instruction; DI is required before changing the IMR register

#### Figure 53. Interrupt Mask Register (FBH: Read/Write)

Figure 68. 48-Pin SSOP Package Design

**Note:** Check with ZiLOG on the actual bonding diagram and coordinate for chip-on-board assembly.

>