Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | Z8                                                        |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 8MHz                                                      |

| Connectivity               | -                                                         |

| Peripherals                | HLVD, POR, WDT                                            |

| Number of I/O              | 32                                                        |

| Program Memory Size        | 16KB (16K x 8)                                            |

| Program Memory Type        | OTP                                                       |

| EEPROM Size                | -                                                         |

| RAM Size                   | 237 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                 |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                        |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 40-DIP (0.620", 15.75mm)                                  |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/zgp323lap4016g |

|                            |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Z8 GP<sup>™</sup> OTP MCU Family Product Specification

# **Table of Contents**

| Development Features 1                                                                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General Description                                                                                                                                                                                                      |

| Pin Description                                                                                                                                                                                                          |

| Absolute Maximum Ratings 10                                                                                                                                                                                              |

| Standard Test Conditions 10                                                                                                                                                                                              |

| DC Characteristics                                                                                                                                                                                                       |

| AC Characteristics                                                                                                                                                                                                       |

| Pin Functions 16   XTAL1 Crystal 1 (Time-Based Input) 16   XTAL2 Crystal 2 (Time-Based Output) 16   Port 0 (P07–P00) 16   Port 1 (P17–P10) 17   Port 2 (P27–P20) 18   Port 3 (P37–P30) 19   RESET (Input, Active Low) 23 |

| Functional Description23Program Memory23RAM23Expanded Register File24Register File28Stack29Timers30Counter/Timer Functional Blocks38                                                                                     |

| Expanded Register File Control Registers (0D)                                                                                                                                                                            |

| Expanded Register File Control Registers (0F) 69                                                                                                                                                                         |

| Standard Control Registers                                                                                                                                                                                               |

| Package Information                                                                                                                                                                                                      |

| Ordering Information                                                                                                                                                                                                     |

| Precharacterization Product                                                                                                                                                                                              |

## **AC Characteristics**

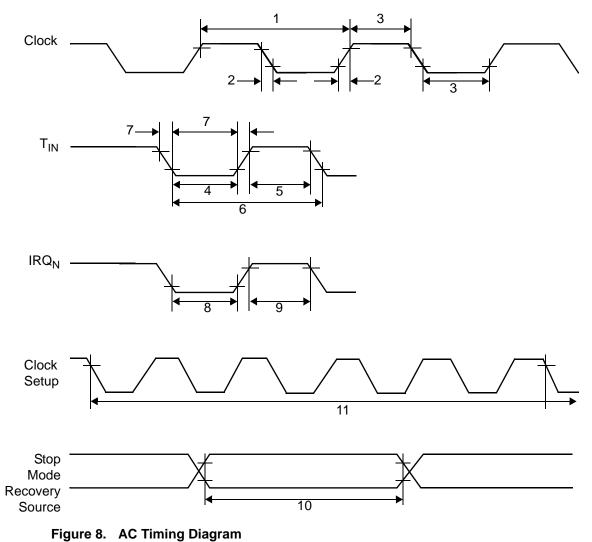

Figure 8 and Table 10 describe the Alternating Current (AC) characteristics.

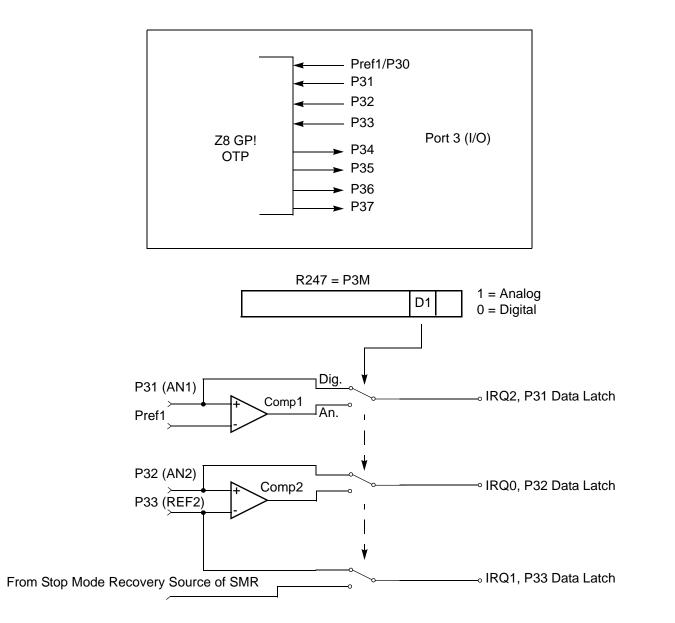

#### Figure 12. Port 3 Configuration

Two on-board comparators process analog signals on P31 and P32, with reference to the voltage on Pref1 and P33. The analog function is enabled by programming the Port 3 Mode Register (bit 1). P31 and P32 are programmable as rising, falling, or both edge triggered interrupts (IRQ register bits 6 and 7). Pref1 and P33 are the comparator reference voltage inputs. Access to the Counter Timer edgedetection circuit is through P31 or P20 (see "T8 and T16 Common Functions—

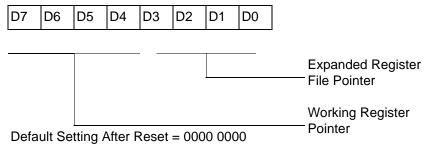

ERF (Expanded Register File). Bits 7–4 of register RP select the working register group. Bits 3–0 of register RP select the expanded register file bank.

>

**Note:** An expanded register bank is also referred to as an expanded register group (see Figure 15).

27

The upper nibble of the register pointer (see Figure 16) selects which working register group, of 16 bytes in the register file, is accessed out of the possible 256. The lower nibble selects the expanded register file bank and, in the case of the Z8 GP family, banks 0, F, and D are implemented. A  $_{0\rm H}$  in the lower nibble allows the normal register file (bank 0) to be addressed. Any other value from 1H to FH exchanges the lower 16 registers to an expanded register bank.

#### Figure 16. Register Pointer

#### Example: Z8 GP: (See Figure 15 on page 26)

R253 RP = 00h R0 = Port 0 R1 = Port 1 R2 = Port 2 R3 = Port 3

But if:

R253 RP = 0Dh R0 = CTRL0 R1 = CTRL1 R2 = CTRL2R3 = Reserved

32

#### Table 12. CTR0(D)00H Counter/Timer8 Control Register (Continued)

| Field            | Bit Position |     | Value | Description                |

|------------------|--------------|-----|-------|----------------------------|

| Counter_INT_Mask | 1-           | R/W | 0     | Disable Time-Out Interrupt |

|                  |              |     | 1     | Enable Time-Out Interrupt  |

| P34_Out          | 0            | R/W | 0*    | P34 as Port Output         |

|                  |              |     | 1     | T8 Output on P34           |

#### Note:

\*Indicates the value upon Power-On Reset.

#### T8 Enable

This field enables T8 when set (written) to 1.

#### Single/Modulo-N

When set to 0 (Modulo-N), the counter reloads the initial value when the terminal count is reached. When set to 1 (single-pass), the counter stops when the terminal count is reached.

#### Timeout

This bit is set when T8 times out (terminal count reached). To reset this bit, write a 1 to its location.

**Caution:** Writing a 1 is the only way to reset the Terminal Count status condition. Reset this bit before using/enabling the counter/timers.

The first clock of T8 might not have complete clock width and can occur any time when enabled.

Note: Take care when using the OR or AND commands to manipulate CTR0, bit 5 and CTR1, bits 0 and 1 (Demodulation Mode). These instructions use a Read-Modify-Write sequence in which the current status from the CTR0 and CTR1 registers is ORed or ANDed with the designated value and then written back into the registers.

#### **T8 Clock**

This bit defines the frequency of the input signal to T8.

#### Capture\_INT\_Mask

Set this bit to allow an interrupt when data is captured into either LO8 or HI8 upon a positive or negative edge detection in demodulation mode.

#### Counter\_INT\_Mask

Set this bit to allow an interrupt when T8 has a timeout.

#### P34\_Out

This bit defines whether P34 is used as a normal output pin or the T8 output.

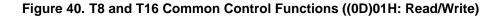

#### T8 and T16 Common Functions—CTR1(0D)01H

This register controls the functions in common with the T8 and T16.

Table 13 lists and briefly describes the fields for this register.

| Field             | Bit Position |     | Value | Description       |

|-------------------|--------------|-----|-------|-------------------|

| Mode              | 7            | R/W | 0*    | Transmit Mode     |

|                   |              |     |       | Demodulation Mode |

| P36_Out/          | -6           | R/W |       | Transmit Mode     |

| Demodulator_Input |              |     | 0*    | Port Output       |

|                   |              |     | 1     | T8/T16 Output     |

|                   |              |     |       | Demodulation Mode |

|                   |              |     | 0     | P31               |

|                   |              |     | 1     | P20               |

| T8/T16_Logic/     | 54           | R/W |       | Transmit Mode     |

| Edge _Detect      |              |     | 00**  | AND               |

| -                 |              |     | 01    | OR                |

|                   |              |     | 10    | NOR               |

|                   |              |     | 11    | NAND              |

|                   |              |     |       | Demodulation Mode |

|                   |              |     | 00**  | Falling Edge      |

|                   |              |     | 01    | Rising Edge       |

|                   |              |     | 10    | Both Edges        |

|                   |              |     | 11    | Reserved          |

#### Table 13. CTR1(0D)01H T8 and T16 Common Functions

# Z i L 0 G 36

| Field            | Bit Position |     | Value | Description                    |

|------------------|--------------|-----|-------|--------------------------------|

| T16_Enable       | 7            | R   | 0*    | Counter Disabled               |

|                  |              |     | 1     | Counter Enabled                |

|                  |              | W   | 0     | Stop Counter                   |

|                  |              |     | 1     | Enable Counter                 |

| Single/Modulo-N  | -6           | R/W |       | Transmit Mode                  |

|                  |              |     | 0*    | Modulo-N                       |

|                  |              |     | 1     | Single Pass                    |

|                  |              |     |       | Demodulation Mode              |

|                  |              |     | 0     | T16 Recognizes Edge            |

|                  |              |     | 1     | T16 Does Not Recognize<br>Edge |

| Time_Out         | 5            | R   | 0*    | No Counter Timeout             |

|                  |              |     | 1     | Counter Timeout                |

|                  |              |     |       | Occurred                       |

|                  |              | W   | 0     | No Effect                      |

|                  |              |     | 1     | Reset Flag to 0                |

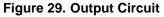

| T16 _Clock       | 43           | R/W | 00**  | SCLK                           |

|                  |              |     | 01    | SCLK/2                         |

|                  |              |     | 10    | SCLK/4                         |

|                  |              |     | 11    | SCLK/8                         |

| Capture_INT_Mask | 2            | R/W | 0**   | Disable Data Capture Int.      |

|                  |              |     | 1     | Enable Data Capture Int.       |

| Counter_INT_Mask | 1-           | R/W | 0     | Disable Timeout Int.           |

|                  |              |     | 1     | Enable Timeout Int.            |

| P35_Out          | 0            | R/W | 0*    | P35 as Port Output             |

|                  |              |     | 1     | T16 Output on P35              |

#### Table 14. CTR2(D)02H: Counter/Timer16 Control Register

#### Note:

\*Indicates the value upon Power-On Reset.

\*\*Indicates the value upon Power-On Reset.Not reset with Stop Mode recovery.

#### T16\_Enable

This field enables T16 when set to 1.

#### Single/Modulo-N

In TRANSMIT Mode, when set to 0, the counter reloads the initial value when it reaches the terminal count. When set to 1, the counter stops when the terminal count is reached.

**Note:** The letter h denotes hexadecimal values.

Transition from 0 to FFh is not a timeout condition.

**Caution:** Using the same instructions for stopping the counter/timers and setting the status bits is not recommended.

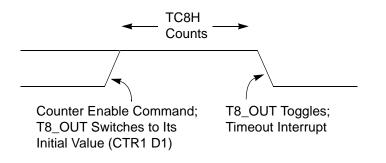

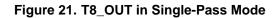

Two successive commands are necessary. First, the counter/timers must be stopped. Second, the status bits must be reset. These commands are required because it takes one counter/timer clock interval for the initiated event to actually occur. See Figure 21 and Figure 22.

Figure 22. T8\_OUT in Modulo-N Mode

#### **T8 Demodulation Mode**

The user must program TC8L and TC8H to FFH. After T8 is enabled, when the first edge (rising, falling, or both depending on CTR1, D5; D4) is detected, it starts to count down. When a subsequent edge (rising, falling, or both depending on CTR1, D5; D4) is detected during counting, the current value of T8 is complemented and put into one of the capture registers. If it is a positive edge, data is put

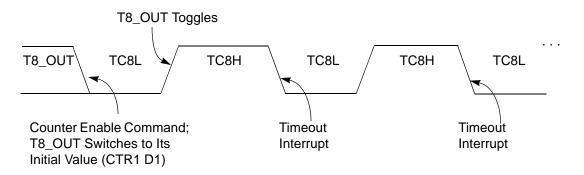

Figure 28. Ping-Pong Mode Diagram

#### Initiating PING-PONG Mode

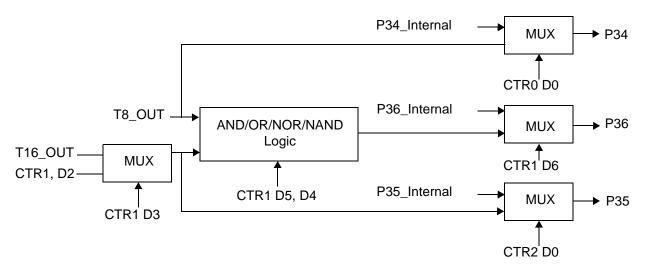

First, make sure both counter/timers are not running. Set T8 into Single-Pass mode (CTR0, D6), set T16 into SINGLE-PASS mode (CTR2, D6), and set the Ping-Pong mode (CTR1, D2; D3). These instructions can be in random order. Finally, start PING-PONG mode by enabling either T8 (CTR0, D7) or T16 (CTR2, D7). See Figure 29.

The initial value of T8 or T16 must not be 1. Stopping the timer and restarting the timer reloads the initial value to avoid an unknown previous value.

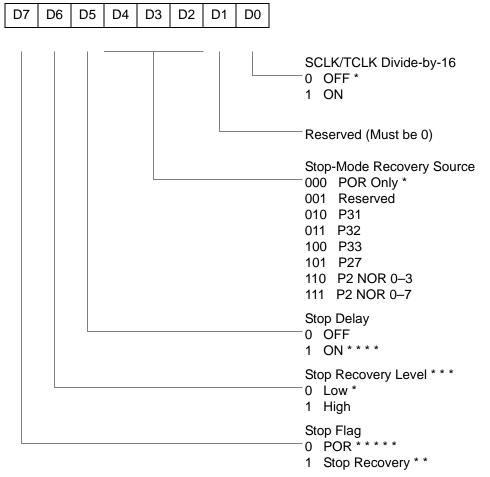

#### Stop-Mode Recovery Source (D2, D3, and D4)

These three bits of the SMR specify the wake-up source of the Stop recovery (Figure 35 and Table 19).

#### Stop-Mode Recovery Register 2—SMR2(F)0DH

Table 18 lists and briefly describes the fields for this register.

| Field          | Bit Position |   | Value            | Description                  |

|----------------|--------------|---|------------------|------------------------------|

| Reserved       | 7            |   | 0                | Reserved (Must be 0)         |

| Recovery Level | -6           | W | 0 <sup>†</sup>   | Low                          |

| -              |              |   | 1                | High                         |

| Reserved       | 5            |   | 0                | Reserved (Must be 0)         |

| Source         | 432          | W | 000 <sup>†</sup> | A. POR Only                  |

|                |              |   | 001              | B. NAND of P23–P20           |

|                |              |   | 010              | C. NAND of P27–P20           |

|                |              |   | 011              | D. NOR of P33–P31            |

|                |              |   | 100              | E. NAND of P33–P31           |

|                |              |   | 101              | F. NOR of P33–P31, P00, P07  |

|                |              |   | 110              | G. NAND of P33–P31, P00, P07 |

|                |              |   | 111              | H. NAND of P33–P31, P22–P20  |

| Reserved       | 10           |   | 00               | Reserved (Must be 0)         |

#### Table 18. SMR2(F)0DH:Stop Mode Recovery Register 2\*

#### Notes:

\* Port pins configured as outputs are ignored as a SMR recovery source. † Indicates the value upon Power-On Reset

#### Stop Mode Recovery Register 2 (SMR2)

This register determines the mode of Stop Mode Recovery for SMR2 (Figure 36).

SMR2(0F)DH

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | ]                                                                                                                                                                                                                                                                                                         |

|----|----|----|----|----|----|----|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |    |    |    |    |    |    |    | Reserved (Must be 0)<br>Reserved (Must be 0)<br>Stop-Mode Recovery Source 2<br>000 POR Only *<br>001 NAND P20, P21, P22, P23<br>010 NAND P20, P21, P22, P23, P24, P25, P26, P27<br>011 NOR P31, P32, P33<br>100 NAND P31, P32, P33<br>101 NOR P31, P32, P33, P00, P07<br>110 NAND P31, P32, P33, P00, P07 |

|    |    |    |    |    |    |    |    | 111 NAND P31, P32, P33, P20, P21, P22<br>Reserved (Must be 0)                                                                                                                                                                                                                                             |

|    |    |    |    |    |    |    |    | Recovery Level * *<br>0 Low *<br>1 High                                                                                                                                                                                                                                                                   |

|    |    |    |    |    |    |    |    | Reserved (Must be 0)                                                                                                                                                                                                                                                                                      |

Note: If used in conjunction with SMR, either of the two specified events causes a Stop-Mode Recovery.

\* Default setting after reset

\* \* At the XOR gate input

#### Figure 36. Stop Mode Recovery Register 2 ((0F)DH:D2–D4, D6 Write Only)

If SMR2 is used in conjunction with SMR, either of the specified events causes a Stop Mode Recovery.

**Note:** Port pins configured as outputs are ignored as an SMR or SMR2 recovery source. For example, if the NAND or P23–P20 is selected as the recovery source and P20 is configured as an output, the remaining SMR pins (P23–P21) form the NAND equation.

#### Watch-Dog Timer Mode Register (WDTMR)

The Watch-Dog Timer (WDT) is a retriggerable one-shot timer that resets the Z8<sup>®</sup> CPU if it reaches its terminal count. The WDT must initially be enabled by executing the WDT instruction. On subsequent executions of the WDT instruction, the WDT is refreshed. The WDT circuit is driven by an on-board RC-oscillator. The WDT instruction affects the Zero (Z), Sign (S), and Overflow (V) flags.

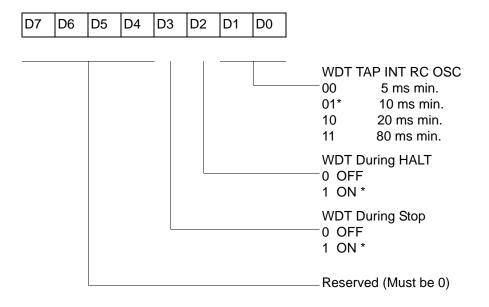

The POR clock source the internal RC-oscillator. Bits 0 and 1 of the WDT register control a tap circuit that determines the minimum timeout period. Bit 2 determines whether the WDT is active during HALT, and Bit 3 determines WDT activity during Stop. Bits 4 through 7 are reserved (Figure 37). This register is accessible only during the first 60 processor cycles (120 XTAL clocks) from the execution of the first instruction after Power-On-Reset, Watch-Dog Reset, or a Stop-Mode Recovery (Figure 36). After this point, the register cannot be modified by any means (intentional or otherwise). The WDTMR cannot be read. The register is located in Bank F of the Expanded Register Group at address location 0Fh. It is organized as shown in Figure 37.

WDTMR(0F)0Fh

\* Default setting after reset

#### Figure 37. Watch-Dog Timer Mode Register (Write Only)

#### WDT Time Select (D0, D1)

This bit selects the WDT time period. It is configured as indicated in Table 20.

# Z8 GP<sup>™</sup> OTP MCU Family Product Specification

#### CTR1(0D)01H D7 D6 D5 D3 D1 D0 D4 D2 Transmit Mode\* R/W 0 T16\_OUT is 0 initially\* 1 T16\_OUT is 1 initially **Demodulation Mode** R 0 No Falling Edge Detection R 1 Falling Edge Detection W 0 No Effect W 1 Reset Flag to 0 Transmit Mode\* R/W 0 T8\_OUT is 0 initially\* 1 T8\_OUT is 1 initially **Demodulation Mode** R 0 No Rising Edge Detection R 1 Rising Edge Detection W 0 No Effect W 1 Reset Flag to 0 Transmit Mode\* 0 0 Normal Operation\* 0 1 Ping-Pong Mode 1 0 T16\_OUT = 0 1 1 T16\_OUT = 1 **Demodulation Mode** 0 0 No Filter 0 1 4 SCLK Cycle Filter 1 0 8 SCLK Cycle Filter 1 1 Reserved Transmit Mode/T8/T16 Logic 0 0 AND\*\* 0 1 OR 1 0 NOR 1 1 NAND **Demodulation Mode** 0 0 Falling Edge Detection 0 1 Rising Edge Detection 1 0 Both Edge Detection 1 1 Reserved Transmit Mode 0 P36 as Port Output \* 1 P36 as T8/T16\_OUT **Demodulation Mode** 0 P31 as Demodulator Input 1 P20 as Demodulator Input Transmit/Demodulation Mode 0 Transmit Mode \* \* Default setting after reset \*\*Default setting after reset. Not reset with Stop Mode 1 Demodulation Mode recovery

#### SMR(0F)0BH

- \* Default setting after Reset

- \* \* Set after STOP Mode Recovery

- \* \* \* At the XOR gate input

- \*\*\*\* Default setting after Reset. Must be 1 if using a crystal or resonator clock source.

- \* \* \* \* \* Default setting after Power On Reset. Not Reset with a Stop Mode recovery.

# Figure 45. Stop Mode Recovery Register ((0F)0BH: D6–D0=Write Only, D7=Read Only)

# Z8 GP<sup>™</sup> OTP MCU Family Product Specification

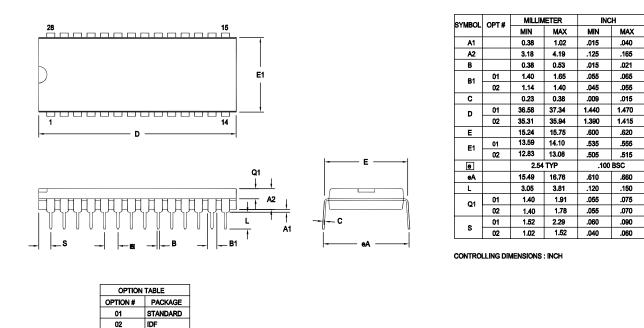

Note: ZILOG supplies both options for production. Component layout PCB design should cover bigger option 01.

Figure 64. 28-Pin PDIP Package Diagram

# Z i L 0 G 92

#### 4KB Standard Temperature: 0° to +70°C

| Part Number    | Description        | Part Number    | Description        |

|----------------|--------------------|----------------|--------------------|

| ZGP323LSH4804C | 48-pin SSOP 4K OTP | ZGP323LSS2804C | 28-pin SOIC 4K OTP |

| ZGP323LSP4004C | 40-pin PDIP 4K OTP | ZGP323LSH2004C | 20-pin SSOP 4K OTP |

| ZGP323LSH2804C | 28-pin SSOP 4K OTP | ZGP323LSP2004C | 20-pin PDIP 4K OTP |

| ZGP323LSP2804C | 28-pin PDIP 4K OTP | ZGP323LSS2004C | 20-pin SOIC 4K OTP |

#### 4KB Extended Temperature: -40° to +105°C

| Part Number    | Description        | Part Number    | Description        |

|----------------|--------------------|----------------|--------------------|

| ZGP323LEH4804C | 48-pin SSOP 4K OTP | ZGP323LES2804C | 28-pin SOIC 4K OTP |

| ZGP323LEP4004C | 40-pin PDIP 4K OTP | ZGP323LEH2004C | 20-pin SSOP 4K OTP |

| ZGP323LEH2804C | 28-pin SSOP 4K OTP | ZGP323LEP2004C | 20-pin PDIP 4K OTP |

| ZGP323LEP2804C | 28-pin PDIP 4K OTP | ZGP323LES2004C | 20-pin SOIC 4K OTP |

#### 4KB Automotive Temperature: -40° to +125°C

|                | •                  |                |                    |

|----------------|--------------------|----------------|--------------------|

| Part Number    | Description        | Part Number    | Description        |

| ZGP323LAH4804C | 48-pin SSOP 4K OTP | ZGP323LAS2804C | 28-pin SOIC 4K OTP |

| ZGP323LAP4004C | 40-pin PDIP 4K OTP | ZGP323LAH2004C | 20-pin SSOP 4K OTP |

| ZGP323LAH2804C | 28-pin SSOP 4K OTP | ZGP323LAP2004C | 20-pin PDIP 4K OTP |

| ZGP323LAP2804C | 28-pin PDIP 4K OTP | ZGP323LAS2004C | 20-pin SOIC 4K OTP |

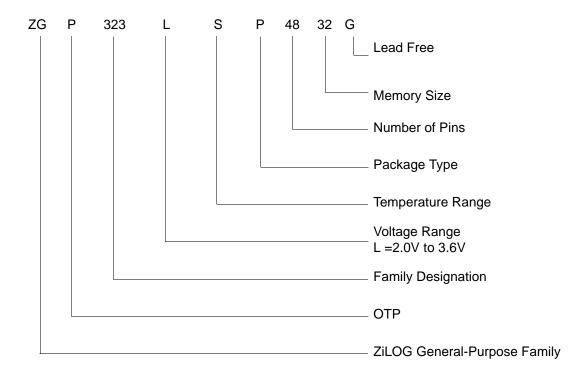

#### Note: Replace C with G for Lead-Free Packaging

#### **Additional Components**

| Part Number    | Description         | Part Number    | Description        |

|----------------|---------------------|----------------|--------------------|

| ZGP323ICE01ZEM | Emulator/programmer | ZGP32300100ZPR | Programming System |

#### Example

### **Precharacterization Product**

The product represented by this document is newly introduced and ZiLOG has not completed the full characterization of the product. The document states what ZiLOG knows about this product at this time, but additional features or nonconformance with some aspects of the document might be found, either by ZiLOG or its customers in the course of further application and characterization work. In addition, ZiLOG cautions that delivery might be uncertain at times, due to start-up yield issues.

ZiLOG, Inc.

532 Race Street San Jose, CA 95126-3432 Telephone: (408) 558-8500 FAX: 408 558-8300 Internet: <u>http://www.ZiLOG.com</u>

# Z8 GP<sup>™</sup> OTP MCU Family Product Specification

# Index

### **Numerics**

16-bit counter/timer circuits 44 20-pin DIP package diagram 81 20-pin SSOP package diagram 82 28-pin DIP package diagram 85 28-pin SOICpackage diagram 84 28-pin SSOP package diagram 86 40-pin DIP package diagram 87 48-pin SSOP package diagram 88 8-bit counter/timer circuits 40

## Α

absolute maximum ratings 10 AC characteristics 14 timing diagram 14 address spaces, basic 2 architecture 2 expanded register file 26

## В

basic address spaces 2 block diagram, ZLP32300 functional 3

## С

capacitance 11 characteristics AC 14 DC 11 clock 51 comparator inputs/outputs 23 configuration port 0 17 port 1 18 port 2 19 port 3 20 port 3 counter/timer 22 counter/timer 16-bit circuits 44 8-bit circuits 40 brown-out voltage/standby 62 clock 51 demodulation mode count capture flowchart 42 demodulation mode flowchart 43 EPROM selectable options 62 glitch filter circuitry 38 halt instruction 52 input circuit 38 interrupt block diagram 49 interrupt types, sources and vectors 50 oscillator configuration 51 output circuit 47 ping-pong mode 46 port configuration register 53 resets and WDT 61 SCLK circuit 56 stop instruction 52 stop mode recovery register 55 stop mode recovery register 2 59 stop mode recovery source 57 T16 demodulation mode 45 T16 transmit mode 44 T16\_OUT in modulo-N mode 45 T16 OUT in single-pass mode 45 T8 demodulation mode 41 T8 transmit mode 38 T8 OUT in modulo-N mode 41 T8 OUT in single-pass mode 41 transmit mode flowchart 39 voltage detection and flags 63 watch-dog timer mode register 60 watch-dog timer time select 61 CTR(D)01h T8 and T16 Common Functions 33