# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | Z8                                                        |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 8MHz                                                      |

| Connectivity               | -                                                         |

| Peripherals                | HLVD, POR, WDT                                            |

| Number of I/O              | 16                                                        |

| Program Memory Size        | 16KB (16K x 8)                                            |

| Program Memory Type        | OTP                                                       |

| EEPROM Size                | -                                                         |

| RAM Size                   | 237 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                 |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/zgp323las2016c |

|                            |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

This publication is subject to replacement by a later edition. To determine whether a later edition exists, or to request copies of publications, contact:

**ZiLOG Worldwide Headquarters** 532 Race Street

San Jose, CA 95126-3432 Telephone: 408.558.8500 Fax: 408.558.8300 www.zilog.com

ZiLOG is a registered trademark of ZiLOG Inc. in the United States and in other countries. All other products and/or service names mentioned herein may be trademarks of the companies with which they are associated.

#### **Document Disclaimer**

©2004 by ZiLOG, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZiLOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. Devices sold by ZiLOG, Inc. are covered by warranty and limitation of liability provisions appearing in the ZiLOG, Inc. Terms and Conditions of Sale. ZiLOG, Inc. makes no warranty of merchantability or fitness for any purpose. Except with the express written approval of ZiLOG, use of information, devices, or technology as critical components of life support systems is not authorized. No licenses are conveyed, implicitly or otherwise, by this document under any intellectual property rights.

# List of Figures

| Figure 1.  | Functional Block Diagram                        | . 3 |

|------------|-------------------------------------------------|-----|

| Figure 2.  | Counter/Timers Diagram                          | . 4 |

| Figure 3.  | 20-Pin PDIP/SOIC/SSOP/CDIP* Pin Configuration   | . 5 |

| Figure 4.  | 28-Pin PDIP/SOIC/SSOP/CDIP* Pin Configuration   | . 6 |

| Figure 5.  | 40-Pin PDIP/CDIP* Pin Configuration             | . 7 |

| Figure 6.  | 48-Pin SSOP Pin Configuration                   | . 8 |

| Figure 7.  | Test Load Diagram                               | 10  |

| Figure 8.  | AC Timing Diagram                               | 14  |

| Figure 9.  | Port 0 Configuration                            | 17  |

| Figure 10. | Port 1 Configuration                            | 18  |

|            | Port 2 Configuration                            |     |

| Figure 12. | Port 3 Configuration                            | 20  |

| Figure 13. | Port 3 Counter/Timer Output Configuration       | 22  |

| Figure 14. | Program Memory Map (32K OTP)                    | 24  |

| Figure 15. | Expanded Register File Architecture             | 26  |

| Figure 16. | Register Pointer                                | 27  |

| Figure 17. | Register Pointer—Detail                         | 29  |

| Figure 18. | Glitch Filter Circuitry                         | 38  |

| Figure 19. | Transmit Mode Flowchart                         | 39  |

| Figure 20. | 8-Bit Counter/Timer Circuits                    | 40  |

| Figure 21. | T8_OUT in Single-Pass Mode                      | 41  |

| Figure 22. | T8_OUT in Modulo-N Mode                         | 41  |

| Figure 23. | Demodulation Mode Count Capture Flowchart       | 42  |

| Figure 24. | Demodulation Mode Flowchart                     | 43  |

| Figure 25. | 16-Bit Counter/Timer Circuits                   | 44  |

| Figure 26. | T16_OUT in Single-Pass Mode                     | 45  |

| Figure 27. | T16_OUT in Modulo-N Mode                        | 45  |

| Figure 28. | Ping-Pong Mode Diagram                          | 47  |

| Figure 29. | Output Circuit                                  | 47  |

| Figure 30. | Interrupt Block Diagram                         | 49  |

| Figure 31. | Oscillator Configuration                        | 51  |

| Figure 32. | Port Configuration Register (PCON) (Write Only) | 53  |

| Figure 33. | STOP Mode Recovery Register                     | 55  |

| Figure 34. | SCLK Circuit                                    | 56  |

- Port 1: 0–3 pull-up transistors

- Port 1: 4–7 pull-up transistors

- Port 2: 0–7 pull-up transistors

- EPROM Protection

- WDT enabled at POR

- **Note:** The mask option pull-up transistor has a *typical* equivalent resistance of 200 K $\Omega$  ±50% at V<sub>CC</sub>=3 V and 450 K $\Omega$  ±50% at  $V_{CC}=2$  V.

### **General Description**

The Z8 GP<sup>TM</sup> OTP MCU Family is an OTP-based member of the MCU family of infrared microcontrollers. With 237B of general-purpose RAM and up to 32KB of OTP, ZiLOG<sup>®</sup>'s CMOS microcontrollers offer fast-executing, efficient use of memory, sophisticated interrupts, input/output bit manipulation capabilities, automated pulse generation/reception, and internal key-scan pull-up transistors.

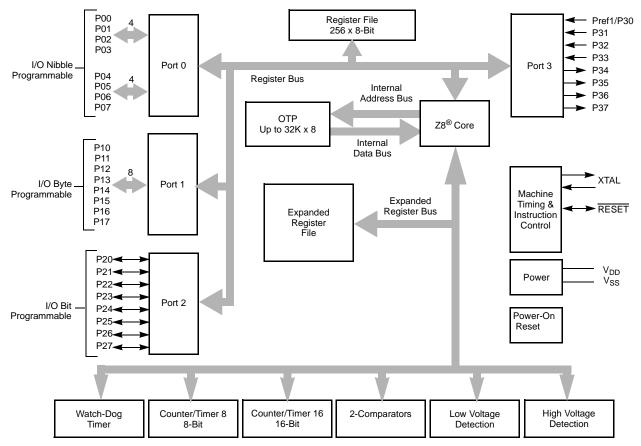

The Z8 GP<sup>TM</sup> OTP MCU Family architecture (Figure 1) is based on ZiLOG's 8-bit microcontroller core with an Expanded Register File allowing access to registermapped peripherals, input/output (I/O) circuits, and powerful counter/timer circuitry. The Z8<sup>®</sup> offers a flexible I/O scheme, an efficient register and address space structure, and a number of ancillary features that are useful in many consumer, automotive, computer peripheral, and battery-operated hand-held applications.

There are three basic address spaces available to support a wide range of configurations: Program Memory, Register File and Expanded Register File. The register file is composed of 256 Bytes (B) of RAM. It includes 4 I/O port registers, 16 control and status registers, and 236 general-purpose registers. The Expanded Register File consists of two additional register groups (F and D).

To unburden the program from coping with such real-time problems as generating complex waveforms or receiving and demodulating complex waveform/pulses, the Z8 GP OTP MCU offers a new intelligent counter/timer architecture with 8-bit and 16-bit counter/timers (see Figure 2). Also included are a large number of userselectable modes and two on-board comparators to process analog signals with separate reference voltages.

**Note:** All signals with an overline, "", are active Low. For example,  $B/\overline{W}$ , in which WORD is active Low, and  $\overline{B}/W$ , in which BYTE is active Low.

Power connections use the conventional descriptions listed in Table 2.

# Z8 GP<sup>TM</sup> OTP MCU Family Product Specification

#### Table 2. Power Connections

| Connection | Circuit         | Device          |  |

|------------|-----------------|-----------------|--|

| Power      | V <sub>CC</sub> | V <sub>DD</sub> |  |

| Ground     | GND             | V <sub>SS</sub> |  |

Note: Refer to the specific package for available pins.

#### Figure 1. Functional Block Diagram

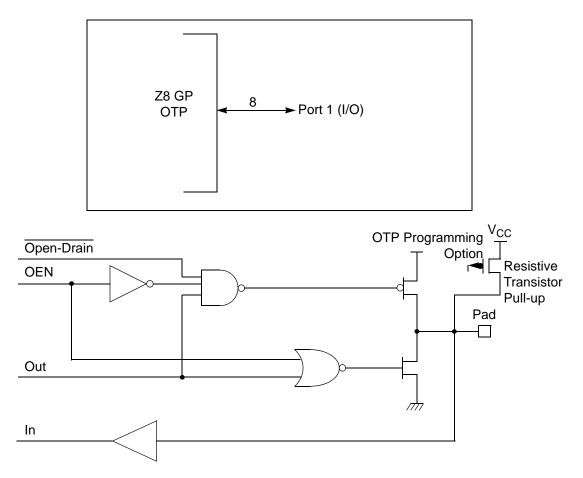

Figure 10. Port 1 Configuration

### Port 2 (P27-P20)

Port 2 is an 8-bit, bidirectional, CMOS-compatible I/O port (see Figure 11). These eight I/O lines can be independently configured under software control as inputs or outputs. Port 2 is always available for I/O operation. A mask option is available to connect eight pull-up transistors on this port. Bits programmed as outputs are globally programmed as either push-pull or open-drain. The POR resets with the eight bits of Port 2 configured as inputs.

Port 2 also has an 8-bit input OR and AND gate, which can be used to wake up the part. P20 can be programmed to access the edge-detection circuitry in demodulation mode.

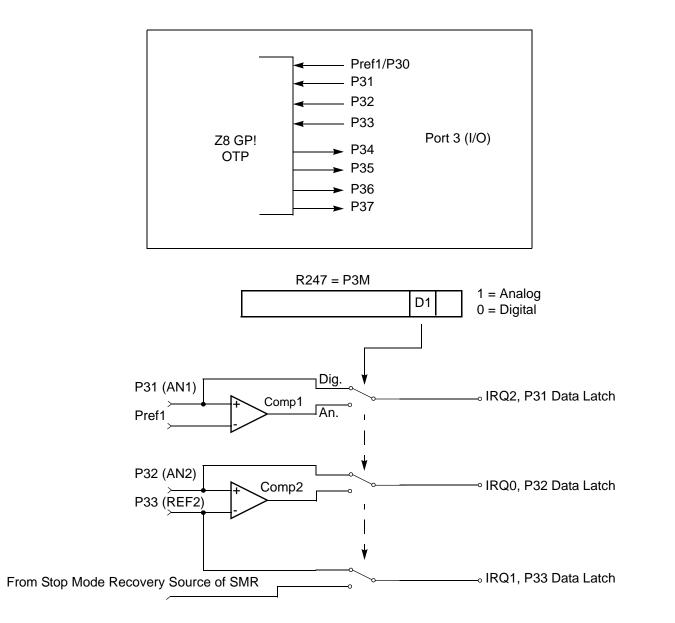

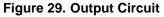

#### Figure 12. Port 3 Configuration

Two on-board comparators process analog signals on P31 and P32, with reference to the voltage on Pref1 and P33. The analog function is enabled by programming the Port 3 Mode Register (bit 1). P31 and P32 are programmable as rising, falling, or both edge triggered interrupts (IRQ register bits 6 and 7). Pref1 and P33 are the comparator reference voltage inputs. Access to the Counter Timer edgedetection circuit is through P31 or P20 (see "T8 and T16 Common Functions—

CTR1(0D)01H" on page 33). Other edge detect and IRQ modes are described in Table 11.

**Note:** Comparators are powered down by entering Stop Mode. For P31–P33 to be used in a Stop Mode Recovery (SMR) source, these inputs must be placed into digital mode.

| Pin       | I/O | Counter/Timers | Comparator | Interrupt |

|-----------|-----|----------------|------------|-----------|

| Pref1/P30 | IN  |                | RF1        |           |

| P31       | IN  | IN             | AN1        | IRQ2      |

| P32       | IN  |                | AN2        | IRQ0      |

| P33       | IN  |                | RF2        | IRQ1      |

| P34       | OUT | Т8             | AO1        |           |

| P35       | OUT | T16            |            |           |

| P36       | OUT | T8/16          |            |           |

| P37       | OUT |                | AO2        |           |

| P20       | I/O | IN             |            |           |

#### Table 11. Port 3 Pin Function Summary

>

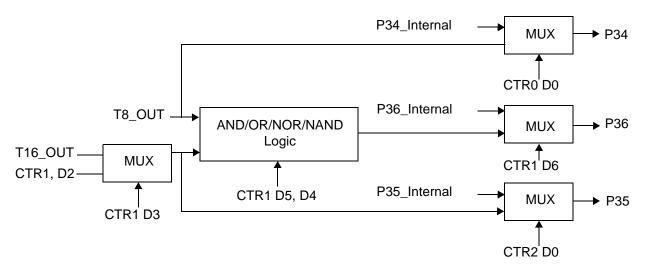

Port 3 also provides output for each of the counter/timers and the AND/OR Logic (see Figure 13). Control is performed by programming bits D5–D4 of CTR1, bit 0 of CTR0, and bit 0 of CTR2.

34

| Field             | Bit Position |     | Value | Description            |

|-------------------|--------------|-----|-------|------------------------|

| Transmit_Submode/ | 32           | R/W |       | Transmit Mode          |

| Glitch_Filter     |              |     | 00*   | Normal Operation       |

|                   |              |     | 01    | Ping-Pong Mode         |

|                   |              |     | 10    | T16_Out = 0            |

|                   |              |     | 11    | T16_Out = 1            |

|                   |              |     |       | Demodulation Mode      |

|                   |              |     | 00*   | No Filter              |

|                   |              |     | 01    | 4 SCLK Cycle           |

|                   |              |     | 10    | 8 SCLK Cycle           |

|                   |              |     | 11    | Reserved               |

| Initial_T8_Out/   | 1-           |     |       | Transmit Mode          |

| Rising Edge       |              | R/W | 0*    | T8_OUT is 0 Initially  |

|                   |              |     | 1     | T8_OUT is 1 Initially  |

|                   |              |     |       | Demodulation Mode      |

|                   |              | R   | 0*    | No Rising Edge         |

|                   |              |     | 1     | Rising Edge Detected   |

|                   |              | W   | 0     | No Effect              |

|                   |              |     | 1     | Reset Flag to 0        |

| Initial_T16_Out/  | 0            |     |       | Transmit Mode          |

| Falling_Edge      |              | R/W | 0*    | T16_OUT is 0 Initially |

|                   |              |     | 1     | T16_OUT is 1 Initially |

|                   |              |     |       | Demodulation Mode      |

|                   |              | R   | 0*    | No Falling Edge        |

|                   |              |     | 1     | Falling Edge Detected  |

|                   |              | W   | 0     | No Effect              |

|                   |              |     | 1     | Reset Flag to 0        |

#### Table 13. CTR1(0D)01H T8 and T16 Common Functions (Continued)

#### Note:

\*Default at Power-On Reset.

\*\*Default at Power-On Reset.Not reset with Stop Mode recovery.

#### Mode

If the result is 0, the counter/timers are in TRANSMIT mode; otherwise, they are in DEMODULATION mode.

#### P36\_Out/Demodulator\_Input

In TRANSMIT Mode, this bit defines whether P36 is used as a normal output pin or the combined output of T8 and T16.

In DEMODULATION Mode, this bit defines whether the input signal to the Counter/Timers is from P20 or P31.

If the input signal is from Port 31, a capture event may also generate an IRQ2 interrupt. To prevent generating an IRQ2, either disable the IRQ2 interrupt by clearing its IMR bit D2 or use P20 as the input.

ZILOG

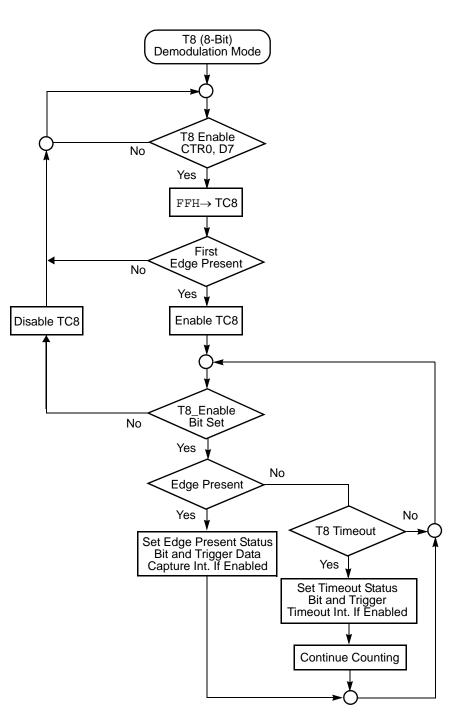

Figure 24. Demodulation Mode Flowchart

#### If D6 of CTR2 Is 1

T16 ignores the subsequent edges in the input signal and continues counting down. A timeout of T8 causes T16 to capture its current value and generate an interrupt if enabled (CTR2, D2). In this case, T16 does not reload and continues counting. If the D6 bit of CTR2 is toggled (by writing a 0 then a 1 to it), T16 captures and reloads on the next edge (rising, falling, or both depending on CTR1, D5; D4), continuing to ignore subsequent edges.

This T16 mode generally measures mark time, the length of an active carrier signal burst.

If T16 reaches 0, T16 continues counting from FFFFh. Meanwhile, a status bit (CTR2 D5) is set, and an interrupt timeout can be generated if enabled (CTR2 D1).

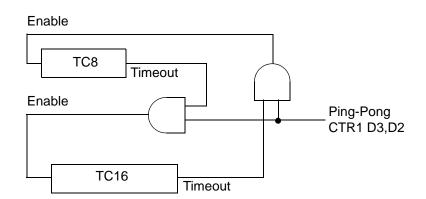

#### **Ping-Pong Mode**

This operation mode is only valid in TRANSMIT Mode. T8 and T16 must be programmed in Single-Pass mode (CTR0, D6; CTR2, D6), and Ping-Pong mode must be programmed in CTR1, D3; D2. The user can begin the operation by enabling either T8 or T16 (CTR0, D7 or CTR2, D7). For example, if T8 is enabled, T8\_OUT is set to this initial value (CTR1, D1). According to T8\_OUT's level, TC8H or TC8L is loaded into T8. After the terminal count is reached, T8 is disabled, and T16 is enabled. T16\_OUT then switches to its initial value (CTR1, D0), data from TC16H and TC16L is loaded, and T16 starts to count. After T16 reaches the terminal count, it stops, T8 is enabled again, repeating the entire cycle. Interrupts can be allowed when T8 or T16 reaches terminal control (CTR0, D1; CTR2, D1). To stop the ping-pong operation, write 00 to bits D3 and D2 of CTR1. See Figure 28.

**Note:** Enabling ping-pong operation while the counter/timers are running might cause intermittent counter/timer function. Disable the counter/timers and reset the status flags before instituting this operation.

Figure 28. Ping-Pong Mode Diagram

#### Initiating PING-PONG Mode

First, make sure both counter/timers are not running. Set T8 into Single-Pass mode (CTR0, D6), set T16 into SINGLE-PASS mode (CTR2, D6), and set the Ping-Pong mode (CTR1, D2; D3). These instructions can be in random order. Finally, start PING-PONG mode by enabling either T8 (CTR0, D7) or T16 (CTR2, D7). See Figure 29.

The initial value of T8 or T16 must not be 1. Stopping the timer and restarting the timer reloads the initial value to avoid an unknown previous value.

Figure 30. Interrupt Block Diagram

#### **Power-On Reset**

A timer circuit clocked by a dedicated on-board RC-oscillator is used for the Power-On Reset (POR) timer function. The POR time allows  $V_{DD}$  and the oscillator circuit to stabilize before instruction execution begins.

The POR timer circuit is a one-shot timer triggered by one of three conditions:

- Power Fail to Power OK status, including Waking up from V<sub>BO</sub> Standby

- Stop-Mode Recovery (if D5 of SMR = 1)

- WDT Timeout

The POR timer is 2.5 ms minimum. Bit 5 of the Stop-Mode Register determines whether the POR timer is bypassed after Stop-Mode Recovery (typical for external clock).

#### HALT Mode

This instruction turns off the internal CPU clock, but not the XTAL oscillation. The counter/timers and external interrupts IRQ0, IRQ1, IRQ2, IRQ3, IRQ4, and IRQ5 remain active. The devices are recovered by interrupts, either externally or internally generated. An interrupt request must be executed (enabled) to exit HALT Mode. After the interrupt service routine, the program continues from the instruction after HALT Mode.

#### **STOP Mode**

This instruction turns off the internal clock and external crystal oscillation, reducing the standby current to 10  $\mu$ A or less. STOP Mode is terminated only by a reset, such as WDT timeout, POR, SMR or external reset. This condition causes the processor to restart the application program at address 000CH. To enter STOP (or HALT) mode, first flush the instruction pipeline to avoid suspending execution in mid-instruction. Execute a NOP (Opcode = FFH) immediately before the appropriate sleep instruction, as follows:

#### CTR3(0D)03H

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |                                                                                                                                                  |

|----|----|----|----|----|----|----|----|--------------------------------------------------------------------------------------------------------------------------------------------------|

|    |    |    |    |    |    |    |    | Reserved<br>No effect when written<br>Always reads 11111                                                                                         |

|    |    |    |    |    |    |    |    | Sync Mode<br>0* Disable Sync Mode**<br>1 Enable Sync Mode                                                                                        |

|    |    |    |    |    |    |    |    | T <sub>8</sub> Enable<br>R 0* T <sub>8</sub> Disabled<br>R 1 T <sub>8</sub> Enabled<br>W0 Stop T <sub>8</sub><br>W1 Enable T <sub>8</sub>        |

|    |    |    |    |    |    |    |    | T <sub>16</sub> Enable<br>R 0* T <sub>16</sub> Disabled<br>R 1 T <sub>16</sub> Enabled<br>W 0 Stop T <sub>16</sub><br>W 1 Enable T <sub>16</sub> |

\* Default setting after reset. \*\* Default setting after reset. Not reset with Stop Mode recovery.

#### Figure 42. T8/T16 Control Register (0D)03H: Read/Write (Except Where Noted)

**Note:** If Sync Mode is enabled, the first pulse of T8 carrier is always synchronized with T16 (demodulated signal). It can always provide a full carrier pulse.

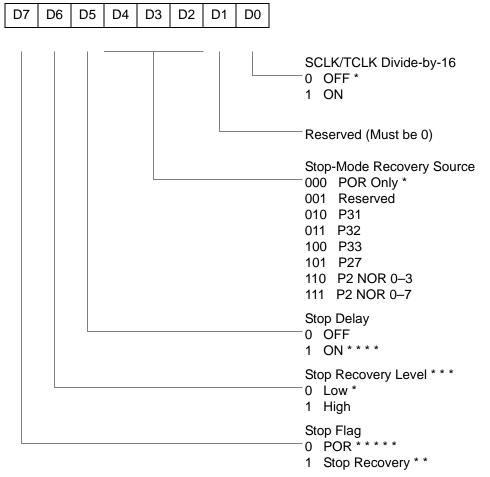

#### SMR(0F)0BH

- \* Default setting after Reset

- \* \* Set after STOP Mode Recovery

- \* \* \* At the XOR gate input

- \*\*\*\* Default setting after Reset. Must be 1 if using a crystal or resonator clock source.

- \* \* \* \* \* Default setting after Power On Reset. Not Reset with a Stop Mode recovery.

## Figure 45. Stop Mode Recovery Register ((0F)0BH: D6–D0=Write Only, D7=Read Only)

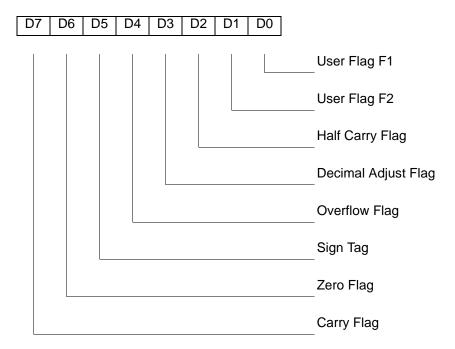

#### R252 Flags(FCH)

#### Figure 54. Flag Register (FCH: Read/Write)

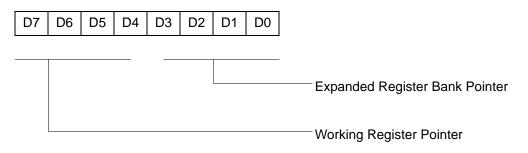

R253 RP(FDH)

Default setting after reset = 0000 0000

#### Figure 55. Register Pointer (FDH: Read/Write)

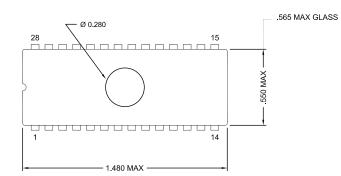

Figure 62. 28-Pin CDIP Package

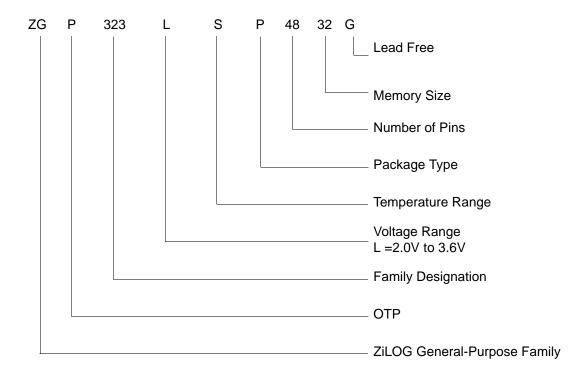

### **Ordering Information**

#### 32KB Standard Temperature: 0° to +70°C

|                | •                   |                |                     |

|----------------|---------------------|----------------|---------------------|

| Part Number    | Description         | Part Number    | Description         |

| ZGP323LSH4832C | 48-pin SSOP 32K OTP | ZGP323LSS2832C | 28-pin SOIC 32K OTP |

| ZGP323LSP4032C | 40-pin PDIP 32K OTP | ZGP323LSH2032C | 20-pin SSOP 32K OTP |

| ZGP323LSH2832C | 28-pin SSOP 32K OTP | ZGP323LSP2032C | 20-pin PDIP 32K OTP |

| ZGP323LSP2832C | 28-pin PDIP 32K OTP | ZGP323LSS2032C | 20-pin SOIC 32K OTP |

| ZGP323LSK2032E | 20-pin CDIP 32K OTP | ZGP323LSK4032E | 40-pin CDIP 32K OTP |

|                |                     | ZGP323LSK2832E | 28-pin CDIP 32K OTP |

|                |                     |                |                     |

#### 32KB Extended Temperature: -40° to +105°C

| Part Number    | Description         | Part Number    | Description         |

|----------------|---------------------|----------------|---------------------|

| ZGP323LEH4832C | 48-pin SSOP 32K OTP | ZGP323LES2832C | 28-pin SOIC 32K OTP |

| ZGP323LEP4032C | 40-pin PDIP 32K OTP | ZGP323LEH2032C | 20-pin SSOP 32K OTP |

| ZGP323LEH2832C | 28-pin SSOP 32K OTP | ZGP323LEP2032C | 20-pin PDIP 32K OTP |

| ZGP323LEP2832C | 28-pin PDIP 32K OTP | ZGP323LES2032C | 20-pin SOIC 32K OTP |

#### 32KB Automotive Temperature: -40° to +125°C

|                                                | •                   | 1              |                     |  |  |  |

|------------------------------------------------|---------------------|----------------|---------------------|--|--|--|

| Part Number                                    | Description         | Part Number    | Description         |  |  |  |

| ZGP323LAH4832C                                 | 48-pin SSOP 32K OTP | ZGP323LAS2832C | 28-pin SOIC 32K OTP |  |  |  |

| ZGP323LAP4032C                                 | 40-pin PDIP 32K OTP | ZGP323LAH2032C | 20-pin SSOP 32K OTP |  |  |  |

| ZGP323LAH2832C                                 | 28-pin SSOP 32K OTP | ZGP323LAP2032C | 20-pin PDIP 32K OTP |  |  |  |

| ZGP323LAP2832C                                 | 28-pin PDIP 32K OTP | ZGP323LAS2032C | 20-pin SOIC 32K OTP |  |  |  |

|                                                |                     |                |                     |  |  |  |

| Note: Replace C with G for Lead-Free Packaging |                     |                |                     |  |  |  |

#### Example

### **Precharacterization Product**

The product represented by this document is newly introduced and ZiLOG has not completed the full characterization of the product. The document states what ZiLOG knows about this product at this time, but additional features or nonconformance with some aspects of the document might be found, either by ZiLOG or its customers in the course of further application and characterization work. In addition, ZiLOG cautions that delivery might be uncertain at times, due to start-up yield issues.

ZiLOG, Inc.

532 Race Street San Jose, CA 95126-3432 Telephone: (408) 558-8500 FAX: 408 558-8300 Internet: <u>http://www.ZiLOG.com</u>