# E·XFL

# Zilog - ZGP323LAS2032C00TR Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                      |

|----------------------------|---------------------------------------------------------------|

| Core Processor             | Z8                                                            |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 8MHz                                                          |

| Connectivity               | -                                                             |

| Peripherals                | HLVD, POR, WDT                                                |

| Number of I/O              | 16                                                            |

| Program Memory Size        | 32KB (32K x 8)                                                |

| Program Memory Type        | OTP                                                           |

| EEPROM Size                | -                                                             |

| RAM Size                   | 237 x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                     |

| Data Converters            | -                                                             |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                            |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                |

| Supplier Device Package    | -                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/zgp323las2032c00tr |

|                            |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

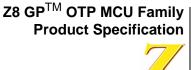

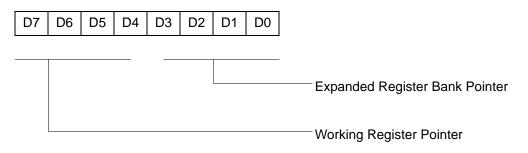

ERF (Expanded Register File). Bits 7–4 of register RP select the working register group. Bits 3–0 of register RP select the expanded register file bank.

>

**Note:** An expanded register bank is also referred to as an expanded register group (see Figure 15).

\* RP = 00: Selects Register Bank 0, Working Register Group 0

Figure 17. Register Pointer—Detail

# Stack

The internal register file is used for the stack. An 8-bit Stack Pointer SPL (R255) is used for the internal stack that resides in the general-purpose registers (R4–R239). SPH (R254) can be used as a general-purpose register.

# Timers

# T8\_Capture\_HI—HI8(D)0BH

This register holds the captured data from the output of the 8-bit Counter/Timer0. Typically, this register holds the number of counts when the input signal is 1.

| Field         | Bit Position |     | Description               |  |

|---------------|--------------|-----|---------------------------|--|

| T8_Capture_HI | [7:0]        | R/W | Captured Data - No Effect |  |

## T8\_Capture\_LO—L08(D)0AH

This register holds the captured data from the output of the 8-bit Counter/Timer0. Typically, this register holds the number of counts when the input signal is 0.

| Field         | Bit Position |     | Description               |  |

|---------------|--------------|-----|---------------------------|--|

| T8_Capture_L0 | [7:0]        | R/W | Captured Data - No Effect |  |

#### T16\_Capture\_HI—HI16(D)09H

This register holds the captured data from the output of the 16-bit Counter/ Timer16. This register holds the MS-Byte of the data.

| Field          | Bit Position |     | Description               |  |

|----------------|--------------|-----|---------------------------|--|

| T16_Capture_HI | [7:0]        | R/W | Captured Data - No Effect |  |

#### T16\_Capture\_LO—L016(D)08H

This register holds the captured data from the output of the 16-bit Counter/ Timer16. This register holds the LS-Byte of the data.

| Field          | Bit Position | Description                   |

|----------------|--------------|-------------------------------|

| T16_Capture_LO | [7:0]        | R/W Captured Data - No Effect |

#### Counter/Timer2 MS-Byte Hold Register—TC16H(D)07H

| Field       | Bit Position |     | Description |

|-------------|--------------|-----|-------------|

| T16_Data_HI | [7:0]        | R/W | Data        |

## Capture\_INT\_Mask

Set this bit to allow an interrupt when data is captured into either LO8 or HI8 upon a positive or negative edge detection in demodulation mode.

## Counter\_INT\_Mask

Set this bit to allow an interrupt when T8 has a timeout.

#### P34\_Out

This bit defines whether P34 is used as a normal output pin or the T8 output.

## T8 and T16 Common Functions—CTR1(0D)01H

This register controls the functions in common with the T8 and T16.

Table 13 lists and briefly describes the fields for this register.

| Field             | Bit Position |     | Value | Description       |

|-------------------|--------------|-----|-------|-------------------|

| Mode              | 7            | R/W | 0*    | Transmit Mode     |

|                   |              |     |       | Demodulation Mode |

| P36_Out/          | -6           | R/W |       | Transmit Mode     |

| Demodulator_Input |              |     | 0*    | Port Output       |

|                   |              |     | 1     | T8/T16 Output     |

|                   |              |     |       | Demodulation Mode |

|                   |              |     | 0     | P31               |

|                   |              |     | 1     | P20               |

| T8/T16_Logic/     | 54           | R/W |       | Transmit Mode     |

| Edge _Detect      |              |     | 00**  | AND               |

| -                 |              |     | 01    | OR                |

|                   |              |     | 10    | NOR               |

|                   |              |     | 11    | NAND              |

|                   |              |     |       | Demodulation Mode |

|                   |              |     | 00**  | Falling Edge      |

|                   |              |     | 01    | Rising Edge       |

|                   |              |     | 10    | Both Edges        |

|                   |              |     | 11    | Reserved          |

#### Table 13. CTR1(0D)01H T8 and T16 Common Functions

| Field             | Bit Position |     | Value | Description            |

|-------------------|--------------|-----|-------|------------------------|

| Transmit_Submode/ | 32           | R/W |       | Transmit Mode          |

| Glitch_Filter     |              |     | 00*   | Normal Operation       |

|                   |              |     | 01    | Ping-Pong Mode         |

|                   |              |     | 10    | T16_Out = 0            |

|                   |              |     | 11    | T16_Out = 1            |

|                   |              |     |       | Demodulation Mode      |

|                   |              |     | 00*   | No Filter              |

|                   |              |     | 01    | 4 SCLK Cycle           |

|                   |              |     | 10    | 8 SCLK Cycle           |

|                   |              |     | 11    | Reserved               |

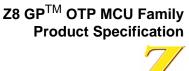

| Initial_T8_Out/   | 1-           |     |       | Transmit Mode          |

| Rising Edge       |              | R/W | 0*    | T8_OUT is 0 Initially  |

|                   |              |     | 1     | T8_OUT is 1 Initially  |

|                   |              |     |       | Demodulation Mode      |

|                   |              | R   | 0*    | No Rising Edge         |

|                   |              |     | 1     | Rising Edge Detected   |

|                   |              | W   | 0     | No Effect              |

|                   |              |     | 1     | Reset Flag to 0        |

| Initial_T16_Out/  | 0            |     |       | Transmit Mode          |

| Falling_Edge      |              | R/W | 0*    | T16_OUT is 0 Initially |

|                   |              |     | 1     | T16_OUT is 1 Initially |

|                   |              |     |       | Demodulation Mode      |

|                   |              | R   | 0*    | No Falling Edge        |

|                   |              |     | 1     | Falling Edge Detected  |

|                   |              | W   | 0     | No Effect              |

|                   |              |     | 1     | Reset Flag to 0        |

#### Table 13. CTR1(0D)01H T8 and T16 Common Functions (Continued)

#### Note:

\*Default at Power-On Reset.

\*\*Default at Power-On Reset.Not reset with Stop Mode recovery.

#### Mode

If the result is 0, the counter/timers are in TRANSMIT mode; otherwise, they are in DEMODULATION mode.

#### P36\_Out/Demodulator\_Input

In TRANSMIT Mode, this bit defines whether P36 is used as a normal output pin or the combined output of T8 and T16.

In DEMODULATION Mode, this bit defines whether the input signal to the Counter/Timers is from P20 or P31.

If the input signal is from Port 31, a capture event may also generate an IRQ2 interrupt. To prevent generating an IRQ2, either disable the IRQ2 interrupt by clearing its IMR bit D2 or use P20 as the input.

# T8/T16\_Logic/Edge \_Detect

In TRANSMIT Mode, this field defines how the outputs of T8 and T16 are combined (AND, OR, NOR, NAND).

In DEMODULATION Mode, this field defines which edge should be detected by the edge detector.

#### Transmit\_Submode/Glitch Filter

In Transmit Mode, this field defines whether T8 and T16 are in the PING-PONG mode or in independent normal operation mode. Setting this field to "NORMAL OPERATION Mode" terminates the "PING-PONG Mode" operation. When set to 10, T16 is immediately forced to a 0; a setting of 11 forces T16 to output a 1.

In DEMODULATION Mode, this field defines the width of the glitch that must be filtered out.

## Initial\_T8\_Out/Rising\_Edge

In TRANSMIT Mode, if 0, the output of T8 is set to 0 when it starts to count. If 1, the output of T8 is set to 1 when it starts to count. When the counter is not enabled and this bit is set to 1 or 0, T8\_OUT is set to the opposite state of this bit. This ensures that when the clock is enabled, a transition occurs to the initial state set by CTR1, D1.

In DEMODULATION Mode, this bit is set to 1 when a rising edge is detected in the input signal. In order to reset the mode, a 1 should be written to this location.

#### Initial\_T16 Out/Falling \_Edge

In TRANSMIT Mode, if it is 0, the output of T16 is set to 0 when it starts to count. If it is 1, the output of T16 is set to 1 when it starts to count. This bit is effective only in Normal or PING-PONG Mode (CTR1, D3; D2). When the counter is not enabled and this bit is set, T16\_OUT is set to the opposite state of this bit. This ensures that when the clock is enabled, a transition occurs to the initial state set by CTR1, D0.

In DEMODULATION Mode, this bit is set to 1 when a falling edge is detected in the input signal. In order to reset it, a 1 should be written to this location.

**Note:** Modifying CTR1 (D1 or D0) while the counters are enabled causes unpredictable output from T8/16\_OUT.

# CTR2 Counter/Timer 16 Control Register—CTR2(D)02H

Table 14 lists and briefly describes the fields for this register.

# Z i L 0 G 36

| Field            | Bit Position |     | Value | Description                    |

|------------------|--------------|-----|-------|--------------------------------|

| T16_Enable       | 7            | R   | 0*    | Counter Disabled               |

|                  |              |     | 1     | Counter Enabled                |

|                  |              | W   | 0     | Stop Counter                   |

|                  |              |     | 1     | Enable Counter                 |

| Single/Modulo-N  | -6           | R/W |       | Transmit Mode                  |

|                  |              |     | 0*    | Modulo-N                       |

|                  |              |     | 1     | Single Pass                    |

|                  |              |     |       | Demodulation Mode              |

|                  |              |     | 0     | T16 Recognizes Edge            |

|                  |              |     | 1     | T16 Does Not Recognize<br>Edge |

| Time_Out         | 5            | R   | 0*    | No Counter Timeout             |

|                  |              |     | 1     | Counter Timeout                |

|                  |              |     |       | Occurred                       |

|                  |              | W   | 0     | No Effect                      |

|                  |              |     | 1     | Reset Flag to 0                |

| T16 _Clock       | 43           | R/W | 00**  | SCLK                           |

|                  |              |     | 01    | SCLK/2                         |

|                  |              |     | 10    | SCLK/4                         |

|                  |              |     | 11    | SCLK/8                         |

| Capture_INT_Mask | 2            | R/W | 0**   | Disable Data Capture Int.      |

|                  |              |     | 1     | Enable Data Capture Int.       |

| Counter_INT_Mask | 1-           | R/W | 0     | Disable Timeout Int.           |

|                  |              |     | 1     | Enable Timeout Int.            |

| P35_Out          | 0            | R/W | 0*    | P35 as Port Output             |

|                  |              |     | 1     | T16 Output on P35              |

# Table 14. CTR2(D)02H: Counter/Timer16 Control Register

#### Note:

\*Indicates the value upon Power-On Reset.

\*\*Indicates the value upon Power-On Reset.Not reset with Stop Mode recovery.

# T16\_Enable

This field enables T16 when set to 1.

# Single/Modulo-N

In TRANSMIT Mode, when set to 0, the counter reloads the initial value when it reaches the terminal count. When set to 1, the counter stops when the terminal count is reached.

In Demodulation Mode, when set to 0, T16 captures and reloads on detection of all the edges. When set to 1, T16 captures and detects on the first edge but ignores the subsequent edges. For details, see the description of T16 Demodulation Mode on page 45.

# Time\_Out

This bit is set when T16 times out (terminal count reached). To reset the bit, write a 1 to this location.

# T16\_Clock

This bit defines the frequency of the input signal to Counter/Timer16.

## Capture\_INT\_Mask

This bit is set to allow an interrupt when data is captured into LO16 and HI16.

#### Counter\_INT\_Mask

Set this bit to allow an interrupt when T16 times out.

#### P35\_Out

This bit defines whether P35 is used as a normal output pin or T16 output.

# CTR3 T8/T16 Control Register—CTR3(D)03H

Table 15 lists and briefly describes the fields for this register. This register allows the  $T_8$  and  $T_{16}$  counters to be synchronized.

| Table 15. CTR3 | (D)03H: | T8/T16 | Control | Register |

|----------------|---------|--------|---------|----------|

|----------------|---------|--------|---------|----------|

| Field                  | Bit Position |     | Value | Description       |

|------------------------|--------------|-----|-------|-------------------|

| T <sub>16</sub> Enable | 7            | R   | 0*    | Counter Disabled  |

|                        |              | R   | 1     | Counter Enabled   |

|                        |              | W   | 0     | Stop Counter      |

|                        |              | W   | 1     | Enable Counter    |

| T <sub>8</sub> Enable  | -6           | R   | 0*    | Counter Disabled  |

| -                      |              | R   | 1     | Counter Enabled   |

|                        |              | W   | 0     | Stop Counter      |

|                        |              | W   | 1     | Enable Counter    |

| Sync Mode              | 5            | R/W | 0**   | Disable Sync Mode |

|                        |              |     | 1     | Enable Sync Mode  |

Figure 19. Transmit Mode Flowchart

# Port 0 Output Mode (D2)

Bit 2 controls the output mode of port 0. A 1 in this location sets the output to push-pull, and a 0 sets the output to open-drain.

## Stop-Mode Recovery Register (SMR)

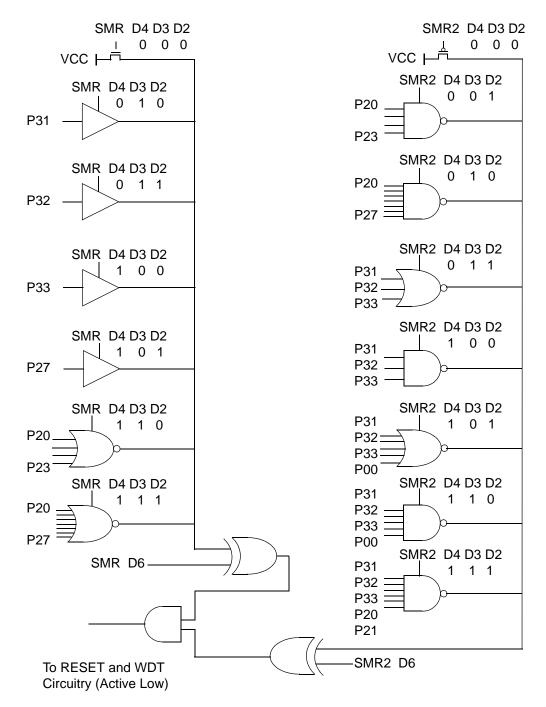

This register selects the clock divide value and determines the mode of Stop Mode Recovery (Figure 33). All bits are write only except bit 7, which is read only. Bit 7 is a flag bit that is hardware set on the condition of Stop recovery and reset by a power-on cycle. Bit 6 controls whether a low level or a high level at the XOR-gate input (Figure 35 on page 57) is required from the recovery source. Bit 5 controls the reset delay after recovery. Bits D2, D3, and D4 of the SMR register specify the source of the Stop Mode Recovery signal. Bits D0 determines if SCLK/TCLK are divided by 16 or not. The SMR is located in Bank F of the Expanded Register Group at address <code>0BH</code>.

Z8 GP<sup>TM</sup> OTP MCU Family Product Specification

Figure 35. Stop Mode Recovery Source

## Low-Voltage Detection Register—LVD(D)0Ch

**Note:** Voltage detection does not work at Stop mode. It must be disabled during Stop mode in order to reduce current.

| Field    | Bit Position |     |         | Description                    |

|----------|--------------|-----|---------|--------------------------------|

| LVD      | 76543        |     |         | Reserved<br>No Effect          |

|          | 2            | R   | 1<br>0* | HVD flag set<br>HVD flag reset |

|          | 1-           | R   | 1<br>0* | LVD flag set<br>LVD flag reset |

|          | 0            | R/W | 1<br>0* | Enable VD<br>Disable VD        |

| *Default | after POR    |     |         |                                |

**Note:** Do not modify register P01M while checking a low-voltage condition. Switching noise of both ports 0 and 1 together might trigger the LVD flag.

#### **Voltage Detection and Flags**

The Voltage Detection register (LVD, register 0CH at the expanded register bank 0Dh) offers an option of monitoring the V<sub>CC</sub> voltage. The Voltage Detection is enabled when bit 0 of LVD register is set. Once Voltage Detection is enabled, the the V<sub>CC</sub> level is monitored in real time. The flags in the LVD register valid 20uS after Voltage Detection is enabled. The HVD flag (bit 2 of the LVD register) is set only if V<sub>CC</sub> is higher than V<sub>HVD</sub>. The LVD flag (bit 1 of the LVD register) is set only if V<sub>CC</sub> is lower than the V<sub>LVD</sub>. When Voltage Detection is enabled, the LVD flag also triggers IRQ5. The IRQ bit 5 latches the low voltage condition until it is cleared by instructions or reset. The IRQ5 interrupt is served if it is enabled in the IMR register. Otherwise, bit 5 of IRQ register is latched as a flag only.

**Notes:** If it is necessary to receive an LVD interrupt upon power-up at an operating voltage lower than the low battery detect threshold, enable interrupts using the Enable Interrupt instruction (EI) prior to enabling the voltage detection.

**Notes:** Take care in differentiating the Transmit Mode from Demodulation Mode. Depending on which of these two modes is operating, the CTR1 bit has different functions.

Changing from one mode to another cannot be performed without disabling the counter/timers.

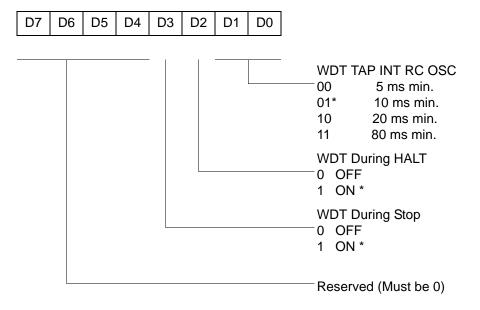

## WDTMR(0F)0FH

\* Default setting after reset

Figure 47. Watch-Dog Timer Register ((0F) 0FH: Write Only)

# **Standard Control Registers**

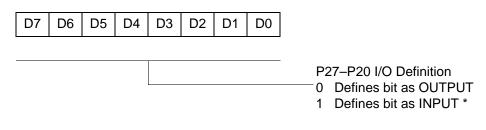

#### R246 P2M(F6H)

\* Default setting after reset

#### Figure 48. Port 2 Mode Register (F6H: Write Only)

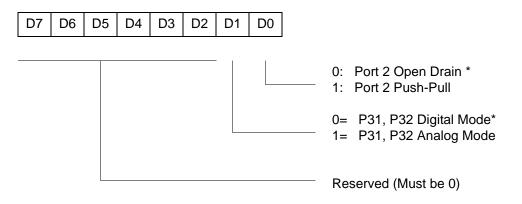

# R247 P3M(F7H)

\* Default setting after reset. Not reset with Stop Mode recovery.

Figure 49. Port 3 Mode Register (F7H: Write Only)

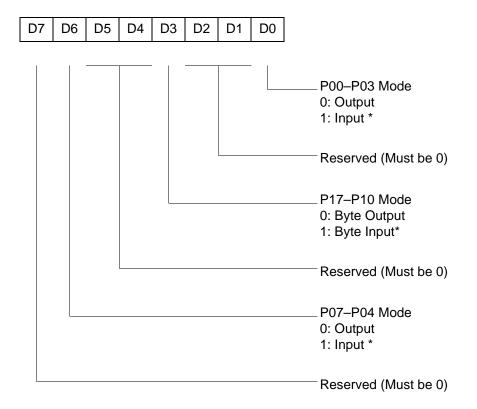

#### R248 P01M(F8H)

\* Default setting after reset; only P00, P01 and P07 are available in 20-pin configurations.

Figure 50. Port 0 and 1 Mode Register (F8H: Write Only)

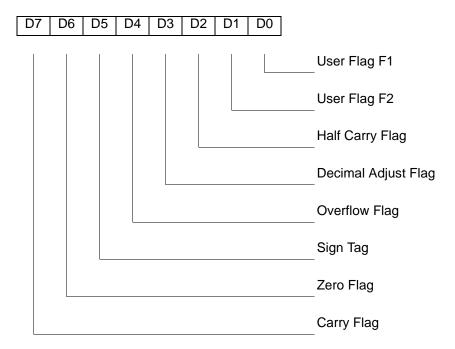

## R252 Flags(FCH)

#### Figure 54. Flag Register (FCH: Read/Write)

R253 RP(FDH)

Default setting after reset = 0000 0000

#### Figure 55. Register Pointer (FDH: Read/Write)

Z8 GP<sup>™</sup> OTP MCU Family Product Specification

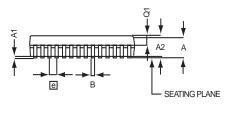

INCH

NOM

0.073

0.005

0.068

0.006

0.402

0.209

0.307

0.030

0.0256 TYP

MAX

0.078

0.008

0.070

0.015

0.008

0.407

0.212

0.311

0.037

| 0-8° |

|------|

DETAIL 'A'

SYMBOL

А

A1

A2

В

С

D

Е

е

Н

L

MIN

1.73

0.05

1.68

0.25

0.09

10.07

5.20

7.65

0.63

CONTROLLING DIMENSIONS: MM LEADS ARE COPLANAR WITHIN .004 INCHES.

MILLIMETER

NOM

1.86

0.13

1.73

\_

10.20

5.30

0.65 TYP

7.80

0.75

MAX

1.99

0.21

1.78

0.38

0.20

10.33

5.38

7.90

0.95

MIN

0.068

0.002

0.066

0.010

0.004

0.397

0.205

0.301

0.025

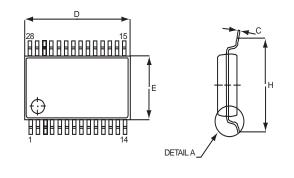

Figure 65. 28-Pin SSOP Package Diagram

For fast results, contact your local ZiLOG sales office for assistance in ordering the part desired.

# Codes

ZG = ZiLOG General Purpose Family

P = OTP

- 323 = Family Designation

- L = Voltage Range

2V to 3.6V

T = Temperature Range:

S = 0 to 70 degrees C (Standard)

- E = -40 to +105 degrees C (Extended)

- A = -40 to +125 degrees C (Automotive)

- P = Package Type:

- K = Windowed Cerdip

- P = PDIP

- H = SSOP

- S = SOIC

- ## = Number of Pins

- CC = Memory Size

- M = Packaging Options

- C = Non Lead-Free

- G = Lead-Free

- E = CDIP

Z8 GP<sup>™</sup> OTP MCU Family Product Specification

# Μ

memory, program 23 modulo-N mode T16\_OUT 45 T8\_OUT 41

# 0

oscillator configuration 51 output circuit, counter/timer 47

# Ρ

package information 20-pin DIP package diagram 81 20-pin SSOP package diagram 82 28-pin DIP package diagram 85 28-pin SOIC package diagram 84 28-pin SSOP package diagram 86 40-pin DIP package diagram 87 48-pin SSOP package diagram 88 pin configuration 20-pin DIP/SOIC/SSOP 5 28-pin DIP/SOIC/SSOP 6 40- and 48-pin 8 40-pin DIP 7 48-pin SSOP 8 pin functions port 0 (P07 - P00) 16 port 0 (P17 - P10) 17 port 0 configuration 17 port 1 configuration 18 port 2 (P27 - P20) 18 port 2 (P37 - P30) 19 port 2 configuration 19 port 3 configuration 20 port 3 counter/timer configuration 22 reset) 23 XTAL1 (time-based input 16 XTAL2 (time-based output) 16 ping-pong mode 46 port 0 configuration 17 port 0 pin function 16

port 1 configuration 18 port 1 pin function 17 port 2 configuration 19 port 2 pin function 18 port 3 configuration 20 port 3 pin function 19 port 3counter/timer configuration 22 port configuration register 53 power connections 3 power supply 5 precharacterization product 95 program memory 23 map 24

# R

ratings, absolute maximum 10 register 59 CTR(D)01h 33 CTR0(D)00h 31 CTR2(D)02h 35 CTR3(D)03h 37 flag 78 HI16(D)09h 30 HI8(D)0Bh 30 interrupt priority 76 interrupt request 77 interruptmask 77 L016(D)08h 30 L08(D)0Ah 30 LVD(D)0Ch 63 pointer 78 port 0 and 1 75 port 2 configuration 73 port 3 mode 74 port configuration 53, 73 SMR2(F)0Dh 38 stack pointer high 79 stack pointer low 79 stop mode recovery 55 stop mode recovery 2 59 stop-mode recovery 71 stop-mode recovery 2 72 T16 control 67