#### Zilog - ZGP323LAS2832C Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | Z8                                                        |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 8MHz                                                      |

| Connectivity               | -                                                         |

| Peripherals                | HLVD, POR, WDT                                            |

| Number of I/O              | 24                                                        |

| Program Memory Size        | 32KB (32K x 8)                                            |

| Program Memory Type        | OTP                                                       |

| EEPROM Size                |                                                           |

| RAM Size                   | 237 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                 |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

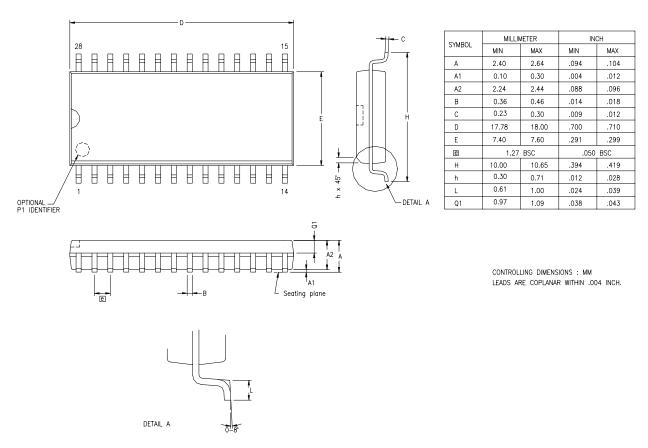

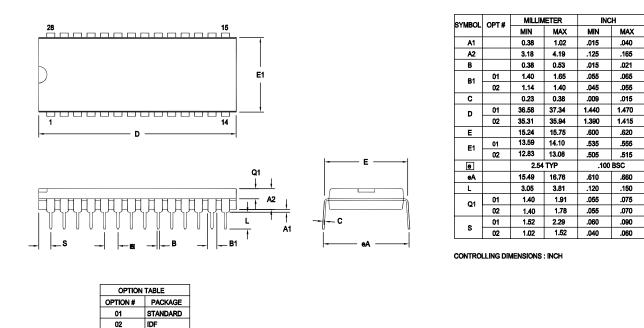

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/zgp323las2832c |

|                            |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Z8 GP<sup>TM</sup> OTP MCU Family Product Specification

## List of Tables

| Table 1.  | Features                                       |

|-----------|------------------------------------------------|

| Table 2.  | Power Connections                              |

| Table 3.  | 20-Pin PDIP/SOIC/SSOP/CDIP* Pin Identification |

| Table 4.  | 28-Pin PDIP/SOIC/SSOP/CDIP* Pin Identification |

| Table 5.  | 40- and 48-Pin Configuration 8                 |

| Table 6.  | Absolute Maximum Ratings 10                    |

| Table 7.  | Capacitance                                    |

| Table 8.  | DC Characteristics 11                          |

| Table 9.  | EPROM/OTP Characteristics 13                   |

| Table 10. | AC Characteristics 15                          |

| Table 11. | Port 3 Pin Function Summary 21                 |

| Table 12. | CTR0(D)00H Counter/Timer8 Control Register 31  |

| Table 13. | CTR1(0D)01H T8 and T16 Common Functions        |

| Table 14. | CTR2(D)02H: Counter/Timer16 Control Register   |

| Table 15. | CTR3 (D)03H: T8/T16 Control Register 37        |

| Table 16. | Interrupt Types, Sources, and Vectors          |

| Table 17. | IRQ Register 50                                |

| Table 18. | SMR2(F)0DH:Stop Mode Recovery Register 2* 56   |

| Table 19. | Stop Mode Recovery Source 58                   |

| Table 20. | Watch-Dog Timer Time Select 61                 |

| Table 21. | EPROM Selectable Options 62                    |

- Port 1: 0–3 pull-up transistors

- Port 1: 4–7 pull-up transistors

- Port 2: 0–7 pull-up transistors

- EPROM Protection

- WDT enabled at POR

- **Note:** The mask option pull-up transistor has a *typical* equivalent resistance of 200 K $\Omega$  ±50% at V<sub>CC</sub>=3 V and 450 K $\Omega$  ±50% at  $V_{CC}=2$  V.

## **General Description**

The Z8 GP<sup>TM</sup> OTP MCU Family is an OTP-based member of the MCU family of infrared microcontrollers. With 237B of general-purpose RAM and up to 32KB of OTP, ZiLOG<sup>®</sup>'s CMOS microcontrollers offer fast-executing, efficient use of memory, sophisticated interrupts, input/output bit manipulation capabilities, automated pulse generation/reception, and internal key-scan pull-up transistors.

The Z8 GP<sup>TM</sup> OTP MCU Family architecture (Figure 1) is based on ZiLOG's 8-bit microcontroller core with an Expanded Register File allowing access to registermapped peripherals, input/output (I/O) circuits, and powerful counter/timer circuitry. The Z8<sup>®</sup> offers a flexible I/O scheme, an efficient register and address space structure, and a number of ancillary features that are useful in many consumer, automotive, computer peripheral, and battery-operated hand-held applications.

There are three basic address spaces available to support a wide range of configurations: Program Memory, Register File and Expanded Register File. The register file is composed of 256 Bytes (B) of RAM. It includes 4 I/O port registers, 16 control and status registers, and 236 general-purpose registers. The Expanded Register File consists of two additional register groups (F and D).

To unburden the program from coping with such real-time problems as generating complex waveforms or receiving and demodulating complex waveform/pulses, the Z8 GP OTP MCU offers a new intelligent counter/timer architecture with 8-bit and 16-bit counter/timers (see Figure 2). Also included are a large number of userselectable modes and two on-board comparators to process analog signals with separate reference voltages.

**Note:** All signals with an overline, "", are active Low. For example,  $B/\overline{W}$ , in which WORD is active Low, and  $\overline{B}/W$ , in which BYTE is active Low.

Power connections use the conventional descriptions listed in Table 2.

|       |             | $\bigcirc$ |                |

|-------|-------------|------------|----------------|

| NC    |             |            | 40 □ NC        |

| P25   |             |            | 39 🗖 P24       |

| P26   |             |            | 38 🗖 P23       |

| P27   | □ 4         |            | 37 🗖 P22       |

| P04   | □ 5         |            | 36 🗖 P21       |

| P05   | □ 6         | 40-Pin     | 35 🗖 P20       |

| P06   | <b>–</b> 7  | PDIP       | 34 🗖 P03       |

| P14   | □ 8         | CDIP*      | 33 🗖 P13       |

| P15   | □ 9         | ODI        | 32 🗖 P12       |

| P07   | <b>1</b> 0  |            | 31 🗖 VSS       |

| VDD   | <b>–</b> 11 |            | 30 🗖 P02       |

| P16   | <b>1</b> 2  |            | 39 🗖 P11       |

| P17   | □ 13        |            | 28 🗖 P10       |

| XTAL2 | □ 14        |            | 27 🗖 P01       |

| XTAL1 | □ 15        |            | 26 🗖 P00       |

| P31   | <b>1</b> 6  |            | 25 🗖 Pref1/P30 |

| P32   | 17          |            | 24 🗖 P36       |

| P33   | <b>1</b> 8  |            | 23 🗖 P37       |

| P34   | □ 19        |            | 22 🗖 P35       |

| NC    | 20          |            | 21 🗖 RESET     |

|       |             |            |                |

#### Figure 5. 40-Pin PDIP/CDIP\* Pin Configuration

**Note:** \*Windowed Cerdip. These units are intended to be used for engineering code development only. ZiLOG does not recommend/guarantee this package for production use.

Z8 GP<sup>™</sup> OTP MCU Family Product Specification

11

Zilog

## Capacitance

Table 7 lists the capacitances.

#### Table 7. Capacitance

| Parameter                                                                                      | Maximum |  |  |  |  |

|------------------------------------------------------------------------------------------------|---------|--|--|--|--|

| Input capacitance                                                                              | 12pF    |  |  |  |  |

| Output capacitance                                                                             | 12pF    |  |  |  |  |

| I/O capacitance                                                                                | 12pF    |  |  |  |  |

| Note: $T_A = 25^{\circ}$ C, $V_{CC} = GND = 0$ V, f = 1.0 MHz, unmeasured pins returned to GND |         |  |  |  |  |

## **DC Characteristics**

|                     |                                             |                 | T <sub>A</sub> = 0°C to +70°C |     |                          |          |                                                            |              |

|---------------------|---------------------------------------------|-----------------|-------------------------------|-----|--------------------------|----------|------------------------------------------------------------|--------------|

| Symbol              | Parameter                                   | V <sub>CC</sub> | Min                           | Тур | Max                      | Units    | Conditions                                                 | Notes        |

| V <sub>CC</sub>     | Supply Voltage                              |                 | 2.0                           |     | 3.6                      | V        | See Note 5                                                 | 5            |

| V <sub>CH</sub>     | Clock Input High<br>Voltage                 | 2.0-3.6         | 0.8                           |     | V <sub>CC</sub> +0.3     | V        | Driven by External<br>Clock Generator                      |              |

| V <sub>CL</sub>     | Clock Input Low<br>Voltage                  | 2.0-3.6         | V <sub>SS</sub> -0.3          |     | 0.5                      | V        | Driven by External<br>Clock Generator                      |              |

| V <sub>IH</sub>     | Input High Voltage                          | 2.0-3.6         | 0.7 V <sub>CC</sub>           |     | V <sub>CC</sub> +0.3     | V        |                                                            |              |

| V <sub>IL</sub>     | Input Low Voltage                           | 2.0-3.6         | V <sub>SS</sub> -0.3          |     | 0.2 V <sub>CC</sub>      | V        |                                                            |              |

| V <sub>OH1</sub>    | Output High Voltage                         | 2.0-3.6         | V <sub>CC</sub> -0.4          |     |                          | V        | I <sub>OH</sub> = -0.5mA                                   |              |

| V <sub>OH2</sub>    | Output High Voltage<br>(P36, P37, P00, P01) | 2.0-3.6         | V <sub>CC</sub> -0.8          |     |                          | V        | I <sub>OH</sub> = -7mA                                     |              |

| V <sub>OL1</sub>    | Output Low Voltage                          | 2.0-3.6         |                               |     | 0.4                      | V        | $I_{OL} = 1.0 \text{mA}$<br>$I_{OL} = 4.0 \text{mA}$       |              |

| V <sub>OL2</sub>    | Output Low Voltage<br>(P00, P01, P36, P37)  | 2.0-3.6         |                               |     | 0.8                      | V        | I <sub>OL</sub> = 10mA                                     |              |

| V <sub>OFFSET</sub> | Comparator Input<br>Offset Voltage          | 2.0-3.6         |                               |     | 25                       | mV       |                                                            |              |

| V <sub>REF</sub>    | Comparator<br>Reference<br>Voltage          | 2.0-3.6         | 0                             |     | V <sub>DD</sub><br>-1.75 | V        |                                                            |              |

| ۱ <sub>IL</sub>     | Input Leakage                               | 2.0-3.6         | -1                            |     | 1                        | μΑ       | V <sub>IN</sub> = 0V, V <sub>CC</sub><br>Pull-ups disabled |              |

| IOL                 | Output Leakage                              | 2.0-3.6         | -1                            |     | 1                        | μΑ       | $V_{IN} = 0V, V_{CC}$                                      |              |

| ICC                 | Supply Current                              | 2.0<br>3.6      |                               |     | 10<br>15                 | mA<br>mA | at 8.0 MHz<br>at 8.0 MHz                                   | 1, 2<br>1, 2 |

13

#### Table 9. EPROM/OTP Characteristics

| Symbol | Parameter                  | Min. | Тур. | Max. | Unit    | Notes |

|--------|----------------------------|------|------|------|---------|-------|

|        | Erase Time                 | 15   |      |      | Minutes | 1,3   |

|        | Data Retention @ use years |      | 10   |      | Years   | 2     |

|        | Program/Erase Endurance    | 25   |      |      | Cycles  | 1     |

Notes:

1. For windowed cerdip package only.

2. Standard: 0°C to 70°C; Extended: -40°C to +105°C; Automotive: -40°C to +125°C. Determined using the Arrhenius model, which is an industry standard for estimating data retention of floating gate technologies:

AF = exp[(Ea/k)\*(1/Tuse - 1/TStress)] Where: Ea is the intrinsic activation energy (eV; typ. 0.8) k is Boltzman's constant (8.67 x 10-5 eV/°K) °K = -273.16°C Tuse = Use Temperature in °K TStress = Stress Temperature in °K 3. At a stable UV Lamp output of 20mW/CM<sup>2</sup>

### **Pin Functions**

#### XTAL1 Crystal 1 (Time-Based Input)

This pin connects a parallel-resonant crystal or ceramic resonator to the on-chip oscillator input. Additionally, an optional external single-phase clock can be coded to the on-chip oscillator input.

#### XTAL2 Crystal 2 (Time-Based Output)

This pin connects a parallel-resonant crystal or ceramic resonant to the on-chip oscillator output.

#### Port 0 (P07-P00)

Port 0 is an 8-bit, bidirectional, CMOS-compatible port. These eight I/O lines are configured under software control as a nibble I/O port. The output drivers are push-pull or open-drain controlled by bit D2 in the PCON register.

If one or both nibbles are needed for I/O operation, they must be configured by writing to the Port 0 mode register. After a hardware reset, Port 0 is configured as an input port.

An optional pull-up transistor is available as a mask option on all Port 0 bits with nibble select.

**Notes:** Internal pull-ups are disabled on any given pin or group of port pins when programmed into output mode.

The Port 0 direction is reset to be input following an SMR.

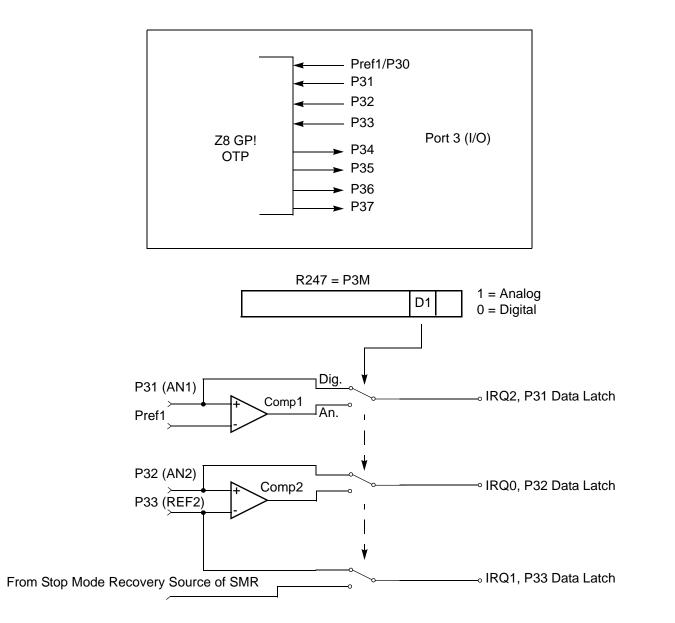

#### Figure 12. Port 3 Configuration

Two on-board comparators process analog signals on P31 and P32, with reference to the voltage on Pref1 and P33. The analog function is enabled by programming the Port 3 Mode Register (bit 1). P31 and P32 are programmable as rising, falling, or both edge triggered interrupts (IRQ register bits 6 and 7). Pref1 and P33 are the comparator reference voltage inputs. Access to the Counter Timer edgedetection circuit is through P31 or P20 (see "T8 and T16 Common Functions—

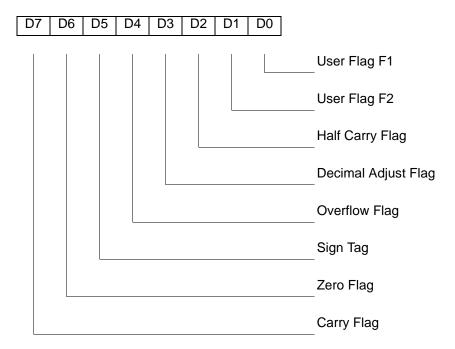

ERF (Expanded Register File). Bits 7–4 of register RP select the working register group. Bits 3–0 of register RP select the expanded register file bank.

>

**Note:** An expanded register bank is also referred to as an expanded register group (see Figure 15).

#### Capture\_INT\_Mask

Set this bit to allow an interrupt when data is captured into either LO8 or HI8 upon a positive or negative edge detection in demodulation mode.

#### Counter\_INT\_Mask

Set this bit to allow an interrupt when T8 has a timeout.

#### P34\_Out

This bit defines whether P34 is used as a normal output pin or the T8 output.

#### T8 and T16 Common Functions—CTR1(0D)01H

This register controls the functions in common with the T8 and T16.

Table 13 lists and briefly describes the fields for this register.

| Field             | Bit Position |     | Value | Description       |

|-------------------|--------------|-----|-------|-------------------|

| Mode              | 7            | R/W | 0*    | Transmit Mode     |

|                   |              |     |       | Demodulation Mode |

| P36_Out/          | -6           | R/W |       | Transmit Mode     |

| Demodulator_Input |              |     | 0*    | Port Output       |

|                   |              |     | 1     | T8/T16 Output     |

|                   |              |     |       | Demodulation Mode |

|                   |              |     | 0     | P31               |

|                   |              |     | 1     | P20               |

| T8/T16_Logic/     | 54           | R/W |       | Transmit Mode     |

| Edge _Detect      |              |     | 00**  | AND               |

| -                 |              |     | 01    | OR                |

|                   |              |     | 10    | NOR               |

|                   |              |     | 11    | NAND              |

|                   |              |     |       | Demodulation Mode |

|                   |              |     | 00**  | Falling Edge      |

|                   |              |     | 01    | Rising Edge       |

|                   |              |     | 10    | Both Edges        |

|                   |              |     | 11    | Reserved          |

#### Table 13. CTR1(0D)01H T8 and T16 Common Functions

37

In Demodulation Mode, when set to 0, T16 captures and reloads on detection of all the edges. When set to 1, T16 captures and detects on the first edge but ignores the subsequent edges. For details, see the description of T16 Demodulation Mode on page 45.

#### Time\_Out

This bit is set when T16 times out (terminal count reached). To reset the bit, write a 1 to this location.

#### T16\_Clock

This bit defines the frequency of the input signal to Counter/Timer16.

#### Capture\_INT\_Mask

This bit is set to allow an interrupt when data is captured into LO16 and HI16.

#### Counter\_INT\_Mask

Set this bit to allow an interrupt when T16 times out.

#### P35\_Out

This bit defines whether P35 is used as a normal output pin or T16 output.

#### CTR3 T8/T16 Control Register—CTR3(D)03H

Table 15 lists and briefly describes the fields for this register. This register allows the  $T_8$  and  $T_{16}$  counters to be synchronized.

| Table 15. CTR3 | (D)03H: | T8/T16 | Control | Register |

|----------------|---------|--------|---------|----------|

|----------------|---------|--------|---------|----------|

| Field                  | Bit Position |     | Value | Description       |

|------------------------|--------------|-----|-------|-------------------|

| T <sub>16</sub> Enable | 7            | R   | 0*    | Counter Disabled  |

|                        |              | R   | 1     | Counter Enabled   |

|                        |              | W   | 0     | Stop Counter      |

|                        |              | W   | 1     | Enable Counter    |

| T <sub>8</sub> Enable  | -6           | R   | 0*    | Counter Disabled  |

| -                      |              | R   | 1     | Counter Enabled   |

|                        |              | W   | 0     | Stop Counter      |

|                        |              | W   | 1     | Enable Counter    |

| Sync Mode              | 5            | R/W | 0**   | Disable Sync Mode |

|                        |              |     | 1     | Enable Sync Mode  |

**Note:** The letter h denotes hexadecimal values.

Transition from 0 to FFh is not a timeout condition.

**Caution:** Using the same instructions for stopping the counter/timers and setting the status bits is not recommended.

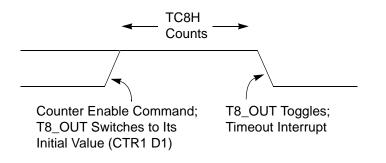

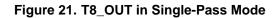

Two successive commands are necessary. First, the counter/timers must be stopped. Second, the status bits must be reset. These commands are required because it takes one counter/timer clock interval for the initiated event to actually occur. See Figure 21 and Figure 22.

Figure 22. T8\_OUT in Modulo-N Mode

#### **T8 Demodulation Mode**

The user must program TC8L and TC8H to FFH. After T8 is enabled, when the first edge (rising, falling, or both depending on CTR1, D5; D4) is detected, it starts to count down. When a subsequent edge (rising, falling, or both depending on CTR1, D5; D4) is detected during counting, the current value of T8 is complemented and put into one of the capture registers. If it is a positive edge, data is put

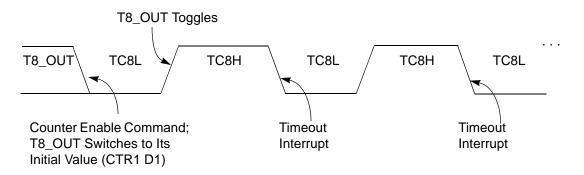

Figure 28. Ping-Pong Mode Diagram

#### Initiating PING-PONG Mode

First, make sure both counter/timers are not running. Set T8 into Single-Pass mode (CTR0, D6), set T16 into SINGLE-PASS mode (CTR2, D6), and set the Ping-Pong mode (CTR1, D2; D3). These instructions can be in random order. Finally, start PING-PONG mode by enabling either T8 (CTR0, D7) or T16 (CTR2, D7). See Figure 29.

The initial value of T8 or T16 must not be 1. Stopping the timer and restarting the timer reloads the initial value to avoid an unknown previous value.

#### **During PING-PONG Mode**

The enable bits of T8 and T16 (CTR0, D7; CTR2, D7) are set and cleared alternately by hardware. The timeout bits (CTR0, D5; CTR2, D5) are set every time the counter/timers reach the terminal count.

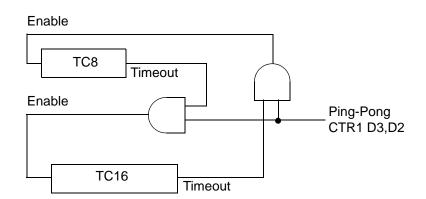

#### **Timer Output**

The output logic for the timers is illustrated in Figure 29. P34 is used to output T8-OUT when D0 of CTR0 is set. P35 is used to output the value of TI6-OUT when D0 of CTR2 is set. When D6 of CTR1 is set, P36 outputs the logic combination of T8-OUT and T16-OUT determined by D5 and D4 of CTR1.

#### Interrupts

The Z8 GP<sup>TM</sup> OTP MCU Family features six different interrupts (Table 16). The interrupts are maskable and prioritized (Figure 30). The six sources are divided as follows: three sources are claimed by Port 3 lines P33–P31, two by the counter/ timers (Table 16) and one for low voltage detection. The Interrupt Mask Register (globally or individually) enables or disables the six interrupt requests.

The source for IRQ is determined by bit 1 of the Port 3 mode register (P3M). When in digital mode, Pin P33 is the source. When in analog mode the output of the Stop mode recovery source logic is used as the source for the interrupt. See Figure 35, Stop Mode Recovery Source, on page 57.

#### **Power-On Reset**

A timer circuit clocked by a dedicated on-board RC-oscillator is used for the Power-On Reset (POR) timer function. The POR time allows  $V_{DD}$  and the oscillator circuit to stabilize before instruction execution begins.

The POR timer circuit is a one-shot timer triggered by one of three conditions:

- Power Fail to Power OK status, including Waking up from V<sub>BO</sub> Standby

- Stop-Mode Recovery (if D5 of SMR = 1)

- WDT Timeout

The POR timer is 2.5 ms minimum. Bit 5 of the Stop-Mode Register determines whether the POR timer is bypassed after Stop-Mode Recovery (typical for external clock).

#### HALT Mode

This instruction turns off the internal CPU clock, but not the XTAL oscillation. The counter/timers and external interrupts IRQ0, IRQ1, IRQ2, IRQ3, IRQ4, and IRQ5 remain active. The devices are recovered by interrupts, either externally or internally generated. An interrupt request must be executed (enabled) to exit HALT Mode. After the interrupt service routine, the program continues from the instruction after HALT Mode.

#### **STOP Mode**

This instruction turns off the internal clock and external crystal oscillation, reducing the standby current to 10  $\mu$ A or less. STOP Mode is terminated only by a reset, such as WDT timeout, POR, SMR or external reset. This condition causes the processor to restart the application program at address 000CH. To enter STOP (or HALT) mode, first flush the instruction pipeline to avoid suspending execution in mid-instruction. Execute a NOP (Opcode = FFH) immediately before the appropriate sleep instruction, as follows:

#### Low-Voltage Detection Register—LVD(D)0Ch

**Note:** Voltage detection does not work at Stop mode. It must be disabled during Stop mode in order to reduce current.

| Field    | Bit Position |     |         | Description                    |

|----------|--------------|-----|---------|--------------------------------|

| LVD      | 76543        |     |         | Reserved<br>No Effect          |

|          | 2            | R   | 1<br>0* | HVD flag set<br>HVD flag reset |

|          | 1-           | R   | 1<br>0* | LVD flag set<br>LVD flag reset |

|          | 0            | R/W | 1<br>0* | Enable VD<br>Disable VD        |

| *Default | after POR    |     |         |                                |

**Note:** Do not modify register P01M while checking a low-voltage condition. Switching noise of both ports 0 and 1 together might trigger the LVD flag.

#### **Voltage Detection and Flags**

The Voltage Detection register (LVD, register 0CH at the expanded register bank 0Dh) offers an option of monitoring the V<sub>CC</sub> voltage. The Voltage Detection is enabled when bit 0 of LVD register is set. Once Voltage Detection is enabled, the the V<sub>CC</sub> level is monitored in real time. The flags in the LVD register valid 20uS after Voltage Detection is enabled. The HVD flag (bit 2 of the LVD register) is set only if V<sub>CC</sub> is higher than V<sub>HVD</sub>. The LVD flag (bit 1 of the LVD register) is set only if V<sub>CC</sub> is lower than the V<sub>LVD</sub>. When Voltage Detection is enabled, the LVD flag also triggers IRQ5. The IRQ bit 5 latches the low voltage condition until it is cleared by instructions or reset. The IRQ5 interrupt is served if it is enabled in the IMR register. Otherwise, bit 5 of IRQ register is latched as a flag only.

**Notes:** If it is necessary to receive an LVD interrupt upon power-up at an operating voltage lower than the low battery detect threshold, enable interrupts using the Enable Interrupt instruction (EI) prior to enabling the voltage detection.

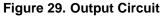

#### R252 Flags(FCH)

#### Figure 54. Flag Register (FCH: Read/Write)

R253 RP(FDH)

Default setting after reset = 0000 0000

#### Figure 55. Register Pointer (FDH: Read/Write)

Figure 63. 28-Pin SOIC Package Diagram

## Z8 GP<sup>™</sup> OTP MCU Family Product Specification

Note: ZILOG supplies both options for production. Component layout PCB design should cover bigger option 01.

Figure 64. 28-Pin PDIP Package Diagram

## **Ordering Information**

#### 32KB Standard Temperature: 0° to +70°C

|                | •                   |                |                     |

|----------------|---------------------|----------------|---------------------|

| Part Number    | Description         | Part Number    | Description         |

| ZGP323LSH4832C | 48-pin SSOP 32K OTP | ZGP323LSS2832C | 28-pin SOIC 32K OTP |

| ZGP323LSP4032C | 40-pin PDIP 32K OTP | ZGP323LSH2032C | 20-pin SSOP 32K OTP |

| ZGP323LSH2832C | 28-pin SSOP 32K OTP | ZGP323LSP2032C | 20-pin PDIP 32K OTP |

| ZGP323LSP2832C | 28-pin PDIP 32K OTP | ZGP323LSS2032C | 20-pin SOIC 32K OTP |

| ZGP323LSK2032E | 20-pin CDIP 32K OTP | ZGP323LSK4032E | 40-pin CDIP 32K OTP |

|                |                     | ZGP323LSK2832E | 28-pin CDIP 32K OTP |

|                |                     |                |                     |

#### 32KB Extended Temperature: -40° to +105°C

| Part Number    | Description         | Part Number    | Description         |

|----------------|---------------------|----------------|---------------------|

| ZGP323LEH4832C | 48-pin SSOP 32K OTP | ZGP323LES2832C | 28-pin SOIC 32K OTP |

| ZGP323LEP4032C | 40-pin PDIP 32K OTP | ZGP323LEH2032C | 20-pin SSOP 32K OTP |

| ZGP323LEH2832C | 28-pin SSOP 32K OTP | ZGP323LEP2032C | 20-pin PDIP 32K OTP |

| ZGP323LEP2832C | 28-pin PDIP 32K OTP | ZGP323LES2032C | 20-pin SOIC 32K OTP |

#### 32KB Automotive Temperature: -40° to +125°C

|                                                | •                   | 1              |                     |

|------------------------------------------------|---------------------|----------------|---------------------|

| Part Number                                    | Description         | Part Number    | Description         |

| ZGP323LAH4832C                                 | 48-pin SSOP 32K OTP | ZGP323LAS2832C | 28-pin SOIC 32K OTP |

| ZGP323LAP4032C                                 | 40-pin PDIP 32K OTP | ZGP323LAH2032C | 20-pin SSOP 32K OTP |

| ZGP323LAH2832C                                 | 28-pin SSOP 32K OTP | ZGP323LAP2032C | 20-pin PDIP 32K OTP |

| ZGP323LAP2832C                                 | 28-pin PDIP 32K OTP | ZGP323LAS2032C | 20-pin SOIC 32K OTP |

|                                                |                     |                |                     |

| Note: Replace C with G for Lead-Free Packaging |                     |                |                     |

# Z i L 0 G 91

#### 8KB Standard Temperature: 0° to +70°C

|  | Part Number    | Description        | Part Number    | Description        |

|--|----------------|--------------------|----------------|--------------------|

|  | ZGP323LSH4808C | 48-pin SSOP 8K OTP | ZGP323LSS2808C | 28-pin SOIC 8K OTP |

|  | ZGP323LSP4008C | 40-pin PDIP 8K OTP | ZGP323LSH2008C | 20-pin SSOP 8K OTP |

|  | ZGP323LSH2808C | 28-pin SSOP 8K OTP | ZGP323LSP2008C | 20-pin PDIP 8K OTP |

|  | ZGP323LSP2808C | 28-pin PDIP 8K OTP | ZGP323LSS2008C | 20-pin SOIC 8K OTP |

|  |                |                    |                |                    |

#### 8KB Extended Temperature: -40° to +105°C

| Description        | Part Number                                                    | Description                                                                                               |

|--------------------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| 48-pin SSOP 8K OTP | ZGP323LES2808C                                                 | 28-pin SOIC 8K OTP                                                                                        |

| 40-pin PDIP 8K OTP | ZGP323LEH2008C                                                 | 20-pin SSOP 8K OTP                                                                                        |

| 28-pin SSOP 8K OTP | ZGP323LEP2008C                                                 | 20-pin PDIP 8K OTP                                                                                        |

| 28-pin PDIP 8K OTP | ZGP323LES2008C                                                 | 20-pin SOIC 8K OTP                                                                                        |

|                    | 48-pin SSOP 8K OTP<br>40-pin PDIP 8K OTP<br>28-pin SSOP 8K OTP | 48-pin SSOP 8K OTP ZGP323LES2808C   40-pin PDIP 8K OTP ZGP323LEH2008C   28-pin SSOP 8K OTP ZGP323LEP2008C |

#### 8KB Automotive Temperature: -40° to +125°C

|                | •                  |                |                    |

|----------------|--------------------|----------------|--------------------|

| Part Number    | Description        | Part Number    | Description        |

| ZGP323LAH4808C | 48-pin SSOP 8K OTP | ZGP323LAS2808C | 28-pin SOIC 8K OTP |

| ZGP323LAP4008C | 40-pin PDIP 8K OTP | ZGP323LAH2008C | 20-pin SSOP 8K OTP |

| ZGP323LAH2808C | 28-pin SSOP 8K OTP | ZGP323LAP2008C | 20-pin PDIP 8K OTP |

| ZGP323LAP2808C | 28-pin PDIP 8K OTP | ZGP323LAS2008C | 20-pin SOIC 8K OTP |

Note: Replace C with G for Lead-Free Packaging