Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detailo                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | Z8                                                        |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 8MHz                                                      |

| Connectivity               | -                                                         |

| Peripherals                | HLVD, POR, WDT                                            |

| Number of I/O              | 24                                                        |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | OTP                                                       |

| EEPROM Size                | -                                                         |

| RAM Size                   | 237 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                 |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/zgp323lsh2808g |

|                            |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

This publication is subject to replacement by a later edition. To determine whether a later edition exists, or to request copies of publications, contact:

**ZiLOG Worldwide Headquarters** 532 Race Street

San Jose, CA 95126-3432 Telephone: 408.558.8500 Fax: 408.558.8300 www.zilog.com

ZiLOG is a registered trademark of ZiLOG Inc. in the United States and in other countries. All other products and/or service names mentioned herein may be trademarks of the companies with which they are associated.

#### **Document Disclaimer**

©2004 by ZiLOG, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZiLOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. Devices sold by ZiLOG, Inc. are covered by warranty and limitation of liability provisions appearing in the ZiLOG, Inc. Terms and Conditions of Sale. ZiLOG, Inc. makes no warranty of merchantability or fitness for any purpose. Except with the express written approval of ZiLOG, use of information, devices, or technology as critical components of life support systems is not authorized. No licenses are conveyed, implicitly or otherwise, by this document under any intellectual property rights.

## List of Figures

| Figure 1.  | Functional Block Diagram                        | . 3 |

|------------|-------------------------------------------------|-----|

| Figure 2.  | Counter/Timers Diagram                          | . 4 |

| Figure 3.  | 20-Pin PDIP/SOIC/SSOP/CDIP* Pin Configuration   | . 5 |

| Figure 4.  | 28-Pin PDIP/SOIC/SSOP/CDIP* Pin Configuration   | . 6 |

| Figure 5.  | 40-Pin PDIP/CDIP* Pin Configuration             | . 7 |

| Figure 6.  | 48-Pin SSOP Pin Configuration                   | . 8 |

| Figure 7.  | Test Load Diagram                               | 10  |

| Figure 8.  | AC Timing Diagram                               | 14  |

| Figure 9.  | Port 0 Configuration                            | 17  |

| Figure 10. | Port 1 Configuration                            |     |

|            | Port 2 Configuration                            |     |

| Figure 12. | Port 3 Configuration                            | 20  |

|            | Port 3 Counter/Timer Output Configuration       |     |

| Figure 14. | Program Memory Map (32K OTP)                    | 24  |

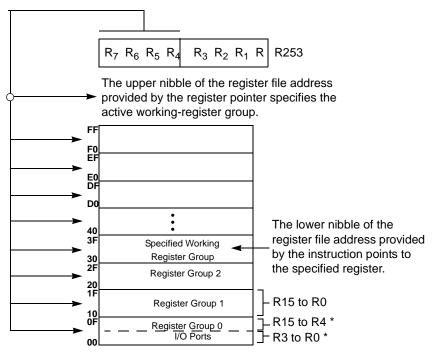

| Figure 15. | Expanded Register File Architecture             | 26  |

| Figure 16. | Register Pointer                                | 27  |

| Figure 17. | Register Pointer—Detail                         | 29  |

| Figure 18. | Glitch Filter Circuitry                         | 38  |

| Figure 19. | Transmit Mode Flowchart                         | 39  |

| Figure 20. | 8-Bit Counter/Timer Circuits                    | 40  |

| Figure 21. | T8_OUT in Single-Pass Mode                      | 41  |

| Figure 22. | T8_OUT in Modulo-N Mode                         | 41  |

| Figure 23. | Demodulation Mode Count Capture Flowchart       | 42  |

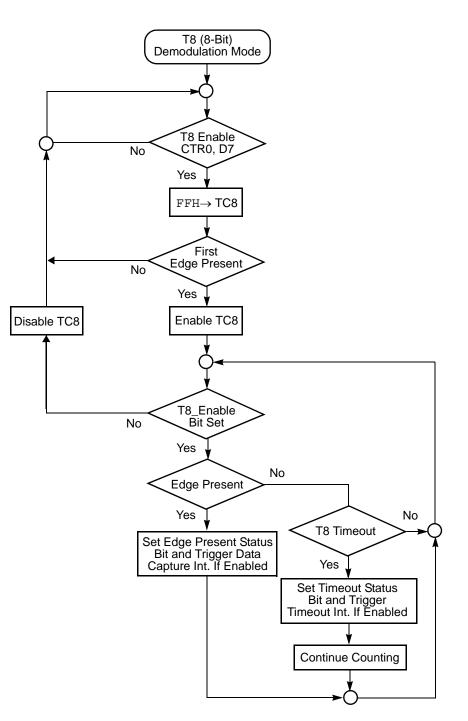

| Figure 24. | Demodulation Mode Flowchart                     | 43  |

| Figure 25. | 16-Bit Counter/Timer Circuits                   | 44  |

| Figure 26. | T16_OUT in Single-Pass Mode                     | 45  |

| Figure 27. | T16_OUT in Modulo-N Mode                        | 45  |

| Figure 28. | Ping-Pong Mode Diagram                          | 47  |

| Figure 29. | Output Circuit                                  | 47  |

| Figure 30. | Interrupt Block Diagram                         | 49  |

| Figure 31. | Oscillator Configuration                        | 51  |

| Figure 32. | Port Configuration Register (PCON) (Write Only) | 53  |

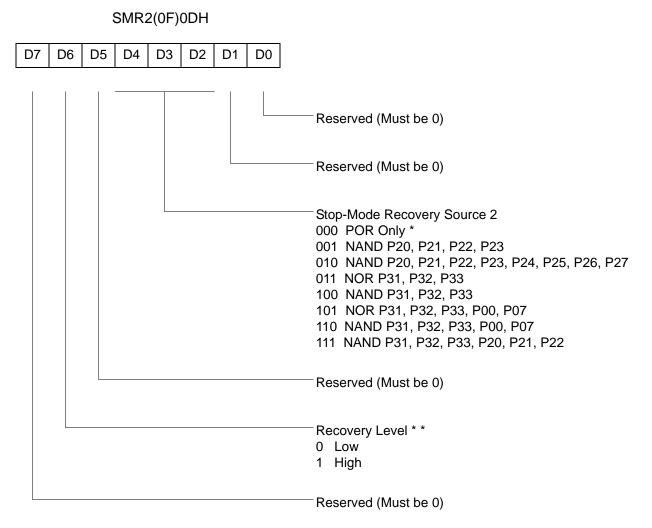

| Figure 33. | STOP Mode Recovery Register                     | 55  |

| Figure 34. | SCLK Circuit                                    | 56  |

- Port 1: 0–3 pull-up transistors

- Port 1: 4–7 pull-up transistors

- Port 2: 0–7 pull-up transistors

- EPROM Protection

- WDT enabled at POR

- **Note:** The mask option pull-up transistor has a *typical* equivalent resistance of 200 K $\Omega$  ±50% at V<sub>CC</sub>=3 V and 450 K $\Omega$  ±50% at  $V_{CC}=2$  V.

## **General Description**

The Z8 GP<sup>TM</sup> OTP MCU Family is an OTP-based member of the MCU family of infrared microcontrollers. With 237B of general-purpose RAM and up to 32KB of OTP, ZiLOG<sup>®</sup>'s CMOS microcontrollers offer fast-executing, efficient use of memory, sophisticated interrupts, input/output bit manipulation capabilities, automated pulse generation/reception, and internal key-scan pull-up transistors.

The Z8 GP<sup>TM</sup> OTP MCU Family architecture (Figure 1) is based on ZiLOG's 8-bit microcontroller core with an Expanded Register File allowing access to registermapped peripherals, input/output (I/O) circuits, and powerful counter/timer circuitry. The Z8<sup>®</sup> offers a flexible I/O scheme, an efficient register and address space structure, and a number of ancillary features that are useful in many consumer, automotive, computer peripheral, and battery-operated hand-held applications.

There are three basic address spaces available to support a wide range of configurations: Program Memory, Register File and Expanded Register File. The register file is composed of 256 Bytes (B) of RAM. It includes 4 I/O port registers, 16 control and status registers, and 236 general-purpose registers. The Expanded Register File consists of two additional register groups (F and D).

To unburden the program from coping with such real-time problems as generating complex waveforms or receiving and demodulating complex waveform/pulses, the Z8 GP OTP MCU offers a new intelligent counter/timer architecture with 8-bit and 16-bit counter/timers (see Figure 2). Also included are a large number of userselectable modes and two on-board comparators to process analog signals with separate reference voltages.

**Note:** All signals with an overline, "", are active Low. For example,  $B/\overline{W}$ , in which WORD is active Low, and  $\overline{B}/W$ , in which BYTE is active Low.

Power connections use the conventional descriptions listed in Table 2.

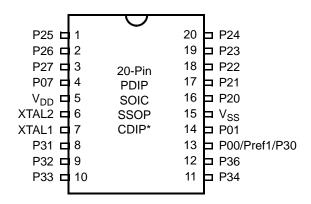

#### Figure 3. 20-Pin PDIP/SOIC/SSOP/CDIP\* Pin Configuration

| Table 3. | 20-Pin PDIP/SOIC/SSOP/CDIP* Pin Identification |

|----------|------------------------------------------------|

|          |                                                |

| Pin # | Symbol          | Function                                             | Direction                                   |

|-------|-----------------|------------------------------------------------------|---------------------------------------------|

| 1–3   | P25–P27         | Port 2, Bits 5,6,7                                   | Input/Output                                |

| 4     | P07             | Port 0, Bit 7                                        | Input/Output                                |

| 5     | V <sub>DD</sub> | Power Supply                                         |                                             |

| 6     | XTAL2           | Crystal Oscillator Clock                             | Output                                      |

| 7     | XTAL1           | Crystal Oscillator Clock                             | Input                                       |

| 8–10  | P31–P33         | Port 3, Bits 1,2,3                                   | Input                                       |

| 11,12 | P34. P36        | Port 3, Bits 4,6                                     | Output                                      |

| 13    | P00/Pref1/P30   | Port 0, Bit 0/Analog reference input<br>Port 3 Bit 0 | Input/Output for P00<br>Input for Pref1/P30 |

| 14    | P01             | Port 0, Bit 1                                        | Input/Output                                |

| 15    | V <sub>SS</sub> | Ground                                               |                                             |

| 16–20 | P20-P24         | Port 2, Bits 0,1,2,3,4                               | Input/Output                                |

**Note:** \*Windowed Cerdip. These units are intended to be used for engineering code development only. ZiLOG does not recommend/guarantee this package for production use.

>

|    |                  |                                      |                 | T <sub>A</sub> =0°C<br>8.0 | Watch-Dog<br>Timer<br><sup>-</sup> Mode |       |       |                      |

|----|------------------|--------------------------------------|-----------------|----------------------------|-----------------------------------------|-------|-------|----------------------|

| No | Symbol           | Parameter                            | v <sub>cc</sub> | Minimum                    | Maximum                                 | Units | Notes | Register<br>(D1, D0) |

| 1  | ТрС              | Input Clock Period                   | 2.0–3.6         | 121                        | DC                                      | ns    | 1     |                      |

| 2  | TrC,TfC          | Clock Input Rise and Fall Times      | 2.0–3.6         |                            | 25                                      | ns    | 1     |                      |

| 3  | TwC              | Input Clock Width                    | 2.0–3.6         | 37                         |                                         | ns    | 1     |                      |

| 4  | TwTinL           | Timer Input<br>Low Width             | 2.0<br>3.6      | 100<br>70                  |                                         | ns    | 1     |                      |

| 5  | TwTinH           | Timer Input High<br>Width            | 2.0–3.6         | 3ТрС                       |                                         |       | 1     |                      |

| 6  | TpTin            | Timer Input Period                   | 2.0–3.6         | 8TpC                       |                                         |       | 1     |                      |

| 7  | TrTin,TfTin      | Timer Input Rise and Fall Timers     | 2.0–3.6         |                            | 100                                     | ns    | 1     |                      |

| 8  | TwIL             | Interrupt Request<br>Low Time        | 2.0<br>3.6      | 100<br>70                  |                                         | ns    | 1, 2  |                      |

| 9  | TwIH             | Interrupt Request<br>Input High Time | 2.0–3.6         | 5TpC                       |                                         |       | 1, 2  |                      |

| 10 | Twsm             | Stop-Mode<br>Recovery Width          | 2.0–3.6         | 12                         |                                         | ns    | 3     |                      |

|    |                  | Spec                                 |                 | 10TpC                      |                                         |       | 4     |                      |

| 11 | Tost             | Oscillator<br>Start-Up Time          | 2.0–3.6         |                            | 5TpC                                    |       | 4     |                      |

| 12 | Twdt             | Watch-Dog Timer                      | 2.0–3.6         | 5                          |                                         | ms    |       | 0, 0                 |

|    |                  | Delay Time                           | 2.0–3.6         | 10                         |                                         | ms    |       | 0, 1                 |

|    |                  |                                      | 2.0–3.6         | 20                         |                                         | ms    |       | 1, 0                 |

|    |                  |                                      | 2.0–3.6         | 80                         |                                         | ms    |       | 1, 1                 |

| 13 | T <sub>POR</sub> | Power-On Reset                       | 2.0–3.6         | 2.5                        | 10                                      | ms    |       |                      |

#### **Table 10. AC Characteristics**

Notes:

1. Timing Reference uses 0.9  $V_{CC}$  for a logic 1 and 0.1  $V_{CC}$  for a logic 0. 2. Interrupt request through Port 3 (P33–P31).

3. SMR – D5 = 1.

4. SMR - D5 = 0.

CTR1(0D)01H" on page 33). Other edge detect and IRQ modes are described in Table 11.

**Note:** Comparators are powered down by entering Stop Mode. For P31–P33 to be used in a Stop Mode Recovery (SMR) source, these inputs must be placed into digital mode.

| Pin       | I/O | Counter/Timers | Comparator | Interrupt |

|-----------|-----|----------------|------------|-----------|

| Pref1/P30 | IN  |                | RF1        |           |

| P31       | IN  | IN             | AN1        | IRQ2      |

| P32       | IN  |                | AN2        | IRQ0      |

| P33       | IN  |                | RF2        | IRQ1      |

| P34       | OUT | Т8             | AO1        |           |

| P35       | OUT | T16            |            |           |

| P36       | OUT | T8/16          |            |           |

| P37       | OUT |                | AO2        |           |

| P20       | I/O | IN             |            |           |

#### Table 11. Port 3 Pin Function Summary

>

Port 3 also provides output for each of the counter/timers and the AND/OR Logic (see Figure 13). Control is performed by programming bits D5–D4 of CTR1, bit 0 of CTR0, and bit 0 of CTR2.

#### **Comparator Inputs**

In analog mode, P31 and P32 have a comparator front end. The comparator reference is supplied to P33 and Pref1. In this mode, the P33 internal data latch and its corresponding IRQ1 are diverted to the SMR sources (excluding P31, P32, and P33) as indicated in Figure 12 on page 20. In digital mode, P33 is used as D3 of the Port 3 input register, which then generates IRQ1.

**Note:** Comparators are powered down by entering Stop Mode. For P31–P33 to be used in a Stop Mode Recovery source, these inputs must be placed into digital mode.

#### **Comparator Outputs**

These channels can be programmed to be output on P34 and P37 through the PCON register.

## **RESET (Input, Active Low)**

Reset initializes the MCU and is accomplished either through Power-On, Watch-Dog Timer, Stop Mode Recovery, Low-Voltage detection, or external reset. During Power-On Reset and Watch-Dog Timer Reset, the internally generated reset drives the reset pin Low for the POR time. Any devices driving the external reset line must be open-drain to avoid damage from a possible conflict during reset conditions. Pull-up is provided internally.

When the Z8  $GP^{TM}$  asserts (Low) the RESET pin, the internal pull-up is disabled. The Z8  $GP^{TM}$  does not assert the RESET pin when under VBO.

**Note:** The external Reset does not initiate an exit from STOP mode.

## **Functional Description**

This device incorporates special functions to enhance the Z8<sup>®</sup>, functionality in consumer and battery-operated applications.

#### **Program Memory**

This device addresses up to 32KB of OTP memory. The first 12 Bytes are reserved for interrupt vectors. These locations contain the six 16-bit vectors that correspond to the six available interrupts.

#### RAM

This device features 256B of RAM. See Figure 14.

27

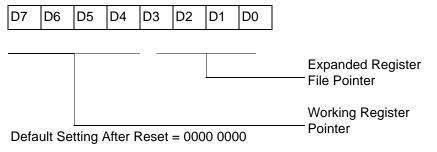

The upper nibble of the register pointer (see Figure 16) selects which working register group, of 16 bytes in the register file, is accessed out of the possible 256. The lower nibble selects the expanded register file bank and, in the case of the Z8 GP family, banks 0, F, and D are implemented. A  $_{0\rm H}$  in the lower nibble allows the normal register file (bank 0) to be addressed. Any other value from 1H to FH exchanges the lower 16 registers to an expanded register bank.

#### Figure 16. Register Pointer

#### Example: Z8 GP: (See Figure 15 on page 26)

R253 RP = 00h R0 = Port 0 R1 = Port 1 R2 = Port 2 R3 = Port 3

But if:

R253 RP = 0Dh R0 = CTRL0 R1 = CTRL1 R2 = CTRL2R3 = Reserved

\* RP = 00: Selects Register Bank 0, Working Register Group 0

Figure 17. Register Pointer—Detail

#### Stack

The internal register file is used for the stack. An 8-bit Stack Pointer SPL (R255) is used for the internal stack that resides in the general-purpose registers (R4–R239). SPH (R254) can be used as a general-purpose register.

32

#### Table 12. CTR0(D)00H Counter/Timer8 Control Register (Continued)

| Field            | Bit Position |     | Value | Description                |

|------------------|--------------|-----|-------|----------------------------|

| Counter_INT_Mask | 1-           | R/W | 0     | Disable Time-Out Interrupt |

|                  |              |     | 1     | Enable Time-Out Interrupt  |

| P34_Out          | 0            | R/W | 0*    | P34 as Port Output         |

|                  |              |     | 1     | T8 Output on P34           |

#### Note:

\*Indicates the value upon Power-On Reset.

#### T8 Enable

This field enables T8 when set (written) to 1.

#### Single/Modulo-N

When set to 0 (Modulo-N), the counter reloads the initial value when the terminal count is reached. When set to 1 (single-pass), the counter stops when the terminal count is reached.

#### Timeout

This bit is set when T8 times out (terminal count reached). To reset this bit, write a 1 to its location.

**Caution:** Writing a 1 is the only way to reset the Terminal Count status condition. Reset this bit before using/enabling the counter/timers.

The first clock of T8 might not have complete clock width and can occur any time when enabled.

Note: Take care when using the OR or AND commands to manipulate CTR0, bit 5 and CTR1, bits 0 and 1 (Demodulation Mode). These instructions use a Read-Modify-Write sequence in which the current status from the CTR0 and CTR1 registers is ORed or ANDed with the designated value and then written back into the registers.

#### **T8 Clock**

This bit defines the frequency of the input signal to T8.

35

#### T8/T16\_Logic/Edge \_Detect

In TRANSMIT Mode, this field defines how the outputs of T8 and T16 are combined (AND, OR, NOR, NAND).

In DEMODULATION Mode, this field defines which edge should be detected by the edge detector.

#### Transmit\_Submode/Glitch Filter

In Transmit Mode, this field defines whether T8 and T16 are in the PING-PONG mode or in independent normal operation mode. Setting this field to "NORMAL OPERATION Mode" terminates the "PING-PONG Mode" operation. When set to 10, T16 is immediately forced to a 0; a setting of 11 forces T16 to output a 1.

In DEMODULATION Mode, this field defines the width of the glitch that must be filtered out.

#### Initial\_T8\_Out/Rising\_Edge

In TRANSMIT Mode, if 0, the output of T8 is set to 0 when it starts to count. If 1, the output of T8 is set to 1 when it starts to count. When the counter is not enabled and this bit is set to 1 or 0, T8\_OUT is set to the opposite state of this bit. This ensures that when the clock is enabled, a transition occurs to the initial state set by CTR1, D1.

In DEMODULATION Mode, this bit is set to 1 when a rising edge is detected in the input signal. In order to reset the mode, a 1 should be written to this location.

#### Initial\_T16 Out/Falling \_Edge

In TRANSMIT Mode, if it is 0, the output of T16 is set to 0 when it starts to count. If it is 1, the output of T16 is set to 1 when it starts to count. This bit is effective only in Normal or PING-PONG Mode (CTR1, D3; D2). When the counter is not enabled and this bit is set, T16\_OUT is set to the opposite state of this bit. This ensures that when the clock is enabled, a transition occurs to the initial state set by CTR1, D0.

In DEMODULATION Mode, this bit is set to 1 when a falling edge is detected in the input signal. In order to reset it, a 1 should be written to this location.

**Note:** Modifying CTR1 (D1 or D0) while the counters are enabled causes unpredictable output from T8/16\_OUT.

#### CTR2 Counter/Timer 16 Control Register—CTR2(D)02H

Table 14 lists and briefly describes the fields for this register.

ZILOG

Figure 24. Demodulation Mode Flowchart

#### **During PING-PONG Mode**

The enable bits of T8 and T16 (CTR0, D7; CTR2, D7) are set and cleared alternately by hardware. The timeout bits (CTR0, D5; CTR2, D5) are set every time the counter/timers reach the terminal count.

#### **Timer Output**

The output logic for the timers is illustrated in Figure 29. P34 is used to output T8-OUT when D0 of CTR0 is set. P35 is used to output the value of TI6-OUT when D0 of CTR2 is set. When D6 of CTR1 is set, P36 outputs the logic combination of T8-OUT and T16-OUT determined by D5 and D4 of CTR1.

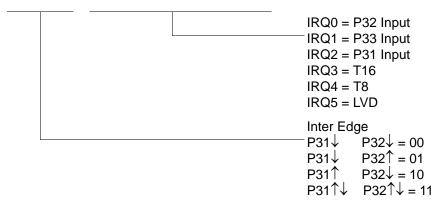

#### Interrupts

The Z8 GP<sup>TM</sup> OTP MCU Family features six different interrupts (Table 16). The interrupts are maskable and prioritized (Figure 30). The six sources are divided as follows: three sources are claimed by Port 3 lines P33–P31, two by the counter/ timers (Table 16) and one for low voltage detection. The Interrupt Mask Register (globally or individually) enables or disables the six interrupt requests.

The source for IRQ is determined by bit 1 of the Port 3 mode register (P3M). When in digital mode, Pin P33 is the source. When in analog mode the output of the Stop mode recovery source logic is used as the source for the interrupt. See Figure 35, Stop Mode Recovery Source, on page 57.

| Name | Source               | Vector Location | Comments                                       |

|------|----------------------|-----------------|------------------------------------------------|

| IRQ0 | P32                  | 0,1             | External (P32), Rising, Falling Edge Triggered |

| IRQ1 | P33                  | 2,3             | External (P33), Falling Edge Triggered         |

| IRQ2 | P31, T <sub>IN</sub> | 4,5             | External (P31), Rising, Falling Edge Triggered |

| IRQ3 | T16                  | 6,7             | Internal                                       |

| IRQ4 | Т8                   | 8,9             | Internal                                       |

| IRQ5 | LVD                  | 10,11           | Internal                                       |

#### Table 16. Interrupt Types, Sources, and Vectors

When more than one interrupt is pending, priorities are resolved by a programmable priority encoder controlled by the Interrupt Priority Register. An interrupt machine cycle activates when an interrupt request is granted. As a result, all subsequent interrupts are disabled, and the Program Counter and Status Flags are saved. The cycle then branches to the program memory vector location reserved for that interrupt. All Z8 GP<sup>TM</sup> OTP MCU Family interrupts are vectored through locations in the program memory. This memory location and the next byte contain the 16-bit address of the interrupt service routine for that particular interrupt request. To accommodate polled interrupt systems, interrupt inputs are masked, and the Interrupt Request register is polled to determine which of the interrupt requests require service.

An interrupt resulting from AN1 is mapped into IRQ2, and an interrupt from AN2 is mapped into IRQ0. Interrupts IRQ2 and IRQ0 can be rising, falling, or both edge triggered. These interrupts are programmable by the user. The software can poll to identify the state of the pin.

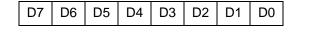

Programming bits for the Interrupt Edge Select are located in the IRQ Register (R250), bits D7 and D6. The configuration is indicated in Table 17.

| IRQ                                            |    | Interrupt Edge |            |  |  |

|------------------------------------------------|----|----------------|------------|--|--|

| D7                                             | D6 | IRQ2 (P31)     | IRQ0 (P32) |  |  |

| 0                                              | 0  | F              | F          |  |  |

| 0                                              | 1  | F              | R          |  |  |

| 1                                              | 0  | R              | F          |  |  |

| 1 1 R/F R/F                                    |    |                |            |  |  |

| <b>Note:</b> F = Falling Edge; R = Rising Edge |    |                |            |  |  |

#### Table 17. IRQ Register

Note: If used in conjunction with SMR, either of the two specified events causes a Stop-Mode Recovery.

\* Default setting after reset

\* \* At the XOR gate input

ZILOG

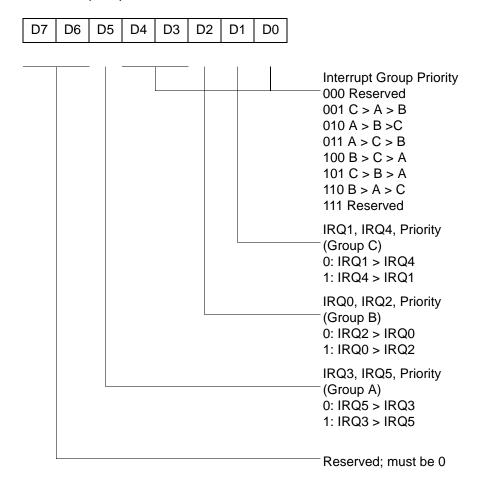

#### R249 IPR(F9H)

Figure 51. Interrupt Priority Register (F9H: Write Only)

#### R250 IRQ(FAH)

#### Figure 52. Interrupt Request Register (FAH: Read/Write)

#### R251 IMR(FBH)

\* Default setting after reset

\* \* Only by using EI, DI instruction; DI is required before changing the IMR register

#### Figure 53. Interrupt Mask Register (FBH: Read/Write)

Z8 GP<sup>™</sup> OTP MCU Family Product Specification

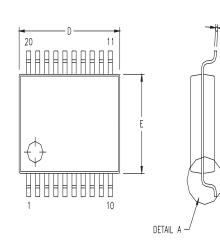

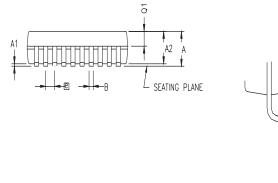

| CVALDOL |      | MILLIMETER          |      |       | INCH  |       |

|---------|------|---------------------|------|-------|-------|-------|

| SYMBOL  | MIN  | NOM                 | MAX  | MIN   | NOM   | MAX   |

| A       | 1.73 | 1.85                | 1.98 | 0.068 | 0.073 | 0.078 |

| A1      | 0.05 | 0.13                | 0.21 | 0.002 | 0.005 | 0.008 |

| A2      | 1.68 | 1.73                | 1.83 | 0.066 | 0.068 | 0.072 |

| В       | 0.25 | 0.30                | 0.38 | 0.010 | 0.012 | 0.015 |

| С       | 0.13 | 0.15                | 0.22 | 0.005 | 0.006 | 0.009 |

| D       | 7.07 | 7.20                | 7.33 | 0.278 | 0.283 | 0.289 |

| E       | 5.20 | 5.30                | 5.38 | 0.205 | 0.209 | 0.212 |

| e       |      | 0.65 BSC 0.0256 BSC |      |       | ;     |       |

| Н       | 7.65 | 7.80                | 7.90 | 0.301 | 0.307 | 0.311 |

| L       | 0.56 | 0.75                | 0.94 | 0.022 | 0.030 | 0.037 |

| Q1      | 0.74 | 0.78                | 0.82 | 0.029 | 0.031 | 0.032 |

CONTROLLING DIMENSIONS : MM LEADS ARE COPLANAR WITHIN .004 INCH.

Figure 61. 20-Pin SSOP Package Diagram

Н

0-"8

DETAIL A

# Z i L 0 G 92

#### 4KB Standard Temperature: 0° to +70°C

| Part Number    | Description        | Part Number    | Description        |

|----------------|--------------------|----------------|--------------------|

| ZGP323LSH4804C | 48-pin SSOP 4K OTP | ZGP323LSS2804C | 28-pin SOIC 4K OTP |

| ZGP323LSP4004C | 40-pin PDIP 4K OTP | ZGP323LSH2004C | 20-pin SSOP 4K OTP |

| ZGP323LSH2804C | 28-pin SSOP 4K OTP | ZGP323LSP2004C | 20-pin PDIP 4K OTP |

| ZGP323LSP2804C | 28-pin PDIP 4K OTP | ZGP323LSS2004C | 20-pin SOIC 4K OTP |

#### 4KB Extended Temperature: -40° to +105°C

| Part Number    | Description        | Part Number    | Description        |

|----------------|--------------------|----------------|--------------------|

| ZGP323LEH4804C | 48-pin SSOP 4K OTP | ZGP323LES2804C | 28-pin SOIC 4K OTP |

| ZGP323LEP4004C | 40-pin PDIP 4K OTP | ZGP323LEH2004C | 20-pin SSOP 4K OTP |

| ZGP323LEH2804C | 28-pin SSOP 4K OTP | ZGP323LEP2004C | 20-pin PDIP 4K OTP |

| ZGP323LEP2804C | 28-pin PDIP 4K OTP | ZGP323LES2004C | 20-pin SOIC 4K OTP |

#### 4KB Automotive Temperature: -40° to +125°C

|                | •                  |                |                    |

|----------------|--------------------|----------------|--------------------|

| Part Number    | Description        | Part Number    | Description        |

| ZGP323LAH4804C | 48-pin SSOP 4K OTP | ZGP323LAS2804C | 28-pin SOIC 4K OTP |

| ZGP323LAP4004C | 40-pin PDIP 4K OTP | ZGP323LAH2004C | 20-pin SSOP 4K OTP |

| ZGP323LAH2804C | 28-pin SSOP 4K OTP | ZGP323LAP2004C | 20-pin PDIP 4K OTP |

| ZGP323LAP2804C | 28-pin PDIP 4K OTP | ZGP323LAS2004C | 20-pin SOIC 4K OTP |

#### Note: Replace C with G for Lead-Free Packaging

#### **Additional Components**

| Part Number    | Description         | Part Number    | Description        |

|----------------|---------------------|----------------|--------------------|

| ZGP323ICE01ZEM | Emulator/programmer | ZGP32300100ZPR | Programming System |

## Z8 GP<sup>™</sup> OTP MCU Family Product Specification

## D

DC characteristics 11 demodulation mode count capture flowchart 42 flowchart 43 T16 45 T8 41 description functional 23 general 2 pin 4

## Ε

**EPROM** selectable options 62 expanded register file 24 expanded register file architecture 26 expanded register file control registers 69 flag 78 interrupt mask register 77 interrupt priority register 76 interrupt request register 77 port 0 and 1 mode register 75 port 2 configuration register 73 port 3 mode register 74 port configuration register 73 register pointer 78 stack pointer high register 79 stack pointer low register 79 stop-mode recovery register 71 stop-mode recovery register 2 72 T16 control register 67 T8 and T16 common control functions register 65 T8/T16 control register 68 TC8 control register 64 watch-dog timer register 73

## F

features standby modes 1 functional description counter/timer functional blocks 38 CTR(D)01h register 33 CTR0(D)00h register 31 CTR2(D)02h register 35 CTR3(D)03h register 37 expanded register file 24 expanded register file architecture 26 HI16(D)09h register 30 HI8(D)0Bh register 30 L08(D)0Ah register 30 L0I6(D)08h register 30 program memory map 24 **RAM 23** register description 63 register file 28 register pointer 27 register pointer detail 29 SMR2(F)0D1h register 38 stack 29 TC16H(D)07h register 30 TC16L(D)06h register 31 TC8H(D)05h register 31 TC8L(D)04h register 31

## G

glitch filter circuitry 38

## Η

halt instruction, counter/timer 52

## I

input circuit 38 interrupt block diagram, counter/timer 49 interrupt types, sources and vectors 50

## L

low-voltage detection register 63