## E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | Z8                                                        |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 8MHz                                                      |

| Connectivity               | -                                                         |

| Peripherals                | HLVD, POR, WDT                                            |

| Number of I/O              | 16                                                        |

| Program Memory Size        | 32KB (32K x 8)                                            |

| Program Memory Type        | ОТР                                                       |

| EEPROM Size                | -                                                         |

| RAM Size                   | 237 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                 |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/zgp323lss2032c |

|                            |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

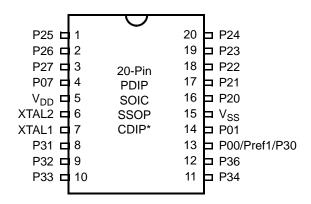

#### Figure 3. 20-Pin PDIP/SOIC/SSOP/CDIP\* Pin Configuration

| Table 3. | 20-Pin PDIP/SOIC/SSOP/CDIP* Pin Identification |

|----------|------------------------------------------------|

|          |                                                |

| Pin # Symbol |                 | Function                                             | Direction                                   |  |

|--------------|-----------------|------------------------------------------------------|---------------------------------------------|--|

| 1–3          | P25–P27         | Port 2, Bits 5,6,7                                   | Input/Output                                |  |

| 4            | P07             | Port 0, Bit 7                                        | Input/Output                                |  |

| 5            | V <sub>DD</sub> | Power Supply                                         |                                             |  |

| 6            | XTAL2           | Crystal Oscillator Clock                             | Output                                      |  |

| 7            | XTAL1           | Crystal Oscillator Clock                             | Input                                       |  |

| 8–10         | P31–P33         | Port 3, Bits 1,2,3                                   | Input                                       |  |

| 11,12        | P34. P36        | Port 3, Bits 4,6                                     | Output                                      |  |

| 13           | P00/Pref1/P30   | Port 0, Bit 0/Analog reference input<br>Port 3 Bit 0 | Input/Output for P00<br>Input for Pref1/P30 |  |

| 14           | P01             | Port 0, Bit 1                                        | Input/Output                                |  |

| 15           | V <sub>SS</sub> | Ground                                               |                                             |  |

| 16–20        | P20-P24         | Port 2, Bits 0,1,2,3,4                               | Input/Output                                |  |

**Note:** \*Windowed Cerdip. These units are intended to be used for engineering code development only. ZiLOG does not recommend/guarantee this package for production use.

>

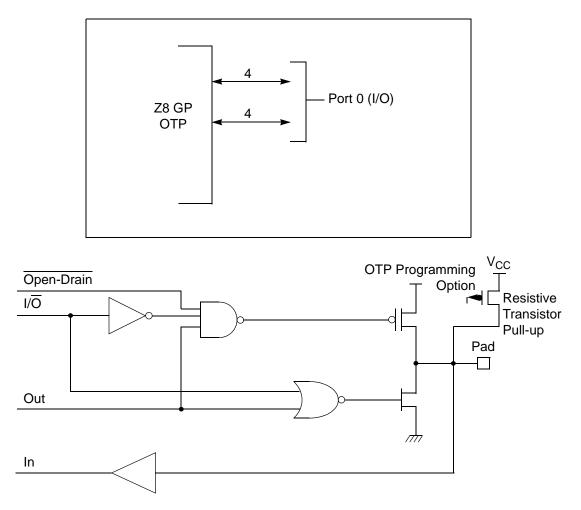

Figure 9. Port 0 Configuration

#### Port 1 (P17–P10)

Port 1 (see Figure 10) Port 1 can be configured for standard port input or output mode. After POR, Port 1 is configured as an input port. The output drivers are either push-pull or open-drain and are controlled by bit D1 in the PCON register.

**Note:** The Port 1 direction is reset to be input following an SMR.

27

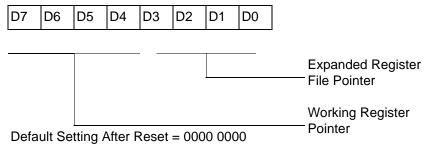

The upper nibble of the register pointer (see Figure 16) selects which working register group, of 16 bytes in the register file, is accessed out of the possible 256. The lower nibble selects the expanded register file bank and, in the case of the Z8 GP family, banks 0, F, and D are implemented. A  $_{0\rm H}$  in the lower nibble allows the normal register file (bank 0) to be addressed. Any other value from 1H to FH exchanges the lower 16 registers to an expanded register bank.

#### Figure 16. Register Pointer

#### Example: Z8 GP: (See Figure 15 on page 26)

R253 RP = 00h R0 = Port 0 R1 = Port 1 R2 = Port 2 R3 = Port 3

But if:

R253 RP = 0Dh R0 = CTRL0 R1 = CTRL1 R2 = CTRL2R3 = Reserved

#### Capture\_INT\_Mask

Set this bit to allow an interrupt when data is captured into either LO8 or HI8 upon a positive or negative edge detection in demodulation mode.

#### Counter\_INT\_Mask

Set this bit to allow an interrupt when T8 has a timeout.

#### P34\_Out

This bit defines whether P34 is used as a normal output pin or the T8 output.

#### T8 and T16 Common Functions—CTR1(0D)01H

This register controls the functions in common with the T8 and T16.

Table 13 lists and briefly describes the fields for this register.

| Field             | Bit Position |     | Value | Description       |

|-------------------|--------------|-----|-------|-------------------|

| Mode              | 7            | R/W | 0*    | Transmit Mode     |

|                   |              |     |       | Demodulation Mode |

| P36_Out/          | -6           | R/W |       | Transmit Mode     |

| Demodulator_Input |              |     | 0*    | Port Output       |

|                   |              |     | 1     | T8/T16 Output     |

|                   |              |     |       | Demodulation Mode |

|                   |              |     | 0     | P31               |

|                   |              |     | 1     | P20               |

| T8/T16_Logic/     | 54           | R/W |       | Transmit Mode     |

| Edge _Detect      |              |     | 00**  | AND               |

| -                 |              |     | 01    | OR                |

|                   |              |     | 10    | NOR               |

|                   |              |     | 11    | NAND              |

|                   |              |     |       | Demodulation Mode |

|                   |              |     | 00**  | Falling Edge      |

|                   |              |     | 01    | Rising Edge       |

|                   |              |     | 10    | Both Edges        |

|                   |              |     | 11    | Reserved          |

#### Table 13. CTR1(0D)01H T8 and T16 Common Functions

# Z i L 0 G 36

| Field            | Bit Position |     | Value | Description                    |

|------------------|--------------|-----|-------|--------------------------------|

| T16_Enable       | 7            | R   | 0*    | Counter Disabled               |

|                  |              |     | 1     | Counter Enabled                |

|                  |              | W   | 0     | Stop Counter                   |

|                  |              |     | 1     | Enable Counter                 |

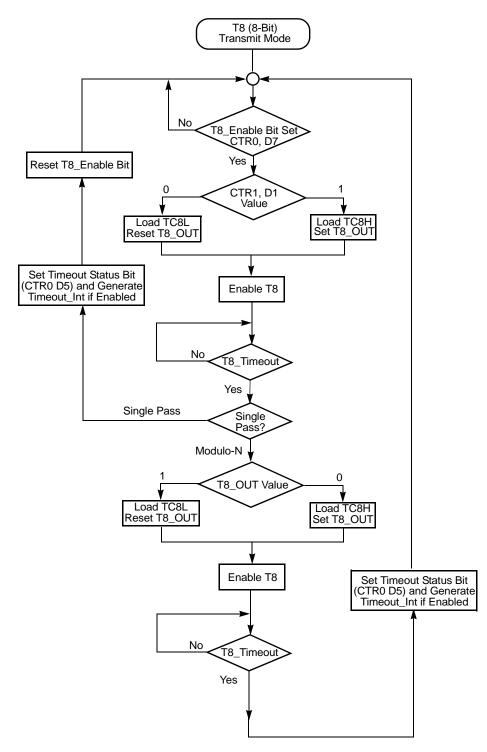

| Single/Modulo-N  | -6           | R/W |       | Transmit Mode                  |

|                  |              |     | 0*    | Modulo-N                       |

|                  |              |     | 1     | Single Pass                    |

|                  |              |     |       | Demodulation Mode              |

|                  |              |     | 0     | T16 Recognizes Edge            |

|                  |              |     | 1     | T16 Does Not Recognize<br>Edge |

| Time_Out         | 5            | R   | 0*    | No Counter Timeout             |

|                  |              |     | 1     | Counter Timeout                |

|                  |              |     |       | Occurred                       |

|                  |              | W   | 0     | No Effect                      |

|                  |              |     | 1     | Reset Flag to 0                |

| T16 _Clock       | 43           | R/W | 00**  | SCLK                           |

|                  |              |     | 01    | SCLK/2                         |

|                  |              |     | 10    | SCLK/4                         |

|                  |              |     | 11    | SCLK/8                         |

| Capture_INT_Mask | 2            | R/W | 0**   | Disable Data Capture Int.      |

|                  |              |     | 1     | Enable Data Capture Int.       |

| Counter_INT_Mask | 1-           | R/W | 0     | Disable Timeout Int.           |

|                  |              |     | 1     | Enable Timeout Int.            |

| P35_Out          | 0            | R/W | 0*    | P35 as Port Output             |

|                  |              |     | 1     | T16 Output on P35              |

#### Table 14. CTR2(D)02H: Counter/Timer16 Control Register

#### Note:

\*Indicates the value upon Power-On Reset.

\*\*Indicates the value upon Power-On Reset.Not reset with Stop Mode recovery.

#### T16\_Enable

This field enables T16 when set to 1.

#### Single/Modulo-N

In TRANSMIT Mode, when set to 0, the counter reloads the initial value when it reaches the terminal count. When set to 1, the counter stops when the terminal count is reached.

Figure 19. Transmit Mode Flowchart

#### If D6 of CTR2 Is 1

T16 ignores the subsequent edges in the input signal and continues counting down. A timeout of T8 causes T16 to capture its current value and generate an interrupt if enabled (CTR2, D2). In this case, T16 does not reload and continues counting. If the D6 bit of CTR2 is toggled (by writing a 0 then a 1 to it), T16 captures and reloads on the next edge (rising, falling, or both depending on CTR1, D5; D4), continuing to ignore subsequent edges.

This T16 mode generally measures mark time, the length of an active carrier signal burst.

If T16 reaches 0, T16 continues counting from FFFFh. Meanwhile, a status bit (CTR2 D5) is set, and an interrupt timeout can be generated if enabled (CTR2 D1).

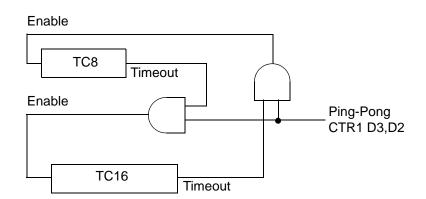

#### **Ping-Pong Mode**

This operation mode is only valid in TRANSMIT Mode. T8 and T16 must be programmed in Single-Pass mode (CTR0, D6; CTR2, D6), and Ping-Pong mode must be programmed in CTR1, D3; D2. The user can begin the operation by enabling either T8 or T16 (CTR0, D7 or CTR2, D7). For example, if T8 is enabled, T8\_OUT is set to this initial value (CTR1, D1). According to T8\_OUT's level, TC8H or TC8L is loaded into T8. After the terminal count is reached, T8 is disabled, and T16 is enabled. T16\_OUT then switches to its initial value (CTR1, D0), data from TC16H and TC16L is loaded, and T16 starts to count. After T16 reaches the terminal count, it stops, T8 is enabled again, repeating the entire cycle. Interrupts can be allowed when T8 or T16 reaches terminal control (CTR0, D1; CTR2, D1). To stop the ping-pong operation, write 00 to bits D3 and D2 of CTR1. See Figure 28.

**Note:** Enabling ping-pong operation while the counter/timers are running might cause intermittent counter/timer function. Disable the counter/timers and reset the status flags before instituting this operation.

Figure 28. Ping-Pong Mode Diagram

#### Initiating PING-PONG Mode

First, make sure both counter/timers are not running. Set T8 into Single-Pass mode (CTR0, D6), set T16 into SINGLE-PASS mode (CTR2, D6), and set the Ping-Pong mode (CTR1, D2; D3). These instructions can be in random order. Finally, start PING-PONG mode by enabling either T8 (CTR0, D7) or T16 (CTR2, D7). See Figure 29.

The initial value of T8 or T16 must not be 1. Stopping the timer and restarting the timer reloads the initial value to avoid an unknown previous value.

#### **During PING-PONG Mode**

The enable bits of T8 and T16 (CTR0, D7; CTR2, D7) are set and cleared alternately by hardware. The timeout bits (CTR0, D5; CTR2, D5) are set every time the counter/timers reach the terminal count.

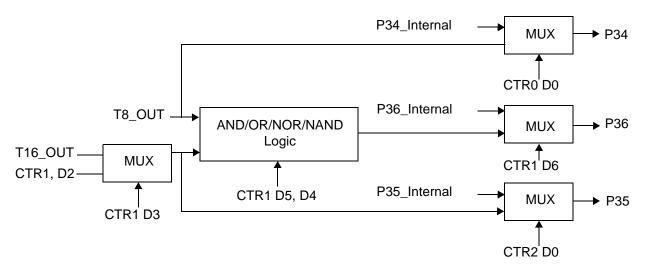

#### **Timer Output**

The output logic for the timers is illustrated in Figure 29. P34 is used to output T8-OUT when D0 of CTR0 is set. P35 is used to output the value of TI6-OUT when D0 of CTR2 is set. When D6 of CTR1 is set, P36 outputs the logic combination of T8-OUT and T16-OUT determined by D5 and D4 of CTR1.

#### Interrupts

The Z8 GP<sup>TM</sup> OTP MCU Family features six different interrupts (Table 16). The interrupts are maskable and prioritized (Figure 30). The six sources are divided as follows: three sources are claimed by Port 3 lines P33–P31, two by the counter/ timers (Table 16) and one for low voltage detection. The Interrupt Mask Register (globally or individually) enables or disables the six interrupt requests.

The source for IRQ is determined by bit 1 of the Port 3 mode register (P3M). When in digital mode, Pin P33 is the source. When in analog mode the output of the Stop mode recovery source logic is used as the source for the interrupt. See Figure 35, Stop Mode Recovery Source, on page 57.

#### **Power-On Reset**

A timer circuit clocked by a dedicated on-board RC-oscillator is used for the Power-On Reset (POR) timer function. The POR time allows  $V_{DD}$  and the oscillator circuit to stabilize before instruction execution begins.

The POR timer circuit is a one-shot timer triggered by one of three conditions:

- Power Fail to Power OK status, including Waking up from V<sub>BO</sub> Standby

- Stop-Mode Recovery (if D5 of SMR = 1)

- WDT Timeout

The POR timer is 2.5 ms minimum. Bit 5 of the Stop-Mode Register determines whether the POR timer is bypassed after Stop-Mode Recovery (typical for external clock).

#### HALT Mode

This instruction turns off the internal CPU clock, but not the XTAL oscillation. The counter/timers and external interrupts IRQ0, IRQ1, IRQ2, IRQ3, IRQ4, and IRQ5 remain active. The devices are recovered by interrupts, either externally or internally generated. An interrupt request must be executed (enabled) to exit HALT Mode. After the interrupt service routine, the program continues from the instruction after HALT Mode.

#### **STOP Mode**

This instruction turns off the internal clock and external crystal oscillation, reducing the standby current to 10  $\mu$ A or less. STOP Mode is terminated only by a reset, such as WDT timeout, POR, SMR or external reset. This condition causes the processor to restart the application program at address 000CH. To enter STOP (or HALT) mode, first flush the instruction pipeline to avoid suspending execution in mid-instruction. Execute a NOP (Opcode = FFH) immediately before the appropriate sleep instruction, as follows:

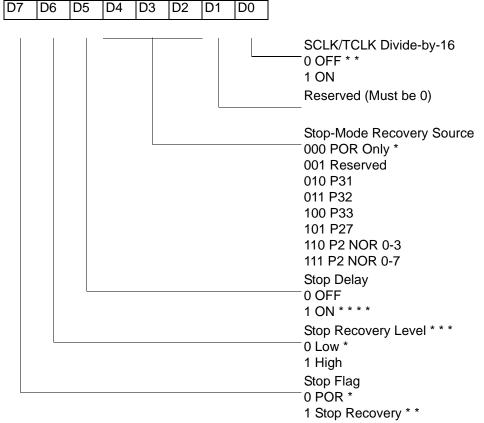

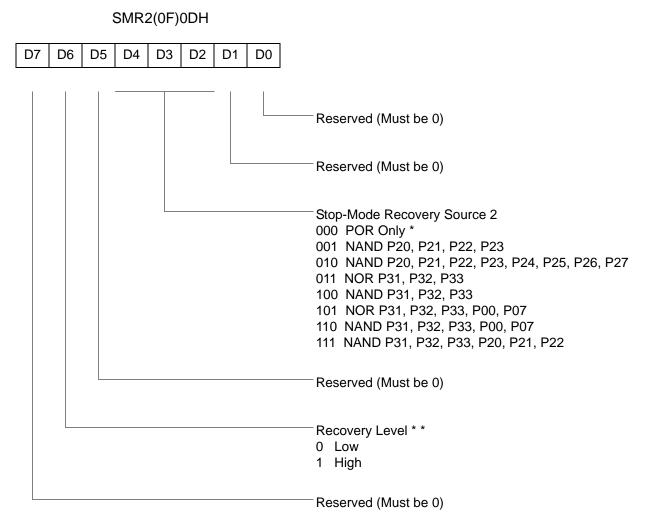

#### SMR(0F)0BH

\* Default after Power On Reset or Watch-Dog Reset

- \* \* Set after STOP Mode Recovery

- \* \* \* At the XOR gate input

\* \* \* \* Default setting after reset. Must be 1 if using a crystal or resonator clock source.

#### Figure 33. STOP Mode Recovery Register

#### SCLK/TCLK Divide-by-16 Select (D0)

D0 of the SMR controls a divide-by-16 prescaler of SCLK/TCLK (Figure 34). This control selectively reduces device power consumption during normal processor execution (SCLK control) and/or Halt Mode (where TCLK sources interrupt logic). After Stop Mode Recovery, this bit is set to a 0.

Z8 GP<sup>TM</sup> OTP MCU Family Product Specification

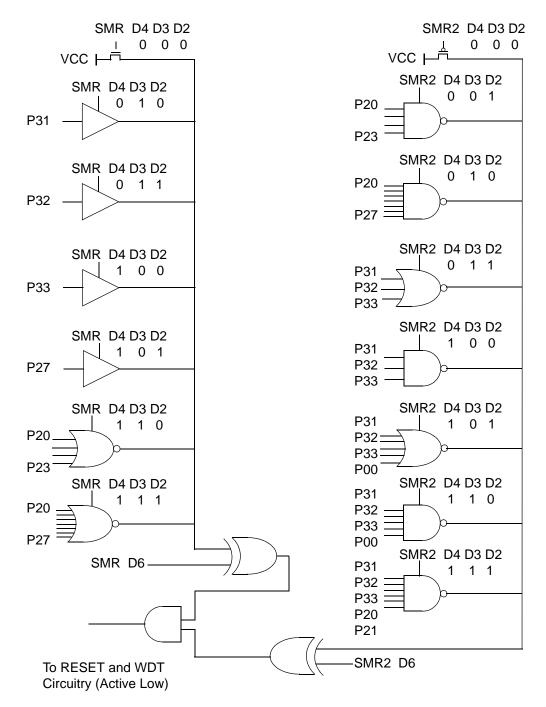

Figure 35. Stop Mode Recovery Source

### **Expanded Register File Control Registers (0D)**

The expanded register file control registers (0D) are depicted in Figure 39 through Figure 43.

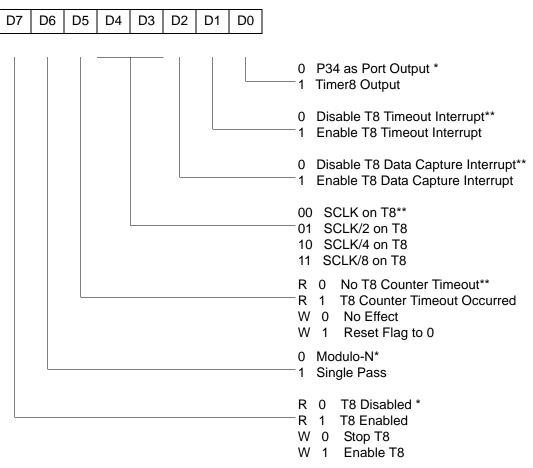

#### CTR0(0D)00H

\* Default setting after reset

\*\*Default setting after reset. Not reset with Stop Mode recovery.

#### Figure 39. TC8 Control Register ((0D)O0H: Read/Write Except Where Noted)

#### CTR3(0D)03H

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |                                                                                                                                                  |

|----|----|----|----|----|----|----|----|--------------------------------------------------------------------------------------------------------------------------------------------------|

|    |    |    |    |    |    |    |    | Reserved<br>No effect when written<br>Always reads 11111                                                                                         |

|    |    |    |    |    |    |    |    | Sync Mode<br>0* Disable Sync Mode**<br>1 Enable Sync Mode                                                                                        |

|    |    |    |    |    |    |    |    | T <sub>8</sub> Enable<br>R 0* T <sub>8</sub> Disabled<br>R 1 T <sub>8</sub> Enabled<br>W0 Stop T <sub>8</sub><br>W1 Enable T <sub>8</sub>        |

|    |    |    |    |    |    |    |    | T <sub>16</sub> Enable<br>R 0* T <sub>16</sub> Disabled<br>R 1 T <sub>16</sub> Enabled<br>W 0 Stop T <sub>16</sub><br>W 1 Enable T <sub>16</sub> |

\* Default setting after reset. \*\* Default setting after reset. Not reset with Stop Mode recovery.

#### Figure 42. T8/T16 Control Register (0D)03H: Read/Write (Except Where Noted)

**Note:** If Sync Mode is enabled, the first pulse of T8 carrier is always synchronized with T16 (demodulated signal). It can always provide a full carrier pulse.

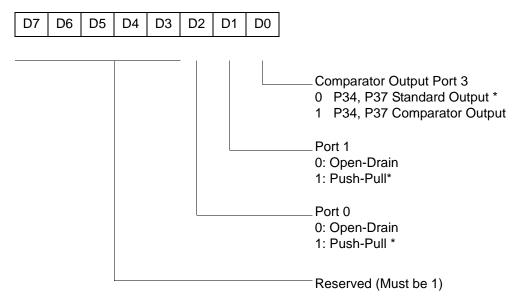

#### PCON(0F)00H

\* Default setting after reset

#### Figure 44. Port Configuration Register (PCON)(0F)00H: Write Only)

Note: If used in conjunction with SMR, either of the two specified events causes a Stop-Mode Recovery.

\* Default setting after reset

\* \* At the XOR gate input

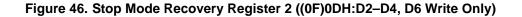

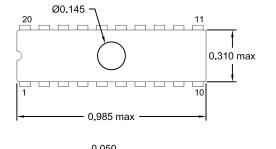

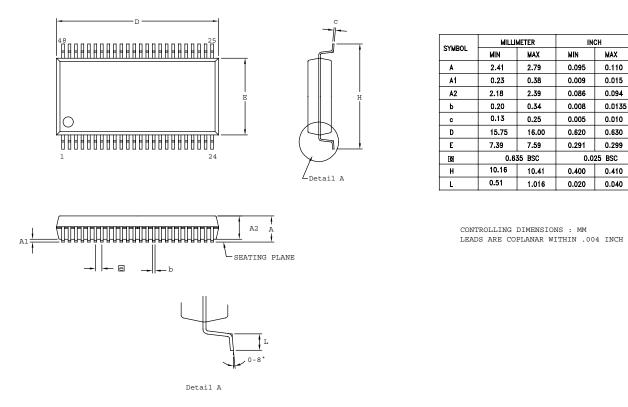

## **Package Information**

Package information for all versions of Z8 GP<sup>TM</sup> OTP MCU Family are depicted in Figures 58 through Figure 68.

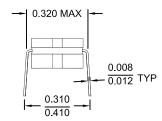

Figure 58. 20-Pin CDIP Package

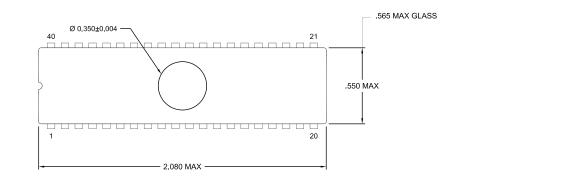

Figure 66. 40-Pin CDIP Package

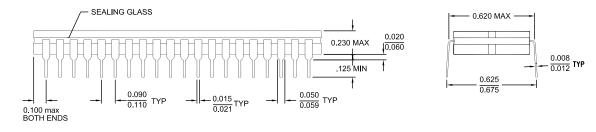

MILLIMETER INCH SYMBOL MIN MAX MIN MAX .040 A1 0.51 .020 A2 3.94 .125 .155 3.18 В 0.38 0.53 .015 .021 B1 .040 .060 1.02 1.52 С 0.38 .009 .015 0.23 D 2.050 2.070 52.07 52.58 Ε 15.24 15.75 .600 .620 .100 TYP E1 13.59 .59 14.22 2.54 TYP .535 e .660 eA 15.49 16.76 .610 3.81 .120 .150 L 3.05 Q1 1.91 .075 1.40 .055 S .060 1.52 2.29 .090

Figure 67. 40-Pin PDIP Package Diagram

CONTROLLING DIMENSIONS : INCH

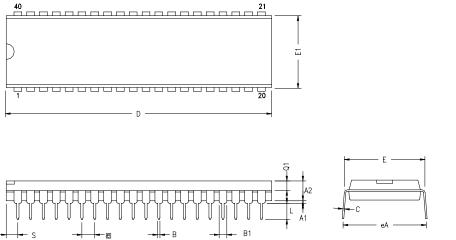

Figure 68. 48-Pin SSOP Package Design

**Note:** Check with ZiLOG on the actual bonding diagram and coordinate for chip-on-board assembly.

>

93

For fast results, contact your local ZiLOG sales office for assistance in ordering the part desired.

#### Codes

ZG = ZiLOG General Purpose Family

P = OTP

- 323 = Family Designation

- L = Voltage Range

2V to 3.6V

T = Temperature Range:

S = 0 to 70 degrees C (Standard)

- E = -40 to +105 degrees C (Extended)

- A = -40 to +125 degrees C (Automotive)

- P = Package Type:

- K = Windowed Cerdip

- P = PDIP

- H = SSOP

- S = SOIC

- ## = Number of Pins

- CC = Memory Size

- M = Packaging Options

- C = Non Lead-Free

- G = Lead-Free

- E = CDIP