Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Obsolete                                                                  |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM7®                                                                     |

| Core Size                  | 16/32-Bit                                                                 |

| Speed                      | 36MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                |

| Number of I/O              | 80                                                                        |

| Program Memory Size        | 128KB (128K x 8)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 6K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.55V ~ 1.8V                                                              |

| Data Converters            | A/D 4x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 128-LQFP                                                                  |

| Supplier Device Package    | 128-LQFP (20x14)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at91sam7l128-au |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 6. I/O Line Considerations

## 6.1 JTAG Port Pins

TMS, TDI and TCK are schmitt trigger inputs. TMS, TDI and TCK do not integrate a pull-up resistor.

TDO is an output, driven at up to VDDIO, and has no pull-up resistor.

The JTAGSEL pin is used to select the JTAG boundary scan when asserted at a high level. The JTAGSEL pin integrates a permanent pull-down resistor of about 115 KOND, so that it can be left unconnected for norma operations.

## 6.2 Test Pin

The TST pin is used for manufacturing test or fast programming mode of the AT91SAM7L128/64 when ass high. The TST pin integrates a permanent pull-down resistor of aboutt05GND, so that it can be left unconnected for normal operations.

To enter fast programming mode, the TST and CLKIN pins must be tied high while FWUP is tied low.

## 6.3 NRST Pin

The NRST pin is bidirectional. It is handled by the on-chip reset controller and can be driven low to provide a signal to the external components or asserted low externally to reset the microcontroller. There is no const the length of the reset pulse and the reset controller can guarantee a minimum pulse length.

The NRST pin integrates a permanent pull-up resistor to VDDIO1 of about. 100 k

## 6.4 NRSTB Pin

The NRSTB pin is input only and enables asynchronous reset of the AT91SAM7L128/64 when asserted low. NRSTB pin integrates a permanent pull-up resistor of about. This allows connection of a simple push button on the NRBST pin as a system-user reset.

In all modes, this pin will reset the chip. It can be used as an external system reset source.

In harsh environments, it is recommended to add an external capacitor (10 nF) between NRSTB and VDDIO1.

NRSTB pin must not be connected to VDDIO1. There must not be an external pull-up on NRSTB.

## 6.5 ERASE Pin

The ERASE pin is used to reinitialize the Flash content **aor**he of its NVM bits. It integrates a permanent pull down resistor of about 15 the GND, so that it can be left unconnected for normal operations.

This pin is debounced by SCLK to improve the glitch tolerance. When the ERASE pin is tied high during less t 100 ms, it is not taken into account. The pin must be tied high during more than 220 ms to perform the re tion of the Flash.

## 6.6 PIO Controller Lines

All the I/O lines; PAO to PA25, PBO to PB23, PCO to PC29 integrate a programmable pull-up resistor. Program of this pull-up resistor is performed independently for each I/O line through the PIO controllers. All I/Os hav schmitt triggers.

Typical pull-up value is 100 k

Maximum frequency is:

36 MHz under 25 pF of load on PIOC

36 MHz under 25 pF of load on PIOA and PIOB

# 10.4 PIO Controller A Multiplexing

| Table 10-2. | Multiplexing on PIO Controller A |

|-------------|----------------------------------|

|-------------|----------------------------------|

| PIO Controller A |              |              |                | Application Usage |          |

|------------------|--------------|--------------|----------------|-------------------|----------|

| I/O Line         | Peripheral A | Peripheral B | Extra Function | Function          | Comments |

| PAO              |              |              | СОМО           |                   |          |

| PA1              |              |              | COM1           |                   |          |

| PA2              |              |              | COM2           |                   |          |

| PA3              |              |              | COM3           |                   |          |

| PA4              |              |              | COM4           |                   |          |

| PA5              |              |              | COM5           |                   |          |

| PA6              |              |              | SEGO           |                   |          |

| PA7              |              |              | SEG1           |                   |          |

| PA8              |              |              | SEG2           |                   |          |

| PA9              |              |              | SEG3           |                   |          |

| PA10             |              |              | SEG4           |                   |          |

| PA11             |              |              | SEG5           |                   |          |

| PA12             |              |              | SEG6           |                   |          |

| PA13             |              |              | SEG7           |                   |          |

| PA14             |              |              | SEG8           |                   |          |

| PA15             |              |              | SEG9           |                   |          |

| PA16             |              |              | SEG10          |                   |          |

| PA17             |              |              | SEG11          |                   |          |

| PA18             |              |              | SEG12          |                   |          |

| PA19             |              |              | SEG13          |                   |          |

| PA20             |              |              | SEG14          |                   |          |

| PA21             |              |              | SEG15          |                   |          |

| PA22             |              |              | SEG16          |                   |          |

| PA23             |              |              | SEG17          |                   |          |

| PA24             |              |              | SEG18          |                   |          |

| PA25             |              |              | SEG19          |                   |          |

## 13.4.1 Reset Controller Control Register

| Name:        | RSTC_C  | CR   |    |        |        |    |         |

|--------------|---------|------|----|--------|--------|----|---------|

| Access Type: | Write-c | only |    |        |        |    |         |

| 31           | 30      | 29   | 28 | 27     | 26     | 25 | 24      |

|              |         |      | KI | ΞΥ     |        |    |         |

| 23           | 22      | 21   | 20 | 19     | 18     | 17 | 16      |

|              |         |      |    |        |        |    |         |

| 15           | 14      | 13   | 12 | 11     | 10     | 9  | 8       |

|              |         |      |    |        |        |    |         |

| 7            | 6       | 5    | 4  | 3      | 2      | 1  | 0       |

|              |         |      |    | EXTRST | PERRST |    | PROCRST |

|              |         | •    | •  |        |        |    | •       |

PROCRST: Processor Reset

O = No effect.

1 = If KEY is correct, resets the processor.

PERRST: Peripheral Reset

O = No effect.

1 = If KEY is correct, resets the peripherals.

EXTRST: External Reset

O = No effect.

1 = If KEY is correct, asserts the NRST pin.

KEY: Password

Should be written at value 0xA5. Writing any other value in this field aborts the write operation.

the source of the access leading to the last abort (bits MST\_EMAC, MST\_PDC and MST\_ARM) whether or not an abort occurred for each master since the last read of the register (bits SVMST\_EMAC, SVMST\_PDC and SVMST\_ARM) unless this information is loaded in MST bits

In the case of a Data Abort from the processor, the address of the data access is stored. This is useful, as sing for which address generated the abort would require disassembling the instructions and full knowledge processor context.

In the case of a Prefetch Abort, the address may have changed, as the prefetch abort is pipelined in the ARM cessor. The ARM processor takes the prefetch abort into account only if the read instruction is executed a

Each wake-up input pin can be enabled to generate a Fast Startup event by writing at 1 the corresponding be Fast Startup Mode Register SUPC\_FSMR. Only a low level on the enabled wake-up input pins generates a F Startup.

The user interface does not provide any status for Fast Startup, but the user can easily recover this information reading the PIO Controller.

## 25.7 Programming Sequence

1. Checking the Main Oscillator Frequency (Optional):

#### Debug Unit Chip ID Extension Register 26.5.11 DBGU EXID Name:

| Nume:        | 0000_  |      |    |    |    |    |    |

|--------------|--------|------|----|----|----|----|----|

| Access Type: | Read-o | only |    |    |    |    |    |

| 31           | 30     | 29   | 28 | 27 | 26 | 25 | 24 |

|              |        |      | EX | ID |    |    |    |

| 23           | 22     | 21   | 20 | 19 | 18 | 17 | 16 |

|              |        |      | EX | ID |    |    |    |

| 15           | 14     | 13   | 12 | 11 | 10 | 9  | 8  |

|              | EXID   |      |    |    |    |    |    |

| 7            | 6      | 5    | 4  | 3  | 2  | 1  | 0  |

|              |        |      | EX | ID |    |    |    |

**EXID:** Chip ID Extension

Reads O if the bit EXT in DBGU\_CIDR is O.

#### 26.5.12 Debug Unit Force NTRST Register GU\_FNR Ν

| Name: | DB |

|-------|----|

|       |    |

Access Type: Read-write

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24     |

|----|----|----|----|----|----|----|--------|

|    |    |    |    |    |    |    |        |

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16     |

|    |    |    |    |    |    |    |        |

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8      |

|    |    |    |    |    |    |    |        |

| 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0      |

|    |    |    |    |    |    |    | FNTRST |

**FNTRST: Force NTRST**

O = NTRST of the ARM processor s TAP controller is driven by the power\_on\_reset signal.

1 = NTRST of the ARM processor s TAP controller is held low.

#### 27.6.17 PIO Controller Interrupt Status Register PIO\_ISR

Name:

| Access Type: | Read-or | nly |     |     |     |     |     |

|--------------|---------|-----|-----|-----|-----|-----|-----|

| 31           | 30      | 29  | 28  | 27  | 26  | 25  | 24  |

| P31          | P30     | P29 | P28 | P27 | P26 | P25 | P24 |

| 23           | 22      | 21  | 20  | 19  | 18  | 17  | 16  |

| P23          | P22     | P21 | P20 | P19 | P18 | P17 | P16 |

| 15           | 14      | 13  | 12  | 11  | 10  | 9   | 8   |

| P15          | P14     | P13 | P12 | P11 | P10 | P9  | P8  |

| 7            | 6       | 5   | 4   | 3   | 2   | 1   | 0   |

| P7           | P6      | P5  | P4  | P3  | P2  | P1  | PO  |

PO-P31: Input Change Interrupt Status

O = No Input Change has been detected on the I/O line since PIO\_ISR was last read or since reset.

1 = At least one Input Change has been detected on the I/O line since PIO\_ISR was last read or since reset.

27.6.18 PIO Multi-driver Enable Register

PIO\_MDER

Name:

Access Type: Write-only

| 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  |

|-----|-----|-----|-----|-----|-----|-----|-----|

| P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

| 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

| P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

| 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

| P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| P7  | P6  | P5  | P4  | P3  | P2  | P1  | PO  |

PO-P31: Multi Drive Enable.

O = No effect.

1 = Enables Multi Drive on the I/O line.

1 = It indicates that the TWI\_THR is empty and that data has been transmitted and acknowledged.

If TXRDY is high and if a NACK has been detected, the transmission will be stopped. Thus when TRDY = NACK = 1,  $\cdot$  programmer must not fill TWI\_THR to avoid losing it.

*TXRDY behavior in Slave mode*can be seen in Figure 29-24 on page 3,3Figure 29-27 on page 33F3gure 29-29 on page 335 and figure 29-30 on page 335

SVREAD: Slave Read (automatically set / reset)

This bit is only used in Slave mode. When SVACC is low (no Slave access has been detected) SVREAD is irrelevant.

$\mathsf{O}$  = Indicates that a write access is performed by a Master.

1 = Indicates that a read access is performed by a Master.

SVREAD behavior can be seen inFigure 29-24 on page 3,3F1gure 29-25 on page 3,3F1gure 29-29 on page 33abd Figure 29-30 on page 335

SVACC: Slave Access (automatically set / reset) This bit is only used in Slave mode.

O = TWI is not addressed. SVACC is automatically cleared after a NACK or a STOP condition is detected.

1 = Indicates that the address decoding sequence has matched (A Master has sent SADR). SVACC remains high un NACK or a STOP condition is detected.

SVACC behavior can be seen inFigure 29-24 on page 3,3F1gure 29-25 on page 331, Figure 29-29 on page 335 ure 29-30 on page 335

GACC: General Call Access (clear on read) This bit is only used in Slave mode.

O = No General Call has been detected.

1 = A General Call has been detected. After the detection of General Call, the programmer decoded the commands th low and the programming sequence.

GACC behavior can be seen in Figure 29-26 on page .332

OVRE: Overrun Error (clear on read) This bit is only used in Master mode.

O = TWI\_RHR has not been loaded while RXRDY was set

1 = TWI\_RHR has been loaded while RXRDY was set. Reset by read in TWI\_SR when TXCOMP is set.

NACK: Not Acknowledged (clear on read) NACK used in Master mode

O = Each data byte has been correctly received by the far-end side TWI slave component.

1 = A data byte has not been acknowledged by the slave component. Set at the same time as TXCOMP.

## NACK used in Slave Read mode

O = Each data byte has been correctly received by the Master.

1 = In read mode, a data byte has not been acknowledged by the Master. When NACK is set the programmer must TWI\_THR even if TXRDY is set, because it means that the Master will stop the data transfer or re initiate it.

Note that in Slave Write mode all data are acknowledged by the TWI.

## 32.3 I/O Lines Description

Each channel outputs one waveform on one external I/O line.

| Table 32-1. | I/O Line Description |

|-------------|----------------------|

|-------------|----------------------|

| Name | Description                       | Туре   |

|------|-----------------------------------|--------|

| PWMx | PWM Waveform Output for channel x | Output |

### 32.4 Product Dependencies

### 32.4.1 I/O Lines

The pins used for interfacing the PWM may be multiplexed with PIO lines. The programmer must first program PIO controller to assign the desired PWM pins to their peripheral function. If I/O lines of the PWM are not us the application, they can be used for other purposes by the PIO controller.

All of the PWM outputs may or may not be enableed af pplication requires only four channels, then only four PIO lines will be assigned to PWM outputs.

### 32.4.2 Power Management

The PWM is not continuously clocked. The programmerst first enable the PWM clock in the Power Management Controller (PMC) before using the PWM. However, if the application does not require PWM operations PWM clock can be stopped when not needed and be restarted later. In this case, the PWM will resume its o tions where it left off.

Configuring the PWM does not require the PWM clock to be enabled.

### 32.4.3 Interrupt Sources

The PWM interrupt line is connected on one of the internal sources of the Advanced Interrupt Controller. Usin PWM interrupt requires the AIC to be programmed first. Note that it is not recommended to use the PWM in line in edge sensitive mode.

### 32.5 Functional Description

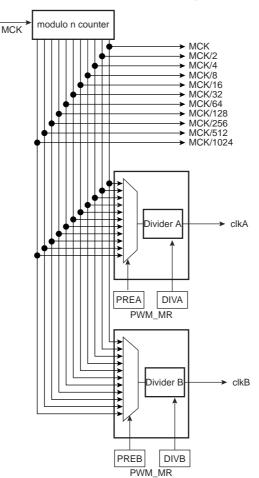

The PWM macrocell is primarily composed of a clock generator module and annels.

Clocked by the system clock, MCK, the clock generator module provides 13 clocks.

Each channel can independently choose one of the clock generator outputs.

Each channel generates an output waveform with attributes that can be defined independently for each channel through the user interface registers.

Figure 32-2. Functional View of the Clock Generator Block Diagram

Caution: Before using the PWM macrocell, the programmer must first enable the PWM clock in the Power Magement Controller (PMC).

The PWM macrocell master clock, MCK, is divided in the clock generator module to provide different clocks a able for all channels. Each channel can independently select one of the divided clocks.

The clock generator is divided in three blocks:

a modulo n counter which provides 11 clocks;  $F_{MCK}/2$ ,  $F_{MCK}/4$ ,  $F_{MCK}/8$ ,  $F_{MCK}/16$ ,  $F_{MCK}/32$ ,  $F_{MCK}/64$ ,  $F_{MCK}/128$ ,  $F_{MCK}/256$ ,  $F_{MCK}/512$ ,  $F_{MCK}/1024$

two linear dividers (1, 1/2, 1/3, ... 1/255) that provide two separate clocks: clkA and clkB

Each linear divider can independently divide one of the clocks of the modulo n counter. The selection of the of to be divided is made according to the PREA (PREB) field of the PWM Mode register (PWM\_MR). The result clock clkA (clkB) is the clock selected divided by DIVA (DIVB) field value in the PWM Mode register (PWM\_MR).

After a reset of the PWM controller, DIVA (DIVB) and PREA (PREB) in the PWM Mode register are set to 0. Timplies that after reset clkA (clkB) are turned off.

At reset, all clocks provided by the modulo n counter **aned** off except clock clk. This situation is also true when the PWM master clock is turned off through the Power Management Controller.

## 35.3.2.2 High Frequency

| Mode                                            | Conditions                                                                                                                                                                                                                    | VDDIO1<br>Consumption                                                                                                                     | Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Unit |

|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Active<br>(AT91SAM7L128/64)<br>(See Figure 35-₿ | Voltage regulator in Normal Mode<br>VDDOUT = 1.80V<br>RTC ON<br>Programmable BOD ON (Continuous)<br>Charge pump ON<br>LCD Regulator ON<br>Flash is read<br>ADC ON<br>All peripheral clocks activated<br>RC 2MHz OFF<br>PLL ON | 3.346<br>5.37<br>10.37<br>11.16<br>12.13<br>14.24<br>19.55<br>22.63<br>3.34<br>5.39<br>10.39<br>11.22<br>12.21<br>14.35<br>19.55<br>22.66 | VDDIO1= 3V @ 25°C<br>ARM core clock = 4 MHz<br>ARM core clock = 8 MHz<br>ARM core clock = 16 MHz<br>ARM core clock = 16 MHz<br>ARM core clock = 20 MHz<br>ARM core clock = 20 MHz<br>ARM core clock = 24 MHz<br>ARM core clock = 30 MHz<br>ARM core clock = 36 MHz<br>VDDIO1= 3V @ 85°C<br>ARM core clock = 4 MHz<br>ARM core clock = 4 MHz<br>ARM core clock = 16 MHz<br>ARM core clock = 16 MHz<br>ARM core clock = 18 MHz<br>ARM core clock = 20 MHz<br>ARM core clock = 20 MHz<br>ARM core clock = 30 MHz<br>ARM core clock = 30 MHz<br>ARM core clock = 30 MHz<br>ARM core clock = 36 MHz | mA   |

| Active<br>(AT91SAM7L128/64)<br>(See Figure 35-9 | Voltage regulator in Normal Mode<br>VDDOUT = 1.55V<br>RTC ON<br>Programmable BOD ON (Continuous)<br>Charge pump ON<br>LCD Regulator ON<br>Flash is read<br>ADC ON<br>All peripheral clocks activated<br>RC 2MHz OFF<br>PLL ON | 2.73<br>4.47<br>8.55<br>9.23<br>10.1<br>11.9<br>16<br>18.6<br>2.76<br>4.52<br>8.62<br>9.33<br>10.21<br>12.04<br>16.07<br>18.75            | VDDIO1= 3V @ 25°C<br>ARM core clock = 4 MHz<br>ARM core clock = 8 MHz<br>ARM core clock = 16 MHz<br>ARM core clock = 16 MHz<br>ARM core clock = 20 MHz<br>ARM core clock = 20 MHz<br>ARM core clock = 24 MHz<br>ARM core clock = 30 MHz<br>ARM core clock = 36 MHz<br>VDDIO1= 3V @ 85°C<br>ARM core clock = 4 MHz<br>ARM core clock = 4 MHz<br>ARM core clock = 8 MHz<br>ARM core clock = 16 MHz<br>ARM core clock = 18 MHz<br>ARM core clock = 20 MHz<br>ARM core clock = 20 MHz<br>ARM core clock = 24 MHz<br>ARM core clock = 30 MHz<br>ARM core clock = 30 MHz<br>ARM core clock = 36 MHz  | mA   |

Table 35-10. High-range Frequencies, Active Mode (Peripheral Activated)

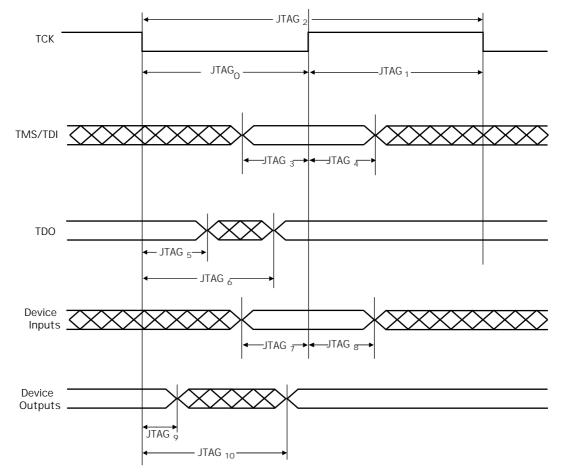

## 35.10.5.2 JTAG Interface Signals

| Symbol            | Parameter                      | Conditions | Min | Max | Units |

|-------------------|--------------------------------|------------|-----|-----|-------|

| JTAG <sub>o</sub> | TCK Low Half-period            | (1)        | 6.5 |     | ns    |

| JTAG 1            | TCK High Half-period           | (1)        | 5.5 |     | ns    |

| JTAG <sub>2</sub> | TCK Period                     | (1)        | 12  |     | ns    |

| JTAG 3            | TDI, TMS Setup before TCK High | (1)        | 2   |     | ns    |

| JTAG 4            | TDI, TMS Hold after TCK High   | (1)        | 3   |     | ns    |

| JTAG 5            | TDO Hold Time                  | (1)        | 4   |     | ns    |

| JTAG <sub>6</sub> | TCK Low to TDO Valid           | (1)        |     | 16  | ns    |

| JTAG 7            | Device Inputs Setup Time       | (1)        | 0   |     | ns    |

| JTAG <sub>8</sub> | Device Inputs Hold Time        | (1)        | 3   |     | ns    |

| JTAG <sub>9</sub> | Device Outputs Hold Time       | (1)        | 6   |     | ns    |

| JTAG 10           | TCK to Device Outputs Valid    | (1)        |     | 18  | ns    |

### Table 35-38. JTAG Interface Timing specification

Note: 1.  $V_{VDDIO}$  from 3.0V to 3.6V, maximum external capacitor = 40pF.

Figure 35-18.JTAG Interface Signals