Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| 2011.12                    |                                                              |

|----------------------------|--------------------------------------------------------------|

| Product Status             | Active                                                       |

| Core Processor             | S12Z                                                         |

| Core Size                  | 16-Bit                                                       |

| Speed                      | 32MHz                                                        |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SCI, SPI                   |

| Peripherals                | DMA, LCD, POR, PWM, WDT                                      |

| Number of I/O              | 73                                                           |

| Program Memory Size        | 32KB (32K x 8)                                               |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 2K x 8                                                       |

| RAM Size                   | 2K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                  |

| Data Converters            | A/D 4x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                            |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 100-LQFP                                                     |

| Supplier Device Package    | 100-LQFP (14x14)                                             |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=s912zvhy32f1cll |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 1.9.1.2 Special Single-Chip Mode

This mode is used for debugging operation, boot-strapping, or security related operations. The background debug mode BDM is active on leaving reset in this mode.

## 1.9.2 Debugging Modes

The background debug mode (BDM) can be activated by the BDC module or directly when resetting into

Special Single-Chip mode. Detailed information can be found in the BDC module section.

Writing to internal memory locations using the debugger, whilst code is running or at a breakpoint, can

change the flow of application code.

The MC9S12ZVHY/MC9S12ZVHL Families supports BDC communication throughout the device Stop mode. During Stop

mode, writes to control registers can alter the operation and lead to unexpected results. It is thus

recommended not to reconfigure the peripherals during STOP using the debugger.

### 1.9.3 Low Power Modes

The device has two dynamic-power modes (run and wait) and two static low-power modes stop and pseudo stop). For a detailed description refer to Chapter 7, "S12 Clock, Reset and Power Management Unit (S12CPMU\_UHV\_V5).

- Dynamic power mode: Run

- Run mode is the main full performance operating mode with the entire device clocked. The user can configure the device operating speed through selection of the clock source and the phase locked loop (PLL) frequency. To save power, unused peripherals must not be enabled.

- Dynamic power mode: Wait

- This mode is entered when the CPU executes the WAI instruction. In this mode the CPU does not execute instructions. The internal CPU clock is switched off. All peripherals can be active in system wait mode. For further power consumption reduction, the peripherals can individually turn off their local clocks. Asserting RESET, XIRQ, IRQ, or any other interrupt that is not masked ends system wait mode.

- Static power mode Pseudo-stop:

- In this mode the system clocks are stopped but the oscillator is still running and the real time interrupt (RTI), watchdog (COP), RTC, LCD and Autonomous Periodic Interrupt (API) may be enabled. Other peripherals are turned off. This mode consumes more current than system STOP mode but, as the oscillator continues to run, the full speed wake up time from this mode is significantly shorter.

- Static power mode: Stop

- The oscillator is stopped in this mode. By default, clocks are switched off and the counters and dividers remain frozen. The Autonomous Periodic Interrupt (API), Key Wake-Up, RTC, CAN and the CAN physical layer transceiver modules may be enabled to wake the device.

## 1.12 COP Configuration

The COP time-out rate bits CR[2:0] and the WCOP bit in the CPMUCOP register are loaded from the Flash configuration field byte at global address 0xFF\_FE0E during the reset sequence. See Table 1-12 and Table 1-13 for coding

| NV[2:0] in<br>FOPT Register | CR[2:0] in<br>COPCTL Register |

|-----------------------------|-------------------------------|

| 000                         | 111                           |

| 001                         | 110                           |

| 010                         | 101                           |

| 011                         | 100                           |

| 100                         | 011                           |

| 101                         | 010                           |

| 110                         | 001                           |

| 111                         | 000                           |

#### Table 1-12. Initial COP Rate Configuration

#### Table 1-13. Initial WCOP Configuration

| NV[3] in<br>FOPT Register | WCOP in<br>COPCTL Register |

|---------------------------|----------------------------|

| 1                         | 0                          |

| 0                         | 1                          |

## 1.13 ADC0 Internal Channels

Table 1-14 lists the internal sources which are connected to these special conversion channels.

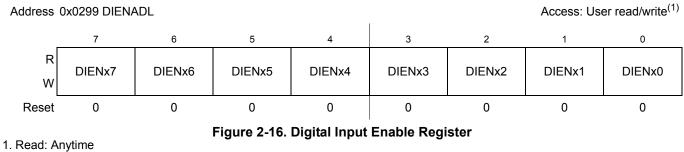

## 2.3.2.14 Digital Input Enable Register

Write: Anytime

| Field        | Description                                                                                                                                                                                                                                     |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0<br>DIENx | Digital Input Enable — Input buffer control                                                                                                                                                                                                     |

|              | This bit controls the digital input function. If set to 1 the input buffers are enabled and the pin can be used with the digital function. If the pin is used with an analog function this bit shall be cleared to avoid shoot-through current. |

|              | 1 Associated pin is configured as digital input<br>0 Associated pin digital input is disabled                                                                                                                                                   |

Chapter 2 Port Integration Module (S12ZVHYPIMV1)

#### 2.3.2.15 **Pull Device Enable Register**

|                             | 0x0226 PERA                                                                                                                                                                                     |       |       |       |       |       | Access: Use | er read/write <sup>(1)</sup> |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------------|------------------------------|

|                             | 0x0227 PERB<br>0x0246 PERC<br>0x0247 PERD<br>0x0266 PERE<br>0x0267 PERF<br>0x0287 PERA<br>0x02C3 PERT<br>0x02D3 PERS<br>0x02F3 PERP<br>0x0303 PERH<br>0x0313 PERJ<br>0x0323 PERG<br>0x0353 PERU | DL    |       |       |       |       |             |                              |

| _                           | 7                                                                                                                                                                                               | 6     | 5     | 4     | 3     | 2     | 1           | 0                            |

| R<br>W                      | PERx7                                                                                                                                                                                           | PERx6 | PERx5 | PERx4 | PERx3 | PERx2 | PERx1       | PERx0                        |

| Reset                       |                                                                                                                                                                                                 |       |       |       |       |       |             |                              |

| Ports B, E:                 | 0                                                                                                                                                                                               | 0     | 0     | 0     | 1     | 1     | 1           | 1                            |

| Ports C, P T,<br>ADL, J, U: | 0                                                                                                                                                                                               | 0     | 0     | 0     | 0     | 0     | 0           | 0                            |

| Others:                     | 1                                                                                                                                                                                               | 1     | 1     | 1     | 1     | 1     | 1           | 1                            |

| 1 Deed Aputin               | Figure 2-17. Pull Device Enable Register                                                                                                                                                        |       |       |       |       |       |             |                              |

1. Read: Anytime Write: Anytime

# Table 2-15. Pull Device Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0<br>PERx | Pull Enable — Activate pull device on input pin                                                                                                                                                                                                                                                            |

|             | This bit controls whether a pull device on the associated port input or open-drain output pin is active. If a pin is used as push-pull output this bit has no effect. The polarity is selected by the related polarity select register bit. On open-drain output pins only a pullup device can be enabled. |

|             | 1 Pull device enabled<br>0 Pull device disabled                                                                                                                                                                                                                                                            |

Chapter 5 Background Debug Controller (S12ZBDCV2)

## 5.4.11 Serial Communication Timeout

The host initiates a host-to-target serial transmission by generating a falling edge on the BKGD pin. If BKGD is kept low for more than 128 target clock cycles, the target understands that a SYNC command was issued. In this case, the target waits for a rising edge on BKGD in order to answer the SYNC request pulse. When the BDC detects the rising edge a soft reset is generated, whereby the current BDC command is discarded. If the rising edge is not detected, the target keeps waiting forever without any timeout limit.

If a falling edge is not detected by the target within 512 clock cycles since the last falling edge, a timeout occurs and the current command is discarded without affecting memory or the operating mode of the MCU. This is referred to as a soft-reset. This timeout also applies if 512 cycles elapse between 2 consecutive ERASE\_FLASH commands. The soft reset is disabled whilst the internal flash mass erase operation is pending completion.

timeouts are also possible if a BDC command is partially issued, or data partially retrieved. Thus if a time greater than 512 BDCSI clock cycles is observed between two consecutive negative edges, a soft-reset occurs causing the partially received command or data retrieved to be discarded. The next negative edge at the BKGD pin, after a soft-reset has occurred, is considered by the target as the start of a new BDC command, or the start of a SYNC request pulse.

## 5.5 Application Information

## 5.5.1 Clock Frequency Considerations

Read commands without status and without ACK must consider the frequency relationship between BDCSI and the internal core clock. If the core clock is slow, then the internal access may not have been carried out within the standard 16 BDCSI cycle delay period (DLY). The host must then extend the DLY period or clock frequencies accordingly. Taking internal clock domain synchronizers into account, the minimum number of BDCSI periods required for the DLY is expressed by:

#DLY > 3(f<sub>(BDCSI clock)</sub> / f<sub>(core clock)</sub>) + 4

and the minimum core clock frequency with respect to BDCSI clock frequency is expressed by

Minimum  $f_{(core clock)} = (3/(\#DLY cycles -4))f_{(BDCSI clock)}$

For the standard 16 period DLY this yields  $f_{(core clock)} \ge (1/4) f_{(BDCSI clock)}$

#### Chapter 6 S12Z Debug (S12ZDBGV2) Module

Write: Bit 7 Anytime with the exception that it cannot be set if PTACT is set. An ongoing profiling session must be finished before DBG can be armed again.

Bit 6 can be written anytime but always reads back as 0.

Bits 5:0 anytime DBG is not armed and PTACT is clear.

### NOTE

On a write access to DBGC1 and simultaneous hardware disarm from an internal event, the hardware disarm has highest priority, clearing the ARM bit and generating a breakpoint, if enabled.

#### NOTE

When disarming the DBG by clearing ARM with software, the contents of bits[5:0] are not affected by the write, since up until the write operation, ARM = 1 preventing these bits from being written. These bits must be cleared using a second write if required.

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>ARM    | <ul> <li>Arm Bit — The ARM bit controls whether the DBG module is armed. This bit can be set and cleared by register writes and is automatically cleared when the state sequencer returns to State0 on completing a debugging session. On setting this bit the state sequencer enters State1.</li> <li>0 Debugger disarmed. No breakpoint is generated when clearing this bit by software register writes.</li> <li>1 Debugger armed</li> </ul> |

| 6<br>TRIG   | <ul> <li>Immediate Trigger Request Bit — This bit when written to 1 requests an immediate transition to final state independent of comparator status. This bit always reads back a 0. Writing a 0 to this bit has no effect.</li> <li>0 No effect.</li> <li>1 Force state sequencer immediately to final state.</li> </ul>                                                                                                                      |

| 4<br>BDMBP  | <ul> <li>Background Debug Mode Enable — This bit determines if a CPU breakpoint causes the system to enter Background Debug Mode (BDM) or initiate a Software Interrupt (SWI). If this bit is set but the BDC is not enabled, then no breakpoints are generated.</li> <li>0 Breakpoint to Software Interrupt if BDM inactive. Otherwise no breakpoint.</li> <li>1 Breakpoint to BDM, if BDC enabled. Otherwise no breakpoint.</li> </ul>        |

| 3<br>BRKCPU | <b>CPU Breakpoint Enable</b> — The BRKCPU bit controls whether the debugger requests a breakpoint to CPU upon transitions to State0. If tracing is enabled, the breakpoint is generated on completion of the tracing session. If tracing is not enabled, the breakpoint is generated immediately. Please refer to Section 6.4.7 for further details. 0 Breakpoints disabled 1 Breakpoints enabled                                               |

| 1–0<br>EEVE | <b>External Event Enable</b> — The EEVE bits configure the external event function. Table 6-4 explains the bit encoding.                                                                                                                                                                                                                                                                                                                        |

#### Table 6-4. EEVE Bit Encoding

| EEVE | Description                                                                     |

|------|---------------------------------------------------------------------------------|

| 00   | External event function disabled                                                |

| 01   | External event forces a trace buffer entry if tracing is enabled                |

| 10   | External event is mapped to the state sequencer, replacing comparator channel 3 |

| 11   | External event pin gates trace buffer entries                                   |

#### S12ZVHY/S12ZVHL Family Reference Manual Rev. 1.05

#### Table 6-18. DBGSCR2 Field Descriptions (continued)

| Field            | Description                                                                                                                                                                                                                      |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5–4<br>C2SC[1:0] | Channel 2 State Control.<br>These bits select the targeted next state whilst in State2 following a match2.                                                                                                                       |

| 7–6<br>C3SC[1:0] | Channel 3 State Control.<br>If EEVE !=10, these bits select the targeted next state whilst in State2 following a match3.<br>If EEVE =10, these bits select the targeted next state whilst in State2 following an external event. |

#### Table 6-19. State2 Match State Sequencer Transitions

| CxSC[1:0] | Function                              |

|-----------|---------------------------------------|

| 00        | Match has no effect                   |

| 01        | Match forces sequencer to State1      |

| 10        | Match forces sequencer to State3      |

| 11        | Match forces sequencer to Final State |

In the case of simultaneous matches, the match on the higher channel number (3...0) has priority.

### 6.3.2.9 Debug State Control Register 3 (DBGSCR3)

Address: 0x0109

| _      | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| R<br>W | C3SC1 | C3SC0 | C2SC1 | C2SC0 | C1SC1 | C1SC0 | C0SC1 | C0SC0 |

| Reset  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

#### Figure 6-11. Debug State Control Register 3 (DBGSCR3)

Read: Anytime.

Write: If DBG is not armed and PTACT is clear.

The state control register three selects the targeted next state whilst in State3. The matches refer to the outputs of the comparator match control logic as depicted in Figure 6-1 and described in Section 6.3.2.12". Comparators must be enabled by setting the comparator enable bit in the associated DBGxCTL control register.

| Field     | Description                                                                    |  |  |  |  |  |  |  |  |

|-----------|--------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| 1–0       | Channel 0 State Control.                                                       |  |  |  |  |  |  |  |  |

| C0SC[1:0] | These bits select the targeted next state whilst in State3 following a match0. |  |  |  |  |  |  |  |  |

| 3–2       | Channel 1 State Control.                                                       |  |  |  |  |  |  |  |  |

| C1SC[1:0] | These bits select the targeted next state whilst in State3 following a match1. |  |  |  |  |  |  |  |  |

| 5–4       | Channel 2 State Control.                                                       |  |  |  |  |  |  |  |  |

| C2SC[1:0] | These bits select the targeted next state whilst in State3 following a match2. |  |  |  |  |  |  |  |  |

#### S12ZVHY/S12ZVHL Family Reference Manual Rev. 1.05

frequency as shown in Table 7-3. Setting the VCOFRQ[1:0] bits incorrectly can result in a non functional PLL (no locking and/or insufficient stability).

| VCOCLK Frequency Ranges            | VCOFRQ[1:0] |

|------------------------------------|-------------|

| 32MHz <= f <sub>VCO</sub> <= 48MHz | 00          |

| 48MHz < f <sub>VCO</sub> <= 64MHz  | 01          |

| Reserved                           | 10          |

| Reserved                           | 11          |

Table 7-3. VCO Clock Frequency Selection

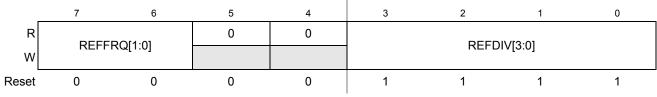

### 7.3.2.3 S12CPMU\_UHV\_V5 Reference Divider Register (CPMUREFDIV)

The CPMUREFDIV register provides a finer granularity for the PLL multiplier steps when using the external oscillator as reference.

Module Base + 0x0005

Figure 7-6. S12CPMU\_UHV\_V5 Reference Divider Register (CPMUREFDIV)

Read: Anytime

Write: If PROT=0 (CPMUPROT register) and PLLSEL=1 (CPMUCLKS register), then write anytime. Else write has no effect.

### NOTE

Write to this register clears the LOCK and UPOSC status bits.

If XOSCLCP is enabled (OSCE=1)  $f_{REF} = \frac{f_{OSC}}{(REFDIV+1)}$ If XOSCLCP is disabled (OSCE=0)  $f_{REF} = f_{IRC1M}$

The REFFRQ[1:0] bits are used to configure the internal PLL filter for optimal stability and lock time. For correct PLL operation the REFFRQ[1:0] bits have to be selected according to the actual REFCLK frequency as shown in Table 7-4.

If IRC1M is selected as REFCLK (OSCE=0) the PLL filter is fixed configured for the 1MHz  $\leq f_{REF} \leq 2MHz$  range. The bits can still be written but will have no effect on the PLL filter configuration.

For OSCE=1, setting the REFFRQ[1:0] bits incorrectly can result in a non functional PLL (no locking and/or insufficient stability).

S12ZVHY/S12ZVHL Family Reference Manual, Rev. 1.05

Chapter 7 S12 Clock, Reset and Power Management Unit (S12CPMU\_UHV\_V5)

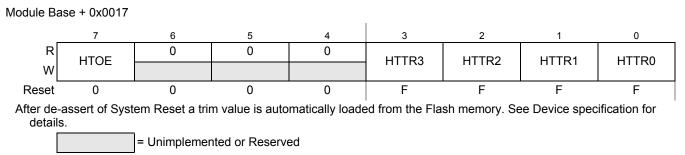

## 7.3.2.20 High Temperature Trimming Register (CPMUHTTR)

The CPMUHTTR register configures the trimming of the S12CPMU\_UHV\_V5 temperature sense.

#### Figure 7-26. High Temperature Trimming Register (CPMUHTTR)

Read: Anytime

Write: Anytime

#### Table 7-25. CPMUHTTR Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                           |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>HTOE        | <ul> <li>High Temperature Offset Enable Bit — If set the temperature sense offset is enabled.</li> <li>0 The temperature sense offset is disabled. HTTR[3:0] bits don't care.</li> <li>1 The temperature sense offset is enabled. HTTR[3:0] select the temperature offset.</li> </ul> |

| 3–0<br>HTTR[3:0] | High Temperature Trimming Bits — See Table 7-26 for trimming effects.                                                                                                                                                                                                                 |

#### Table 7-26. Trimming Effect of HTTR

| HTTR[3:0] | Temperature<br>sensor voltage V <sub>HT</sub> | Interrupt threshold<br>temperatures T <sub>HTIA</sub> and T <sub>HTID</sub> |

|-----------|-----------------------------------------------|-----------------------------------------------------------------------------|

| 0000      | lowest                                        | highest                                                                     |

| 0001      |                                               |                                                                             |

|           | increasing                                    | decreasing                                                                  |

| 1110      |                                               |                                                                             |

| 1111      | highest                                       | lowest                                                                      |

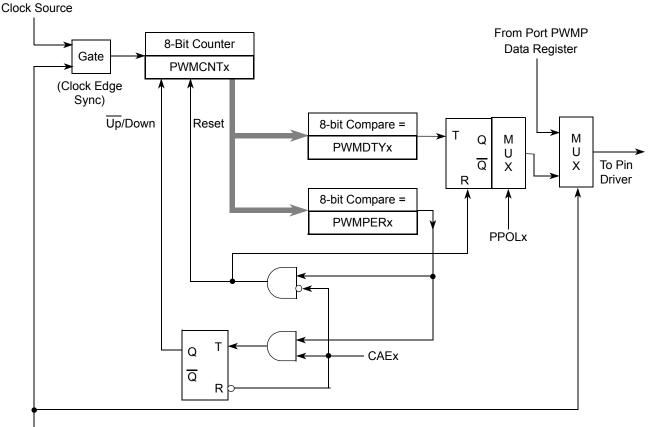

## 9.4.2 PWM Channel Timers

The main part of the PWM module are the actual timers. Each of the timer channels has a counter, a period register and a duty register (each are 8-bit). The waveform output period is controlled by a match between the period register and the value in the counter. The duty is controlled by a match between the duty register and the counter value and causes the state of the output to change during the period. The starting polarity of the output is also selectable on a per channel basis. Shown below in Figure 9-16 is the block diagram for the PWM timer.

PWMEx

Figure 9-16. PWM Timer Channel Block Diagram

### 9.4.2.1 PWM Enable

Each PWM channel has an enable bit (PWMEx) to start its waveform output. When any of the PWMEx bits are set (PWMEx = 1), the associated PWM output signal is enabled immediately. However, the actual PWM waveform is not available on the associated PWM output until its clock source begins its next cycle due to the synchronization of PWMEx and the clock source. An exception to this is when channels are concatenated. Refer to Section 9.4.2.7, "PWM 16-Bit Functions" for more detail.

### NOTE

The first PWM cycle after enabling the channel can be irregular.

Chapter 11 Freescale's Scalable Controller Area Network (S12MSCANV3)

S12ZVHY/S12ZVHL Family Reference Manual Rev. 1.05

### 11.4.4.2 Special System Operating Modes

The MSCAN module behaves as described within this specification in all special system operating modes. Write restrictions which exist on specific registers in normal modes are lifted for test purposes in special modes.

### 11.4.4.3 Emulation Modes

In all emulation modes, the MSCAN module behaves just like in normal system operating modes as described within this specification.

### 11.4.4.4 Listen-Only Mode

In an optional CAN bus monitoring mode (listen-only), the CAN node is able to receive valid data frames and valid remote frames, but it sends only "recessive" bits on the CAN bus. In addition, it cannot start a transmission.

If the MAC sub-layer is required to send a "dominant" bit (ACK bit, overload flag, or active error flag), the bit is rerouted internally so that the MAC sub-layer monitors this "dominant" bit, although the CAN bus may remain in recessive state externally.

### 11.4.4.5 MSCAN Initialization Mode

The MSCAN enters initialization mode when it is enabled (CANE=1).

When entering initialization mode during operation, any on-going transmission or reception is immediately aborted and synchronization to the CAN bus is lost, potentially causing CAN protocol violations. To protect the CAN bus system from fatal consequences of violations, the MSCAN immediately drives TXCAN into a recessive state.

### NOTE

The user is responsible for ensuring that the MSCAN is not active when initialization mode is entered. The recommended procedure is to bring the MSCAN into sleep mode (SLPRQ = 1 and SLPAK = 1) before setting the INITRQ bit in the CANCTL0 register. Otherwise, the abort of an on-going message can cause an error condition and can impact other CAN bus devices.

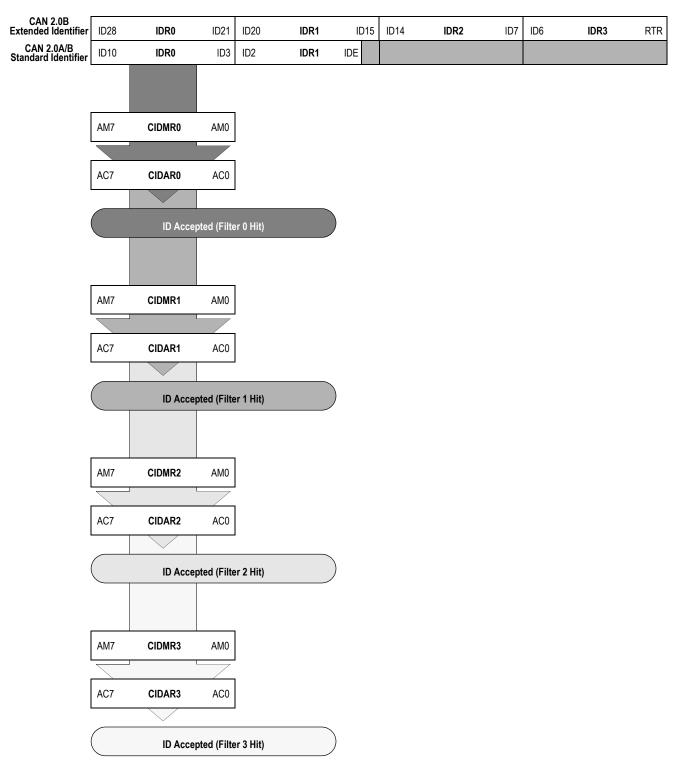

In initialization mode, the MSCAN is stopped. However, interface registers remain accessible. This mode is used to reset the CANCTL0, CANRFLG, CANRIER, CANTFLG, CANTIER, CANTARQ, CANTAAK, and CANTBSEL registers to their default values. In addition, the MSCAN enables the configuration of the CANBTR0, CANBTR1 bit timing registers; CANIDAC; and the CANIDAR, CANIDMR message filters. See Section 11.3.2.1, "MSCAN Control Register 0 (CANCTL0)," for a detailed description of the initialization mode.

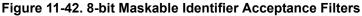

Figure 11-45. Initialization Request/Acknowledge Cycle

Due to independent clock domains within the MSCAN, INITRQ must be synchronized to all domains by using a special handshake mechanism. This handshake causes additional synchronization delay (see Figure 11-45).

If there is no message transfer ongoing on the CAN bus, the minimum delay will be two additional bus clocks and three additional CAN clocks. When all parts of the MSCAN are in initialization mode, the INITAK flag is set. The application software must use INITAK as a handshake indication for the request (INITRQ) to go into initialization mode.

#### NOTE

The CPU cannot clear INITRQ before initialization mode (INITRQ = 1 and INITAK = 1) is active.

### 11.4.5 Low-Power Options

If the MSCAN is disabled (CANE = 0), the MSCAN clocks are stopped for power saving.

If the MSCAN is enabled (CANE = 1), the MSCAN has two additional modes with reduced power consumption, compared to normal mode: sleep and power down mode. In sleep mode, power consumption is reduced by stopping all clocks except those to access the registers from the CPU side. In power down mode, all clocks are stopped and no power is consumed.

Table 11-37 summarizes the combinations of MSCAN and CPU modes. A particular combination of modes is entered by the given settings on the CSWAI and SLPRQ/SLPAK bits.

Chapter 12 Serial Communication Interface (S12SCIV6)

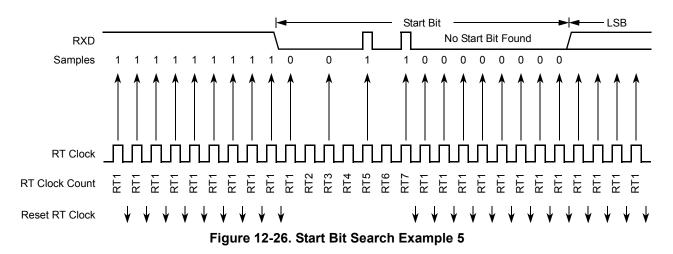

Figure 12-26 shows a burst of noise near the beginning of the start bit that resets the RT clock. The sample after the reset is low but is not preceded by three high samples that would qualify as a falling edge. Depending on the timing of the start bit search and on the data, the frame may be missed entirely or it may set the framing error flag.

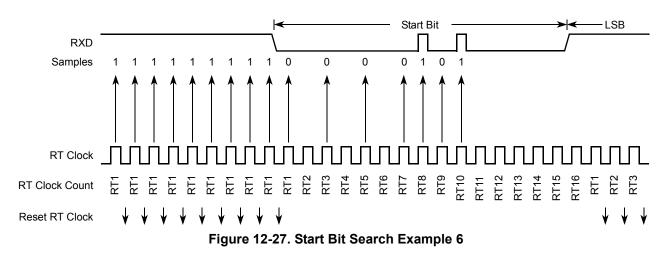

In Figure 12-27, a noise burst makes the majority of data samples RT8, RT9, and RT10 high. This sets the noise flag but does not reset the RT clock. In start bits only, the RT8, RT9, and RT10 data samples are ignored.

## 12.4.6.4 Framing Errors

If the data recovery logic does not detect a logic 1 where the stop bit should be in an incoming frame, it sets the framing error flag, FE, in SCI status register 1 (SCISR1). A break character also sets the FE flag because a break character has no stop bit. The FE flag is set at the same time that the RDRF flag is set.

## 12.5.2 Modes of Operation

### 12.5.2.1 Run Mode

Normal mode of operation.

To initialize a SCI transmission, see Section 12.4.5.2, "Character Transmission".

### 12.5.2.2 Wait Mode

SCI operation in wait mode depends on the state of the SCISWAI bit in the SCI control register 1 (SCICR1).

- If SCISWAI is clear, the SCI operates normally when the CPU is in wait mode.

- If SCISWAI is set, SCI clock generation ceases and the SCI module enters a power-conservation state when the CPU is in wait mode. Setting SCISWAI does not affect the state of the receiver enable bit, RE, or the transmitter enable bit, TE.

If SCISWAI is set, any transmission or reception in progress stops at wait mode entry. The transmission or reception resumes when either an internal or external interrupt brings the CPU out of wait mode. Exiting wait mode by reset aborts any transmission or reception in progress and resets the SCI.

### 12.5.2.3 Stop Mode

The SCI is inactive during stop mode for reduced power consumption. The STOP instruction does not affect the SCI register states, but the SCI bus clock will be disabled. The SCI operation resumes from where it left off after an external interrupt brings the CPU out of stop mode. Exiting stop mode by reset aborts any transmission or reception in progress and resets the SCI.

The receive input active edge detect circuit is still active in stop mode. An active edge on the receive input can be used to bring the CPU out of stop mode.

## 12.5.3 Interrupt Operation

This section describes the interrupt originated by the SCI block. The MCU must service the interrupt requests. Table 12-20 lists the eight interrupt sources of the SCI.

| Interrupt | Source    | Local Enable | Description                                                                                               |

|-----------|-----------|--------------|-----------------------------------------------------------------------------------------------------------|

| TDRE      | SCISR1[7] | TIE          | Active high level. Indicates that a byte was transferred from SCIDRH/L to the transmit shift register.    |

| TC        | SCISR1[6] | TCIE         | Active high level. Indicates that a transmit is complete.                                                 |

| RDRF      | SCISR1[5] | RIE          | Active high level. The RDRF interrupt indicates that received data is available in the SCI data register. |

| OR        | SCISR1[3] |              | Active high level. This interrupt indicates that an overrun condition has occurred.                       |

| IDLE      | SCISR1[4] | ILIE         | Active high level. Indicates that receiver input has become idle.                                         |

Table 12-20. SCI Interrupt Sources

#### S12ZVHY/S12ZVHL Family Reference Manual Rev. 1.05

#### Chapter 13 Serial Peripheral Interface (S12SPIV5)

the SPI system is configured as a slave, the  $\overline{SS}$  pin is a dedicated input pin. Mode fault error doesn't occur in slave mode.

If a mode fault error occurs, the SPI is switched to slave mode, with the exception that the slave output buffer is disabled. So SCK, MISO, and MOSI pins are forced to be high impedance inputs to avoid any possibility of conflict with another output driver. A transmission in progress is aborted and the SPI is forced into idle state.

If the mode fault error occurs in the bidirectional mode for a SPI system configured in master mode, output enable of the MOMI (MOSI in bidirectional mode) is cleared if it was set. No mode fault error occurs in the bidirectional mode for SPI system configured in slave mode.

The mode fault flag is cleared automatically by a read of the SPI status register (with MODF set) followed by a write to SPI control register 1. If the mode fault flag is cleared, the SPI becomes a normal master or slave again.

### NOTE

If a mode fault error occurs and a received data byte is pending in the receive shift register, this data byte will be lost.

## 13.4.7 Low Power Mode Options

### 13.4.7.1 SPI in Run Mode

In run mode with the SPI system enable (SPE) bit in the SPI control register clear, the SPI system is in a low-power, disabled state. SPI registers remain accessible, but clocks to the core of this module are disabled.

### 13.4.7.2 SPI in Wait Mode

SPI operation in wait mode depends upon the state of the SPISWAI bit in SPI control register 2.

- If SPISWAI is clear, the SPI operates normally when the CPU is in wait mode

- If SPISWAI is set, SPI clock generation ceases and the SPI module enters a power conservation state when the CPU is in wait mode.

- If SPISWAI is set and the SPI is configured for master, any transmission and reception in progress stops at wait mode entry. The transmission and reception resumes when the SPI exits wait mode.

- If SPISWAI is set and the SPI is configured as a slave, any transmission and reception in progress continues if the SCK continues to be driven from the master. This keeps the slave synchronized to the master and the SCK.

If the master transmits several bytes while the slave is in wait mode, the slave will continue to send out bytes consistent with the operation mode at the start of wait mode (i.e., if the slave is currently sending its SPIDR to the master, it will continue to send the same byte. Else if the slave is currently sending the last received byte from the master, it will continue to send each previous master byte).

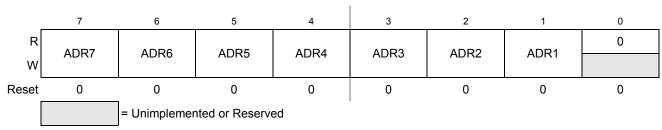

### 14.3.1.1 IIC Address Register (IBAD)

Module Base +0x0000

Read and write anytime

This register contains the address the IIC bus will respond to when addressed as a slave; note that it is not the address sent on the bus during the address transfer.

Table 14-2. IBAD Field Descriptions

| Field           | Description                                                                                                                                                                    |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:1<br>ADR[7:1] | Slave Address — Bit 1 to bit 7 contain the specific slave address to be used by the IIC bus module. The default mode of IIC bus is slave mode for an address match on the bus. |

| 0<br>Reserved   | Reserved — Bit 0 of the IBAD is reserved for future compatibility. This bit will always read 0.                                                                                |

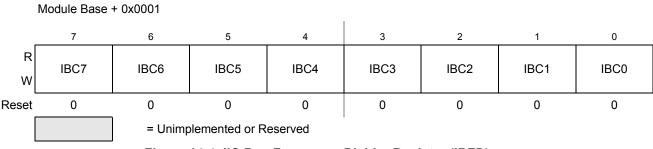

### 14.3.1.2 IIC Frequency Divider Register (IBFD)

#### Figure 14-4. IIC Bus Frequency Divider Register (IBFD)

#### Read and write anytime

#### Table 14-3. IBFD Field Descriptions

| Field           | Description                                                                                                                                                                                                                                                                                                                                                               |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>IBC[7:0] | <b>I Bus Clock Rate 7:0</b> — This field is used to prescale the clock for bit rate selection. The bit clock generator is implemented as a prescale divider — IBC7:6, prescaled shift register — IBC5:3 select the prescaler divider and IBC2-0 select the shift register tap point. The IBC bits are decoded to give the tap and prescale values as shown in Table 14-4. |

Appendix A MCU Electrical Specifications

Appendix H BATS Electrical Specifications

## H.2 Static Electrical Characteristics

#### Table H-2. Static Electrical Characteristics - Supply Voltage Sense - (BATS).

Characteristics noted under conditions  $-40^{\circ}C \le T_J \le 150^{\circ}C^{(1)}$  unless otherwise noted. Typical values noted reflect the approximate parameter mean at  $T_A = 25^{\circ}C^{(2)}$  under nominal conditions unless otherwise noted.

| Num | С | Ratings                                                                                                                                                                             | Symbol                                                            | Min             | Тур              | Мах             | Unit        |

|-----|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-----------------|------------------|-----------------|-------------|

| 1   | Р | Low Voltage Warning (LBI 1)<br>Assert (Measured on selected pin, falling edge)<br>Deassert (Measured on selected pin, rising edge)<br>Hysteresis (measured on selected pin)         | V <sub>LBI1_A</sub><br>V <sub>LBI1_D</sub><br>V <sub>LBI1_H</sub> | 4.75<br>_<br>_  | 5.5<br>-<br>0.4  | 6<br>6.5<br>-   | V<br>V<br>V |

| 2   | Ρ | Low Voltage Warning (LBI 2)<br>Assert (Measured on selected pin, falling edge)<br>Deassert (Measured on selected pin, rising edge)<br>Hysteresis (measured on selected pin)         | V <sub>LBI2_A</sub><br>V <sub>LBI2_D</sub><br>V <sub>LBI2_H</sub> | 6<br>-<br>-     | 6.75<br>_<br>0.4 | 7<br>7.75<br>–  | V<br>V<br>V |

| 3   | Ρ | Low Voltage Warning (LBI 3)<br>Assert (Measured on selected pin, falling edge)<br>Deassert (Measured on selected pin, rising edge)<br>Hysteresis (measured on selected pin)         | V <sub>LBI3_A</sub><br>V <sub>LBI3_D</sub><br>V <sub>LBI3_H</sub> | 7<br>-<br>-     | 7.75<br>-<br>0.4 | 8.5<br>9<br>–   | V<br>V<br>V |

| 4   | Ρ | Low Voltage Warning (LBI 4)<br>Assert (Measured on selected pin, falling edge)<br>Deassert (Measured on selected pin, rising edge)<br>Hysteresis (measured on selected pin)         | V <sub>LBI4_A</sub><br>V <sub>LBI4_D</sub><br>V <sub>LBI4_H</sub> | 8<br><br>       | 9<br>_<br>0.4    | 10<br>10.5<br>- | V<br>V<br>V |

| 5   | Ρ | High Voltage Warning (HBI 1)<br>Assert (Measured on selected pin, rising edge)<br>Deassert (Measured on selected pin, falling edge)<br>Hysteresis (measured on selected pin)        | V <sub>HBI1_A</sub><br>V <sub>HBI1_D</sub><br>V <sub>HBI1_H</sub> | 14.5<br>14<br>- | 16.5<br>_<br>1.0 | 18<br>-<br>-    | V<br>V<br>V |

| 6   | Ρ | High Voltage Warning (HBI 2)<br>Assert (Measured on selected pin, rising edge)<br>Deassert (Measured on selected pin, falling edge)<br>Hysteresis (measured on selected pin)        | V <sub>HBI2_A</sub><br>V <sub>HBI2_D</sub><br>V <sub>HBI2_H</sub> | 25<br>24<br>-   | 27.5<br>-<br>1.0 | 30<br>-<br>-    | V<br>V<br>V |

| 7   | Т | Pin Input Divider Ratio<br>Ratio <sub>VSENSE</sub> = $V_{SENSE} / V_{ADC}^{(3)}$<br>Ratio <sub>VSUP</sub> = $V_{SUP} / V_{ADC}$<br>5.5V < VSENSE < 29 V; 5.5V < VSUP < 29 V         | Ratio <sub>VSENSE</sub><br>Ratio <sub>VSUP</sub>                  | -               | 9<br>9           |                 | -           |

| 8   | С | Analog Input Matching<br>Absolute Error on V <sub>ADC</sub><br>- compared to V <sub>SENSE</sub> / Ratio <sub>VSENSE</sub><br>- compared to V <sub>SUP</sub> / Ratio <sub>VSUP</sub> | Al <sub>Matching</sub>                                            | _               | +-2%             | +-5%            | _           |

| 9   | D | VSENSE Series Resistor<br>Required to be placed externally at VSENSE pin.                                                                                                           | R <sub>VSENSE_R</sub>                                             | 9.5             | 10               | 10.5            | kΩ          |

| 10  | D | VSENSE Impedance<br>If path to ground is enabled.                                                                                                                                   | R <sub>VSEN_IMP</sub>                                             | _               | 350              | _               | kΩ          |

#### 0x0788–0x07BF Reserved

| Address           | Name     |   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------------|----------|---|-------|-------|-------|-------|-------|-------|-------|-------|

| 0x0788-<br>0x07BF | Reserved | R | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

|                   | Reserved | W |       |       |       |       |       |       |       |       |

## 0x07C0-0x07C7 Inter IC Bus (IIC0)

| Address | Name      |        | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2     | Bit 1 | Bit 0  |

|---------|-----------|--------|-------|--------|-------|-------|-------|-----------|-------|--------|

| 0x07C0  | IIC0IBAD  | R<br>W | ADR7  | ADR6   | ADR5  | ADR4  | ADR3  | ADR2      | ADR1  | 0      |

| 0x07C1  | IIC0IBFD  | R<br>W | IBC7  | IBC6   | IBC5  | IBC4  | IBC3  | IBC2      | IBC1  | IBC0   |

| 0x07C2  | IIC0IBCR  | R<br>W | IBEN  | IBIE   | MS/SL | TX/RX | TXAK  | 0<br>RSTA | 0     | IBSWAI |

| 0x07C3  | IIC0IBSR  | R<br>W | TCF   | IAAS   | IBB   | IBAL  | 0     | SRW       | IBIF  | RXAK   |

| 0x07C4  | IIC0IBDR  | R<br>W | D7    | D6     | D5    | D4    | D3    | D2        | D1    | D 0    |

| 0x07C5  | IIC0IBCR2 | R<br>W | GCEN  | ADTYPE | 0     | 0     | 0     | ADR10     | ADR9  | ADR8   |

| 0x07C6  | Reserved  | R<br>W | 0     | 0      | 0     | 0     | 0     | 0         | 0     | 0      |

| 0x07C7  | Reserved  | R<br>W | 0     | 0      | 0     | 0     | 0     | 0         | 0     | 0      |

### 0x07C8–0x07FF Reserved

| Address           | Name     |   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------------|----------|---|-------|-------|-------|-------|-------|-------|-------|-------|

| 0x07C8-<br>0x07FF | Reserved | R | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

|                   |          | W |       |       |       |       |       |       |       |       |