#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | H8S/2600                                                                    |

| Core Size                  | 16-Bit                                                                      |

| Speed                      | 20MHz                                                                       |

| Connectivity               | CANbus, SCI, SmartCard                                                      |

| Peripherals                | Motor Control PWM, POR, PWM, WDT                                            |

| Number of I/O              | 72                                                                          |

| Program Memory Size        | 384KB (384K x 8)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 16K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                 |

| Data Converters            | A/D 12x10b; D/A 2x8b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 128-BFQFP                                                                   |

| Supplier Device Package    | 128-QFP (14x20)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df2630f20v |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 7.2.4 Bus Control Register H (BCRH)

| Bit         | :     | 7     | 6     | 5      | 4      | 3      | 2   | 1   | 0   |

|-------------|-------|-------|-------|--------|--------|--------|-----|-----|-----|

|             |       | ICIS1 | ICIS0 | BRSTRM | BRSTS1 | BRSTS0 |     |     | —   |

| Initial val | lue : | 1     | 1     | 0      | 1      | 0      | 0   | 0   | 0   |

| R/W         | :     | R/W   | R/W   | R/W    | R/W    | R/W    | R/W | R/W | R/W |

BCRH is an 8-bit readable/writable register that selects enabling or disabling of idle cycle insertion, and the memory interface for area 2 to 5, and 0.

BCRH is initialized to H'D0 by a reset and in hardware standby mode. It is not initialized in software standby mode.

**Bit 7—Idle Cycle Insert 1 (ICIS1):** Selects whether or not one idle cycle state is to be inserted between bus cycles when successive external read cycles are performed in different areas.

####

**Bit 6—Idle Cycle Insert 0 (ICIS0):** Selects whether or not one idle cycle state is to be inserted between bus cycles when successive external read and external write cycles are performed.

#### Bit 6

| ICIS0 | Description                                                                                       |

|-------|---------------------------------------------------------------------------------------------------|

| 0     | Idle cycle not inserted in case of successive external read and external write cycles             |

| 1     | Idle cycle inserted in case of successive external read and external write cycles (Initial value) |

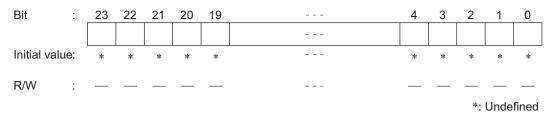

#### 8.2.3 DTC Source Address Register (SAR)

SAR is a 24-bit register that designates the source address of data to be transferred by the DTC. For word-size transfer, specify an even source address.

## 8.2.4 DTC Destination Address Register (DAR)

DAR is a 24-bit register that designates the destination address of data to be transferred by the DTC. For word-size transfer, specify an even destination address.

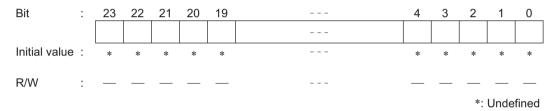

#### 8.2.5 DTC Transfer Count Register A (CRA)

CRA is a 16-bit register that designates the number of times data is to be transferred by the DTC.

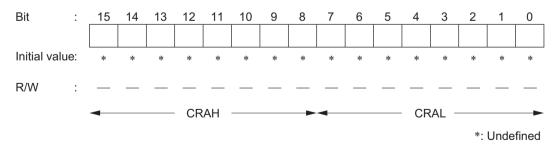

#### 8.3.9 Operation Timing

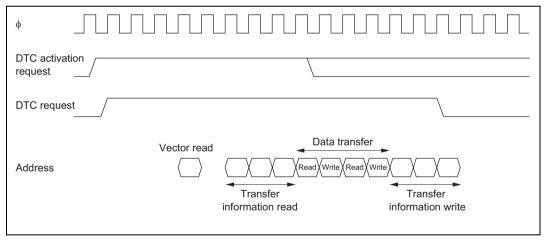

Figures 8-10 to 8-12 show an example of DTC operation timing.

Figure 8-10 DTC Operation Timing (Example in Normal Mode or Repeat Mode)

Figure 8-11 DTC Operation Timing (Example of Block Transfer Mode, with Block Size of 2)

# 8.4 Interrupts

An interrupt request is issued to the CPU when the DTC finishes the specified number of data transfers, or a data transfer for which the DISEL bit was set to 1. In the case of interrupt activation, the interrupt set as the activation source is generated. These interrupts to the CPU are subject to CPU mask level and interrupt controller priority level control.

In the case of activation by software, a software activated data transfer end interrupt (SWDTEND) is generated.

When the DISEL bit is 1 and one data transfer has ended, or the specified number of transfers have ended, after data transfer ends, the SWDTE bit is held at 1 and an SWDTEND interrupt is generated. The interrupt handling routine should clear the SWDTE bit to 0.

When the DTC is activated by software, an SWDTEND interrupt is not generated during a data transfer wait or during data transfer even if the SWDTE bit is set to 1.

# 8.5 Usage Notes

**Module Stop:** When the MSTPA6 bit in MSTPCRA is set to 1, the DTC clock stops, and the DTC enters the module stop state. However, 1 cannot be written in the MSTPA6 bit while the DTC is operating.

**On-Chip RAM:** The MRA, MRB, SAR, DAR, CRA, and CRB registers are all located in on-chip RAM. When the DTC is used, the RAME bit in SYSCR must not be cleared to 0.

**DTCE Bit Setting:** For DTCE bit setting, use bit manipulation instructions such as BSET and BCLR. If all interrupts are masked, multiple activation sources can be set at one time by writing data after executing a dummy read on the relevant register.

| Port   | Description                  | Pins                                                                                                 | Mode 4                                                                       | Mode 5            | Mode 6       | Mode 7                |  |

|--------|------------------------------|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-------------------|--------------|-----------------------|--|

| Port E | • 8-bit I/O                  | PE7/D7                                                                                               | In 8-bit-bus mo                                                              | de: I/O port      |              | I/O port              |  |

|        | port                         | PE6/D6                                                                                               | In 16-bit-bus m                                                              | ode: data bus inj | put/output   |                       |  |

|        | On-chip                      | PE5/D5                                                                                               |                                                                              |                   |              |                       |  |

|        | MOS input<br>pull-up         | PE4/D4                                                                                               |                                                                              |                   |              |                       |  |

|        | pan ap                       | PE3/D3                                                                                               |                                                                              |                   |              |                       |  |

|        |                              | PE2/D2                                                                                               |                                                                              |                   |              |                       |  |

|        |                              | PE1/D1                                                                                               |                                                                              |                   |              |                       |  |

|        |                              | PE0/D0                                                                                               |                                                                              |                   |              |                       |  |

| Port F | • 6-bit I/O                  | PF7/ø                                                                                                | When DDR = 0                                                                 | : input port      |              | When                  |  |

|        | port                         |                                                                                                      | When DDR = 1                                                                 | (after reset):    | output       | DDR = 0 (after        |  |

|        | <ul> <li>Schmitt-</li> </ul> |                                                                                                      |                                                                              |                   |              | reset): input<br>port |  |

|        | triggered<br>input (PF3,     |                                                                                                      |                                                                              |                   |              | When                  |  |

|        | PF0)                         |                                                                                                      |                                                                              |                   |              | DDR = 1: φ            |  |

|        |                              |                                                                                                      |                                                                              |                   |              | output                |  |

|        |                              | PF6/AS                                                                                               | RD, HWR, LWF                                                                 | Routputs          |              | I/O port              |  |

|        |                              | PF5/RD                                                                                               | ADTRG, IRQ3                                                                  | input             |              | ADTRG, IRQ3           |  |

|        |                              | PF4/HWR                                                                                              |                                                                              |                   |              | input                 |  |

|        |                              | PF3/LWR/ADTRG/                                                                                       |                                                                              |                   |              |                       |  |

|        |                              | IRQ3                                                                                                 |                                                                              |                   |              |                       |  |

|        |                              | PF0/IRQ2                                                                                             | IRQ2 input, I/O                                                              | port              |              |                       |  |

| Port H | • 8-bit I/O<br>port          | PH7/PWM1H<br>PH6/PWM1G<br>PH5/PWM1F<br>PH4/PWM1E<br>PH3/PWM1D<br>PH2/PWM1C<br>PH1/PWM1B<br>PH0/PWM1A | Function as bol<br>bit I/O port.                                             | h Motor Control   | PWM Timer ou | itput pins and 8-     |  |

| Port J | • 8-bit I/O<br>port          | PJ7/PWM2H<br>PJ6/PWM2G<br>PJ5/PWM2F<br>PJ4/PWM2E<br>PJ3/PWM2D<br>PJ2/PWM2C<br>PJ1/PWM2B<br>PJ0/PWM2A | Function as both Motor Control PWM Timer output pins and 8-<br>bit I/O port. |                   |              |                       |  |

Notes: 1. Pins for I<sup>2</sup>C bus interface.

$\rm I^2C$  bus interface is available as an option in the H8S/2638, H8S/2639, and H8S/2630.

- 2. The PPG output is not implemented in the H8S/2635 Group.

- 3. The DA output is not implemented in the H8S/2635 Group.

#### Port B MOS Pull-Up Control Register (PBPCR)

| Bit        | :      | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

|            |        | PB7PCR | PB6PCR | PB5PCR | PB4PCR | PB3PCR | PB2PCR | PB1PCR | PB0PCR |

| Initial va | alue : | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| R/W        | :      | R/W    |

PBPCR is an 8-bit readable/writable register that controls the MOS input pull-up function incorporated into port B on an individual bit basis.

In modes 4 to 6, if a pin is in the input state in accordance with the settings in PFCR, in the TPU's TIOR, and in DDR, setting the corresponding PBPCR bit to 1 turns on the MOS input pull-up for that pin.

In mode 7, if a pin is in the input state in accordance with the settings in the TPU's TIOR and in DDR, setting the corresponding PBPCR bit to 1 turns on the MOS input pull-up for that pin.

PBPCR is initialized to H'00 by a reset, and in hardware standby mode. It retains its prior state in software standby mode.

#### Port B Open Drain Control Register (PBODR)

| Bit        | :     | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|

|            |       | PB7ODR | PB6ODR | PB5ODR | PB40DR | PB3ODR | PB2ODR | PB10DR | PB0ODR |

| Initial va | lue : | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| R/W        | :     | R/W    |

PBODR is an 8-bit readable/writable register that controls the PMOS on/off state for each port B pin (PB7 to PB0).

When pins are not address outputs in accordance with the setting of bits AE3 to AE0 in PFCR, setting a PBODR bit makes the corresponding port B pin an NMOS open-drain output, while clearing the bit to 0 makes the pin a CMOS output.

PBODR is initialized to H'00 by a reset, and in hardware standby mode. It retains its prior state in software standby mode.

#### Bit 6—Receive Data Register Full (RDRF): Indicates that the received data is stored in RDR.

| Bit 6 |                                                                                                                                                               |  |  |  |  |  |  |  |  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| RDRF  | F Description                                                                                                                                                 |  |  |  |  |  |  |  |  |

| 0     | [Clearing conditions] (Initial value)                                                                                                                         |  |  |  |  |  |  |  |  |

|       | <ul> <li>When 0 is written to RDRF after reading RDRF = 1</li> </ul>                                                                                          |  |  |  |  |  |  |  |  |

|       | <ul> <li>When the DTC is activated by an RXI interrupt and reads data from RDR</li> </ul>                                                                     |  |  |  |  |  |  |  |  |

| 1     | [Setting condition]                                                                                                                                           |  |  |  |  |  |  |  |  |

|       | When serial reception ends normally and receive data is transferred from RSR to                                                                               |  |  |  |  |  |  |  |  |

|       | RDR                                                                                                                                                           |  |  |  |  |  |  |  |  |

| Note: | RDR and the RDRF flag are not affected and retain their previous values when an error is detected during reception or when the RE bit in SCR is cleared to 0. |  |  |  |  |  |  |  |  |

|       | If reception of the next data is completed while the RDRF flag is still set to 1, an overrun error will occur and the receive data will be lost.              |  |  |  |  |  |  |  |  |

**Bit 5—Overrun Error (ORER):** Indicates that an overrun error occurred during reception, causing abnormal termination.

#### Bit 5

| ORER     | <br>Description                                                                                                                         |                               |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| 0        | [Clearing condition]                                                                                                                    | (Initial value) <sup>*1</sup> |

|          | <ul> <li>When 0 is written to ORER after reading ORER = 1</li> </ul>                                                                    |                               |

| 1        | [Setting condition]                                                                                                                     |                               |

|          | • When the next serial reception is completed while RDRF = 1*                                                                           | :2                            |

| Notes: 1 | The ORER flag is not affected and retains its previous state when cleared to 0.                                                         | the RE bit in SCR is          |

| 2        | The receive data prior to the overrun error is retained in RDR, and subsequently is lost. Also, subsequent serial reception cannot be a |                               |

subsequently is lost. Also, subsequent serial reception cannot be continued while the ORER flag is set to 1. In clocked synchronous mode, serial transmission cannot be continued, either.

#### 13.2.8 Bit Rate Register (BRR)

| Bit           | : | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------------|---|-----|-----|-----|-----|-----|-----|-----|-----|

|               |   |     |     |     |     |     |     |     |     |

| Initial value | : | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

| R/W           | : | R/W |

BRR is an 8-bit register that sets the serial transfer bit rate in accordance with the baud rate generator operating clock selected by bits CKS1 and CKS0 in SMR.

BRR can be read or written to by the CPU at all times.

BRR is initialized to H'FF by a reset and in standby mode.

As baud rate generator control is performed independently for each channel, different values can be set for each channel.

Table 13-3 shows sample BRR settings in asynchronous mode, and table 13-4 shows sample BRR settings in clocked synchronous mode.

|                     |   | φ = 4 M | Hz           | 4 | • = 4.9152 | MHz          |   | φ = 5 N | lHz          |

|---------------------|---|---------|--------------|---|------------|--------------|---|---------|--------------|

| Bit Rate<br>(bit/s) | n | N       | Error<br>(%) | n | N          | Error<br>(%) | n | N       | Error<br>(%) |

| 110                 | 2 | 70      | 0.03         | 2 | 86         | 0.31         | 2 | 88      | -0.25        |

| 150                 | 1 | 207     | 0.16         | 1 | 255        | 0.00         | 2 | 64      | 0.16         |

| 300                 | 1 | 103     | 0.16         | 1 | 127        | 0.00         | 1 | 129     | 0.16         |

| 600                 | 0 | 207     | 0.16         | 0 | 255        | 0.00         | 1 | 64      | 0.16         |

| 1200                | 0 | 103     | 0.16         | 0 | 127        | 0.00         | 0 | 129     | 0.16         |

| 2400                | 0 | 51      | 0.16         | 0 | 63         | 0.00         | 0 | 64      | 0.16         |

| 4800                | 0 | 25      | 0.16         | 0 | 31         | 0.00         | 0 | 32      | -1.36        |

| 9600                | 0 | 12      | 0.16         | 0 | 15         | 0.00         | 0 | 15      | 1.73         |

| 19200               | — | —       | _            | 0 | 7          | 0.00         | 0 | 7       | 1.73         |

| 31250               | 0 | 3       | 0.00         | 0 | 4          | -1.70        | 0 | 4       | 0.00         |

| 38400               | — | —       | —            | 0 | 3          | 0.00         | 0 | 3       | 1.73         |

Table 13-3

BRR Settings for Various Bit Rates (Asynchronous Mode)

#### 14.3.6 Data Transfer Operations

**Initialization:** Before transmitting and receiving data, initialize the SCI as described below. Initialization is also necessary when switching from transmit mode to receive mode, or vice versa.

- [1] Clear the TE and RE bits in SCR to 0.

- [2] Clear the error flags ERS, PER, and ORER in SSR to 0.

- [3] Set the GM, BLK,  $O/\overline{E}$ , BCP1, BCP0, CKS1, CKS0 bits in SMR. Set the PE bit to 1.

- [4] Set the SMIF, SDIR, and SINV bits in SCMR.When the SMIF bit is set to 1, the TxD and RxD pins are both switched from ports to SCI pins, and are placed in the high-impedance state.

- [5] Set the value corresponding to the bit rate in BRR.

- [6] Set the CKE0 and CKE1 bits in SCR. Clear the TIE, RIE, TE, RE, MPIE, and TEIE bits to 0. If the CKE0 bit is set to 1, the clock is output from the SCK pin.

- [7] Wait at least one bit interval, then set the TIE, RIE, TE, and RE bits in SCR. Do not set the TE bit and RE bit at the same time, except for self-diagnosis.

PWPR1

## 19.2.3 PWM Polarity Registers 1 and 2 (PWPR1, PWPR2)

| Bit           | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|

|               | OPS1H | OPS1G | OPS1F | OPS1E | OPS1D | OPS1C | OPS1B | OPS1A |

| Initial value | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| Read/Write    | R/W   |

|               |       |       |       |       |       |       |       |       |

| PWPR2         |       |       |       |       |       |       |       |       |

| Bit           | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|               | OPS2H | OPS2G | OPS2F | OPS2E | OPS2D | OPS2C | OPS2B | OPS2A |

| Initial value | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| Read/Write    | R/W   |

PWPR is an 8-bit read/write register that selects the PWM output polarity. PWPR1 controls outputs PWM1H to PWM1A, and PWPR2 controls outputs PWM2H to PWM2A.

PWPR is initialized to H'00 upon reset, and in standby mode, watch mode<sup>\*</sup>, subactive mode<sup>\*</sup>, subsleep mode<sup>\*</sup>, and module stop mode.

Note: \* Subclock functions (subactive mode, subsleep mode, and watch mode) are available in the U-mask and W-mask versions, and H8S/2635 Group only. These functions cannot be used with the other versions.

**Bits 7 to 0—Output Polarity Select (OPS):** Each of these bits selects the polarity of the corresponding PWM output.

| Bits 7 to 0:<br>OPS | Description        |                 |

|---------------------|--------------------|-----------------|

| 0                   | PWM direct output  | (Initial value) |

| 1                   | PWM inverse output |                 |

#### **Table 21B-7 Flash Memory Erase Blocks**

| Addresses            |

|----------------------|

| H'000000 to H'000FFF |

| H'001000 to H'001FFF |

| H'002000 to H'002FFF |

| H'003000 to H'003FFF |

| H'004000 to H'004FFF |

| H'005000 to H'005FFF |

| H'006000 to H'006FFF |

| H'007000 to H'007FFF |

| H'008000 to H'00FFFF |

| H'010000 to H'01FFFF |

| H'020000 to H'02FFFF |

| H'030000 to H'03FFFF |

| H'040000 to H'04FFFF |

| H'050000 to H'05FFFF |

|                      |

Note: \* This function is not available in the H8S/2638 and H8S/2639.

#### 21B.7.5 RAM Emulation Register (RAMER)

RAMER specifies the area of flash memory to be overlapped with part of RAM when emulating real-time flash memory programming. RAMER initialized to H'00 by a reset and in hardware standby mode. It is not initialized in software standby mode. RAMER settings should be made in user mode or user program mode.

Flash memory area divisions are shown in table 21B-8. To ensure correct operation of the emulation function, the ROM for which RAM emulation is performed should not be accessed immediately after this register has been modified. Normal execution of an access immediately after register modification is not guaranteed.

| Bit:           | 7 | 6 | 5   | 4   | 3    | 2    | 1    | 0    |

|----------------|---|---|-----|-----|------|------|------|------|

|                |   | _ | —   | —   | RAMS | RAM2 | RAM1 | RAM0 |

| Initial value: | 0 | 0 | 0   | 0   | 0    | 0    | 0    | 0    |

| R/W:           | R | R | R/W | R/W | R/W  | R/W  | R/W  | R/W  |

# 21B.9.2 Program-Verify Mode

In program-verify mode, the data written in program mode is read to check whether it has been correctly written in the flash memory.

After the elapse of the given programming time, clear the P bit in FLMCR1, then wait for at least  $(t_{cp}) \mu s$  before clearing the PSU bit to exit program mode. After exiting program mode, the watchdog timer setting is also cleared. The operating mode is then switched to program-verify mode by setting the PV bit in FLMCR1. Before reading in program-verify mode, a dummy write of H'FF data should be made to the addresses to be read. The dummy write should be executed after the elapse of  $(t_{spv}) \mu s$  or more. When the flash memory is read in this state (verify data is read in 16-bit units), the data at the latched address is read. Wait at least  $(t_{spvr}) \mu s$  after the dummy write before performing this read operation. Next, the originally written data is compared with the verify data, and reprogram data is computed (see figure 21B-12) and transferred to RAM. After verification of 128 bytes of data has been completed, exit program-verify mode, wait for at least  $(t_{cpv}) \mu s$ , then clear the SWE bit in FLMCR1. If reprogramming is necessary, set program mode again, and repeat the program/program-verify sequence as before. The maximum number of repetitions of the program/program-verify sequence is indicated by the maximum programming count (N). Leave a wait time of at least  $(t_{cswe}) \mu s$  after clearing SWE.

## Notes on Program/Program-Verify Procedure

- 1. In order to perform 128-byte-unit programming, the lower 8 bits of the write start address must be H'00 or H'80.

- 2. When performing continuous writing of 128-byte data to flash memory, byte-unit transfer should be used.

128-byte data transfer is necessary even when writing fewer than 128 bytes of data. Write H'FF data to the extra addresses.

- 3. Verify data is read in word units.

- 4. The write pulse is applied and a flash memory write executed while the P bit in FLMCR1 is set. In the chip, write pulses should be applied as follows in the program/program-verify procedure to prevent voltage stress on the device and loss of write data reliability.

- a. After write pulse application, perform a verify-read in program-verify mode and apply a write pulse again for any bits read as 1 (reprogramming processing). When all the 0-write bits in the 128-byte write data are read as 0 in the verify-read operation, the program/program-verify procedure is completed. In the chip, the number of loops in reprogramming processing is guaranteed not to exceed the maximum value of the maximum programming count (N).

The H8S/2635 has 192 kbytes of on-chip ROM. The H8S/2634 has 128 kbytes of onchip ROM.

#### Table 21C-3 Operating Modes and ROM (Mask ROM Version)

|        |                                                  |     | Mode P | ins |                                                     |

|--------|--------------------------------------------------|-----|--------|-----|-----------------------------------------------------|

|        | Operating Mode                                   | MD2 | MD1    | MD0 | On-Chip ROM                                         |

| Mode 0 | _                                                | 0   | 0      | 0   |                                                     |

| Mode 1 |                                                  |     |        | 1   |                                                     |

| Mode 2 |                                                  |     | 1      | 0   |                                                     |

| Mode 3 |                                                  |     |        | 1   |                                                     |

| Mode 4 | Advanced expanded mode with on-chip ROM disabled | 1   | 0      | 0   | Disabled                                            |

| Mode 5 | Advanced expanded mode with on-chip ROM disabled |     |        | 1   |                                                     |

| Mode 6 | Advanced expanded mode with on-chip ROM enabled  | _   | 1      | 0   | Enabled<br>(192 kbytes/<br>128 kbytes) <sup>*</sup> |

| Mode 7 | Advanced single-chip mode                        | _   |        | 1   | Enabled<br>(192 kbytes/<br>128 kbytes) <sup>*</sup> |

Note: \* The H8S/2635 has 192 kbytes of on-chip ROM. The H8S/2634 has 128 kbytes of on-chip ROM.

#### • Programmer mode

Flash memory can be programmed/erased in programmer mode, using a PROM programmer, as well as in on-board programming mode.

#### 21C.4.2 Block Diagram

Figure 21C-2 Block Diagram of Flash Memory

| σ                                       |                |             |                 |             |                  |                |                 |               |            |                |             |                 |             |                  |                |                |                |               |                 |                  |                   |                   |                  |                  |          |          |                   |                   |          |          |          |          |          |          |          |          |          |

|-----------------------------------------|----------------|-------------|-----------------|-------------|------------------|----------------|-----------------|---------------|------------|----------------|-------------|-----------------|-------------|------------------|----------------|----------------|----------------|---------------|-----------------|------------------|-------------------|-------------------|------------------|------------------|----------|----------|-------------------|-------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| 8                                       | )              |             |                 |             |                  |                |                 |               |            |                |             |                 |             |                  |                |                |                |               |                 |                  |                   |                   |                  |                  |          |          |                   |                   |          |          |          |          |          |          |          |          |          |

| 7                                       |                |             |                 |             |                  |                |                 |               |            |                |             |                 |             |                  |                |                |                |               |                 |                  |                   |                   |                  |                  |          |          |                   |                   |          |          |          |          |          |          |          |          |          |

| 9                                       | ,              |             |                 |             |                  |                |                 |               |            |                |             |                 |             |                  |                |                |                |               |                 |                  |                   |                   |                  |                  |          |          |                   |                   |          |          |          |          |          |          |          |          |          |

| 5                                       | >              |             |                 |             |                  |                |                 |               |            |                |             |                 |             |                  |                |                |                |               |                 |                  |                   | R:W:M NEXT        |                  |                  |          |          |                   |                   |          |          |          |          |          |          |          |          |          |

| 4                                       |                |             |                 |             |                  |                |                 |               |            |                |             |                 |             |                  |                |                |                |               |                 |                  | R:W:M NEXT        | R:B EA            |                  |                  |          |          |                   |                   |          |          |          |          |          |          |          |          |          |

| e                                       | )              |             |                 |             | R:W NEXT         |                |                 |               |            |                |             |                 |             | R:W NEXT         |                |                |                |               | R:W:M NEXT      | R:W:M NEXT       |                   | R:W 4th           |                  |                  |          |          |                   |                   |          |          |          |          |          |          |          |          |          |

|                                         | 1              |             | R:W NEXT        |             | R:W 3rd          |                |                 |               |            |                |             | R:W NEXT        |             | R:W 3rd          | R:W NEXT       |                | R:W NEXT       |               | R:B EA          | R:B EA           | R:W 3rd           | R:W 3rd           | R:W EA           | R:W EA           | R:W EA   | R:W EA   | R:W EA            | R:W EA            | R:W EA   | R:W EA   | R:W EA   | R:W EA   | R:W EA   | R:W EA   | R:W EA   | R:W EA   | R:W EA   |

|                                         | R:W NEXT       | R:W NEXT    | R:W 2nd         | R:W NEXT    | R:W 2nd          | R:W NEXT       | R:W NEXT        | R:W NEXT      | R:W NEXT   | R:W NEXT       | R:W NEXT    | R:W 2nd         | R:W NEXT    | R:W 2nd          | R:W 2nd        | R:W NEXT       | R:W 2nd        | R:W NEXT      | R:W 2nd         | R:W 2nd          | R:W 2nd           | R:W 2nd           | R:W NEXT         | R:W NEXT         | R:W NEXT | R:W NEXT | R:W NEXT          | R:W NEXT          | R:W NEXT | R:W NEXT | R:W NEXT | R:W NEXT | R:W NEXT | R:W NEXT | R:W NEXT | R:W NEXT | R:W NEXT |

| I able A-0 Instruction Execution Cycles | ADD.B #xx:8,Rd | ADD.B Rs,Rd | ADD.W #xx:16,Rd | ADD.W Rs,Rd | ADD.L #xx:32,ERd | ADD.L ERs, ERd | ADDS #1/2/4,ERd | ADDX #xx:8,Rd | ADDX Rs,Rd | AND.B #xx:8,Rd | AND.B Rs,Rd | AND.W #xx:16,Rd | AND.W Rs,Rd | AND.L #xx:32,ERd | AND.L ERs, ERd | ANDC #xx:8,CCR | ANDC #xx:8,EXR | BAND #xx:3,Rd | BAND #xx:3,@ERd | BAND #xx:3,@aa:8 | BAND #xx:3,@aa:16 | BAND #xx:3,@aa:32 | BRA d:8 (BT d:8) | BRN d:8 (BF d:8) | BHI d:8  | BLS d:8  | BCC d:8 (BHS d:8) | BCS d:8 (BLO d:8) | BNE d:8  | BEQ d:8  | BVC d:8  | BVS d:8  | BPL d:8  | BMI d:8  | BGE d:8  | BLT d:8  | BGT d:8  |

| MC8[1]—Message Control 8[1]H'F860MC8[2]—Message Control 8[2]H'F861MC8[3]—Message Control 8[3]H'F862MC8[4]—Message Control 8[4]H'F863MC8[5]—Message Control 8[5]H'F864MC8[6]—Message Control 8[6]H'F865MC8[7]—Message Control 8[7]H'F866MC8[8]—Message Control 8[8]H'F867 | HCAN0<br>HCAN0<br>HCAN0<br>HCAN0<br>HCAN0<br>HCAN0<br>HCAN0 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| MC8[1]                                                                                                                                                                                                                                                                   |                                                             |

| Bit 7 6 5 4 3 2 1                                                                                                                                                                                                                                                        | 0                                                           |

| DLC3   DLC2   DLC                                                                                                                                                                                                                                                        | 1 DLC0                                                      |

| Initial value Undefined Undefined Undefined Undefined Undefined Undefined                                                                                                                                                                                                | ed Undefined                                                |

| Read/Write R/W R/W R/W R/W R/W R/W                                                                                                                                                                                                                                       | R/W                                                         |

| Data Length Code                                                                                                                                                                                                                                                         |                                                             |

| 0 $0$ $0$ Data length = 0 bytes                                                                                                                                                                                                                                          |                                                             |

| 1 Data length = 1 byte                                                                                                                                                                                                                                                   |                                                             |

| 1 0 Data length = 2 bytes                                                                                                                                                                                                                                                |                                                             |

| 1 Data length = 3 bytes                                                                                                                                                                                                                                                  |                                                             |

| 1 0 0 Data length = 4 bytes                                                                                                                                                                                                                                              |                                                             |

| 1 Data length = 5 bytes                                                                                                                                                                                                                                                  |                                                             |

| 1 0 Data length = 6 bytes                                                                                                                                                                                                                                                |                                                             |

| 1 Data length = 7 bytes                                                                                                                                                                                                                                                  |                                                             |

| 1 0/1 0/1 0/1 Data length = 8 bytes                                                                                                                                                                                                                                      |                                                             |

| MC8[2]                                                                                                                                                                                                                                                                   | ]                                                           |

| Bit 7 6 5 4 3 2 1                                                                                                                                                                                                                                                        | 0                                                           |

|                                                                                                                                                                                                                                                                          |                                                             |

| Initial value Undefined Undefined Undefined Undefined Undefined Undefined Undefined                                                                                                                                                                                      | ed Undefined                                                |

| Read/Write R/W R/W R/W R/W R/W R/W                                                                                                                                                                                                                                       | R/W                                                         |

| MC8[3]                                                                                                                                                                                                                                                                   |                                                             |

| Bit 7 6 5 4 3 2 1                                                                                                                                                                                                                                                        | 0                                                           |

|                                                                                                                                                                                                                                                                          |                                                             |

| Initial value Undefined Undefined Undefined Undefined Undefined Undefined Undefined                                                                                                                                                                                      | ed Undefined                                                |

| Read/Write R/W R/W R/W R/W R/W R/W R/W R/W                                                                                                                                                                                                                               |                                                             |

| MD12[1]—Mes<br>MD12[2]—Mes<br>MD12[3]—Mes<br>MD12[4]—Mes<br>MD12[5]—Mes<br>MD12[6]—Mes<br>MD12[7]—Mes<br>MD12[8]—Mes | sage Data<br>sage Data<br>sage Data<br>sage Data<br>sage Data<br>sage Data<br>sage Data | 12[2]<br>12[3]<br>12[4]<br>12[5]<br>12[6]<br>12[7] |               |               |               | H'F910<br>H'F911<br>H'F912<br>H'F913<br>H'F914<br>H'F915<br>H'F916<br>H'F917 |               |                |                 | HCAN0<br>HCAN0<br>HCAN0<br>HCAN0<br>HCAN0<br>HCAN0<br>HCAN0 |

|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------|---------------|---------------|---------------|------------------------------------------------------------------------------|---------------|----------------|-----------------|-------------------------------------------------------------|

| MDx[1]                                                                                                               | Bit                                                                                     | 7                                                  | 6             | 5             | 4             | 3                                                                            | 2             | 1              | 0               | _                                                           |

| MDx[2]                                                                                                               | Initial value<br>Read/Write<br>Bit                                                      | *<br>R/W<br>7                                      | *<br>R/W<br>6 | *<br>R/W<br>5 | *<br>R/W<br>4 | *<br>R/W<br>3                                                                | *<br>R/W<br>2 | *<br>R/W<br>1  | *<br>R/W<br>0   |                                                             |

|                                                                                                                      | Initial value<br>Read/Write                                                             | *<br>R/W                                           | *<br>R/W      | *<br>R/W      | *<br>R/W      | *<br>R/W                                                                     | *<br>R/W      | *<br>R/W       | *<br>R/W        |                                                             |

| MDx[3]                                                                                                               | Bit                                                                                     | 7                                                  | 6             | 5             | 4             | 3                                                                            | 2             | 1              | 0               |                                                             |

|                                                                                                                      | Initial value<br>Read/Write                                                             | *<br>R/W                                           | *<br>R/W      | *<br>R/W      | *<br>R/W      | *<br>R/W                                                                     | *<br>R/W      | *<br>R/W       | *<br>R/W        |                                                             |

| MDx[4]                                                                                                               | Bit                                                                                     | 7                                                  | 6             | 5             | 4             | 3                                                                            | 2             | 1              | 0               | -                                                           |

| MDx[5]                                                                                                               | Initial value<br>Read/Write<br>Bit                                                      | *<br>R/W<br>7                                      | *<br>R/W<br>6 | *<br>R/W<br>5 | *<br>R/W<br>4 | *<br>R/W<br>3                                                                | *<br>R/W<br>2 | *<br>R/W<br>1  | *<br>R/W<br>0   |                                                             |

|                                                                                                                      | Initial value<br>Read/Write                                                             | *<br>R/W                                           | *<br>R/W      | *<br>R/W      | *<br>R/W      | *<br>R/W                                                                     | *<br>R/W      | *<br>R/W       | *<br>R/W        |                                                             |

| MDx[6]                                                                                                               | Bit                                                                                     | 7                                                  | 6             | 5             | 4             | 3                                                                            | 2             | 1              | 0               | _                                                           |

|                                                                                                                      | Initial value<br>Read/Write                                                             | *<br>R/W                                           | *<br>R/W      | *<br>R/W      | *<br>R/W      | *<br>R/W                                                                     | *<br>R/W      | *<br>R/W       | *<br>R/W        |                                                             |

| MDx[7]                                                                                                               | Bit                                                                                     | 7                                                  | 6             | 5             | 4             | 3                                                                            | 2             | 1              | 0               | -                                                           |

|                                                                                                                      | Initial value<br>Read/Write                                                             | *<br>R/W                                           | *<br>R/W      | *<br>R/W      | *<br>R/W      | *<br>R/W                                                                     | *<br>R/W      | *<br>R/W       | *<br>R/W        |                                                             |

| MDx[8]                                                                                                               | Bit                                                                                     | 7                                                  | 6             | 5             | 4             | 3                                                                            | 2             | 1              | 0               | _                                                           |

|                                                                                                                      | Initial value<br>Read/Write                                                             | *<br>R/W                                           | *<br>R/W      | *<br>R/W      | *<br>R/W      | *<br>R/W                                                                     | *<br>R/W      | *<br>R/W<br>*: | R/W<br>Undefine |                                                             |

x = 0 to 15

####

| DDR                                | 0              | 1              | 1              |

|------------------------------------|----------------|----------------|----------------|

| PSTOP                              |                | 0              | 1              |

| Hardware standby mode              | High impedance | High impedance | High impedance |

| Software standby mode,             | High impedance | Fixed high     | Fixed high     |

| watch mode*, and direct transition |                |                |                |

| Sleep mode and subsleep mode*      | High impedance | φ output       | Fixed high     |

| High-speed mode, medium-speed      | High impedance | φ output       | Fixed high     |

| mode, and subactive mode*          |                |                |                |

Note: \* Subclock functions (subactive mode, subsleep mode, and watch mode) are available in the U-mask and W-mask versions, and H8S/2635 Group only. These functions cannot be used with the other versions.

# Appendix F Product Code Lineup

#### Table F-1 H8S/2636, H8S/2638, H8S/2639, and H8S/2630 Product Code Lineup

| Product Type            |                     | Part No.    | Mark Code   | Functions                                              | Packages                 |

|-------------------------|---------------------|-------------|-------------|--------------------------------------------------------|--------------------------|

| H8S/2636 F-ZTAT version |                     | HD64F2636   | HD64F2636F  | No subclock function                                   | 128-pin QFP<br>(FP-128B) |

|                         |                     |             | HD64F2636UF | Subclock function                                      | 128-pin QFP<br>(FP-128B) |

|                         | Mask ROM<br>version | I HD6432636 | HD6432636F  | No subclock function                                   | 128-pin QFP<br>(FP-128B) |

|                         |                     |             | HD6432636UF | Subclock function                                      | 128-pin QFP<br>(FP-128B) |

| H8S/2638                | F-ZTAT<br>version   | HD64F2638   | HD64F2638F  | No subclock function or I <sup>2</sup> C bus interface | 128-pin QFP<br>(FP-128B) |

|                         |                     |             | HD64F2638UF | Subclock function, no I <sup>2</sup> C bus interface   | 128-pin QFP<br>(FP-128B) |

|                         |                     |             | HD64F2638WF | Subclock function and I <sup>2</sup> C bus interface   | 128-pin QFP<br>(FP-128B) |

|                         | Mask ROM<br>version | I HD6432638 | HD6432638F  | No subclock function or I <sup>2</sup> C bus interface | 128-pin QFP<br>(FP-128B) |

|                         |                     |             | HD6432638UF | Subclock function, no I <sup>2</sup> C bus interface   | 128-pin QFP<br>(FP-128B) |

|                         |                     |             | HD6432638WF | Subclock function and I <sup>2</sup> C bus interface   | 128-pin QFP<br>(FP-128B) |

| H8S/2639                | F-ZTAT<br>version   | HD64F2639   | HD64F2639UF | Subclock function, no I <sup>2</sup> C bus interface   | 128-pin QFP<br>(FP-128B) |

|                         |                     |             | HD64F2639WF | Subclock function and $I^2C$ bus interface             | 128-pin QFP<br>(FP-128B) |

|                         | Mask ROM<br>version | I HD6432639 | HD6432639UF | Subclock function, no I <sup>2</sup> C bus interface   | 128-pin QFP<br>(FP-128B) |

|                         |                     |             | HD6432639WF | Subclock function and I <sup>2</sup> C bus interface   | 128-pin QFP<br>(FP-128B) |