#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                      |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | H8S/2600                                                                      |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 20MHz                                                                         |

| Connectivity               | CANbus, SCI, SmartCard                                                        |

| Peripherals                | Motor Control PWM, POR, PWM, WDT                                              |

| Number of I/O              | 72                                                                            |

| Program Memory Size        | 256KB (256K x 8)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 16K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                   |

| Data Converters            | A/D 12x10b; D/A 2x8b                                                          |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 128-BFQFP                                                                     |

| Supplier Device Package    | 128-QFP (14x20)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df2638uf20jv |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 7.4   | Basic          | Bus Interface                            |     |

|-------|----------------|------------------------------------------|-----|

|       | 7.4.1          | Overview                                 | 167 |

|       | 7.4.2          | Data Size and Data Alignment             | 167 |

|       | 7.4.3          | Valid Strobes                            | 169 |

|       | 7.4.4          | Basic Timing                             |     |

|       | 7.4.5          | Wait Control                             |     |

| 7.5   | Burst 1        | ROM Interface                            | 179 |

|       | 7.5.1          | Overview                                 | 179 |

|       | 7.5.2          | Basic Timing                             |     |

|       | 7.5.3          | Wait Control                             |     |

| 7.6   | Idle C         | ycle                                     |     |

|       | 7.6.1          | Operation                                |     |

|       | 7.6.2          | Pin States During Idle Cycles            |     |

| 7.7   | Write          | Data Buffer Function                     |     |

| 7.8   | Bus A          | rbitration                               |     |

|       | 7.8.1          | Overview                                 |     |

|       | 7.8.2          | Operation                                |     |

|       | 7.8.3          | Bus Transfer Timing                      |     |

| 7.9   | Resets         | and the Bus Controller                   |     |

|       |                |                                          |     |

| Secti | ion 8          | Data Transfer Controller (DTC)           |     |

| 8.1   | Overv          | iew                                      |     |

|       | 8.1.1          | Features                                 |     |

|       | 8.1.2          | Block Diagram                            |     |

|       | 8.1.3          | Register Configuration                   | 191 |

| 8.2   | Regist         | er Descriptions                          |     |

|       | 8.2.1          | DTC Mode Register A (MRA)                |     |

|       | 8.2.2          | DTC Mode Register B (MRB)                |     |

|       | 8.2.3          | DTC Source Address Register (SAR)        |     |

|       | 8.2.4          | DTC Destination Address Register (DAR)   |     |

|       | 8.2.5          | DTC Transfer Count Register A (CRA)      |     |

|       | 8.2.6          | DTC Transfer Count Register B (CRB)      |     |

|       | 8.2.7          | DTC Enable Registers (DTCER)             |     |

|       | 8.2.8          | DTC Vector Register (DTVECR)             |     |

|       | 8.2.9          | Module Stop Control Register A (MSTPCRA) |     |

| 8.3   | Operat         | tion                                     |     |

|       | 8.3.1          | Overview                                 |     |

|       |                |                                          |     |

|       | 8.3.2          | Activation Sources                       |     |

|       | 8.3.2<br>8.3.3 | Activation Sources<br>DTC Vector Table   |     |

# (2) Reset Exception Handling

After the  $\overline{\text{RES}}$  pin has gone low and the reset state has been entered, when  $\overline{\text{RES}}$  goes high again, reset exception handling starts. The CPU enters the reset state when the  $\overline{\text{RES}}$  is low. When reset exception handling starts the CPU fetches a start address (vector) from the exception vector table and starts program execution from that address. All interrupts, including NMI, are disabled during reset exception handling and after it ends.

### (3) Traces

Traces are enabled only in interrupt control mode 2. Trace mode is entered when the T bit of EXR is set to 1. When trace mode is established, trace exception handling starts at the end of each instruction.

At the end of a trace exception-handling sequence, the T bit of EXR is cleared to 0 and trace mode is cleared. Interrupt masks are not affected.

The T bit saved on the stack retains its value of 1, and when the RTE instruction is executed to return from the trace exception-handling routine, trace mode is entered again. Trace exception-handling is not executed at the end of the RTE instruction.

Trace mode is not entered in interrupt control mode 0, regardless of the state of the T bit.

# (4) Interrupt Exception Handling and Trap Instruction Exception Handling

When interrupt or trap-instruction exception handling begins, the CPU references the stack pointer (ER7) and pushes the program counter and other control registers onto the stack. Next, the CPU alters the settings of the interrupt mask bits in the control registers. Then the CPU fetches a start address (vector) from the exception vector table and program execution starts from that start address.

Figure 2-16 shows the stack after exception handling ends.

[10] When the specified number of transfers are completed (the TPU transfer CRA value is 0), the TGFA flag is held at 1, the DTCE bit is cleared to 0, and a TGIA interrupt request is sent to the CPU. Termination processing should be performed in the interrupt handling routine.

# (3) Software Activation

An example is shown in which the DTC is used to transfer a block of 128 bytes of data by means of software activation. The transfer source address is H'1000 and the destination address is H'2000. The vector number is H'60, so the vector address is H'04C0.

- [1] Set MRA to incrementing source address (SM1 = 1, SM0 = 0), incrementing destination address (DM1 = 1, DM0 = 0), block transfer mode (MD1 = 1, MD0 = 0), and byte size (Sz = 0). The DTS bit can have any value. Set MRB for one block transfer by one interrupt (CHNE = 0). Set the transfer source address (H'1000) in SAR, the destination address (H'2000) in DAR, and 128 (H'8080) in CRA. Set 1 (H'0001) in CRB.

- [2] Set the start address of the register information at the DTC vector address (H'04C0).

- [3] Check that the SWDTE bit in DTVECR is 0. Check that there is currently no transfer activated by software.

- [4] Write 1 to the SWDTE bit and the vector number (H'60) to DTVECR. The write data is H'E0.

- [5] Read DTVECR again and check that it is set to the vector number (H'60). If it is not, this indicates that the write failed. This is presumably because an interrupt occurred between steps 3 and 4 and led to a different software activation. To activate this transfer, go back to step 3.

- [6] If the write was successful, the DTC is activated and a block of 128 bytes of data is transferred.

- [7] After the transfer, an SWDTEND interrupt occurs. The interrupt handling routine should clear the SWDTE bit to 0 and perform other wrap-up processing.

**Bit 7—Count Direction Flag (TCFD):** Status flag that shows the direction in which TCNT counts in channels 1, 2, 4, and 5.

In channels 0 and 3, bit 7 is reserved. It is always read as 1 and cannot be modified.

| Bit 7<br>TCFD | Description      |                 |

|---------------|------------------|-----------------|

| 0             | TCNT counts down |                 |

| 1             | TCNT counts up   | (Initial value) |

Bit 6—Reserved: This bit is always read as 1 and cannot be modified.

**Bit 5—Underflow Flag (TCFU):** Status flag that indicates that TCNT underflow has occurred when channels 1, 2, 4, and 5 are set to phase counting mode.

In channels 0 and 3, bit 5 is reserved. It is always read as 0 and cannot be modified.

| Bit 5<br>TCFU | Description                                                          |                 |

|---------------|----------------------------------------------------------------------|-----------------|

| 0             | [Clearing condition]                                                 | (Initial value) |

|               | <ul> <li>When 0 is written to TCFU after reading TCFU = 1</li> </ul> |                 |

| 1             | [Setting condition]                                                  |                 |

|               | • When the TCNT value underflows (changes from H'0000 to H'FFFF)     |                 |

Bit 4—Overflow Flag (TCFV): Status flag that indicates that TCNT overflow has occurred.

| Bit 4<br>TCFV | Description                                                          |                 |

|---------------|----------------------------------------------------------------------|-----------------|

| 0             | [Clearing condition]                                                 | (Initial value) |

|               | <ul> <li>When 0 is written to TCFV after reading TCFV = 1</li> </ul> |                 |

| 1             | [Setting condition]                                                  |                 |

|               | • When the TCNT value overflows (changes from H'FFFF to H'0000 )     |                 |

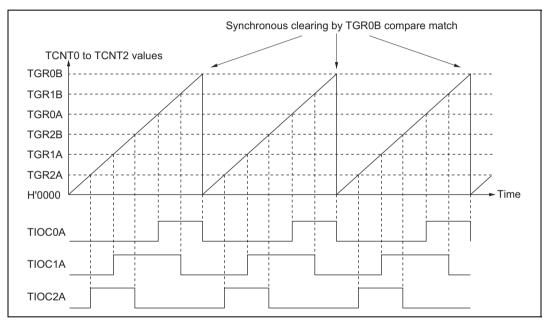

Example of Synchronous Operation: Figure 10-15 shows an example of synchronous operation.

In this example, synchronous operation and PWM mode 1 have been designated for channels 0 to 2, TGR0B compare match has been set as the channel 0 counter clearing source, and synchronous clearing has been set for the channel 1 and 2 counter clearing source.

Three-phase PWM waveforms are output from pins TIOC0A, TIOC1A, and TIOC2A. At this time, synchronous presetting, and synchronous clearing by TGR0B compare match, is performed for channel 0 to 2 TCNT counters, and the data set in TGR0B is used as the PWM cycle.

For details of PWM modes, see section 10.4.6, PWM Modes.

Figure 10-15 Example of Synchronous Operation

# 11.3.2 Output Timing

If pulse output is enabled, NDR contents are transferred to PODR and output when the specified compare match event occurs. Figure 11-3 shows the timing of these operations for the case of normal output in groups 2 and 3, triggered by compare match A.

| ф                         |              |

|---------------------------|--------------|

| TCNT                      | N <u>N+1</u> |

| TGRA                      | N            |

| Compare match<br>A signal |              |

| NDRH                      | n            |

| PODRH                     | n            |

| PO8 to PO15               | m n          |

Figure 11-3 Timing of Transfer and Output of NDR Contents (Example)

**Bit 5—Reset Select (RSTS):** Selects the type of internal reset generated if TCNT overflows during watchdog timer operation.

For details of the types of reset, see section 4, Exception Handling.

| Bit 5<br>RSTS | Description |                 |

|---------------|-------------|-----------------|

| 0             | Reset       | (Initial value) |

| 1             | Do not set  |                 |

Bits 4 to 0—Reserved: Always read as 1 and cannot be modified.

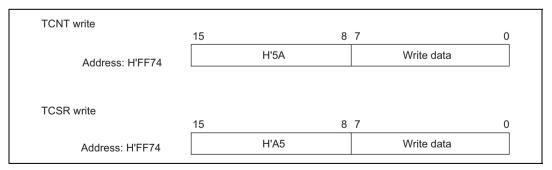

### 12.2.4 Notes on Register Access

The watchdog timer's TCNT, TCSR, and RSTCSR registers differ from other registers in being more difficult to write to. The procedures for writing to and reading these registers are given below.

Writing to TCNT and TCSR: These registers must be written to by a word transfer instruction. They cannot be written to with byte instructions.

Figure 12-2 shows the format of data written to TCNT and TCSR. TCNT and TCSR both have the same write address. For a write to TCNT, the upper byte of the written word must contain H'5A and the lower byte must contain the write data. For a write to TCSR, the upper byte of the written word must contain H'A5 and the lower byte must contain the write data. This transfers the write data from the lower byte to TCNT or TCSR.

Figure 12-2 Format of Data Written to TCNT and TCSR (WDT0)

**Bit 3—Multiprocessor Interrupt Enable (MPIE):** Enables or disables multiprocessor interrupts. The MPIE bit setting is only valid in asynchronous mode when the MP bit in SMR is set to 1.

The MPIE bit setting is invalid in clocked synchronous mode or when the MP bit is cleared to 0.

\_\_\_\_\_

| MPIE | Description                                                                                                                                                                                                   |                 |  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|

| 0    | Multiprocessor interrupts disabled (normal reception performed)                                                                                                                                               | (Initial value) |  |

|      | [Clearing conditions]                                                                                                                                                                                         |                 |  |

|      | When the MPIE bit is cleared to 0                                                                                                                                                                             |                 |  |

|      | When MPB= 1 data is received                                                                                                                                                                                  |                 |  |

| 1    | Multiprocessor interrupts enabled*                                                                                                                                                                            |                 |  |

|      | Receive interrupt (RXI) requests, receive error interrupt (ERI) requests, and setting<br>of the RDRF, FER, and ORER flags in SSR are disabled until data with the<br>multiprocessor bit set to 1 is received. |                 |  |

receive error detection, and setting of the RDRF, FER, and ORER flags in SSR, is not performed. When receive data including MPB = 1 is received, the MPB bit in SSR is set to 1, the MPIE bit is cleared to 0 automatically, and generation of RXI and ERI interrupts (when the TIE and RIE bits in SCR are set to 1) and FER and ORER flag setting is enabled.

**Bit 2—Transmit End Interrupt Enable (TEIE):** Enables or disables transmit end interrupt (TEI) request generation when there is no valid transmit data in TDR in MSB data transmission.

#### Bit 2

| TEIE | Description                                                   |        |                 |

|------|---------------------------------------------------------------|--------|-----------------|

| 0    | Transmit end interrupt (TEI) request disabled $^{st}$         |        | (Initial value) |

| 1    | Transmit end interrupt (TEI) request enabled $\!\!\!\!\!\!^*$ |        |                 |

| N    |                                                               | TODE ( |                 |

Note: \*TEI cancellation can be performed by reading 1 from the TDRE flag in SSR, then clearing it to 0 and clearing the TEND flag to 0, or clearing the TEIE bit to 0.

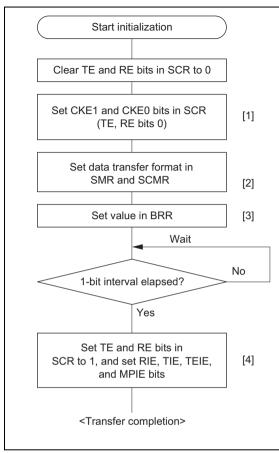

Figure 13-4 shows a sample SCI initialization flowchart.

Set the clock selection in SCR. Be sure to clear bits RIE, TIE, TEIE, and MPIE, and bits TE and RE, to 0.

When the clock is selected in asynchronous mode, it is output immediately after SCR settings are made.

- [2] Set the data transfer format in SMR and SCMR.

- [3] Write a value corresponding to the bit rate to BRR. Not necessary if an external clock is used.

- [4] Wait at least one bit interval, then set the TE bit or RE bit in SCR to 1. Also set the RIE, TIE, TEIE, and MPIE bits.

Setting the TE and RE bits enables the TxD and RxD pins to be used.

Figure 13-4 Sample SCI Initialization Flowchart

# 19.5 Usage Note

Contention between Buffer Register Write and Compare Match

If a PWBFR write is performed in the state immediately after a cycle register compare match, the PWM output does not change, but as the duty register is also rewritten at the same time as the buffer register, normal PWM output will not be achieved.

If a PWBFR write is performed in the state immediately after a cycle register compare match, the buffer register and duty register are overwritten. PWM output changed by the cycle register compare match is not changed in the overwrite of the duty register due to contention. This may result in unanticipated duty output. In the case of channel 2, the duty register used as the transfer destination is selected by the TDS bit of the buffer register when an overwrite of the duty register occurs due to contention. This can also result in an unintended overwrite of the duty register.

Buffer register rewriting must be completed before automatic transfer by the DTC<sup>\*</sup> (data transfer controller), exception handling due to a compare match interrupt, or the occurrence of a cycle register compare match on detection of the rise of CMF (compare match flag) in PWCR.

Τw  $T_2$ Tw φ Address Buffer register address Write signal Compare match PWCNT 0 (lower 10 bits) PWBFR Ν Μ PWDTR Ν Μ PWM output CMF

Note: \* The DTC is not implemented in the H8S/2635 and H8S/2634.

| Wait time:                                                                                                                                                                                                                            | Program-<br>ming/<br>erasing Wait time:<br>possible 100 μs |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| φ                                                                                                                                                                                                                                     | Min. 0 μs                                                  |

| v <sub>cc</sub>                                                                                                                                                                                                                       |                                                            |

| FWE                                                                                                                                                                                                                                   |                                                            |

| MD2 to MD0*1                                                                                                                                                                                                                          |                                                            |

| RESSWE set                                                                                                                                                                                                                            |                                                            |

| SWE bit                                                                                                                                                                                                                               | SWE cleared                                                |

| Period during which flash memory access is proh<br>(x: Wait time after setting SWE bit)*2                                                                                                                                             | ibited                                                     |

| Period during which flash memory can be program<br>(Execution of program in flash memory prohibited<br>prohibited)                                                                                                                    |                                                            |

| <ol> <li>Notes: 1. Except when switching modes, the level of a off by pulling the pins up or down.</li> <li>2. See section 24.1.7, Flash Memory Character</li> <li>3. Mode programming setup time t<sub>MDS</sub> (min.) =</li> </ol> | eristics.                                                  |

Figure 21A-19 Power-On/Off Timing (User Program Mode)

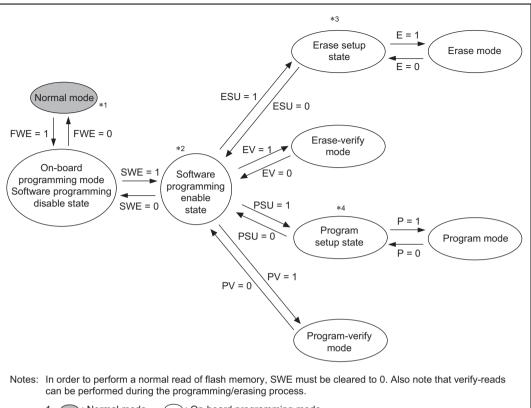

- 1. : Normal mode : On-board programming mode

- Do not make a state transition by setting or clearing multiple bits simultaneously.

After a transition from erase mode to the erase setup state, do not enter erase mode without passing through the software programming enable state.

- After a transition from program mode to the program setup state, do not enter program mode without passing through the software programming enable state.

# Figure 21C-11 FLMCR1 Bit Settings and State Transitions

# Table 24-14 Bus Drive Characteristics [Option]\*

$\begin{array}{ll} \text{Conditions:} & V_{CC} = 4.5 \text{ V to } 5.5 \text{ V}, \text{PWMV}_{CC} = 4.5 \text{ V to } 5.5 \text{ V}, \text{AV}_{CC} = 4.5 \text{ V to } 5.5 \text{ V}, \\ & V_{ref} = 4.5 \text{ V to } \text{AV}_{CC}, \text{V}_{SS} = \text{PWMV}_{SS} = \text{PLLV}_{SS} = \text{AV}_{SS} = 0 \text{ V}, \text{ } \text{T}_{a} = -20^{\circ}\text{C} \text{ to } +75^{\circ}\text{C} \\ & (\text{regular specifications}), \text{ } \text{T}_{a} = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C} \text{ (wide-range specifications)} \end{array}$

| Item                                    | Symbol                      | Min.                       | Тур. | Max.                       | Unit | Test Conditions                                               |

|-----------------------------------------|-----------------------------|----------------------------|------|----------------------------|------|---------------------------------------------------------------|

| Schmitt trigger input                   | V <sub>T</sub> <sup>-</sup> | 1.0                        | —    | _                          | V    |                                                               |

| voltage                                 | V <sub>T</sub> <sup>+</sup> | _                          | _    | $V_{CC} \times 0.7$        | _    |                                                               |

|                                         | $V_{T}^{+}-V_{T}^{-}$       | 0.4                        | _    | _                          | _    | $V_{CC}$ = 4.5 V to 5.5 V                                     |

| Input high voltage                      | V <sub>IH</sub>             | $V_{\text{CC}} \times 0.7$ |      | V <sub>CC</sub> + 0.5      | V    |                                                               |

| Input low voltage                       | VIL                         | - 0.5                      |      | $V_{\text{CC}} \times 0.3$ | V    |                                                               |

| Output low voltage                      | V <sub>OL</sub>             | —                          |      | 0.7                        | V    | $I_{OL} = 8 \text{ mA},$<br>$V_{CC} = 4.5 \text{ V to 5.5 V}$ |

|                                         |                             | _                          |      | 0.4                        |      | $I_{OL} = 3 \text{ mA},$<br>$V_{CC} = 4.5 \text{ V to 5.5 V}$ |

|                                         |                             | _                          |      | 0.4                        |      | $I_{OL}$ = 1.6 mA,<br>V <sub>CC</sub> = 3.3 V to 5.5 V        |

| Input capacitance                       | Cin                         | —                          | —    | 20                         | pF   | $V_{in} = 0 V, f = 1 MHz,$<br>$T_a = 25 \ ^{\circ}C$          |

| Three-state leakage current (off state) | I <sub>TSI</sub>            | —                          |      | 1.0                        | μA   | $V_{in} = 0.5 \text{ V to } V_{CC}$<br>- 5.5 V                |

| SCL, SDA, output fall time              | t <sub>of</sub>             | 20 + 0.1Cb                 | _    | 250                        | ns   |                                                               |

Applicable Pins: SCL1-0, SDA1-0

Note: \* Available when using I<sup>2</sup>C bus interface (the W-mask version only).

# 24.3.5 A/D Conversion Characteristics

Table 24-32 lists the A/D conversion characteristics.

#### Table 24-32 A/D Conversion Characteristics

Conditions:  $V_{CC} = 4.5 \text{ V}$  to 5.5 V, PWMV<sub>CC</sub> = 4.5 V to 5.5 V, AV<sub>CC</sub> = 4.5 V to 5.5 V,  $V_{ref} = 4.5 \text{ V}$  to AV<sub>CC</sub>,  $V_{SS} = PWMV_{SS} = PLLV_{SS} = AV_{SS} = 0 \text{ V}$ ,  $T_a = -20^{\circ}\text{C}$  to +75°C (regular specifications),  $T_a = -40^{\circ}\text{C}$  to +85°C (wide-range specifications)

|                                     |      | Conditi | on   |      |

|-------------------------------------|------|---------|------|------|

| Item                                | Min. | Тур.    | Max. | Unit |

| Resolution                          | 10   | 10      | 10   | bits |

| Conversion time                     | 10   | _       | _    | μs   |

| Analog input capacitance            |      | _       | 20   | pF   |

| Permissible signal-source impedance | _    | —       | 5    | kΩ   |

| Nonlinearity error                  | _    | —       | ±3.5 | LSB  |

| Offset error                        |      | —       | ±3.5 | LSB  |

| Full-scale error                    | _    | —       | ±3.5 | LSB  |

| Quantization                        | _    | ±0.5    | _    | LSB  |

| Absolute accuracy                   | _    | —       | ±4.0 | LSB  |

| Instruc- |                 |      |     |          |          |       |          |          | Instructio | Instruction Format |          |          |          |           |

|----------|-----------------|------|-----|----------|----------|-------|----------|----------|------------|--------------------|----------|----------|----------|-----------|

|          | Mnemonic        | Size | 1st | 1st byte | 2nd byte | oyte  | 3rd byte | 4th byte | 5th byte   | 6th byte           | 7th byte | 8th byte | 9th byte | 10th byte |

|          | ROTR.B Rd       | ш    | -   | з        | ∞        | Þ     |          |          |            |                    |          |          |          |           |

|          | ROTR.B #2, Rd   | ш    | -   | 3        | υ        | p     |          |          |            |                    |          |          |          |           |

|          | ROTR.W Rd       | ≥    | -   | 3        | 6        | Þ     |          |          |            |                    |          |          |          |           |

|          | ROTR.W #2, Rd   | 8    | -   | 3        | ۵        | Þ     |          |          |            |                    |          |          |          |           |

|          | ROTR.L ERd      | _    | -   | 3        | В        | 0 erd |          |          |            |                    |          |          |          |           |

|          | ROTR.L #2, ERd  | _    | -   | 3        | ш        | 0 erd |          |          |            |                    |          |          |          |           |

| ROTXL    | ROTXL.B Rd      | ш    | -   | 2        | 0        | Þ     |          |          |            |                    |          |          |          |           |

|          | ROTXL.B #2, Rd  | ш    | -   | 2        | 4        | Þ     |          |          |            |                    |          |          |          |           |

|          | ROTXL.W Rd      | ≥    | -   | 2        | -        | Þ     |          |          |            |                    |          |          |          |           |

|          | ROTXL.W #2, Rd  | ≥    | -   | 2        | 2        | p     |          |          |            |                    |          |          |          |           |

|          | ROTXL.L ERd     | _    | -   | 2        | ę        | 0 erd |          |          |            |                    |          |          |          |           |

|          | ROTXL.L #2, ERd | _    | -   | 2        | 7        | 0 erd |          |          |            |                    |          |          |          |           |

| ROTXR    | ROTXR.B Rd      | В    | -   | 3        | 0        | Þ     |          |          |            |                    |          |          |          |           |

|          | ROTXR.B #2, Rd  | В    | ٢   | 3        | 4        | p     |          |          |            |                    |          |          |          |           |

|          | ROTXR.W Rd      | 8    | -   | 3        | -        | p     |          |          |            |                    |          |          |          |           |

|          | ROTXR.W #2, Rd  | ≥    | -   | з        | 2        | p     |          |          |            |                    |          |          |          |           |

|          | ROTXR.L ERd     | _    | -   | 3        | ę        | 0 erd |          |          |            |                    |          |          |          |           |

|          | ROTXR.L #2, ERd | _    | -   | 3        | 7        | 0 erd |          |          |            |                    |          |          |          |           |

|          | RTE             |      | 5   | 9        | 7        | 0     |          |          |            |                    |          |          |          |           |

|          | RTS             |      | 5   | 4        | 7        | 0     |          |          |            |                    |          |          |          |           |

|          | SHAL.B Rd       | ш    | -   | 0        | ∞        | p     |          |          |            |                    |          |          |          |           |

|          | SHAL.B #2, Rd   | ۵    | -   | 0        | υ        | Þ     |          |          |            |                    |          |          |          |           |

|          | SHAL.W Rd       | ≥    | -   | 0        | 6        | Þ     |          |          |            |                    |          |          |          |           |

|          | SHAL.W #2, Rd   | 8    | ۲   | 0        | ۵        | p     |          |          |            |                    |          |          |          |           |

|          | SHAL.L ERd      | _    | -   | 0        | m        | 0 erd |          |          |            |                    |          |          |          |           |

|          | SHAL.L #2, ERd  | _    | -   | 0        | ш        | 0 erd |          |          |            |                    |          |          |          |           |

Page 1094 of 1458

| 6           |                  |                   |                   |            |              |               |                |                |               |                 |                  |                   |                   |                     |         |                |             |                 |             |                  |                |          |          |          |               |                |                               |                               |                               |                               |                       |                       |                                     |            |           |            |          |

|-------------|------------------|-------------------|-------------------|------------|--------------|---------------|----------------|----------------|---------------|-----------------|------------------|-------------------|-------------------|---------------------|---------|----------------|-------------|-----------------|-------------|------------------|----------------|----------|----------|----------|---------------|----------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|-----------------------|-----------------------|-------------------------------------|------------|-----------|------------|----------|

| 8           |                  |                   |                   |            |              |               |                |                |               |                 |                  |                   |                   |                     |         |                |             |                 |             |                  |                |          |          |          |               |                |                               |                               |                               |                               |                       |                       |                                     |            |           |            |          |

| 7           |                  |                   |                   |            |              |               |                |                |               |                 |                  |                   |                   |                     |         |                |             |                 |             |                  |                |          |          |          |               |                |                               |                               |                               |                               |                       |                       |                                     |            |           |            |          |

| 9           |                  |                   |                   |            |              |               |                |                |               |                 |                  |                   |                   |                     |         |                |             |                 |             |                  |                |          |          |          |               |                |                               |                               |                               |                               | R:W NEXT              | R:W NEXT              |                                     |            |           |            |          |

| 5           |                  |                   | R:W:M NEXT        |            |              |               |                | R:W:M NEXT     |               |                 |                  |                   | R:W:M NEXT        |                     |         |                |             |                 |             |                  |                |          |          |          |               |                |                               |                               |                               |                               | W:B EAd*2             | W:B EAd*2             | n times <sup>*2</sup> $\rightarrow$ |            |           |            |          |

| 4           |                  | R:W:M NEXT        | R:B EA            |            |              |               | R:W:M NEXT     | R:B EA         |               |                 |                  | R:W:M NEXT        | R:B EA            |                     |         |                |             |                 |             |                  |                |          |          |          |               |                | on, 11 states                 | on, 19 states                 |                               |                               | R:B EAs*2             | R:B EAs <sup>*2</sup> | ← Repeated n times <sup>*2</sup>    |            |           |            |          |

| 3           | R:W:M NEXT       |                   | R:W 4th           |            | R:W:M NEXT   | R:W:M NEXT    | R:B EA         | R:W 4th        |               | R:W:M NEXT      | R:W:M NEXT       | R:B EA            | R:W 4th           |                     |         |                |             |                 |             | R:W NEXT         |                |          |          |          |               |                | Internal operation, 11 states | Internal operation, 19 states | on, 11 states                 | on, 19 states                 | R:B EAd <sup>*1</sup> | R:B EAd <sup>*1</sup> |                                     |            |           |            |          |

| 2           |                  | R:W 3rd           | R:W 3rd           |            |              | R:B EA        | R:W 3rd        | R:W 3rd        |               | R:B EA          | R:B EA           | R:W 3rd           | R:W 3rd           | Internal operation, | 1 state |                |             | R:W NEXT        |             | R:W 3rd          |                |          |          |          |               |                | R:W NEXT                      | R:W NEXT                      | Internal operation, 11 states | Internal operation, 19 states | R:B EAs*1             | R:B EAs*1             |                                     |            |           |            |          |

| 1           | R:W 2nd          | R:W 2nd           | R:W 2nd           | R:W NEXT   | R:W 2nd      | R:W 2nd       | R:W 2nd        | R:W 2nd        | R:W NEXT      | R:W 2nd         | R:W 2nd          | R:W 2nd           | R:W 2nd           | R:W NEXT            |         | R:W NEXT       | R:W NEXT    | R:W 2nd         | R:W NEXT    | R:W 2nd          | R:W NEXT       | R:W NEXT | R:W NEXT | R:W NEXT | R:W NEXT      | R:W NEXT       | R:W 2nd                       | R:W 2nd                       | R:W NEXT                      | R:W NEXT                      | R:W 2nd               | R:W 2nd               | R:W NEXT                            | R:W NEXT   | R:W NEXT  | R:W NEXT   | R:W NEXT |

| Instruction | BTST #xx:3,@aa:8 | BTST #xx:3,@aa:16 | BTST #xx:3,@aa:32 | BTST Rn,Rd | BTST Rn,@ERd | BTST Rn,@aa:8 | BTST Rn,@aa:16 | BTST Rn,@aa:32 | BXOR #xx:3,Rd | BXOR #xx:3,@ERd | BXOR #xx:3,@aa:8 | BXOR #xx:3,@aa:16 | BXOR #xx:3,@aa:32 | CLRMAC              |         | CMP.B #xx:8,Rd | CMP.B Rs,Rd | CMP.W #xx:16,Rd | CMP.W Rs,Rd | CMP.L #xx:32,ERd | CMP.L ERS, ERd | DAA Rd   | DAS Rd   | DEC.B Rd | DEC.W #1/2,Rd | DEC.L #1/2,ERd | DIVXS.B Rs,Rd                 | DIVXS.W Rs, ERd               | DIVXU.B Rs,Rd                 | DIVXU.W Rs, ERd               | EEPMOV.B              | EEPMOV.W              | EXTS.W Rd                           | EXTS.L ERd | EXTU.W Rd | EXTU.L ERd | INC.B Rd |

Page 1122 of 1458

# A.6 Condition Code Modification

This section indicates the effect of each CPU instruction on the condition code. The notation used in the table is defined below.

| m = (          | 31 for longword operands                                             |

|----------------|----------------------------------------------------------------------|

| ł              | 15 for word operands                                                 |

| l              | 7 for byte operands                                                  |

| Si             | The i-th bit of the source operand                                   |

| Di             | The i-th bit of the destination operand                              |

| Ri             | The i-th bit of the result                                           |

| Dn             | The specified bit in the destination operand                         |

| _              | Not affected                                                         |

| $\updownarrow$ | Modified according to the result of the instruction (see definition) |

| 0              | Always cleared to 0                                                  |

| 1              | Always set to 1                                                      |

| *              | Undetermined (no guaranteed value)                                   |

| Z'             | Z flag before instruction execution                                  |

| C'             | C flag before instruction execution                                  |

| MC10[7]       |           |                          |           |              |              |           |           |           |

|---------------|-----------|--------------------------|-----------|--------------|--------------|-----------|-----------|-----------|

| Bit           | 7         | 6                        | 5         | 4            | 3            | 2         | 1         | 0         |

|               | EXD_ID7   | EXD_ID6                  | EXD_ID5   | EXD_ID4      | EXD_ID3      | EXD_ID2   | EXD_ID1   | EXD_ID0   |

| Initial value | Undefined | Undefined                | Undefined | Undefined    | Undefined    | Undefined | Undefined | Undefined |

| Read/Write    | R/W       | R/W                      | R/W       | R/W          | R/W          | R/W       | R/W       | R/W       |

| MC10[8]       |           | nded Iden<br>he identifi |           | ed identifie | er) of data  | frames an | id remote | frames    |

| Bit           | 7         | 6                        | 5         | 4            | 3            | 2         | 1         | 0         |

|               | EXD_ID15  | EXD_ID14                 | EXD_ID13  | EXD_ID12     | EXD_ID11     | EXD_ID10  | EXD_ID9   | EXD_ID8   |

| Initial value | Undefined | Undefined                | Undefined | Undefined    | Undefined    | Undefined | Undefined | Undefined |

| Read/Write    | R/W       | R/W                      | R/W       | R/W          | R/W          | R/W       | R/W       | R/W       |

|               |           | nded Iden                |           | od idoptifi  | )<br>of data | frames an | d romoto  | framas    |

Set the identifier (extended identifier) of data frames and remote frames

| MC0[7]        |           |                          |           |              |             |           |           |           |

|---------------|-----------|--------------------------|-----------|--------------|-------------|-----------|-----------|-----------|

| Bit           | 7         | 6                        | 5         | 4            | 3           | 2         | 1         | 0         |

|               | EXD_ID7   | EXD_ID6                  | EXD_ID5   | EXD_ID4      | EXD_ID3     | EXD_ID2   | EXD_ID1   | EXD_ID0   |

| Initial value | Undefined | Undefined                | Undefined | Undefined    | Undefined   | Undefined | Undefined | Undefined |

| Read/Write    | R/W       | R/W                      | R/W       | R/W          | R/W         | R/W       | R/W       | R/W       |

| MC0[8]        | _/        | nded Iden<br>he identifi |           | ed identifie | er) of data | frames an | id remote | frames    |

| Bit           | 7         | 6                        | 5         | 4            | 3           | 2         | 1         | 0         |

| Dit           |           | -                        | -         | -            | -           | EXD_ID10  |           | EXD_ID8   |

| Initial value | Undefined | Undefined                | Undefined | Undefined    | Undefined   | Undefined | Undefined | Undefined |

| Read/Write    | R/W       | R/W                      | R/W       | R/W          | R/W         | R/W       | R/W       | R/W       |

|               |           | nded Iden<br>he identifi |           | ed identifie | er) of data | frames an | id remote | frames    |

S

| SYSCR—Syste   | em Contro | l Registe | er                     |            | H'FDE5        | 5           |              | System    |

|---------------|-----------|-----------|------------------------|------------|---------------|-------------|--------------|-----------|

| Bit           | 7         | 6         | 5                      | 4          | 3             | 2           | 1            | 0         |

|               | MACS      | _         | INTM1                  | INTM0      | NMIEG         |             |              | RAME      |

| Initial value | 0         | 0         | 0                      | 0          | 0             | 0           | 0            | 1         |

| Read/Write    | R/W       |           | R/W                    | R/W        | R/W           | _           |              | R/W       |

|               |           |           |                        |            | RA            | M Enable    |              |           |

|               |           |           |                        |            | 0             | On-chip     | RAM is dis   | sabled    |

|               |           |           |                        |            | 1             | On-chip     | RAM is en    | abled     |

|               |           | N         | MI Edge Se             | elect —    |               |             |              |           |

|               |           | (         |                        |            | uested at t   | he falling  | edge of N    | MI input  |

|               |           | 1         | An interr              | upt is req | uested at t   | he rising e | edge of NM   | /II input |

|               | Interru   | pt Contro | ol Mode 1 a            | ind 0      |               |             |              |           |

|               | INTM      | 1 INTM0   | Interrup<br>Control Mo |            |               | Descript    | ion          |           |

|               | 0         | 0         | 0                      | Con        | trol of inter | rupts by I  | bit          |           |

|               |           | 1         |                        | Sett       | ng prohibi    | ted         |              |           |

|               | 1         | 0         | 2                      | Con        | trol of inter | rupts by I2 | 2 to I0 bits | and IPR   |

|               |           | 1         | —                      | Sett       | ng prohibi    | ted         |              |           |

# MAC Saturation

|   | Non-saturating calculation for MAC instruction |

|---|------------------------------------------------|

| 1 | Saturating calculation for MAC instruction     |