Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | ARM® Cortex®-M3                                                             |

| Core Size                  | 32-Bit Single-Core                                                          |

| Speed                      | 48MHz                                                                       |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, SmartCard, SPI, UART/USART                 |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, POR, PWM, WDT                             |

| Number of I/O              | 90                                                                          |

| Program Memory Size        | 512KB (512K x 8)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 128K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.98V ~ 3.8V                                                                |

| Data Converters            | A/D 8x12b; D/A 2x12b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 112-LFBGA                                                                   |

| Supplier Device Package    | 112-BGA (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32gg890f512g-e-bga112r |

# **1 Ordering Information**

Table 1.1 (p. 2) shows the available EFM32GG890 devices.

Table 1.1. Ordering Information

| Ordering Code             | Flash (kB) | RAM (kB) | Max<br>Speed<br>(MHz) | Supply<br>Voltage<br>(V) | Temperature<br>(°C) | Package |

|---------------------------|------------|----------|-----------------------|--------------------------|---------------------|---------|

| EFM32GG890F512G-E-BGA112  | 512        | 128      | 48                    | 1.98 - 3.8               | -40 - 85            | BGA112  |

| EFM32GG890F1024G-E-BGA112 | 1024       | 128      | 48                    | 1.98 - 3.8               | -40 - 85            | BGA112  |

Adding the suffix 'R' to the part number (e.g. EFM32GG890F512G-E-BGA112R) denotes tape and reel.

Visit www.silabs.com for information on global distributors and representatives.

# 2 System Summary

# 2.1 System Introduction

The EFM32 MCUs are the world's most energy friendly microcontrollers. With a unique combination of the powerful 32-bit ARM Cortex-M3, innovative low energy techniques, short wake-up time from energy saving modes, and a wide selection of peripherals, the EFM32GG microcontroller is well suited for any battery operated application as well as other systems requiring high performance and low-energy consumption. This section gives a short introduction to each of the modules in general terms and also shows a summary of the configuration for the EFM32GG890 devices. For a complete feature set and in-depth information on the modules, the reader is referred to the *EFM32GG Reference Manual*.

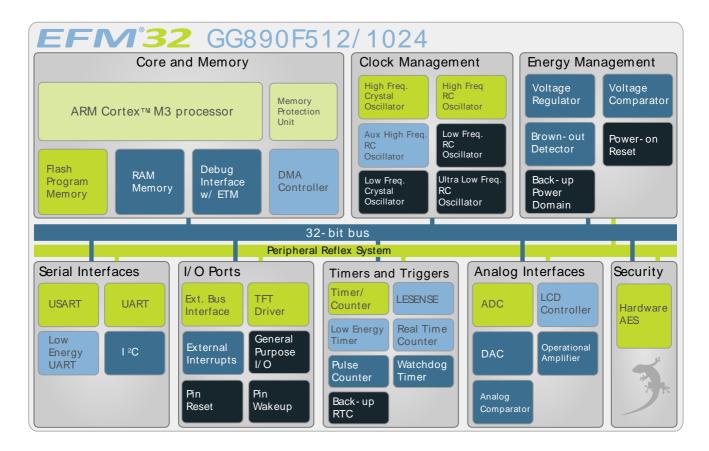

A block diagram of the EFM32GG890 is shown in Figure 2.1 (p. 3).

Figure 2.1. Block Diagram

#### 2.1.1 ARM Cortex-M3 Core

The ARM Cortex-M3 includes a 32-bit RISC processor which can achieve as much as 1.25 Dhrystone MIPS/MHz. A Memory Protection Unit with support for up to 8 memory segments is included, as well as a Wake-up Interrupt Controller handling interrupts triggered while the CPU is asleep. The EFM32 implementation of the Cortex-M3 is described in detail in *EFM32 Cortex-M3 Reference Manual*.

### 2.1.2 Debug Interface (DBG)

This device includes hardware debug support through a 2-pin serial-wire debug interface and an Embedded Trace Module (ETM) for data/instruction tracing . In addition there is also a 1-wire Serial Wire Viewer pin which can be used to output profiling information, data trace and software-generated messages.

#### 2.1.19 Backup Real Time Counter (BURTC)

The Backup Real Time Counter (BURTC) contains a 32-bit counter and is clocked either by a 32.768 kHz crystal oscillator, a 32.768 kHz RC oscillator or a 1 kHz ULFRCO. The BURTC is available in all Energy Modes and it can also run in backup mode, making it operational even if the main power should drain out.

#### 2.1.20 Low Energy Timer (LETIMER)

The unique LETIMER<sup>TM</sup>, the Low Energy Timer, is a 16-bit timer that is available in energy mode EM2 in addition to EM1 and EM0. Because of this, it can be used for timing and output generation when most of the device is powered down, allowing simple tasks to be performed while the power consumption of the system is kept at an absolute minimum. The LETIMER can be used to output a variety of waveforms with minimal software intervention. It is also connected to the Real Time Counter (RTC), and can be configured to start counting on compare matches from the RTC.

#### 2.1.21 Pulse Counter (PCNT)

The Pulse Counter (PCNT) can be used for counting pulses on a single input or to decode quadrature encoded inputs. It runs off either the internal LFACLK or the PCNTn\_S0IN pin as external clock source. The module may operate in energy mode EM0 - EM3.

### 2.1.22 Analog Comparator (ACMP)

The Analog Comparator is used to compare the voltage of two analog inputs, with a digital output indicating which input voltage is higher. Inputs can either be one of the selectable internal references or from external pins. Response time and thereby also the current consumption can be configured by altering the current supply to the comparator.

#### 2.1.23 Voltage Comparator (VCMP)

The Voltage Supply Comparator is used to monitor the supply voltage from software. An interrupt can be generated when the supply falls below or rises above a programmable threshold. Response time and thereby also the current consumption can be configured by altering the current supply to the comparator.

### 2.1.24 Analog to Digital Converter (ADC)

The ADC is a Successive Approximation Register (SAR) architecture, with a resolution of up to 12 bits at up to one million samples per second. The integrated input mux can select inputs from 8 external pins and 6 internal signals.

### 2.1.25 Digital to Analog Converter (DAC)

The Digital to Analog Converter (DAC) can convert a digital value to an analog output voltage. The DAC is fully differential rail-to-rail, with 12-bit resolution. It has two single ended output buffers which can be combined into one differential output. The DAC may be used for a number of different applications such as sensor interfaces or sound output.

## 2.1.26 Operational Amplifier (OPAMP)

The EFM32GG890 features 3 Operational Amplifiers. The Operational Amplifier is a versatile general purpose amplifier with rail-to-rail differential input and rail-to-rail single ended output. The input can be set to pin, DAC or OPAMP, whereas the output can be pin, OPAMP or ADC. The current is programmable and the OPAMP has various internal configurations such as unity gain, programmable gain using internal resistors etc.

## 2.1.27 Low Energy Sensor Interface (LESENSE)

The Low Energy Sensor Interface (LESENSE<sup>TM</sup>), is a highly configurable sensor interface with support for up to 16 individually configurable sensors. By controlling the analog comparators and DAC, LESENSE

# 3 Electrical Characteristics

#### 3.1 Test Conditions

#### 3.1.1 Typical Values

The typical data are based on  $T_{AMB}=25^{\circ}C$  and  $V_{DD}=3.0$  V, as defined in Table 3.2 (p. 10), unless otherwise specified.

#### 3.1.2 Minimum and Maximum Values

The minimum and maximum values represent the worst conditions of ambient temperature, supply voltage and frequencies, as defined in Table 3.2 (p. 10), unless otherwise specified.

## 3.2 Absolute Maximum Ratings

The absolute maximum ratings are stress ratings, and functional operation under such conditions are not guaranteed. Stress beyond the limits specified in Table 3.1 (p. 10) may affect the device reliability or cause permanent damage to the device. Functional operating conditions are given in Table 3.2 (p. 10).

Table 3.1. Absolute Maximum Ratings

| Symbol             | Parameter                      | Condition                              | Min  | Тур | Max                  | Unit |

|--------------------|--------------------------------|----------------------------------------|------|-----|----------------------|------|

| T <sub>STG</sub>   | Storage tempera-<br>ture range |                                        | -40  |     | 150                  | °C   |

| T <sub>S</sub>     | Maximum soldering temperature  | Latest IPC/JEDEC J-STD-020<br>Standard |      |     | 260                  | °C   |

| V <sub>DDMAX</sub> | External main supply voltage   |                                        | 0    |     | 3.8                  | V    |

| V <sub>IOPIN</sub> | Voltage on any I/O pin         |                                        | -0.3 |     | V <sub>DD</sub> +0.3 | V    |

|                    | Current per I/O pin (sink)     |                                        |      |     | 100                  | mA   |

| I <sub>IOMAX</sub> | Current per I/O pin (source)   |                                        |      |     | -100                 | mA   |

# 3.3 General Operating Conditions

# 3.3.1 General Operating Conditions

Table 3.2. General Operating Conditions

| Symbol            | Parameter                    | Min  | Тур | Max | Unit |

|-------------------|------------------------------|------|-----|-----|------|

| T <sub>AMB</sub>  | Ambient temperature range    | -40  |     | 85  | °C   |

| V <sub>DDOP</sub> | Operating supply voltage     | 1.98 |     | 3.8 | V    |

| f <sub>APB</sub>  | Internal APB clock frequency |      |     | 48  | MHz  |

| f <sub>AHB</sub>  | Internal AHB clock frequency |      |     | 48  | MHz  |

#### 3.9 Oscillators

#### 3.9.1 LFXO

Table 3.8. LFXO

| Symbol              | Parameter                                              | Condition                                                                                                      | Min            | Тур    | Max  | Unit |

|---------------------|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------|--------|------|------|

| f <sub>LFXO</sub>   | Supported nominal crystal frequency                    |                                                                                                                |                | 32.768 |      | kHz  |

| ESR <sub>LFXO</sub> | Supported crystal equivalent series resistance (ESR)   |                                                                                                                |                | 30     | 120  | kOhm |

| C <sub>LFXOL</sub>  | Supported crystal external load range                  |                                                                                                                | X <sup>1</sup> |        | 25   | pF   |

| DC <sub>LFXO</sub>  | Duty cycle                                             |                                                                                                                | 48             | 50     | 53.5 | %    |

| I <sub>LFXO</sub>   | Current consumption for core and buffer after startup. | ESR=30 kOhm, C <sub>L</sub> =10 pF,<br>LFXOBOOST in CMU_CTRL is<br>1                                           |                | 190    |      | nA   |

| t <sub>LFXO</sub>   | Start- up time.                                        | ESR=30 kOhm, C <sub>L</sub> =10 pF,<br>40% - 60% duty cycle has<br>been reached, LFXOBOOST in<br>CMU_CTRL is 1 |                | 400    |      | ms   |

<sup>&</sup>lt;sup>1</sup>See Minimum Load Capacitance (C<sub>LFXOL</sub>) Requirement For Safe Crystal Startup in energyAware Designer in Simplicity Studio

For safe startup of a given crystal, the Configurator tool in Simplicity Studio contains a tool to help users configure both load capacitance and software settings for using the LFXO. For details regarding the crystal configuration, the reader is referred to application note "AN0016 EFM32 Oscillator Design Consideration".

#### 3.9.2 HFXO

#### Table 3.9. HFXO

| Symbol              | Parameter                                                            | Condition                                                                          | Min | Тур | Max  | Unit |

|---------------------|----------------------------------------------------------------------|------------------------------------------------------------------------------------|-----|-----|------|------|

| f <sub>HFXO</sub>   | Supported nominal crystal Frequency                                  |                                                                                    | 4   |     | 48   | MHz  |

|                     | Supported crystal                                                    | Crystal frequency 48 MHz                                                           |     |     | 50   | Ohm  |

| ESR <sub>HFXO</sub> | equivalent series re-                                                | Crystal frequency 32 MHz                                                           |     | 30  | 60   | Ohm  |

|                     | sistance (ESR)                                                       | Crystal frequency 4 MHz                                                            |     | 400 | 1500 | Ohm  |

| g <sub>mHFXO</sub>  | The transconductance of the HFXO input transistor at crystal startup | HFXOBOOST in CMU_CTRL equals 0b11                                                  | 20  |     |      | mS   |

| C <sub>HFXOL</sub>  | Supported crystal external load range                                |                                                                                    | 5   |     | 25   | pF   |

| l                   | Current consump-                                                     | 4 MHz: ESR=400 Ohm,<br>C <sub>L</sub> =20 pF, HFXOBOOST in<br>CMU_CTRL equals 0b11 |     | 85  |      | μА   |

| I <sub>HFXO</sub>   | startup                                                              | 32 MHz: ESR=30 Ohm,<br>C <sub>L</sub> =10 pF, HFXOBOOST in<br>CMU_CTRL equals 0b11 |     | 165 |      | μΑ   |

| t <sub>HFXO</sub>   | Startup time                                                         | 32 MHz: ESR=30 Ohm,<br>C <sub>L</sub> =10 pF, HFXOBOOST in<br>CMU_CTRL equals 0b11 |     | 400 |      | μs   |

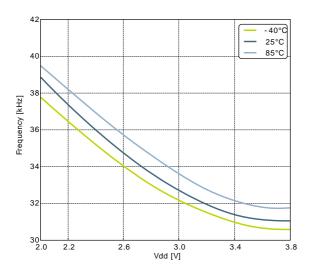

#### 3.9.3 LFRCO

Table 3.10. LFRCO

| Symbol                  | Parameter                                                               | Condition | Min   | Тур    | Max   | Unit |

|-------------------------|-------------------------------------------------------------------------|-----------|-------|--------|-------|------|

| f <sub>LFRCO</sub>      | Oscillation frequency , V <sub>DD</sub> = 3.0 V, T <sub>AMB</sub> =25°C |           | 31.29 | 32.768 | 34.28 | kHz  |

| t <sub>LFRCO</sub>      | Startup time not including software calibration                         |           |       | 150    |       | μs   |

| I <sub>LFRCO</sub>      | Current consumption                                                     |           |       | 300    | 900   | nA   |

| TUNESTEP <sub>L</sub> . | Frequency step<br>for LSB change in<br>TUNING value                     |           |       | 1.5    |       | %    |

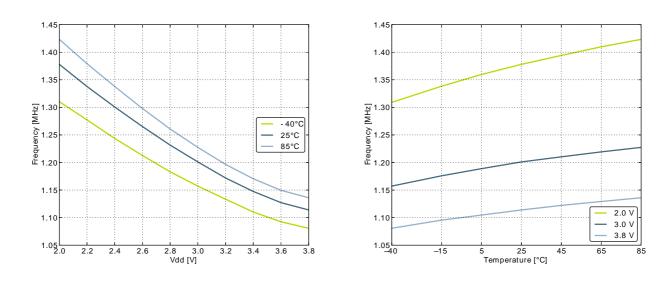

Figure 3.10. Calibrated LFRCO Frequency vs Temperature and Supply Voltage

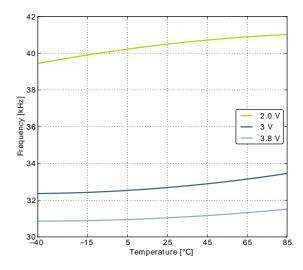

#### 3.9.4 HFRCO

Table 3.11. HFRCO

| Symbol             | Parameter                                            | Condition                   | Min               | Тур               | Max               | Unit   |

|--------------------|------------------------------------------------------|-----------------------------|-------------------|-------------------|-------------------|--------|

|                    |                                                      | 28 MHz frequency band       | 27.5              | 28.0              | 28.5              | MHz    |

|                    |                                                      | 21 MHz frequency band       | 20.6              | 21.0              | 21.4              | MHz    |

| f                  | Oscillation frequen-<br>cy, V <sub>DD</sub> = 3.0 V, | 14 MHz frequency band       | 13.7              | 14.0              | 14.3              | MHz    |

| † <sub>HFRCO</sub> | T <sub>AMB</sub> =25°C                               | 11 MHz frequency band       | 10.8              | 11.0              | 11.2              | MHz    |

|                    |                                                      | 7 MHz frequency band        | 6.48 <sup>1</sup> | 6.60 <sup>1</sup> | 6.72 <sup>1</sup> | MHz    |

|                    |                                                      | 1 MHz frequency band        | 1.15 <sup>2</sup> | 1.20 <sup>2</sup> | 1.25 <sup>2</sup> | MHz    |

| tHFRCO_settling    | Settling time after start-up                         | f <sub>HFRCO</sub> = 14 MHz |                   | 0.6               |                   | Cycles |

|                    | Settling time after band switch                      |                             |                   | 25                |                   | Cycles |

| Symbol                  | Parameter                                           | Condition                    | Min | Тур              | Max | Unit |

|-------------------------|-----------------------------------------------------|------------------------------|-----|------------------|-----|------|

|                         |                                                     | f <sub>HFRCO</sub> = 28 MHz  |     | 165              | 190 | μΑ   |

|                         |                                                     | f <sub>HFRCO</sub> = 21 MHz  |     | 134              | 155 | μΑ   |

|                         | Current consump-<br>tion (Production test           | f <sub>HFRCO</sub> = 14 MHz  |     | 106              | 120 | μΑ   |

| IHFRCO                  | condition = 14MHz)                                  | f <sub>HFRCO</sub> = 11 MHz  |     | 94               | 110 | μA   |

|                         |                                                     | f <sub>HFRCO</sub> = 6.6 MHz |     | 77               | 90  | μΑ   |

|                         |                                                     | f <sub>HFRCO</sub> = 1.2 MHz |     | 25               | 32  | μΑ   |

| TUNESTEP <sub>H</sub> . | Frequency step<br>for LSB change in<br>TUNING value |                              |     | 0.3 <sup>3</sup> |     | %    |

<sup>&</sup>lt;sup>1</sup>For devices with prod. rev. < 19, Typ = 7MHz and Min/Max values not applicable.

Figure 3.11. Calibrated HFRCO 1 MHz Band Frequency vs Supply Voltage and Temperature

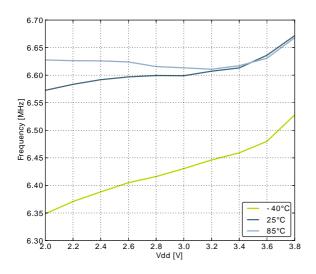

Figure 3.12. Calibrated HFRCO 7 MHz Band Frequency vs Supply Voltage and Temperature

$<sup>^{2}</sup>$ For devices with prod. rev. < 19, Typ = 1MHz and Min/Max values not applicable.

<sup>&</sup>lt;sup>3</sup>The TUNING field in the CMU\_HFRCOCTRL register may be used to adjust the HFRCO frequency. There is enough adjustment range to ensure that the frequency bands above 7 MHz will always have some overlap across supply voltage and temperature. By using a stable frequency reference such as the LFXO or HFXO, a firmware calibration routine can vary the TUNING bits and the frequency band to maintain the HFRCO frequency at any arbitrary value between 7 MHz and 28 MHz across operating conditions.

| Symbol | Parameter | Condition                                                                                                                                  | Min | Тур  | Max | Unit              |

|--------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------------------|

|        |           | V <sub>out</sub> =1V, RESSEL=0, 0.1<br>Hz <f<1 mhz,="" opaxhcmdis="0&lt;/td"><td></td><td>196</td><td></td><td>μV<sub>RMS</sub></td></f<1> |     | 196  |     | μV <sub>RMS</sub> |

|        |           | V <sub>out</sub> =1V, RESSEL=0, 0.1<br>Hz <f<1 mhz,="" opaxhcmdis="1&lt;/td"><td></td><td>229</td><td></td><td>μV<sub>RMS</sub></td></f<1> |     | 229  |     | μV <sub>RMS</sub> |

|        |           | RESSEL=7, 0.1 Hz <f<10 khz,<br="">OPAxHCMDIS=0</f<10>                                                                                      |     | 1230 |     | μV <sub>RMS</sub> |

|        |           | RESSEL=7, 0.1 Hz <f<10 khz,<br="">OPAxHCMDIS=1</f<10>                                                                                      |     | 2130 |     | μV <sub>RMS</sub> |

|        |           | RESSEL=7, 0.1 Hz <f<1 mhz,<br="">OPAxHCMDIS=0</f<1>                                                                                        |     | 1630 |     | μV <sub>RMS</sub> |

|        |           | RESSEL=7, 0.1 Hz <f<1 mhz,<br="">OPAxHCMDIS=1</f<1>                                                                                        |     | 2590 |     | μV <sub>RMS</sub> |

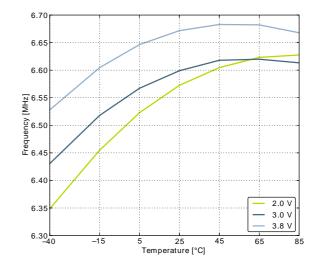

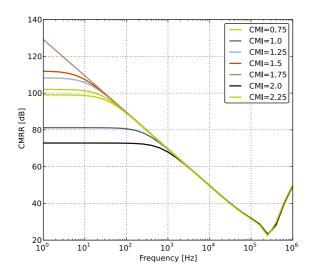

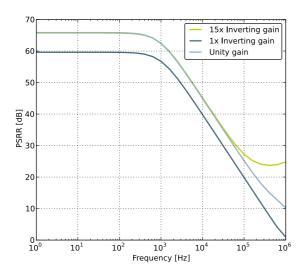

Figure 3.25. OPAMP Common Mode Rejection Ratio

Figure 3.26. OPAMP Positive Power Supply Rejection Ratio

# 3.13 Analog Comparator (ACMP)

Table 3.17. ACMP

| Symbol                  | Parameter                                         | Condition                                                                  | Min | Тур  | Max             | Unit |

|-------------------------|---------------------------------------------------|----------------------------------------------------------------------------|-----|------|-----------------|------|

| V <sub>ACMPIN</sub>     | Input voltage range                               |                                                                            | 0   |      | V <sub>DD</sub> | V    |

| V <sub>ACMPCM</sub>     | ACMP Common<br>Mode voltage range                 |                                                                            | 0   |      | V <sub>DD</sub> | V    |

|                         |                                                   | BIASPROG=0b0000, FULL-<br>BIAS=0 and HALFBIAS=1 in<br>ACMPn_CTRL register  |     | 0.1  | 0.6             | μΑ   |

| I <sub>ACMP</sub>       | Active current                                    | BIASPROG=0b1111, FULL-<br>BIAS=0 and HALFBIAS=0 in<br>ACMPn_CTRL register  |     | 2.87 | 12              | μΑ   |

|                         |                                                   | BIASPROG=0b1111, FULL-<br>BIAS=1 and HALFBIAS=0 in<br>ACMPn_CTRL register  |     | 250  | 520             | μΑ   |

| I <sub>ACMPREF</sub>    | Current consumption of internal voltage reference | Internal voltage reference off. Using external voltage reference           |     | 0    |                 | μА   |

|                         |                                                   | Internal voltage reference                                                 |     | 5    |                 | μA   |

| V <sub>ACMPOFFSET</sub> | Offset voltage                                    | BIASPROG= 0b1010, FULL-<br>BIAS=0 and HALFBIAS=0 in<br>ACMPn_CTRL register | -12 | 0    | 12              | mV   |

| V <sub>ACMPHYST</sub>   | ACMP hysteresis                                   | Programmable                                                               |     | 17   |                 | mV   |

|                         |                                                   | CSRESSEL=0b00 in<br>ACMPn_INPUTSEL                                         |     | 43   |                 | kOhm |

| <b>D</b>                | Capacitive Sense<br>Internal Resistance           | CSRESSEL=0b01 in<br>ACMPn_INPUTSEL                                         |     | 78   |                 | kOhm |

| R <sub>CSRES</sub>      |                                                   | CSRESSEL=0b10 in<br>ACMPn_INPUTSEL                                         |     | 111  |                 | kOhm |

|                         |                                                   | CSRESSEL=0b11 in<br>ACMPn_INPUTSEL                                         |     | 145  |                 | kOhm |

| t <sub>ACMPSTART</sub>  | Startup time                                      |                                                                            |     |      | 10              | μs   |

The total ACMP current is the sum of the contributions from the ACMP and its internal voltage reference as given in Equation 3.1 (p. 43) .  $I_{ACMPREF}$  is zero if an external voltage reference is used.

$$I_{ACMPTOTAL} = I_{ACMP} + I_{ACMPREF}$$

(3.1)

# 3.14 Voltage Comparator (VCMP)

Table 3.18. VCMP

| Symbol                  | Parameter                         | Condition                                                             | Min  | Тур             | Max | Unit |

|-------------------------|-----------------------------------|-----------------------------------------------------------------------|------|-----------------|-----|------|

| V <sub>VCMPIN</sub>     | Input voltage range               |                                                                       |      | V <sub>DD</sub> |     | V    |

| V <sub>VCMPCM</sub>     | VCMP Common<br>Mode voltage range |                                                                       |      | V <sub>DD</sub> |     | V    |

| 1.                      | Active current                    | BIASPROG=0b0000 and<br>HALFBIAS=1 in VCMPn_CTRL<br>register           |      | 0.3             | 0.6 | μА   |

| IVCMP                   | Active current                    | BIASPROG=0b1111 and<br>HALFBIAS=0 in VCMPn_CTRL<br>register. LPREF=0. |      | 22              | 30  | μА   |

| t <sub>VCMPREF</sub>    | Startup time reference generator  | NORMAL                                                                |      | 10              |     | μs   |

| V                       | Offset voltage                    | Single ended                                                          | -230 | -40             | 190 | mV   |

| V <sub>VCMPOFFSET</sub> | Offset voltage                    | Differential                                                          |      | 10              |     | mV   |

| V <sub>VCMPHYST</sub>   | VCMP hysteresis                   |                                                                       |      | 40              |     | mV   |

| t <sub>VCMPSTART</sub>  | Startup time                      |                                                                       |      |                 | 10  | μs   |

The  $V_{DD}$  trigger level can be configured by setting the TRIGLEVEL field of the VCMP\_CTRL register in accordance with the following equation:

VCMP Trigger Level as a Function of Level Setting

$$V_{DD \ Trigger \ Level} = 1.667 V + 0.034 \ \times TRIGLEVEL \tag{3.2}$$

#### 3.15 EBI

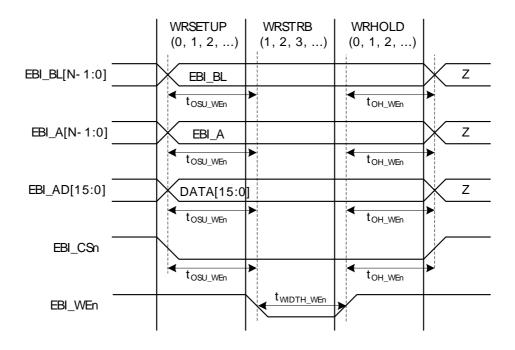

Figure 3.31. EBI Write Enable Timing

#### Table 3.19. EBI Write Enable Timing

| Symbol                   | Parameter                                                                                                  | Min                                                | Тур | Max | Unit |

|--------------------------|------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-----|-----|------|

| t <sub>OH_WEn</sub> 1234 | Output hold time, from trailing EBI_WEn/<br>EBI_NANDWEn edge to EBI_AD, EBI_A,<br>EBI_CSn, EBI_BLn invalid | -6.00 + (WRHOLD * t <sub>HFCORECLK</sub> )         |     |     | ns   |

| tosu_WEn 12345           | Output setup time, from EBI_AD, EBI_A, EBI_CSn, EBI_BLn valid to leading EBI_WEn/ EBI_NANDWEn edge         | -14.00 + (WRSETUP<br>* thfCORECLK)                 |     |     | ns   |

| twiDTH_WEn 12345         | EBI_WEn/EBI_NANDWEn pulse width                                                                            | -7.00 + ((WRSTRB<br>+1) * t <sub>HFCORECLK</sub> ) |     |     | ns   |

<sup>&</sup>lt;sup>1</sup>Applies for all addressing modes (figure only shows D16 addressing mode)

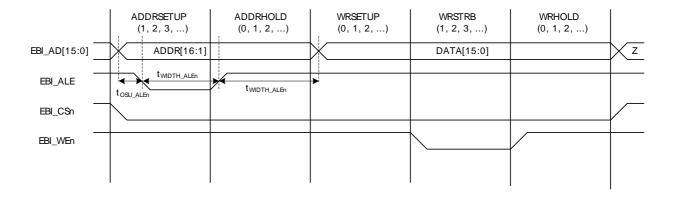

Figure 3.32. EBI Address Latch Enable Related Output Timing

Table 3.20. EBI Address Latch Enable Related Output Timing

| Symbol                       | Parameter                                                      | Min                                                                | Тур | Max | Unit |

|------------------------------|----------------------------------------------------------------|--------------------------------------------------------------------|-----|-----|------|

| t <sub>OH_ALEn</sub> 1234    | Output hold time, from trailing EBI_ALE edge to EBI_AD invalid | -6.00 + (AD-<br>DRHOLD <sup>5</sup> * t <sub>HFCORE-</sub><br>CLK) |     |     | ns   |

| t <sub>OSU_ALEn 124</sub>    | Output setup time, from EBI_AD valid to leading EBI_ALE edge   | -13.00 + (0 * t <sub>HFCORE-</sub>                                 |     |     | ns   |

| t <sub>WIDTH_ALEn</sub> 1234 | EBI_ALEn pulse width                                           | -7.00 + (ADDRSET-<br>UP+1) * t <sub>HFCORECLK</sub> )              |     |     | ns   |

Applies to addressing modes D8A24ALE and D16A16ALE (figure only shows D16A16ALE)

<sup>&</sup>lt;sup>2</sup>Applies for both EBI\_WEn and EBI\_NANWEn (figure only shows EBI\_WEn)

<sup>&</sup>lt;sup>3</sup>Applies for all polarities (figure only shows active low signals)

$<sup>^4</sup>$ Measurement done at 10% and 90% of  $V_{DD}$  (figure shows 50% of  $_{VDD}$ )

$<sup>^{5}</sup>$  The figure shows the timing for the case that the half strobe length functionality is not used, i.e. HALFWE=0. The leading edge of EBI\_WEn can be moved to the right by setting HALFWE=1. This decreases the length of  $t_{WIDTH_{WEn}}$  and increases the length of  $t_{OSU_{WEn}}$  by  $1/2 * t_{HFCLKNODIV}$ .

<sup>&</sup>lt;sup>2</sup>Applies for all polarities (figure only shows active low signals)

<sup>&</sup>lt;sup>3</sup> The figure shows the timing for the case that the half strobe length functionality is not used, i.e. HALFALE=0. The trailing edge of EBI\_ALE can be moved to the left by setting HALFALE=1. This decreases the length of t<sub>WIDTH\_ALEn</sub> and increases the length of tOH\_ALEn by t<sub>HFCORECLK</sub> - 1/2 \* t<sub>HFCLKNODIV</sub>.

<sup>&</sup>lt;sup>4</sup>Measurement done at 10% and 90% of V<sub>DD</sub> (figure shows 50% of <sub>VDD</sub>)

<sup>&</sup>lt;sup>5</sup>Figure only shows a write operation. For a multiplexed read operation the address hold time is controlled via the RDSETUP state instead of via the ADDRHOLD state.

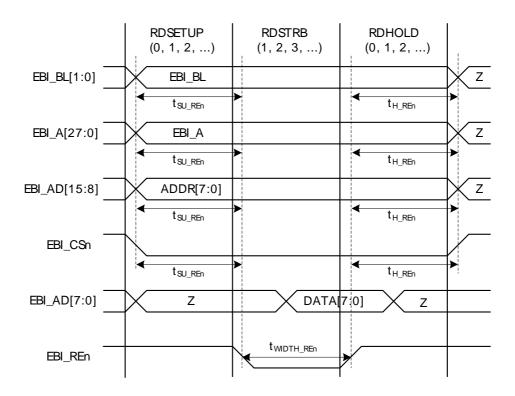

Figure 3.33. EBI Read Enable Related Output Timing

Table 3.21. EBI Read Enable Related Output Timing

| Symbol                        | Parameter                                                                                            | Min                                                     | Тур | Max | Unit |

|-------------------------------|------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-----|-----|------|

| t <sub>OH_REn</sub> 1234      | Output hold time, from trailing EBI_REn/ EBI_NANDREn edge to EBI_AD, EBI_A, EBI_CSn, EBI_BLn invalid | -10.00 + (RDHOLD * the corected)                        |     |     | ns   |

| t <sub>OSU_REn</sub> 12345    | Output setup time, from EBI_AD, EBI_A, EBI_CSn, EBI_BLn valid to leading EBI_REn/EBI_NANDREn edge    | -10.00 + (RDSETUP<br>* thfcorectk)                      |     |     | ns   |

| t <sub>WIDTH_REn</sub> 123456 | EBI_REn pulse width                                                                                  | -9.00 + ((RD-<br>STRB+1) * t <sub>HFCORE-</sub><br>CLK) |     |     | ns   |

<sup>&</sup>lt;sup>1</sup>Applies for all addressing modes (figure only shows D8A8. Output timing for EBI\_AD only applies to multiplexed addressing modes D8A24ALE and D16A16ALE)

<sup>&</sup>lt;sup>2</sup>Applies for both EBI\_REn and EBI\_NANDREn (figure only shows EBI\_REn)

<sup>&</sup>lt;sup>3</sup>Applies for all polarities (figure only shows active low signals)

$<sup>^4\</sup>text{Measurement}$  done at 10% and 90% of  $\text{V}_{\text{DD}}$  (figure shows 50% of  $_{\text{VDD}})$

$<sup>^5</sup>$ The figure shows the timing for the case that the half strobe length functionality is not used, i.e. HALFRE=0. The leading edge of EBI\_REn can be moved to the right by setting HALFRE=1. This decreases the length of  $t_{WIDTH\_REn}$  and increases the length of  $t_{OSU\_REn}$  by 1/2 \*  $t_{HFCLKNODIV}$ .

<sup>&</sup>lt;sup>6</sup>When page mode is used, RDSTRB is replaced by RDPA for page hits.

#### 3.17 I2C

Table 3.25. I2C Standard-mode (Sm)

| Symbol              | Parameter                                        | Min | Тур | Max                 | Unit |

|---------------------|--------------------------------------------------|-----|-----|---------------------|------|

| f <sub>SCL</sub>    | SCL clock frequency                              | 0   |     | 100 <sup>1</sup>    | kHz  |

| t <sub>LOW</sub>    | SCL clock low time                               | 4.7 |     |                     | μs   |

| t <sub>HIGH</sub>   | SCL clock high time                              | 4.0 |     |                     | μs   |

| t <sub>SU,DAT</sub> | SDA set-up time                                  | 250 |     |                     | ns   |

| t <sub>HD,DAT</sub> | SDA hold time                                    | 8   |     | 3450 <sup>2,3</sup> | ns   |

| t <sub>SU,STA</sub> | Repeated START condition set-up time             | 4.7 |     |                     | μs   |

| t <sub>HD,STA</sub> | (Repeated) START condition hold time             | 4.0 |     |                     | μs   |

| t <sub>SU,STO</sub> | STOP condition set-up time                       | 4.0 |     |                     | μs   |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition | 4.7 |     |                     | μs   |

<sup>&</sup>lt;sup>1</sup>For the minimum HFPERCLK frequency required in Standard-mode, see the I2C chapter in the EFM32GG Reference Manual.

#### Table 3.26. I2C Fast-mode (Fm)

| Symbol              | Parameter                                        | Min | Тур | Max                | Unit |

|---------------------|--------------------------------------------------|-----|-----|--------------------|------|

| f <sub>SCL</sub>    | SCL clock frequency                              | 0   |     | 400 <sup>1</sup>   | kHz  |

| t <sub>LOW</sub>    | SCL clock low time                               | 1.3 |     |                    | μs   |

| t <sub>HIGH</sub>   | SCL clock high time                              | 0.6 |     |                    | μs   |

| t <sub>SU,DAT</sub> | SDA set-up time                                  | 100 |     |                    | ns   |

| t <sub>HD,DAT</sub> | SDA hold time                                    | 8   |     | 900 <sup>2,3</sup> | ns   |

| t <sub>SU,STA</sub> | Repeated START condition set-up time             | 0.6 |     |                    | μs   |

| t <sub>HD,STA</sub> | (Repeated) START condition hold time             | 0.6 |     |                    | μs   |

| t <sub>SU,STO</sub> | STOP condition set-up time                       | 0.6 |     |                    | μs   |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition | 1.3 |     |                    | μs   |

For the minimum HFPERCLK frequency required in Fast-mode, see the I2C chapter in the EFM32GG Reference Manual.

<sup>&</sup>lt;sup>2</sup>The maximum SDA hold time (t<sub>HD,DAT</sub>) needs to be met only when the device does not stretch the low time of SCL (t<sub>LOW</sub>).

<sup>&</sup>lt;sup>3</sup>When transmitting data, this number is guaranteed only when I2Cn\_CLKDIV < ((3450\*10<sup>-9</sup> [s] \* f<sub>HFPERCLK</sub> [Hz]) - 4).

$<sup>^2</sup>$ The maximum SDA hold time ( $t_{HD,DAT}$ ) needs to be met only when the device does not stretch the low time of SCL ( $t_{LOW}$ ).

<sup>&</sup>lt;sup>3</sup>When transmitting data, this number is guaranteed only when I2Cn\_CLKDIV < ((900\*10<sup>-9</sup> [s] \* f<sub>HFPERCLK</sub> [Hz]) - 4).

Table 3.27. I2C Fast-mode Plus (Fm+)

| Symbol              | Parameter                                        | Min  | Тур | Max               | Unit |

|---------------------|--------------------------------------------------|------|-----|-------------------|------|

| f <sub>SCL</sub>    | SCL clock frequency                              | 0    |     | 1000 <sup>1</sup> | kHz  |

| t <sub>LOW</sub>    | SCL clock low time                               | 0.5  |     |                   | μs   |

| t <sub>HIGH</sub>   | SCL clock high time                              | 0.26 |     |                   | μs   |

| t <sub>SU,DAT</sub> | SDA set-up time                                  | 50   |     |                   | ns   |

| t <sub>HD,DAT</sub> | SDA hold time                                    | 8    |     |                   | ns   |

| t <sub>SU,STA</sub> | Repeated START condition set-up time             | 0.26 |     |                   | μs   |

| t <sub>HD,STA</sub> | (Repeated) START condition hold time             | 0.26 |     |                   | μs   |

| t <sub>SU,STO</sub> | STOP condition set-up time                       | 0.26 |     |                   | μs   |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition | 0.5  |     |                   | μs   |

<sup>&</sup>lt;sup>1</sup>For the minimum HFPERCLK frequency required in Fast-mode Plus, see the I2C chapter in the EFM32GG Reference Manual.

### 3.18 USART SPI

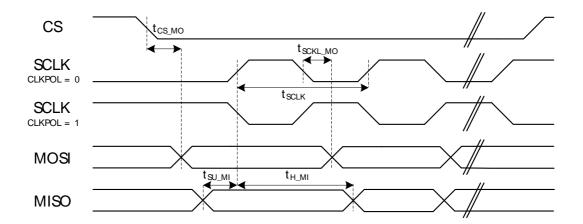

Figure 3.36. SPI Master Timing

Table 3.28. SPI Master Timing

| Symbol                   | Parameter       | Condition      | Min                     | Тур | Max  | Unit |

|--------------------------|-----------------|----------------|-------------------------|-----|------|------|

| t <sub>SCLK</sub> 1 2    | SCLK period     |                | 2 * t <sub>HFPER-</sub> |     |      | ns   |

|                          |                 |                | CLK                     |     |      |      |

| t <sub>CS_MO</sub> 12    | CS to MOSI      |                | -2.00                   |     | 1.00 | ns   |

| t <sub>SCLK_MO</sub> 1 2 | SCLK to MOSI    |                | -4.00                   |     | 3.00 | ns   |

| t <sub>SU_MI</sub> 12    | MISO setup time | IOVDD = 1.98 V | 36.00                   |     |      | ns   |

|                          |                 | IOVDD = 3.0 V  | 29.00                   |     |      | ns   |

| t <sub>H_MI</sub> 1 2    | MISO hold time  |                | -4.00                   |     |      | ns   |

<sup>&</sup>lt;sup>1</sup>Applies for both CLKPHA = 0 and CLKPHA = 1 (figure only shows CLKPHA = 0)

$<sup>^2\</sup>mbox{Measurement}$  done at 10% and 90% of  $\mbox{V}_{\mbox{DD}}$  (figure shows 50% of  $\mbox{V}_{\mbox{DD}})$

| Alternate     |      |      | L    | OCATIO | N |   |   |                                                                      |

|---------------|------|------|------|--------|---|---|---|----------------------------------------------------------------------|

| Functionality | 0    | 1    | 2    | 3      | 4 | 5 | 6 | Description                                                          |

| EBI_AD02      | PE10 | PE10 | PE10 |        |   |   |   | External Bus Interface (EBI) address and data input / output pin 02. |

| EBI_AD03      | PE11 | PE11 | PE11 |        |   |   |   | External Bus Interface (EBI) address and data input / output pin 03. |

| EBI_AD04      | PE12 | PE12 | PE12 |        |   |   |   | External Bus Interface (EBI) address and data input / output pin 04. |

| EBI_AD05      | PE13 | PE13 | PE13 |        |   |   |   | External Bus Interface (EBI) address and data input / output pin 05. |

| EBI_AD06      | PE14 | PE14 | PE14 |        |   |   |   | External Bus Interface (EBI) address and data input / output pin 06. |

| EBI_AD07      | PE15 | PE15 | PE15 |        |   |   |   | External Bus Interface (EBI) address and data input / output pin 07. |

| EBI_AD08      | PA15 | PA15 | PA15 |        |   |   |   | External Bus Interface (EBI) address and data input / output pin 08. |

| EBI_AD09      | PA0  | PA0  | PA0  |        |   |   |   | External Bus Interface (EBI) address and data input / output pin 09. |

| EBI_AD10      | PA1  | PA1  | PA1  |        |   |   |   | External Bus Interface (EBI) address and data input / output pin 10. |

| EBI_AD11      | PA2  | PA2  | PA2  |        |   |   |   | External Bus Interface (EBI) address and data input / output pin 11. |

| EBI_AD12      | PA3  | PA3  | PA3  |        |   |   |   | External Bus Interface (EBI) address and data input / output pin 12. |

| EBI_AD13      | PA4  | PA4  | PA4  |        |   |   |   | External Bus Interface (EBI) address and data input / output pin 13. |

| EBI_AD14      | PA5  | PA5  | PA5  |        |   |   |   | External Bus Interface (EBI) address and data input / output pin 14. |

| EBI_AD15      | PA6  | PA6  | PA6  |        |   |   |   | External Bus Interface (EBI) address and data input / output pin 15. |

| EBI_ALE       | PF3  | PC11 | PC11 |        |   |   |   | External Bus Interface (EBI) Address Latch Enable output.            |

| EBI_ARDY      | PF2  | PF2  | PF2  |        |   |   |   | External Bus Interface (EBI) Hardware Ready Control input.           |

| EBI_BL0       | PF6  | PF6  | PF6  |        |   |   |   | External Bus Interface (EBI) Byte Lane/Enable pin 0.                 |

| EBI_BL1       | PF7  | PF7  | PF7  |        |   |   |   | External Bus Interface (EBI) Byte Lane/Enable pin 1.                 |

| EBI_CS0       | PD9  | PD9  | PD9  |        |   |   |   | External Bus Interface (EBI) Chip Select output 0.                   |

| EBI_CS1       | PD10 | PD10 | PD10 |        |   |   |   | External Bus Interface (EBI) Chip Select output 1.                   |

| EBI_CS2       | PD11 | PD11 | PD11 |        |   |   |   | External Bus Interface (EBI) Chip Select output 2.                   |

| EBI_CS3       | PD12 | PD12 | PD12 |        |   |   |   | External Bus Interface (EBI) Chip Select output 3.                   |

| EBI_CSTFT     | PA7  | PA7  | PA7  |        |   |   |   | External Bus Interface (EBI) Chip Select output TFT.                 |

| EBI_DCLK      | PA8  | PA8  | PA8  |        |   |   |   | External Bus Interface (EBI) TFT Dot Clock pin.                      |

|               |      |      |      |        |   |   |   | ` , ,                                                                |

| EBI_DTEN      | PA9  | PA9  | PA9  |        |   |   |   | External Bus Interface (EBI) TFT Data Enable pin.                    |

| EBI_HSNC      | PA11 | PA11 | PA11 |        |   |   |   | External Bus Interface (EBI) TFT Horizontal Synchronization pin.     |

| EBI_NANDREn   | PC3  | PC3  | PC3  |        |   |   |   | External Bus Interface (EBI) NAND Read Enable output.                |

| EBI_NANDWEn   | PC5  | PC5  | PC5  |        |   |   |   | External Bus Interface (EBI) NAND Write Enable output.               |

| EBI_REn       | PF5  | PF9  | PF5  |        |   |   |   | External Bus Interface (EBI) Read Enable output.                     |

| EBI_VSNC      | PA10 | PA10 | PA10 |        |   |   |   | External Bus Interface (EBI) TFT Vertical Synchronization pin.       |

| EBI_WEn       | PF4  | PF8  | PF4  |        |   |   |   | External Bus Interface (EBI) Write Enable output.                    |

| ETM_TCLK      | PD7  | PF8  | PC6  | PA6    |   |   |   | Embedded Trace Module ETM clock .                                    |

| ETM_TD0       | PD6  | PF9  | PC7  | PA2    |   |   |   | Embedded Trace Module ETM data 0.                                    |

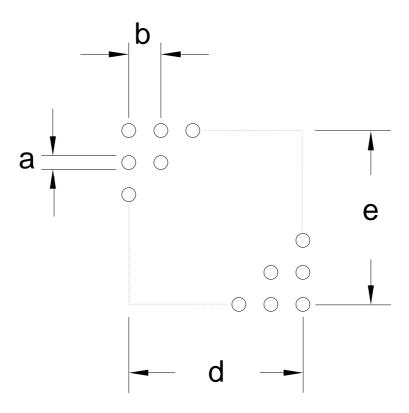

Figure 5.2. BGA112 PCB Solder Mask

Table 5.2. BGA112 PCB Solder Mask Dimensions (Dimensions in mm)

| Symbol | Dim. (mm) |

|--------|-----------|

| а      | 0.48      |

| b      | 0.80      |

| d      | 8.00      |

| е      | 8.00      |

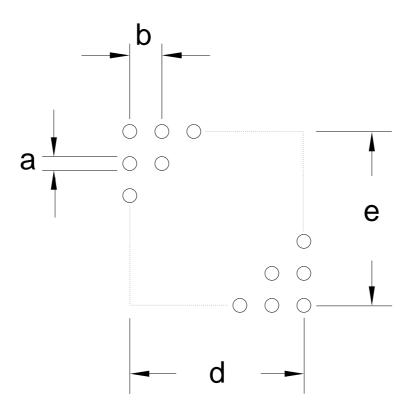

Figure 5.3. BGA112 PCB Stencil Design

Table 5.3. BGA112 PCB Stencil Design Dimensions (Dimensions in mm)

| Symbol | Dim. (mm) |

|--------|-----------|

| а      | 0.33      |

| b      | 0.80      |

| d      | 8.00      |

| е      | 8.00      |

- 1. The drawings are not to scale.

- 2. All dimensions are in millimeters.

- 3. All drawings are subject to change without notice.

- 4. The PCB Land Pattern drawing is in compliance with IPC-7351B.

- 5. Stencil thickness 0.125 mm.

- 6. For detailed pin-positioning, see Figure 4.3 (p. 67).

# **5.2 Soldering Information**

The latest IPC/JEDEC J-STD-020 recommendations for Pb-Free reflow soldering should be followed.

Updated PCB Land Pattern, PCB Solder Mask and PCB Stencil Design figures.

Updated power requirements in the Power Management section.

Removed minimum load capacitance figure and table. Added reference to application note.

Other minor corrections.

#### **7.6 Revision 1.00**

September 11th, 2012

Updated the HFRCO 1 MHz band typical value to 1.2 MHz.

Updated the HFRCO 7 MHz band typical value to 6.6 MHz.

Other minor corrections.

#### **7.7 Revision 0.98**

May 25th, 2012

Corrected BGA solder balls material description.

Corrected EM3 current consumption in the Electrical Characteristics section.

#### 7.8 Revision 0.96

February 28th, 2012

Added reference to errata document.

Corrected BGA112 package drawing.

Updated PCB land pattern, solder mask and stencil design.

#### 7.9 Revision 0.95

September 28th, 2011

Flash configuration for Giant Gecko is now 1024KB or 512KB. For flash sizes below 512KB, see the Leopard Gecko Family.

Corrected operating voltage from 1.8 V to 1.85 V.

Added rising POR level to Electrical Characteristics section.

Updated Minimum Load Capacitance (C<sub>LFXOL</sub>) Requirement For Safe Crystal Startup.

Added Gain error drift and Offset error drift to ADC table.

Added Opamp pinout overview.

Added reference to errata document.

Corrected BGA112 package drawing.

Updated PCB land pattern, solder mask and stencil design.

# **List of Figures**

| 2.1. Block Diagram                                                             | 3    |

|--------------------------------------------------------------------------------|------|

| 2.2. EFM32GG890 Memory Map with largest RAM and Flash sizes                    | 9    |

| 3.1. EM2 current consumption. RTC prescaled to 1 Hz, 32.768 kHz LFRCO.         | . 12 |

| 3.2. EM3 current consumption.                                                  | . 12 |

| 3.3. EM4 current consumption.                                                  | 13   |

| 3.4. Typical Low-Level Output Current, 2V Supply Voltage                       | . 17 |

| 3.5. Typical High-Level Output Current, 2V Supply Voltage                      |      |

| 3.6. Typical Low-Level Output Current, 3V Supply Voltage                       | . 19 |

| 3.7. Typical High-Level Output Current, 3V Supply Voltage                      | 20   |

| 3.8. Typical Low-Level Output Current, 3.8V Supply Voltage                     | 21   |

| 3.9. Typical High-Level Output Current, 3.8V Supply Voltage                    |      |

| 3.10. Calibrated LFRCO Frequency vs Temperature and Supply Voltage             | . 24 |

| 3.11. Calibrated HFRCO 1 MHz Band Frequency vs Supply Voltage and Temperature  | 25   |

| 3.12. Calibrated HFRCO 7 MHz Band Frequency vs Supply Voltage and Temperature  | 25   |

| 3.13. Calibrated HFRCO 11 MHz Band Frequency vs Supply Voltage and Temperature |      |

| 3.14. Calibrated HFRCO 14 MHz Band Frequency vs Supply Voltage and Temperature | . 26 |

| 3.15. Calibrated HFRCO 21 MHz Band Frequency vs Supply Voltage and Temperature | . 26 |

| 3.16. Calibrated HFRCO 28 MHz Band Frequency vs Supply Voltage and Temperature |      |

| 3.17. Integral Non-Linearity (INL)                                             | 32   |

| 3.18. Differential Non-Linearity (DNL)                                         |      |

| 3.19. ADC Frequency Spectrum, Vdd = 3V, Temp = 25°C                            | 34   |

| 3.20. ADC Integral Linearity Error vs Code, Vdd = 3V, Temp = 25°C              | 35   |

| 3.21. ADC Differential Linearity Error vs Code, Vdd = 3V, Temp = 25°C          | 36   |

| 3.22. ADC Absolute Offset, Common Mode = Vdd /2                                | . 37 |

| 3.23. ADC Dynamic Performance vs Temperature for all ADC References, Vdd = 3V  |      |

| 3.24. ADC Temperature sensor readout                                           |      |

| 3.25. OPAMP Common Mode Rejection Ratio                                        |      |

| 3.26. OPAMP Positive Power Supply Rejection Ratio                              | . 41 |

| 3.27. OPAMP Negative Power Supply Rejection Ratio                              | 42   |

| 3.28. OPAMP Voltage Noise Spectral Density (Unity Gain) V <sub>out</sub> =1V   | . 42 |

| 3.29. OPAMP Voltage Noise Spectral Density (Non-Unity Gain)                    | . 42 |

| 3.30. ACMP Characteristics, Vdd = 3V, Temp = 25°C, FULLBIAS = 0, HALFBIAS = 1  | 44   |

| 3.31. EBI Write Enable Timing                                                  | . 45 |

| 3.32. EBI Address Latch Enable Related Output Timing                           | 46   |

| 3.33. EBI Read Enable Related Output Timing                                    |      |

| 3.34. EBI Read Enable Related Timing Requirements                              | . 48 |

| 3.35. EBI Ready/Wait Related Timing Requirements                               |      |

| 3.36. SPI Master Timing                                                        |      |

| 3.37. SPI Slave Timing                                                         |      |

| 4.1. EFM32GG890 Pinout (top view, not to scale)                                | 54   |

| 4.2. Opamp Pinout                                                              |      |

| 4.3. BGA112                                                                    |      |

| 5.1. BGA112 PCB Land Pattern                                                   |      |

| 5.2. BGA112 PCB Solder Mask                                                    |      |

| 5.3. BGA112 PCB Stencil Design                                                 |      |

| 6.1 Example Chip Marking (top view)                                            | 72   |

community.silabs.com

#### Disclaimer

Silicon Laboratories intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Laboratories products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Laboratories reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Laboratories shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products are not designed or authorized to be used within any Life Support System without the specific written consent of Silicon Laboratories. A "Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Laboratories products are not designed or authorized for military applications. Silicon Laboratories products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.

#### **Trademark Information**

Silicon Laboratories Inc.®, Silicon Laboratories®, Silicon Labse, Silicon Laboratories Inc. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701 USA