Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| -                          |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Details                    |                                                                            |

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                           |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                  |

| Data Converters            | A/D 4x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 18-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c712-04i-so |

#### 2.2 **Data Memory Organization**

The data memory is partitioned into multiple banks which contain the General Purpose Registers and the Special Function Registers. Bits RP1 and RP0 are the bank select bits.

RP1<sup>(1)</sup> RP0

(STATUS<6:5>)

- $= 00 \rightarrow Bank 0$

- $= 01 \rightarrow Bank 1$

- = 10 → Bank 2 (not implemented)

- = 11 → Bank 3 (not implemented)

Note 1: Maintain this bit clear to ensure upward compatibility with future products.

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers, implemented as static RAM. All implemented banks contain Special Function Registers. Some "high use" Special Function Registers from one bank may be mirrored in another bank for code reduction and quicker access.

#### 2.2.1 GENERAL PURPOSE REGISTER **FILE**

The register file can be accessed either directly, or indirectly through the File Select Register FSR (see Section 2.5 "Indirect Addressing, INDF and FSR Registers").

FIGURE 2-3: **REGISTER FILE MAP**

| URE 2-3: | , RE                | GISTER FIL           | LIVIAP  |

|----------|---------------------|----------------------|---------|

| File     |                     |                      | File    |

| Address  |                     |                      | Address |

| 00h      | INDF <sup>(1)</sup> | INDF <sup>(1)</sup>  | 80h     |

| 01h      | TMR0                | OPTION_REG           | 81h     |

| 02h      | PCL                 | PCL                  | 82h     |

| 03h      | STATUS              | STATUS               | 83h     |

| 04h      | FSR                 | FSR                  | 84h     |

| 05h      | PORTA               | TRISA                | 85h     |

| 06h      | PORTB               | TRISB                | 86h     |

| 07h      | DATACCP             | TRISCCP              | 87h     |

| 08h      |                     |                      | 88h     |

| 09h      |                     |                      | 89h     |

| 0Ah      | PCLATH              | PCLATH               | 8Ah     |

| 0Bh      | INTCON              | INTCON               | 8Bh     |

| 0Ch      | PIR1                | PIE1                 | 8Ch     |

| 0Dh      |                     |                      | 8Dh     |

| 0Eh      | TMR1L               | PCON                 | 8Eh     |

| 0Fh      | TMR1H               |                      | 8Fh     |

| 10h      | T1CON               |                      | 90h     |

| 11h      | TMR2                |                      | 91h     |

| 12h      | 12h T2CON PR        |                      | 92h     |

| 13h      |                     |                      | 93h     |

| 14h      |                     |                      | 94h     |

| 15h      | CCPR1L              |                      | 95h     |

| 16h      | CCPR1H              |                      | 96h     |

| 17h      | CCP1CON             |                      | 97h     |

| 18h      |                     |                      | 98h     |

| 19h      |                     |                      | 99h     |

| 1Ah      |                     |                      | 9Ah     |

| 1Bh      |                     |                      | 9Bh     |

| 1Ch      |                     |                      | 9Ch     |

| 1Dh      |                     |                      | 9Dh     |

| 1Eh      | ADRES               |                      | 9Eh     |

| 1Fh      | ADCON0              | ADCON1               | 9Fh     |

| 20h      |                     | General              | A0h     |

|          | General             | Purpose<br>Registers |         |

|          | Purpose             | 32 Bytes             | BFh     |

|          | Registers           | ,                    | C0h     |

|          | 96 Bytes            |                      |         |

| 7Fh      |                     |                      | FFh     |

|          | Bank 0              | Bank 1               |         |

| Unir     |                     | ata memory loc       | ations. |

|          | as '0'.             |                      | =::=;   |

|          | a physical re       | gister.              |         |

|          |                     |                      |         |

TABLE 2-1: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

| Addr    | Name                    | Bit 7                                         | Bit 6                                  | Bit 5       | Bit 4           | Bit 3         | Bit 2           | Bit 1         | Bit 0     | Value on:<br>POR,<br>BOR | Value on<br>all other<br>Resets (4) |

|---------|-------------------------|-----------------------------------------------|----------------------------------------|-------------|-----------------|---------------|-----------------|---------------|-----------|--------------------------|-------------------------------------|

| Bank 1  | Bank 1                  |                                               |                                        |             |                 |               |                 |               |           |                          |                                     |

| 80h     | INDF <sup>(1)</sup>     | Addressing                                    | this location                          | uses conten | ts of FSR to ac | ldress data r | nemory (not     | a physical re | gister)   | 0000 0000                | 0000 0000                           |

| 81h     | OPTION_<br>REG          | RBPU                                          | INTEDG                                 | T0CS        | T0SE            | PSA           | PS2             | PS1           | PS0       | 1111 1111                | 1111 1111                           |

| 82h     | PCL <sup>(1)</sup>      | Program Counter's (PC) Least Significant Byte |                                        |             |                 |               |                 |               |           |                          | 0000 0000                           |

| 83h     | STATUS <sup>(1)</sup>   | IRP <sup>(4)</sup>                            | RP1 <sup>(4)</sup>                     | RP0         | TO              | PD            | Z               | DC            | С         | rr01 1xxx                | rr0q quuu                           |

| 84h     | FSR <sup>(1)</sup>      | Indirect Data Memory Address Pointer          |                                        |             |                 |               |                 |               | xxxx xxxx | uuuu uuuu                |                                     |

| 85h     | TRISA                   | ı                                             | — ———————————————————————————————————— |             |                 |               |                 |               |           | x1 1111                  | x1 1111                             |

| 86h     | TRISB                   | PORTB Data Direction Register                 |                                        |             |                 |               |                 |               | 1111 1111 | 1111 1111                |                                     |

| 87h     | TRISCCP                 | (7)                                           | (7)                                    | (7)         | (7)             |               |                 |               |           | xxxx x1x1                | xxxx x1x1                           |

| 88h-89h | -                       | Unimpleme                                     | nted                                   |             |                 |               |                 |               |           | -                        | -                                   |

| 8Ah     | PCLATH <sup>(1,2)</sup> | _                                             | _                                      | _           | Write Buffer fo | or the upper  | 5 bits of the F | Program Cou   | nter      | 0 0000                   | 0 0000                              |

| 8Bh     | INTCON <sup>(1)</sup>   | GIE                                           | PEIE                                   | TOIE        | INTE            | RBIE          | TOIF            | INTF          | RBIF      | 0000 000x                | 0000 000u                           |

| 8Ch     | PIE1                    | _                                             | ADIE                                   | _           | _               | _             | CCP1IE          | TMR2IE        | TMR1IE    | -0000                    | -0000                               |

| 8Dh     | -                       | Unimpleme                                     | nted                                   |             |                 |               |                 |               |           | -                        | -                                   |

| 8Eh     | PCON                    | _                                             | _                                      | _           | _               | _             | _               | POR           | BOR       | qq                       | uu                                  |

| 8Fh-91h | _                       | Unimpleme                                     | nted                                   |             |                 |               |                 |               |           | -                        | -                                   |

| 92h     | PR2                     | Timer2 Peri                                   | od Register                            |             |                 |               |                 |               |           | 1111 1111                | 1111 1111                           |

| 93h-9Eh |                         | Unimplemented                                 |                                        |             |                 |               |                 |               |           | _                        | -                                   |

| 9Fh     | ADCON1                  | _                                             | _                                      | _           | _               | _             | PCFG2           | PCFG1         | PCFG0     | 000                      | 000                                 |

**Legend:** x = unknown, u = unchanged, q = value depends on condition, — = unimplemented, read as '0', Shaded locations are unimplemented, read as '0'.

- Note 1: These registers can be addressed from either bank.

- 2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for PC<12:8> whose contents are transferred to the upper byte of the program counter.

- 3: Other (non Power-up) Resets include: external Reset through  $\overline{\text{MCLR}}$  and the Watchdog Timer Reset.

- 4: The IRP and RP1 bits are reserved. Always maintain these bits clear.

- 5: On any device Reset, these pins are configured as inputs.

- 6: This is the value that will be in the port output latch.

- 7: Reserved bits; Do Not Use.

## 2.2.2.3 INTCON Register

The INTCON Register is a readable and writable register which contains various enable and flag bits for the TMR0 register overflow, RB Port change and External RB0/INT pin interrupts.

Note:

Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

## FIGURE 2-6: INTCON REGISTER (ADDRESS 0Bh, 8Bh)

| R/W-0   | R/W-0                           | R/W-0                        | R/W-0       | R/W-0   | R/W-0              | R/W-0        | R/W-x         |                                       |  |  |

|---------|---------------------------------|------------------------------|-------------|---------|--------------------|--------------|---------------|---------------------------------------|--|--|

| GIE     | PEIE                            | T0IE                         | INTE        | RBIE    | T0IF               | INTF         | RBIF          | R = Readable bit                      |  |  |

| bit7    |                                 |                              |             |         |                    |              | bit0          | W = Writable bit                      |  |  |

|         |                                 |                              |             |         |                    |              |               | U = Unimplemented bit,<br>read as '0' |  |  |

|         |                                 |                              |             |         |                    |              |               | -n = Value at POR Reset               |  |  |

| bit 7:  | GIE: Glob                       | oal Interrup                 | ot Enable   | bit     |                    |              |               |                                       |  |  |

|         |                                 | les all unm                  |             | errupts |                    |              |               |                                       |  |  |

|         | 0 = Disables all interrupts     |                              |             |         |                    |              |               |                                       |  |  |

| bit 6:  |                                 | ripheral In                  |             |         |                    |              |               |                                       |  |  |

|         |                                 | les all unm                  |             |         | terrupts           |              |               |                                       |  |  |

|         | 0 = Disab                       | les all per                  | ipheral int | errupts |                    |              |               |                                       |  |  |

| bit 5:  |                                 | R0 Overflo                   |             |         | bit                |              |               |                                       |  |  |

|         |                                 | les the TM                   |             | •       |                    |              |               |                                       |  |  |

|         | 0 = Disables the TMR0 interrupt |                              |             |         |                    |              |               |                                       |  |  |

| bit 4:  |                                 | 30/INT Ext                   |             |         |                    |              |               |                                       |  |  |

|         |                                 | les the RB                   |             |         | •                  |              |               |                                       |  |  |

|         |                                 | les the RE                   |             |         | •                  |              |               |                                       |  |  |

| bit 3:  |                                 | Port Cha                     |             |         |                    |              |               |                                       |  |  |

|         |                                 | les the RB<br>les the RE     | •           | •       | •                  |              |               |                                       |  |  |

| 1.11.0  |                                 |                              | •           | Ü       | •                  |              |               |                                       |  |  |

| bit 2:  |                                 | R0 Overflo                   |             |         |                    | d in aaftuur | \ra\          |                                       |  |  |

|         |                                 | ) register (<br>) register ( |             |         | st be cleare       | u in Soliwa  | ire)          |                                       |  |  |

| late A. |                                 | ŭ                            |             |         | - : 4              |              |               |                                       |  |  |

| bit 1:  |                                 | O/INT Exte                   |             |         | oit<br>urred (must | he cleare    | d in coftwa   | ro)                                   |  |  |

|         |                                 | RB0/INT ex                   |             | •       | •                  | De cicare    | a iii soitwai | 16)                                   |  |  |

| bit 0:  |                                 | Port Cha                     |             | •       |                    |              |               |                                       |  |  |

| DIL U.  |                                 |                              |             |         | n<br>hanged stat   | e (must be   | e cleared in  | software)                             |  |  |

|         |                                 |                              |             |         | anged state        |              | 2.00.00 111   |                                       |  |  |

|         |                                 |                              | •           |         | -                  |              |               |                                       |  |  |

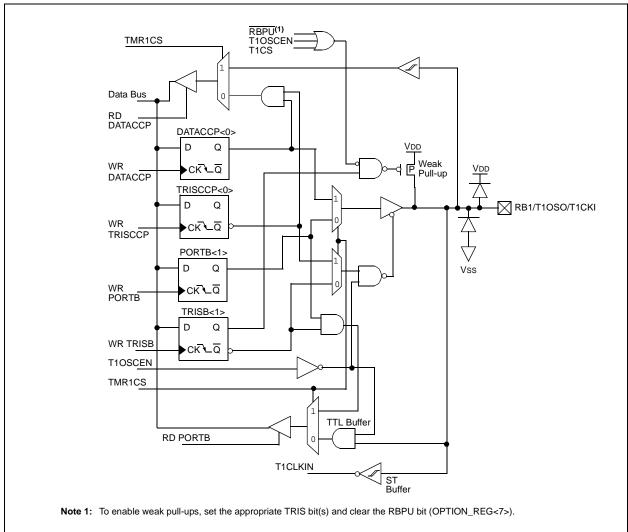

PORTB pins RB3:RB1 are multiplexed with several peripheral functions (Table 3-3). PORTB pins RB3:RB0 have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTB pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override is in effect while the peripheral is enabled, read-modify-write instructions (BSF, BCF, XORWF) with TRISB as destination should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

Four of PORTB's pins, RB7:RB4, have an interrupt-onchange feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupton-change comparison). The input pins, RB7:RB4, are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RB Port Change Interrupt with flag bit RBIF (INTCON<0>).

This interrupt can wake the device from Sleep. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

FIGURE 3-4: BLOCK DIAGRAM OF RB1/T10S0/T1CKI PIN

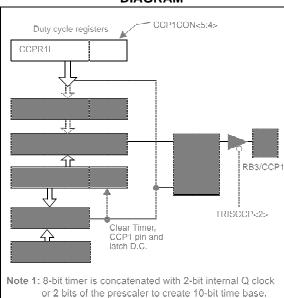

### 7.3 PWM Mode

In Pulse Width Modulation (PWM) mode, the CCP1 pin produces up to a 10-bit resolution PWM output. Since the CCP1 pin is multiplexed with the PORTB data latch, the TRISCCP<2> bit must be cleared to make the CCP1 pin an output.

Note: Clearing the CCP1CON register will force the CCP1 PWM output latch to the default low level. This is neither the PORTB I/O data latch nor the DATACCP latch.

Figure 7-5 shows a simplified block diagram of the CCP module in PWM mode.

For a step by step procedure on how to set up the CCP module for PWM operation, see **Section 7.3.3** "**Set-Up for PWM Operation**".

# FIGURE 7-5: SIMPLIFIED PWM BLOCK DIAGRAM

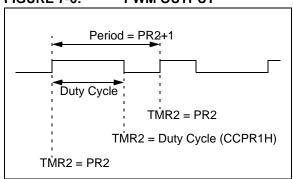

A PWM output (Figure 7-6) has a time base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is the inverse of the period (1/period).

## FIGURE 7-6: PWM OUTPUT

#### 7.3.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula:

PWM period =

$$[(PR2) + 1] \cdot 4 \cdot TOSC \cdot (TMR2 \text{ prescale value})$$

PWM frequency is defined as 1 / [PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP1 pin is set (exception: if PWM duty cycle = 0%, the CCP1 pin will not be set)

- The PWM duty cycle is latched from CCPR1L into CCPR1H

Note: The Timer2 postscaler (see Section 6.0 "Timer2 Module") is not used in the determination of the PWM frequency. The postscaler could be used to have a servo update rate at a different frequency than the PWM output.

### 7.3.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPR1L register and to the CCP1CON<5:4> bits. Up to 10-bit resolution is available. The CCPR1L contains the eight MSbs and the CCP1CON<5:4> contains the two LSbs. This 10-bit value is represented by CCPR1L:CCP1CON<5:4>. The following equation is used to calculate the PWM duty cycle in time:

CCPR1L and CCP1CON<5:4> can be written to at any time, but the duty cycle value is not latched into CCPR1H until after a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPR1H is a read-only register.

The CCPR1H register and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering is essential for glitchless PWM operation.

When the CCPR1H and 2-bit latch match TMR2 concatenated with an internal 2-bit Q clock or 2 bits of the TMR2 prescaler, the CCP1 pin is cleared.

Maximum PWM resolution (bits) for a given PWM frequency:

$$= \frac{\log(\frac{Fosc}{Fpwm})}{\log(2)}$$

bits

**Note:** If the PWM duty cycle value is longer than the PWM period the CCP1 pin will not be cleared.

For an example PWM period and duty cycle calculation, see the PIC<sup>®</sup> Mid-Range Reference Manual, (DS33023).

## 7.3.3 SET-UP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- 2. Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- 3. Make the CCP1 pin an output by clearing the TRISCCP<2> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

- 5. Configure the CCP1 module for PWM operation.

## TABLE 7-3: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 20 MHz

| PWM Frequency              | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|----------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                  | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits)  | 10       | 10       | 10        | 8         | 7         | 5.5       |

### TABLE 7-4: REGISTERS ASSOCIATED WITH PWM AND TIMER2

| Address | Name    | Bit 7                           | Bit 6      | Bit 5        | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|---------|---------|---------------------------------|------------|--------------|---------|---------|--------|---------|---------|-------------------------|---------------------------------|

| 07h     | DATACCP | _                               | _          | _            | _       | _       | DCCP   | _       | DT1CK   | xxxx xxxx               | xxxx xuxu                       |

| 0Bh,8Bh | INTCON  | GIE                             | PEIE       | TOIE         | INTE    | RBIE    | TOIF   | INTF    | RBIF    | 0000 000x               | 0000 000u                       |

| 0Ch     | PIR1    | _                               | ADIF       | _            | _       | _       | CCP1IF | TMR2IF  | TMR1IF  | -0000                   | -0000                           |

| 11h     | TMR2    | Timer2 Module's Register        |            |              |         |         |        |         |         |                         | 0000 0000                       |

| 12h     | T2CON   | _                               | TOUTPS3    | TOUTPS2      | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000               | -000 0000                       |

| 15h     | CCPR1L  | Capture/C                       | ompare/PWI | √ Register 1 | (LSB)   |         |        |         |         | xxxx xxxx               | uuuu uuuu                       |

| 16h     | CCPR1H  | Capture/C                       | ompare/PWI |              | (MSB)   |         |        |         |         | xxxx xxxx               | uuuu uuuu                       |

| 17h     | CCP1CON | _                               | _          | DC1B1        | DC1B0   | CCP1M3  | CCP1M2 | CCP1M1  | CCP1M0  | 00 0000                 | 00 0000                         |

| 87h     | TRISCCP | _                               | _          | _            | _       | _       | TCCP   | _       | TT1CK   | xxxx x1x1               | xxxx x1x1                       |

| 8Ch     | PIE1    | _                               | ADIE       | _            | _       | _       | CCP1IE | TMR2IE  | TMR1IE  | -0000                   | -0000                           |

| 92h     | PR2     | Timer2 Module's Period Register |            |              |         |         |        |         |         | 1111 1111               | 1111 1111                       |

**Legend:** x = unknown, u = unchanged, — = unimplemented read as '0'. Shaded cells are not used by PWM and Timer2.

## FIGURE 8-2: ADCON1 REGISTER (ADDRESS 9Fh)

|     |     |     |     |     | PCFG2 | DCEC1 | DCEC0 |

|-----|-----|-----|-----|-----|-------|-------|-------|

| U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 |

bit7

R = Readable bit

W = Writable bit

bit0

U = Unimplemented bit, read as '0'

-n = Value at POR Reset

bit 7-3: Unimplemented: Read as '0'

bit 2-0: PCFG2:PCFG0: A/D Port Configuration Control bits

| PCFG2:PCFG0 | RA0 | RA1 | RA2 | RA3  | VREF |

|-------------|-----|-----|-----|------|------|

| 0x0         | Α   | Α   | Α   | Α    | Vdd  |

| 0x1         | Α   | Α   | Α   | VREF | RA3  |

| 100         | Α   | Α   | D   | Α    | VDD  |

| 101         | Α   | Α   | D   | VREF | RA3  |

| 11x         | D   | D   | D   | D    | Vdd  |

A = Analog input

D = Digital I/O

## 8.1 A/D Acquisition Requirements

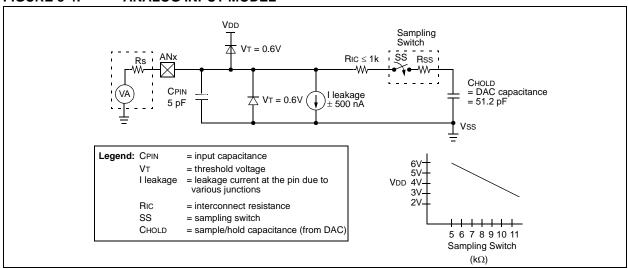

For the A/D converter to meet its specified accuracy, the Charge Holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 8-4. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD). The source impedance affects the offset voltage at the analog input (due to pin leakage current). The maximum recommended impedance for analog sources is 10  $k\Omega$ . After the analog input channel is selected (changed) this acquisition must be done before the conversion can be started.

To calculate the minimum acquisition time, TACQ, see the PIC<sup>®</sup> Mid-Range Reference Manual, (DS33023). This equation calculates the acquisition time to within 1/2 LSb error (512 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified accuracy.

When the conversion is started, the holding capacitor is disconnected from the input pin.

FIGURE 8-4: ANALOG INPUT MODEL

Note:

## 8.4 A/D Conversions

Note: The GO/DONE bit should NOT be set in the same instruction that turns on the A/D.

## 8.5 Use of the CCP Trigger

An A/D conversion can be started by the "Special Event Trigger" of the CCP1 module. This requires that the CCP1M3:CCP1M0 bits (CCP1CON<3:0>) be programmed as 1011 and that the A/D module is enabled (ADON bit is set). When the trigger occurs, the

GO/DONE bit will be set, starting the A/D conversion, and the Timer1 counter will be reset to zero. Timer1 is reset to automatically repeat the A/D acquisition period with minimal software overhead (moving the ADRES to the desired location). The appropriate analog input channel must be selected and the minimum acquisition done before the "Special Event Trigger" sets the GO/DONE bit (starts a conversion).

If the A/D module is not enabled (ADON is cleared), then the "Special Event Trigger" will be ignored by the A/D module, but will still reset the Timer1 counter.

TABLE 8-2: SUMMARY OF A/D REGISTERS

| Address | Name   | Bit 7    | Bit 6       | Bit 5 | Bit 4   | Bit 3     | Bit 2         | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on all other Resets |

|---------|--------|----------|-------------|-------|---------|-----------|---------------|--------|--------|-------------------------|---------------------------|

| 05h     | PORTA  | _        | _           | (1)   | RA4     | RA3       | RA2           | RA1    | RA0    | xx xxxx                 | xu uuuu                   |

| 0Bh,8Bh | INTCON | GIE      | PEIE        | TOIE  | INTE    | RBIE      | T0IF          | INTF   | RBIF   | 0000 000x               | 0000 000u                 |

| 0Ch     | PIR1   | _        | ADIF        | _     | _       | _         | CCP1IF        | TMR2IF | TMR1IF | -0000                   | -0000                     |

| 1Eh     | ADRES  | A/D Resu | ılt Registe | er    |         |           |               |        |        | xxxx xxxx               | uuuu uuuu                 |

| 1Fh     | ADCON0 | ADCS1    | ADCS0       | CHS2  | CHS1    | CHS0      | GO/DONE       | _      | ADON   | 0000 00-0               | 0000 00-0                 |

| 85h     | TRISA  | _        | _           | (1)   | PORTA I | Data Dire | ction Registe | r      |        | 1 1111                  | 1 1111                    |

| 8Ch     | PIE1   | _        | ADIE        | _     | _       | _         | CCP1IE        | TMR2IE | TMR1IE | -0000                   | -0 0000                   |

| 9Fh     | ADCON1 |          | _           | _     |         |           | PCFG2         | PCFG1  | PCFG0  | 000                     | 000                       |

Legend: x = unknown, u = unchanged, — = unimplemented read as '0'. Shaded cells are not used for A/D conversion.

Note 1: Reserved bits; Do Not Use.

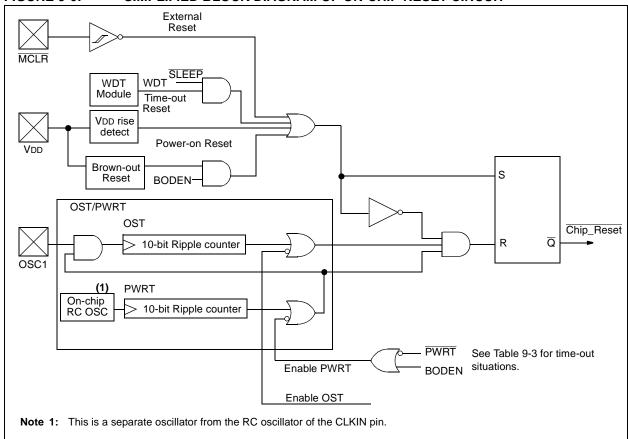

## FIGURE 9-6: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

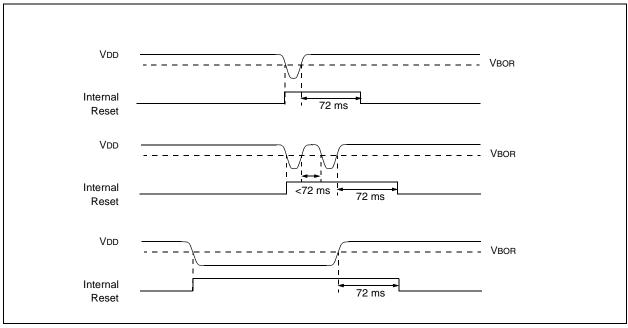

## FIGURE 9-7: BROWN-OUT SITUATIONS

## 9.10.1 INT INTERRUPT

External interrupt on RB0/INT pin is edge triggered, either rising if bit INTEDG (OPTION\_REG<6>) is set, or falling if the INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, flag bit INTF (INTCON<1>) is set. This interrupt can be disabled by clearing enable bit INTE (INTCON<4>). Flag bit INTF must be cleared in software in the Interrupt Service Routine before re-enabling this interrupt. The INT interrupt can wake-up the processor from Sleep, if bit INTE was set prior to going into Sleep. The status of global interrupt enable bit GIE decides whether or not the processor branches to the interrupt vector following wake-up. See Section 9.13 "Power-down Mode (Sleep)" for details on Sleep mode.

#### 9.10.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit T0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit T0IE (INTCON<5>). (Section 4.0 "Timer0 Module")

#### 9.10.3 PORTB INTCON CHANGE

An input change on PORTB<7:4> sets flag bit RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit RBIE (INTCON<4>). (Section 3.2 "PORTB and the TRISB Register")

## 9.11 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt, (i.e., W register and STATUS register). This will have to be implemented in software.

Example 9-1 stores and restores the W and STATUS registers. The register, W\_TEMP, must be defined in each bank and must be defined at the same offset from the bank base address (i.e., if W\_TEMP is defined at 0x20 in bank 0, it must also be defined at 0xA0 in bank 1).

#### The example:

- a) Stores the W register.

- b) Stores the STATUS register in bank 0.

- c) Stores the PCLATH register.

- Executes the Interrupt Service Routine code (User-generated).

- Restores the STATUS register (and bank select bit).

- Restores the W and PCLATH registers.

## EXAMPLE 9-1: SAVING STATUS, W, AND PCLATH REGISTERS IN RAM

```

MOVWF

W TEMP

;Copy W to TEMP register, could be bank one or zero

SWAPF

STATUS, W

;Swap status to be saved into W

; bank 0, regardless of current bank, Clears IRP, RP1, RP0

CLRF

STATUS

MOVWF

STATUS_TEMP

; Save status to bank zero STATUS_TEMP register

PCLATH, W

MOVF

;Only required if using pages 1, 2 and/or 3

MOVWF

PCLATH TEMP

;Save PCLATH into W

CLRF

PCLATH

; Page zero, regardless of current page

STATUS, IRP

;Return to Bank 0

BCF

MOVF

FSR, W

;Copy FSR to W

MOVWF

FSR TEMP

; Copy FSR from W to FSR_TEMP

:(ISR)

PCLATH TEMP, W

MOVE

Restore PCLATH

; Move W into PCLATH

MOVWF

PCLATH

SWAPF

STATUS_TEMP,W

;Swap STATUS_TEMP register into W

; (sets bank to original state)

MOVWF

STATUS

; Move W into STATUS register

; Swap W TEMP

SWAPF

W TEMP, F

W_TEMP,W

;Swap W_TEMP into W

SWAPF

```

## 9.16 In-Circuit Serial Programming™

PIC16CXXX microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

For complete details on serial programming, please refer to the In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) Guide, (DS30277).

## 12.0 ELECTRICAL CHARACTERISTICS

## Absolute Maximum Ratings (†)

| Ambient temperature under bias                                     | 55°C to +125°C       |

|--------------------------------------------------------------------|----------------------|

| Storage temperature                                                | 65°C to +150°C       |

| Voltage on any pin with respect to Vss (except VDD, MCLR, and RA4) | 0.3V to (VDD + 0.3V) |

| Voltage on VDD with respect to Vss                                 | 0.3V to +7.5V        |

| Voltage on MCLR with respect to Vss (Note 2)                       | 0V to +13.25V        |

| Voltage on RA4 with respect to Vss                                 | 0V to +8.5V          |

| Total power dissipation (Note 1) (PDIP and SOIC)                   | 1.0W                 |

| Total power dissipation (Note 1) (SSOP)                            | 0.65W                |

| Maximum current out of Vss pin                                     | 300 mA               |

| Maximum current into VDD pin                                       | 250 mA               |

| Input clamp current, Iik (VI < 0 or VI > VDD)                      |                      |

| Output clamp current, lok (Vo < 0 or Vo > VDD)                     | ±20 mA               |

| Maximum output current sunk by any I/O pin                         | 25 mA                |

| Maximum output current sourced by any I/O pin                      | 25 mA                |

| Maximum current sunk by PORTA and PORTB (combined)                 | 200 mA               |

| Maximum current sourced by PORTA and PORTB (combined)              | 200 mA               |

- **Note 1:** Power dissipation is calculated as follows: Pdis = VDD x {IDD  $\Sigma$  IOH} +  $\Sigma$  {(VDD-VOH) x IOH} +  $\Sigma$ (VOI x IOL)

- 2: Voltage spikes below Vss at the MCLR/VPP pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR/VPP pin rather than pulling this pin directly to Vss.

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

## 12.2 DC Characteristics: PIC16LC712/716-04 (Commercial, Industrial)

| DC CHAI               | DC CHARACTERISTICS |                                                                                                                                                  |                  | d Opera           | _                   | nditions<br>0°<br>-40°   |                                                                                                                               |

|-----------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------|---------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.          | Sym.               | Characteristic                                                                                                                                   | Min.             | Тур†              | Max.                | Units                    | Conditions                                                                                                                    |

| D001                  | VDD                | Supply Voltage                                                                                                                                   | 2.5<br>VBOR*     | _                 | 5.5<br>5.5          | V<br>V                   | BOR enabled (Note 7)                                                                                                          |

| D002*                 | VDR                | RAM Data Retention Voltage <sup>(1)</sup>                                                                                                        | _                | 1.5               | _                   | V                        |                                                                                                                               |

| D003                  | VPOR               | VDD Start Voltage to ensure internal Power-on Reset signal                                                                                       | _                | Vss               | _                   | V                        | See section on Power-on Reset for details                                                                                     |

| D004*<br>D004A*       | SVDD               | VDD Rise Rate to ensure internal<br>Power-on Reset signal                                                                                        | 0.05<br>TBD      | _                 | _                   | V/ms                     | PWRT enabled (PWRTE bit clear) PWRT disabled (PWRTE bit set) See section on Power-on Reset for details                        |

| D005                  | VBOR               | Brown-out Reset voltage trip point                                                                                                               | 3.65             | _                 | 4.35                | V                        | BODEN bit set                                                                                                                 |

| D010<br>D010A         | IDD                | Supply Current <sup>(2,5)</sup>                                                                                                                  | _                | 2.0<br>22.5       | 3.8<br>48           | mA<br>μA                 | XT, RC osc modes FOSC = 4 MHz, VDD = 3.0V (Note 4) LP osc mode FOSC = 32 kHz, VDD = 3.0V, WDT disabled                        |

| D020<br>D021<br>D021A | IPD                | Power-down Current <sup>(3,5)</sup>                                                                                                              | _<br>_<br>_      | 7.5<br>0.9<br>0.9 | 30<br>5<br>5        | μΑ<br>μΑ<br>μΑ           | VDD = 3.0V, WDT enabled, -40°C to +85°C<br>VDD = 3.0V, WDT disabled, 0°C to +70°C<br>VDD = 3.0V, WDT disabled, -40°C to +85°C |

| D022*<br>D022A*       | Δlwdt<br>Δlbor     | Module Differential Current <sup>(6)</sup> Watchdog Timer Brown-out Reset                                                                        | _                | 6.0<br>TBD        | 20<br>200           | μA<br>μA                 | WDTE bit set, VDD = 4.0V<br>BODEN bit set, VDD = 5.0V                                                                         |

| 1A                    | Fosc               | LP Oscillator Operating Frequency<br>RC Oscillator Operating Frequency<br>XT Oscillator Operating Frequency<br>HS Oscillator Operating Frequency | 0<br>0<br>0<br>0 | _<br>_<br>_<br>_  | 200<br>4<br>4<br>20 | KHz<br>MHz<br>MHz<br>MHz | All temperatures All temperatures All temperatures All temperatures                                                           |

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested

- Note1: This is the limit to which VDD can be lowered without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

- The test conditions for all IDD measurements in active operation mode are:

- OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD,

- MCLR = VDD; WDT enabled/disabled as specified.

- 3: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD and Vss.

- 4: For RC Osc mode, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kOhm.

- 5: Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- **6:** The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: This is the voltage where the device enters the Brown-out Reset. When BOR is enabled, the device will operate correctly to this trip point.

#### **AC (Timing) Characteristics** 12.4

#### 12.4.1 TIMING PARAMETER SYMBOLOGY

The timing parameter symbols have been created using one of the following formats:

- 1. TppS2ppS

| 2. TppS |                                      |     |                |

|---------|--------------------------------------|-----|----------------|

| T       |                                      |     |                |

| F       | Frequency                            | Т   | Time           |

| Lowerd  | ase letters (pp) and their meanings: |     |                |

| pp      |                                      |     |                |

| СС      | CCP1                                 | osc | OSC1           |

| ck      | CLKOUT                               | rd  | RD             |

| cs      | <del>CS</del>                        | rw  | RD or WR       |

| di      | SDI                                  | sc  | SCK            |

| do      | SDO                                  | SS  | SS             |

| dt      | Data in                              | tO  | TOCKI          |

| io      | I/O port                             | t1  | T1CKI          |

| mc      | MCLR                                 | wr  | WR             |

| Upperd  | ase letters and their meanings:      |     |                |

| S       |                                      |     |                |

| F       | Fall                                 | Р   | Period         |

| Н       | High                                 | R   | Rise           |

| I       | Invalid (High-impedance)             | V   | Valid          |

| L       | Low                                  | Z   | High-impedance |

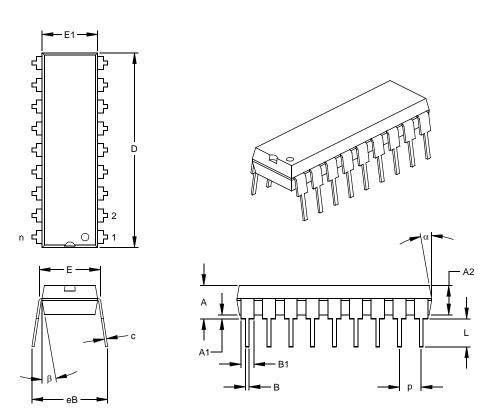

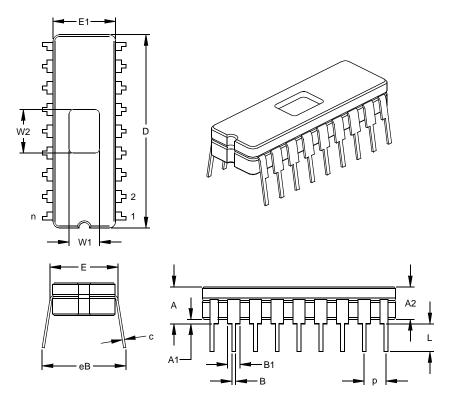

#### 13.2 **Package Details**

The following sections give the technical details of the packages.

## 18-Lead Plastic Dual In-line (P) – 300 mil (PDIP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units  | INCHES* |      |      | MILLIMETERS |       |       |

|----------------------------|--------|---------|------|------|-------------|-------|-------|

| Dimension                  | Limits | MIN     | NOM  | MAX  | MIN         | NOM   | MAX   |

| Number of Pins             | n      |         | 18   |      |             | 18    |       |

| Pitch                      | р      |         | .100 |      |             | 2.54  |       |

| Top to Seating Plane       | Α      | .140    | .155 | .170 | 3.56        | 3.94  | 4.32  |

| Molded Package Thickness   | A2     | .115    | .130 | .145 | 2.92        | 3.30  | 3.68  |

| Base to Seating Plane      | A1     | .015    |      |      | 0.38        |       |       |

| Shoulder to Shoulder Width | Е      | .300    | .313 | .325 | 7.62        | 7.94  | 8.26  |

| Molded Package Width       | E1     | .240    | .250 | .260 | 6.10        | 6.35  | 6.60  |

| Overall Length             | D      | .890    | .898 | .905 | 22.61       | 22.80 | 22.99 |

| Tip to Seating Plane       | L      | .125    | .130 | .135 | 3.18        | 3.30  | 3.43  |

| Lead Thickness             | С      | .008    | .012 | .015 | 0.20        | 0.29  | 0.38  |

| Upper Lead Width           | B1     | .045    | .058 | .070 | 1.14        | 1.46  | 1.78  |

| Lower Lead Width           | В      | .014    | .018 | .022 | 0.36        | 0.46  | 0.56  |

| Overall Row Spacing §      | eВ     | .310    | .370 | .430 | 7.87        | 9.40  | 10.92 |

| Mold Draft Angle Top       | α      | 5       | 10   | 15   | 5           | 10    | 15    |

| Mold Draft Angle Bottom    | β      | 5       | 10   | 15   | 5           | 10    | 15    |

<sup>\*</sup> Controlling Parameter

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010" (0.254mm) per side.

JEDEC Equivalent: MS-001

Drawing No. C04-007

<sup>§</sup> Significant Characteristic

## 18-Lead Ceramic Dual In-line with Window (JW) - 300 mil (CERDIP)

For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units    | INCHES* |      |      | MILLIMETERS |       |       |

|----------------------------|----------|---------|------|------|-------------|-------|-------|

| Dimensio                   | n Limits | MIN     | NOM  | MAX  | MIN         | NOM   | MAX   |

| Number of Pins             | n        |         | 18   |      |             | 18    |       |

| Pitch                      | р        |         | .100 |      |             | 2.54  |       |

| Top to Seating Plane       | Α        | .170    | .183 | .195 | 4.32        | 4.64  | 4.95  |

| Ceramic Package Height     | A2       | .155    | .160 | .165 | 3.94        | 4.06  | 4.19  |

| Standoff                   | A1       | .015    | .023 | .030 | 0.38        | 0.57  | 0.76  |

| Shoulder to Shoulder Width | Е        | .300    | .313 | .325 | 7.62        | 7.94  | 8.26  |

| Ceramic Pkg. Width         | E1       | .285    | .290 | .295 | 7.24        | 7.37  | 7.49  |

| Overall Length             | D        | .880    | .900 | .920 | 22.35       | 22.86 | 23.37 |

| Tip to Seating Plane       | L        | .125    | .138 | .150 | 3.18        | 3.49  | 3.81  |

| Lead Thickness             | С        | .008    | .010 | .012 | 0.20        | 0.25  | 0.30  |

| Upper Lead Width           | B1       | .050    | .055 | .060 | 1.27        | 1.40  | 1.52  |

| Lower Lead Width           | В        | .016    | .019 | .021 | 0.41        | 0.47  | 0.53  |

| Overall Row Spacing §      | eВ       | .345    | .385 | .425 | 8.76        | 9.78  | 10.80 |

| Window Width               | W1       | .130    | .140 | .150 | 3.30        | 3.56  | 3.81  |

| Window Length              | W2       | .190    | .200 | .210 | 4.83        | 5.08  | 5.33  |

<sup>\*</sup> Controlling Parameter § Significant Characteristic JEDEC Equivalent: MO-036 Drawing No. C04-010

**NOTES:**

| PORTC                                    | Brown-out Reset (BOR). See Brown-out Reset (BOR) |            |

|------------------------------------------|--------------------------------------------------|------------|

| TRISC Register 12                        | MCLR Reset. See MCLR                             |            |

| Postscaler, Timer2                       | Power-on Reset (POR). See Power-on Reset (POR)   |            |

| Select (TOUTPS3:TOUTPS0 Bits)            | Reset Conditions for All Registers 5             | 59         |

| Postscaler, WDT                          | Reset Conditions for PCON Register 5             | 58         |

| Assignment (PSA Bit) 14, 29              | Reset Conditions for Program Counter5            |            |

| Block Diagram30                          | Reset Conditions for STATUS Register 5           |            |

| Rate Select (PS2:PS0 Bits) 14, 29        | Timing Diagram8                                  |            |

| Switching Between Timer0 and WDT 30      | WDT Reset. See Watchdog Timer (WDT)              |            |

| Power-down Mode. See Sleep               | Revision History9                                | <b>)</b> 5 |

| Power-on Reset (POR) 51, 54, 55, 58, 59  | ·                                                |            |

| Oscillator Start-up Timer (OST)          | S                                                |            |

| POR Status (POR Bit)                     | Sleep 6                                          | 34         |

| Power Control (PCON) Register 58         | Sleep                                            |            |

| Power-down (PD Bit)                      | Software Simulator (MPLAB SIM)                   |            |

| Power-on Reset Circuit, External         | Special Event Trigger. See Compare               | •          |

| ·                                        | Special Features of the CPU                      | <b>5</b> 1 |

| Power-up Timer (PWRT)                    | Special Function Registers 1                     |            |

| PWRT Enable (PWRTE Bit)                  |                                                  |            |

| Time-out (TO Bit)                        | Speed, Operating                                 |            |

| Time-out Sequence 57                     | Stack                                            |            |

| Time-out Sequence on Power-up 60         | STATUS Register 11, 13, 6                        |            |

| Timing Diagram 83                        | C Bit                                            |            |

| Prescaler, Capture 40                    | DC Bit 1                                         |            |

| Prescaler, Timer0                        | <u>IRP</u> Bit 1                                 | 13         |

| Assignment (PSA Bit) 14, 29              | PD Bit 13, 5                                     |            |

| Block Diagram 30                         | RP1:RP0 Bits 1                                   | 13         |

| Rate Select (PS2:PS0 Bits) 14, 29        | TO Bit 13, 5                                     | 54         |

| Switching Between Timer0 and WDT 30      | Z Bit 1                                          | 13         |

| Prescaler, Timer1                        | <u> </u>                                         |            |

| Select (T1CKPS1:T1CKPS0 Bits)            | Т                                                |            |

| Prescaler, Timer2                        | T1CON Register 11, 3                             | 31         |

| Select (T2CKPS1:T2CKPS0 Bits)            | T1CKPS1:T1CKPS0 Bits                             |            |

|                                          | T1OSCEN Bit                                      |            |

| Product Identification System            | T1SYNC Bit                                       |            |

| Program Counter                          | TMR1CS Bit                                       |            |

| PCL Register                             | TMR1ON Bit                                       |            |

| PCLATH Register 11, 19, 62               |                                                  |            |

| Reset Conditions 58                      | T2CON Register                                   |            |

| Program Memory 9                         | T2CKPS1:T2CKPS0 Bits                             |            |

| Interrupt Vector9                        | TMR2ON Bit                                       |            |

| Paging 9, 19                             | TOUTPS3:TOUTPS0 Bits                             |            |

| Program Memory Map 9                     | Timer0 2                                         |            |

| Reset Vector 9                           | Block Diagram2                                   |            |

| Program Verification 65                  | Clock Source Edge Select (T0SE Bit) 14, 2        | 29         |

| Programming, Device Instructions 67      | Clock Source Select (T0CS Bit) 14, 2             | 29         |

| PWM (CCP Module) 42                      | Overflow Enable (T0IE Bit) 1                     | 5          |

| Block Diagram 42                         | Overflow Flag (T0IF Bit) 15, 6                   | 32         |

| CCPR1H:CCPR1L Registers                  | Overflow Interrupt                               | 32         |

| Duty Cycle                               | Prescaler. See Prescaler, Timer0                 |            |

| Example Frequencies/Resolutions          | Timing Diagram 8                                 | 34         |

|                                          | TMR0 Register 1                                  |            |

| Output Diagram                           | Timer1                                           |            |

| Period                                   | Block Diagram                                    |            |

| Set-Up for PWM Operation                 | Capacitor Selection                              |            |

| TMR2 to PR2 Match                        |                                                  |            |

| TMR2 to PR2 Match Enable (TMR2IE Bit) 16 | Clock Source Select (TMR1CS Bit)                 |            |

| TMR2 to PR2 Match Flag (TMR2IF Bit)17    | External Clock Input Sync (T1SYNC Bit)           |            |

| 0                                        | Module On/Off (TMR1ON Bit)                       |            |

| Q                                        | Oscillator                                       |            |

| Q-Clock                                  | Oscillator Enable (T1OSCEN Bit)                  |            |

| R                                        | Overflow Enable (TMR1IE Bit) 1                   |            |

|                                          | Overflow Flag (TMR1IF Bit)1                      |            |

| RAM. See Data Memory                     | Overflow Interrupt 31, 3                         | 34         |

| Reader Response                          | Prescaler. See Prescaler, Timer1                 |            |

| Register File                            | Special Event Trigger (CCP)                      | ļ1         |

| Register File Map 10                     | T1CON Register 11, 3                             |            |

| Reset51, 54                              | Timing Diagram 8                                 |            |

| Block Diagram56                          | TMR1H Register                                   |            |

| 5                                        |                                                  |            |

| TMR1L Register                        | 11, 31     |

|---------------------------------------|------------|

| Timer2                                |            |

| Block Diagram                         | 36         |

| Postscaler. See Postscaler, Timer2    |            |

| PR2 Register                          | 12, 36, 42 |

| Prescaler. See Prescaler, Timer2      |            |

| T2CON Register                        | 11, 36     |

| TMR2 Register                         | 11, 36     |

| TMR2 to PR2 Match Enable (TMR2IE Bit) | 16         |

| TMR2 to PR2 Match Flag (TMR2IF Bit)   | 17         |

| TMR2 to PR2 Match Interrupt           | 36, 37, 42 |

| Timing Diagrams                       |            |

| Time-out Sequence on Power-up         | 60         |

| Wake-up from Sleep via Interrupt      | 65         |

| Timing Diagrams and Specifications    | 81         |

| A/D Conversion                        | 87         |

| Brown-out Reset (BOR)                 | 83         |

| Capture/Compare/PWM (CCP)             | 85         |

| CLKOUT and I/O                        | 82         |

| External Clock                        | 81         |

| Oscillator Start-up Timer (OST)       | 83         |

| Power-up Timer (PWRT)                 | 83         |

| Reset                                 | 83         |

| Timer0 and Timer1                     |            |

| Watchdog Timer (WDT)                  | 83         |

## W Wake-up from Sleep ...... 51 Wake-up from Sleep ...... 64 Interrupts ...... 58, 59 MCLR Reset ...... 59 Timing Diagram ...... 65 WDT Reset ......59 Watchdog Timer (WDT)...... 51, 63 Block Diagram ...... 63 Enable (WDTE Bit) ...... 52, 63 Postscaler, See Postscaler, WDT Timing Diagram ...... 83 WDT Reset, Normal Operation ...... 54, 58, 59 WDT Reset, Sleep...... 54, 58, 59 WWW Address ...... 101