Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 13                                                                        |

| Program Memory Size        | 1.75KB (1K x 14)                                                          |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                 |

| Data Converters            | A/D 4x8b                                                                  |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 18-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c712-20-so |

#### **Table of Contents**

| 1.0   | Device Overview                                 | 5    |

|-------|-------------------------------------------------|------|

| 2.0   | Memory Organization                             | 9    |

| 3.0   | I/O Ports                                       | . 21 |

| 4.0   | I/O Ports Timer0 Module                         | . 29 |

| 5.0   | Timer1 Module                                   | . 31 |

| 6.0   | Timer2 Module                                   | . 36 |

| 7.0   | Capture/Compare/PWM (CCP) Module(s)             | . 39 |

| 8.0   | Analog-to-Digital Converter (A/D) Module        |      |

| 9.0   | Special Features of the CPU                     |      |

| 10.0  | Instruction Set Summary                         | . 67 |

| 11.0  | Development Support  Electrical Characteristics | . 69 |

| 12.0  | Electrical Characteristics                      | . 73 |

| 13.0  | Packaging Information                           | . 89 |

| Revis | ion History                                     | . 95 |

| Conv  | ersion Considerations                           | . 95 |

|       | tion from Base-line to Mid-Range Devices        |      |

| Index |                                                 | . 97 |

| On-Li | ne Support                                      | 101  |

| Read  | er Response                                     | 102  |

| PIC1  | 6C712/716 Product Identification System         | 103  |

|       |                                                 |      |

#### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### **Errata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

**NOTES:**

TABLE 1-1: PIC16C712/716 PINOUT DESCRIPTION (CONTINUED)

| Pin                       | PIC16C    | 712/716 | Pin        | Buffer    |                                                                                                               |

|---------------------------|-----------|---------|------------|-----------|---------------------------------------------------------------------------------------------------------------|

| Name                      | DIP, SOIC | SSOP    | Туре       | Туре      | Description                                                                                                   |

|                           |           |         |            |           | PORTB is a bidirectional I/O port. PORTB can be software programmed for internal weak pull-ups on all inputs. |

| RB0/INT<br>RB0<br>INT     | 6         | 7       | I/O<br>I   | TTL<br>ST | Digital I/O<br>External Interrupt                                                                             |

| RB1/T1OSO/T1CKI<br>RB1    | 7         | 8       |            |           |                                                                                                               |

| T1OSO                     |           |         | I/O<br>O   | TTL<br>—  | Digital I/O Timer1 oscillator output. Connects to                                                             |

| T1CKI                     |           |         | ı          | ST        | crystal in oscillator mode.<br>Timer1 external clock input.                                                   |

| RB2/T1OSI<br>RB2<br>T1OSI | 8         | 9       | I/O<br>I   | TTL<br>—  | Digital I/O Timer1 oscillator input. Connects to crystal in oscillator mode.                                  |

| RB3/CCP1<br>RB3<br>CCP1   | 9         | 10      | I/O<br>I/O | TTL<br>ST | Digital I/O Capture1 input, Compare1 output, PWM1 output.                                                     |

| RB4                       | 10        | 12      | I/O        | TTL       | Digital I/O<br>Interrupt on change pin.                                                                       |

| RB5                       | 11        | 12      | I/O        | TTL       | Digital I/O<br>Interrupt on change pin.                                                                       |

| RB6                       | 12        | 13      | I/O        | TTL       | Digital I/O<br>Interrupt on change pin.                                                                       |

|                           |           |         | I          | ST        | ICSP programming clock.                                                                                       |

| RB7                       | 13        | 14      | I/O<br>I/O | TTL<br>ST | Digital I/O Interrupt on change pin. ICSP programming data.                                                   |

| Vss                       | 5         | 5, 6    | P          | _         | Ground reference for logic and I/O pins.                                                                      |

| VDD                       | 14        | 15, 16  | P          | _         | Positive supply for logic and I/O pins.                                                                       |

**Legend:** TTL = TTL-compatible input CMOS = CMOS compatible input or output

ST = Schmitt Trigger input with CMOS levels

OD = Open drain output

SM = SMBus compatible input. An external resistor is required if this pin is used as an output

NPU = N-channel pull-up

No-P diode = No P-diode to VDD AN = Analog input or output

I = input O = output P = Power L = LCD Driver

#### 2.2.2.5 PIR1 Register

This register contains the individual flag bits for the peripheral interrupts.

Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### FIGURE 2-8: PIR1 REGISTER (ADDRESS 0Ch)

| FIGURE 2 | :-o:                                                                                                                                                          | PIRTRI                                                                 | EGISTER                                              | (ADDRI                   | 233 UCN)     |             |       |                   |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|------------------------------------------------------|--------------------------|--------------|-------------|-------|-------------------|--|--|

| U-0      | R/W-0                                                                                                                                                         | U-0                                                                    | U-0                                                  | R/W-0                    | R/W-0        | R/W-0       | R/W-0 |                   |  |  |

| —<br>—   |                                                                                                                                                               |                                                                        | U-0                                                  | K/W-0                    |              |             |       | P. – Peadable bit |  |  |

| bit7     | ADIF — — CCP1IF TMR2IF TMR1IF  bit0  R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR Reset  Unimplemented: Read as '0' |                                                                        |                                                      |                          |              |             |       |                   |  |  |

| bit 6:   |                                                                                                                                                               | D convers                                                              | ion comp                                             | •                        | t be cleared | d in softwa | re)   |                   |  |  |

| bit 5-3: | Unimpler                                                                                                                                                      | nented: R                                                              | Read as '0                                           | ,                        |              |             |       |                   |  |  |

| bit 2:   | 0 = No TN<br><u>Compare</u><br>1 = A TMI<br>0 = No TN<br><u>PWM Mod</u>                                                                                       | Mode:<br>R1 registe<br>MR1 regist<br>Mode:<br>R1 registe<br>MR1 regist | er capture<br>ter capture<br>er compare<br>ter compa | occurred (<br>e occurred | curred (mu   |             | ,     | vare)             |  |  |

Note:

0 = No TMR2 to PR2 match occurred

bit 1:

bit 0: TMR1IF: TMR1 Overflow Interrupt Flag bit

TMR2IF: TMR2 to PR2 Match Interrupt Flag bit

1 = TMR2 to PR2 match occurred (must be cleared in software)

- 1 = TMR1 register overflowed (must be cleared in software)

- 0 = TMR1 register did not overflow

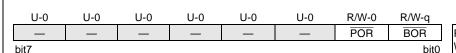

#### 2.2.2.6 PCON Register

The Power Control (PCON) register contains a flag bit to allow differentiation between a Power-on Reset (POR) to an external MCLR Reset or WDT Reset. These devices contain an additional bit to differentiate a Brown-out Reset condition from a Power-on Reset condition.

Note: If the BODEN Configuration bit is set, BOR is '1' on Power-on Reset. If the BODEN

Configuration bit is clear, BOR is unknown

on Power-on Reset.

The BOR Status bit is a "don't care" and is not necessarily predictable if the brown-out circuit is disabled (the BODEN Configuration bit is clear). BOR must then be set by the user and checked on subsequent resets to see if it is clear, indicating a brown-out has occurred.

#### FIGURE 2-9: PCON REGISTER (ADDRESS 8Eh)

R = Readable bit

N = Writable bit

J = Unimplemented bit, read as '0'

-n = Value at POR Reset

bit 7-2: Unimplemented: Read as '0'

bit 1: **POR**: Power-on Reset Status bit

1 = No Power-on Reset occurred

0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

bit 0: BOR: Brown-out Reset Status bit

1 = No Brown-out Reset occurred

0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs)

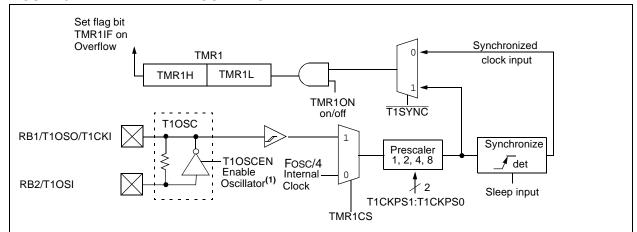

#### FIGURE 5-2: TIMER1 BLOCK DIAGRAM

Note 1: When the T1OSCEN bit is cleared, the inverter and feedback resistor are turned off. This eliminates power drain.

# 5.2 Timer1 Module and PORTB Operation

When Timer1 is configured as timer running from the main oscillator, PORTB<2:1> operate as normal I/O lines. When Timer1 is configured to function as a counter however, the clock source selection may affect the operation of PORTB<2:1>. Multiplexing details of the Timer1 clock selection on PORTB are shown in Figure 3-4 and Figure 3-5.

The clock source for Timer1 in the Counter mode can be from one of the following:

- External circuit connected to the RB1/T1OSO/ T1CKI pin

- 2. Firmware controlled DATACCP<0> bit, DT1CKI

- 3. Timer1 oscillator

Table 5-1 shows the details of Timer1 mode selections, control bit settings, TMR1 and PORTB operations.

TABLE 5-1: TMR1 MODULE AND PORTB OPERATION

| TMR1<br>Module<br>Mode | Clock Source      | Control Bits                   | TMR1 Module Operation                                                                                                                                                                                                                                         | PORTB<2:1> Operation                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|------------------------|-------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Off                    | N/A               | T1CON =xx 0x00                 | Off                                                                                                                                                                                                                                                           | PORTB<2:1> function as normal I/O                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| Timer                  | Fosc/4            | T1CON =xx 0x01                 | TMR1 module uses the main oscillator as clock source. TMR1ON can turn on or turn off Timer1.                                                                                                                                                                  | PORTB<2:1> function as normal I/O                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| Counter                | External circuit  | T1CON =xx 0x11<br>TR1SCCP =x-1 | TMR1 module uses the external signal on the RB1/T1OSO/T1CKI pin as a clock source. TMR1ON can turn on or turn off Timer1. DT1CK can read the signal on the RB1/T1OSO/T1CKI pin.                                                                               | PORTB<2> functions as normal I/O. PORTB<1> always reads '0' when configured as input. If PORTB<1> is configured as output, reading PORTB<1> will read the data latch. Writing to PORTB<1> will always store the                                                                                                                                                                                                                                              |  |

|                        | Firmware          | T1CON =xx 0x11<br>TR1SCCP =x-0 | DATACCP<0> bit drives RB1/<br>T1OSO/T1CKI and produces<br>the TMR1 clock source.<br>TMR1ON can turn on or turn off<br>Timer1. The DATACCP<0> bit,<br>DT1CK, can read and write to<br>the RB1/T1OSO/T1CKI pin.                                                 | result in the data latch, but not to<br>the RB1/T1OSO/T1CKI pin. If<br>the TMR1CS bit is cleared<br>(TMR1 reverts to the timer<br>mode), then pin PORTB<1> will<br>be driven with the value in the<br>data latch.                                                                                                                                                                                                                                            |  |

|                        | Timer1 oscillator | T1CON =xx 1x11                 | RB1/T1OSO/T1CKI and RB2/T1OSI are configured as a 2 pin crystal oscillator. RB1/T1OSI/T1CKI is the clock input for TMR1. TMR1ON can turn on or turn off Timer1. DATACCP<1>bit, DT1CK, always reads '0' as input and can not write to the RB1/T1OSO/T1CK1 pin. | PORTB<2:1> always read '0' when configured as inputs. If PORTB<2:1> are configured as outputs, reading PORTB<2:1> will read the data latches. Writing to PORTB<2:1> will always store the result in the data latches, but not to the RB2/T1OSI and RB1/T1OSO/T1CKI pins. If the TMR1CS and T1OSCEN bits are cleared (TMR1 reverts to the timer mode and TMR1 oscillator is disabled), then pin PORTB<2:1> will be driven with the value in the data latches. |  |

#### 8.4 A/D Conversions

Note: The GO/DONE bit should NOT be set in the same instruction that turns on the A/D.

#### 8.5 Use of the CCP Trigger

An A/D conversion can be started by the "Special Event Trigger" of the CCP1 module. This requires that the CCP1M3:CCP1M0 bits (CCP1CON<3:0>) be programmed as 1011 and that the A/D module is enabled (ADON bit is set). When the trigger occurs, the

GO/DONE bit will be set, starting the A/D conversion, and the Timer1 counter will be reset to zero. Timer1 is reset to automatically repeat the A/D acquisition period with minimal software overhead (moving the ADRES to the desired location). The appropriate analog input channel must be selected and the minimum acquisition done before the "Special Event Trigger" sets the GO/DONE bit (starts a conversion).

If the A/D module is not enabled (ADON is cleared), then the "Special Event Trigger" will be ignored by the A/D module, but will still reset the Timer1 counter.

TABLE 8-2: SUMMARY OF A/D REGISTERS

| Address | Name   | Bit 7    | Bit 6       | Bit 5 | Bit 4   | Bit 3     | Bit 2         | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on all other Resets |

|---------|--------|----------|-------------|-------|---------|-----------|---------------|--------|--------|-------------------------|---------------------------|

| 05h     | PORTA  | _        | _           | (1)   | RA4     | RA3       | RA2           | RA1    | RA0    | xx xxxx                 | xu uuuu                   |

| 0Bh,8Bh | INTCON | GIE      | PEIE        | TOIE  | INTE    | RBIE      | T0IF          | INTF   | RBIF   | 0000 000x               | 0000 000u                 |

| 0Ch     | PIR1   | _        | ADIF        | _     | _       | _         | CCP1IF        | TMR2IF | TMR1IF | -0000                   | -0000                     |

| 1Eh     | ADRES  | A/D Resu | ılt Registe | er    |         |           |               |        |        | xxxx xxxx               | uuuu uuuu                 |

| 1Fh     | ADCON0 | ADCS1    | ADCS0       | CHS2  | CHS1    | CHS0      | GO/DONE       | _      | ADON   | 0000 00-0               | 0000 00-0                 |

| 85h     | TRISA  | _        | _           | (1)   | PORTA I | Data Dire | ction Registe | 1 1111 | 1 1111 |                         |                           |

| 8Ch     | PIE1   | _        | ADIE        | _     | _       | _         | CCP1IE        | TMR2IE | TMR1IE | -0000                   | -0 0000                   |

| 9Fh     | ADCON1 |          | _           | _     |         |           | PCFG2         | PCFG1  | PCFG0  | 000                     | 000                       |

Legend: x = unknown, u = unchanged, — = unimplemented read as '0'. Shaded cells are not used for A/D conversion.

Note 1: Reserved bits; Do Not Use.

#### FIGURE 9-1: CONFIGURATION WORD

CP1 CP0 CP1 CP0 CP1 CP0 BODEN CP1 CP0 PWRTE WDTE FOSC1 FOSC0 Register: CONFIG Address2007h bit13 bit0 bit 13-8, 5-4: CP1:CP0: Code Protection bits (2) Code Protection for 2K Program memory (PIC16C716) 11 = Programming code protection off 10 = 0400h-07FFh code protected 01 = 0200h-07FFh code protected 00 = 0000h-07FFh code protected bit 13-8, 5-4: Code Protection for 1K Program memory bits (PIC16C712) 11 = Programming code protection off 10 = Programming code protection off 01 = 0200h-03FFh code-protected 00 = 0000h-03FFh code-protected bit 7: Unimplemented: Read as '1' bit 6: **BODEN**: Brown-out Reset Enable bit (1) 1 = BOR enabled 0 = BOR disabled **PWRTE**: Power-up Timer Enable bit (1) bit 3: 1 = PWRT disabled 0 = PWRT enabled bit 2: WDTE: Watchdog Timer Enable bit 1 = WDT enabled 0 = WDT disabled FOSC1:FOSC0: Oscillator Selection bits bit 1-0: 11 = RC oscillator 10 = HS oscillator 01 = XT oscillator 00 = LP oscillator Enabling Brown-out Reset automatically enables Power-up Timer (PWRT) regardless of the value of bit PWRTE. Note 1: Ensure the Power-up Timer is enabled anytime Brown-out Reset is enabled. 2: All of the CP1:CP0 pairs have to be given the same value to enable the code protection scheme listed.

### 9.9 Power Control/Status Register (PCON)

The Power Control/Status Register, PCON has two bits.

Bit 0 is Brown-out Reset Status bit, BOR. If the BODEN Configuration bit is set, BOR is '1' on Power-on Reset. If the BODEN Configuration bit is clear, BOR is unknown on Power-on Reset.

The BOR Status bit is a "don't care" and is not necessarily predictable if the brown-out circuit is disabled (the BODEN Configuration bit is clear). BOR must then be set by the user and checked on subsequent Resets to see if it is clear, indicating a brown-out has occurred.

Bit 1 is POR (Power-on Reset Status bit). It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

TABLE 9-3: TIME-OUT IN VARIOUS SITUATIONS

| Oscillator Configuration | Power            | -up       | Brown-out        | Wake-up from |  |

|--------------------------|------------------|-----------|------------------|--------------|--|

| Oscillator Configuration | PWRTE = 0        | PWRTE = 1 | Brown-out        | Sleep        |  |

| XT, HS, LP               | 72 ms + 1024Tosc | 1024Tosc  | 72 ms + 1024Tosc | 1024Tosc     |  |

| RC                       | 72 ms            |           | 72 ms            | _            |  |

TABLE 9-4: STATUS BITS AND THEIR SIGNIFICANCE

| POR | BOR | TO | PD |                                                         |

|-----|-----|----|----|---------------------------------------------------------|

| 0   | х   | 1  | 1  | Power-on Reset                                          |

| 0   | х   | 0  | х  | Illegal, TO is set on POR                               |

| 0   | х   | х  | 0  | Illegal, PD is set on POR                               |

| 1   | 0   | 1  | 1  | Brown-out Reset                                         |

| 1   | 1   | 0  | 1  | WDT Reset                                               |

| 1   | 1   | 0  | 0  | WDT Wake-up                                             |

| 1   | 1   | u  | u  | MCLR Reset during normal operation                      |

| 1   | 1   | 1  | 0  | MCLR Reset during Sleep or interrupt wake-up from Sleep |

TABLE 9-5: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uu               |

| MCLR Reset during Sleep            | 000h                  | 0001 0uuu          | uu               |

| WDT Reset                          | 000h                  | 0000 1uuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | uu               |

| Brown-out Reset                    | 000h                  | 0001 1uuu          | u0               |

| Interrupt wake-up from Sleep       | PC + 1 <sup>(1)</sup> | uuu1 0uuu          | uu               |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit read as '0'.

Note 1: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

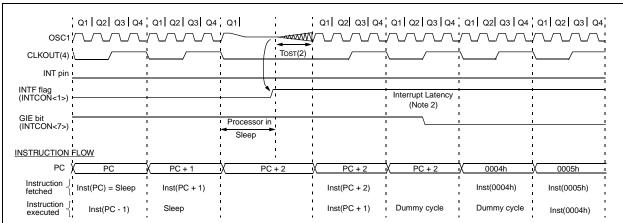

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

#### 9.13.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

If the interrupt occurs before the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT

- postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt occurs during or after the execution of a SLEEP instruction, the device will immediately wake-up from Sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the  $\overline{PD}$  bit. If the  $\overline{PD}$  bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

- Note 1: XT, HS or LP Oscillator mode assumed.

- 2: Tost = 1024Tosc (drawing not to scale) This delay will not be there for RC Osc mode.

- 3: GIE = 1 assumed. In this case after wake-up, the processor jumps to the interrupt routine. If GIE = 0, execution will continue in-line.

- 4: CLKOUT is not available in these osc modes, but shown here for timing reference.

### 9.14 Program Verification/Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

**Note:** Microchip does not recommend code protecting windowed devices.

#### 9.15 ID Locations

Four memory locations (2000h-2003h) are designated as ID locations where the user can store checksum or other code-identification numbers. These locations are not accessible during normal execution, but are readable and writable during Program/Verify. It is recommended that only the 4 Least Significant bits of the ID location are used.

For ROM devices, these values are submitted along with the ROM code.

#### 9.16 In-Circuit Serial Programming™

PIC16CXXX microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

For complete details on serial programming, please refer to the In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) Guide, (DS30277).

#### 12.0 ELECTRICAL CHARACTERISTICS

#### Absolute Maximum Ratings (†)

| Ambient temperature under bias                                     | 55°C to +125°C       |

|--------------------------------------------------------------------|----------------------|

| Storage temperature                                                | 65°C to +150°C       |

| Voltage on any pin with respect to Vss (except VDD, MCLR, and RA4) | 0.3V to (VDD + 0.3V) |

| Voltage on VDD with respect to Vss                                 | 0.3V to +7.5V        |

| Voltage on MCLR with respect to Vss (Note 2)                       | 0V to +13.25V        |

| Voltage on RA4 with respect to Vss                                 | 0V to +8.5V          |

| Total power dissipation (Note 1) (PDIP and SOIC)                   | 1.0W                 |

| Total power dissipation (Note 1) (SSOP)                            | 0.65W                |

| Maximum current out of Vss pin                                     | 300 mA               |

| Maximum current into VDD pin                                       | 250 mA               |

| Input clamp current, Iik (VI < 0 or VI > VDD)                      |                      |

| Output clamp current, lok (Vo < 0 or Vo > VDD)                     | ±20 mA               |

| Maximum output current sunk by any I/O pin                         | 25 mA                |

| Maximum output current sourced by any I/O pin                      | 25 mA                |

| Maximum current sunk by PORTA and PORTB (combined)                 | 200 mA               |

| Maximum current sourced by PORTA and PORTB (combined)              | 200 mA               |

- **Note 1:** Power dissipation is calculated as follows: Pdis = VDD x {IDD  $\Sigma$  IOH} +  $\Sigma$  {(VDD-VOH) x IOH} +  $\Sigma$ (VOI x IOL)

- 2: Voltage spikes below Vss at the MCLR/VPP pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR/VPP pin rather than pulling this pin directly to Vss.

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### 12.2 DC Characteristics: PIC16LC712/716-04 (Commercial, Industrial)

| DC CHAI               | Standard Operating Conditions (unless otherwise stated)  Operating temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for comme $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |                                                                                                                                                  |                  |                   |                     |                          |                                                                                                                               |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------|---------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.          | Sym.                                                                                                                                                                                | Characteristic                                                                                                                                   | Min.             | Тур†              | Max.                | Units                    | Conditions                                                                                                                    |

| D001                  | VDD                                                                                                                                                                                 | Supply Voltage                                                                                                                                   | 2.5<br>VBOR*     | _                 | 5.5<br>5.5          | V<br>V                   | BOR enabled (Note 7)                                                                                                          |

| D002*                 | VDR                                                                                                                                                                                 | RAM Data Retention Voltage <sup>(1)</sup>                                                                                                        | _                | 1.5               | _                   | V                        |                                                                                                                               |

| D003                  | VPOR                                                                                                                                                                                | VDD Start Voltage to ensure internal Power-on Reset signal                                                                                       | _                | Vss               | _                   | V                        | See section on Power-on Reset for details                                                                                     |

| D004*<br>D004A*       | SVDD                                                                                                                                                                                | VDD Rise Rate to ensure internal<br>Power-on Reset signal                                                                                        | 0.05<br>TBD      | _                 | _                   | V/ms                     | PWRT enabled (PWRTE bit clear) PWRT disabled (PWRTE bit set) See section on Power-on Reset for details                        |

| D005                  | VBOR                                                                                                                                                                                | Brown-out Reset voltage trip point                                                                                                               | 3.65             | _                 | 4.35                | V                        | BODEN bit set                                                                                                                 |

| D010<br>D010A         | IDD                                                                                                                                                                                 | Supply Current <sup>(2,5)</sup>                                                                                                                  | _                | 2.0<br>22.5       | 3.8<br>48           | mA<br>μA                 | XT, RC osc modes FOSC = 4 MHz, VDD = 3.0V (Note 4) LP osc mode FOSC = 32 kHz, VDD = 3.0V, WDT disabled                        |

| D020<br>D021<br>D021A | IPD                                                                                                                                                                                 | Power-down Current <sup>(3,5)</sup>                                                                                                              | _<br>_<br>_      | 7.5<br>0.9<br>0.9 | 30<br>5<br>5        | μΑ<br>μΑ<br>μΑ           | VDD = 3.0V, WDT enabled, -40°C to +85°C<br>VDD = 3.0V, WDT disabled, 0°C to +70°C<br>VDD = 3.0V, WDT disabled, -40°C to +85°C |

| D022*<br>D022A*       | Δlwdt<br>Δlbor                                                                                                                                                                      | Module Differential Current <sup>(6)</sup> Watchdog Timer Brown-out Reset                                                                        | _                | 6.0<br>TBD        | 20<br>200           | μA<br>μA                 | WDTE bit set, VDD = 4.0V<br>BODEN bit set, VDD = 5.0V                                                                         |

| 1A                    | Fosc                                                                                                                                                                                | LP Oscillator Operating Frequency<br>RC Oscillator Operating Frequency<br>XT Oscillator Operating Frequency<br>HS Oscillator Operating Frequency | 0<br>0<br>0<br>0 | _<br>_<br>_<br>_  | 200<br>4<br>4<br>20 | KHz<br>MHz<br>MHz<br>MHz | All temperatures All temperatures All temperatures All temperatures                                                           |

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested

- Note1: This is the limit to which VDD can be lowered without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

- The test conditions for all IDD measurements in active operation mode are:

- OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD,

- MCLR = VDD; WDT enabled/disabled as specified.

- 3: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD and Vss.

- 4: For RC Osc mode, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kOhm.

- 5: Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- **6:** The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: This is the voltage where the device enters the Brown-out Reset. When BOR is enabled, the device will operate correctly to this trip point.

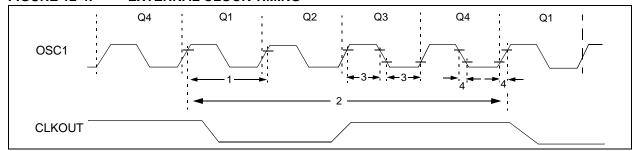

#### 12.4.3 TIMING DIAGRAMS AND SPECIFICATIONS

FIGURE 12-4: EXTERNAL CLOCK TIMING

TABLE 12-2: EXTERNAL CLOCK TIMING REQUIREMENTS

| Param<br>No. | Sym.  | Characteristic                   | Min. | Тур† | Max.   | Units | Conditions          |

|--------------|-------|----------------------------------|------|------|--------|-------|---------------------|

| 1A           | Fosc  | External CLKIN Frequency         | DC   |      | 4      | MHz   | RC and XT osc modes |

| IA           | FUSC  | (Note 1)                         | DC   | _    | ·-     | MHz   | HS osc mode (-04)   |

|              |       | (1010 1)                         | _    | _    | 4      |       | ` '                 |

|              |       |                                  | DC   | _    | 20     | MHz   | HS osc mode (-20)   |

|              |       | 0                                | DC   |      | 200    | kHz   | LP osc mode         |

|              |       | Oscillator Frequency (Note 1)    | DC   | _    | 4      | MHz   | RC osc mode         |

|              |       | (Note 1)                         | 0.1  | _    | 4      | MHz   | XT osc mode         |

|              |       |                                  | 4    | _    | 20     | MHz   | HS osc mode         |

|              |       |                                  | 5    | _    | 200    | kHz   | LP osc mode         |

| 1            | Tosc  | External CLKIN Period            | 250  | _    | _      | ns    | RC and XT osc modes |

|              |       | (Note 1)                         | 250  | _    | _      | ns    | HS osc mode (-04)   |

|              |       |                                  | 50   | _    | _      | ns    | HS osc mode (-20)   |

|              |       |                                  | 5    | _    | _      | μS    | LP osc mode         |

|              |       | Oscillator Period                | 250  | _    | _      | ns    | RC osc mode         |

|              |       | (Note 1)                         | 250  | _    | 10,000 | ns    | XT osc mode         |

|              |       |                                  | 250  | _    | 250    | ns    | HS osc mode (-04)   |

|              |       |                                  | 50   | _    | 250    | ns    | HS osc mode (-20)   |

|              |       |                                  | 5    | _    | _      | μS    | LP osc mode         |

| 2            | Tcy   | Instruction Cycle Time (Note 1)  | 200  | _    | DC     | ns    | Tcy = 4/Fosc        |

| 3*           | TosL, | External Clock in (OSC1) High or | 100  | _    | _      | ns    | XT oscillator       |

|              | TosH  | Low Time                         | 2.5  | _    | _      | μS    | LP oscillator       |

|              |       |                                  | 15   | _    | _      | ns    | HS oscillator       |

| 4*           | TosR, | External Clock in (OSC1) Rise or | _    | _    | 25     | ns    | XT oscillator       |

|              | TosF  | Fall Time                        | _    | _    | 50     | ns    | LP oscillator       |

|              |       |                                  | _    | _    | 15     | ns    | HS oscillator       |

<sup>\*</sup> These parameters are characterized but not tested.

**Note1:** Instruction cycle period (TcY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin.

When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

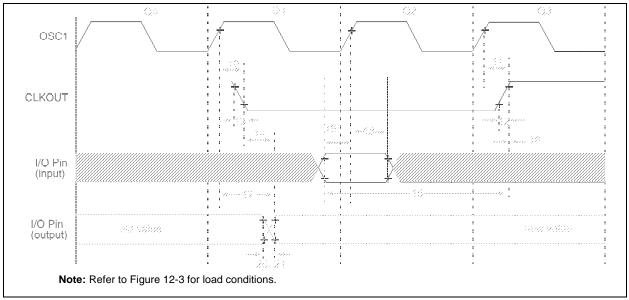

FIGURE 12-5: CLKOUT AND I/O TIMING

TABLE 12-3: CLKOUT AND I/O TIMING REQUIREMENTS

| Param<br>No. | Sym.     | Characteristic                                |               | Min.       | Тур† | Max.        | Units  | Conditions |

|--------------|----------|-----------------------------------------------|---------------|------------|------|-------------|--------|------------|

| 10*          | TosH2ckL | OSC1↑ to CLKOUT↓                              | _             | 75         | 200  | ns          | Note 1 |            |

| 11*          | TosH2ckH | OSC1¦ to CLKOUT¦                              |               | _          | 75   | 200         | ns     | Note 1     |

| 12*          | TckR     | CLKOUT rise time                              | _             | 35         | 100  | ns          | Note 1 |            |

| 13*          | TckF     | CLKOUT fall time                              |               | _          | 35   | 100         | ns     | Note 1     |

| 14*          | TckL2ioV | CLKOUT Ø to Port out valid                    |               | _          | _    | 0.5Tcy + 20 | ns     | Note 1     |

| 15*          | TioV2ckH | Port in valid before CLKOUT ¦                 |               | Tosc + 200 | _    | _           | ns     | Note 1     |

| 16*          | TckH2iol | Port in hold after CLKOUT ¦                   |               | 0          | _    | _           | ns     | Note 1     |

| 17*          | TosH2ioV | OSC1¦ (Q1 cycle) to Port out valid            |               | _          | 50   | 150         | ns     |            |

| 18*          | TosH2ioI | OSC1¦ (Q2 cycle) to Port input                | Standard      | 100        | _    | _           | ns     |            |

| 18A*         |          | invalid (I/O in hold time)                    | Extended (LC) | 200        | _    | _           | ns     |            |

| 19*          | TioV2osH | Port input valid to OSC1¦ (I/O in setup time) |               | 0          | 1    | 1           | ns     |            |

| 20*          | TioR     | Port output rise time                         | Standard      |            | 10   | 40          | ns     |            |

| 20A*         |          |                                               | Extended (LC) | _          | _    | 80          | ns     |            |

| 21*          | TioF     | Port output fall time                         | Standard      | _          | 10   | 40          | ns     |            |

| 21A*         |          |                                               | Extended (LC) | _          | 1    | 80          | ns     |            |

| 22††*        | TINP     | INT pin high or low time                      |               | Tcy        | l    |             | ns     |            |

| 23††*        | TRBP     | RB7:RB4 change INT high or low time           |               | Tcy        | _    | _           | ns     |            |

<sup>\*</sup> These parameters are characterized but not tested.

Note1: Measurements are taken in RC mode where CLKOUT output is 4 x Tosc.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

<sup>††</sup> These parameters are asynchronous events not related to any internal clock edge.

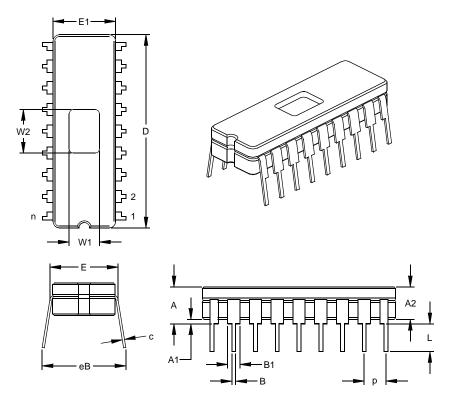

### 18-Lead Ceramic Dual In-line with Window (JW) - 300 mil (CERDIP)

For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units |      | INCHES* |      | MILLIMETERS |       |       |  |

|----------------------------|-------|------|---------|------|-------------|-------|-------|--|

| Dimension Limits           |       | MIN  | NOM     | MAX  | MIN         | NOM   | MAX   |  |

| Number of Pins             | n     |      | 18      |      |             | 18    |       |  |

| Pitch                      | р     |      | .100    |      |             | 2.54  |       |  |

| Top to Seating Plane       | Α     | .170 | .183    | .195 | 4.32        | 4.64  | 4.95  |  |

| Ceramic Package Height     | A2    | .155 | .160    | .165 | 3.94        | 4.06  | 4.19  |  |

| Standoff                   | A1    | .015 | .023    | .030 | 0.38        | 0.57  | 0.76  |  |

| Shoulder to Shoulder Width | Е     | .300 | .313    | .325 | 7.62        | 7.94  | 8.26  |  |

| Ceramic Pkg. Width         | E1    | .285 | .290    | .295 | 7.24        | 7.37  | 7.49  |  |

| Overall Length             | D     | .880 | .900    | .920 | 22.35       | 22.86 | 23.37 |  |

| Tip to Seating Plane       | L     | .125 | .138    | .150 | 3.18        | 3.49  | 3.81  |  |

| Lead Thickness             | С     | .008 | .010    | .012 | 0.20        | 0.25  | 0.30  |  |

| Upper Lead Width           | B1    | .050 | .055    | .060 | 1.27        | 1.40  | 1.52  |  |

| Lower Lead Width           | В     | .016 | .019    | .021 | 0.41        | 0.47  | 0.53  |  |

| Overall Row Spacing §      | eB    | .345 | .385    | .425 | 8.76        | 9.78  | 10.80 |  |

| Window Width               | W1    | .130 | .140    | .150 | 3.30        | 3.56  | 3.81  |  |

| Window Length              | W2    | .190 | .200    | .210 | 4.83        | 5.08  | 5.33  |  |

<sup>\*</sup> Controlling Parameter § Significant Characteristic JEDEC Equivalent: MO-036 Drawing No. C04-010

**NOTES:**

**NOTES:**

### **INDEX**

| A                                                 |        | Enable (CCP1IE Bit)                            |         |    |

|---------------------------------------------------|--------|------------------------------------------------|---------|----|

| A/D                                               | 45     | Flag (CCP1IF Bit)                              |         | 17 |

| A/D Converter Enable (ADIE Bit)                   |        | PWM Mode. See PWM                              |         |    |

| A/D Converter Flag (ADIF Bit)                     |        | Timer Resources                                |         | 39 |

| A/D Converter Interrupt, Configuring              |        | Timing Diagram                                 |         | 85 |

| ADCON0 Register                                   |        | CCP1CON Register                               |         | 39 |

| ADCON1 Register                                   |        | CCP1M3:CCP1M0 Bits                             |         | 39 |

| ADRES Register                                    |        | CCP1X:CCP1Y Bits                               |         | 39 |

|                                                   |        | Code Protection                                | 51,     | 65 |

| Analog Port Pins, Configuring                     |        | CP1:CP0 Bits                                   |         | 52 |

| Block Diagram                                     |        | Compare (CCP Module)                           |         |    |

| Block Diagram, Analog Input Model                 |        | Block Diagram                                  |         |    |

| Channel Select (CHS2:CHS0 Bits)                   |        | CCP Pin Configuration                          |         |    |

| Clock Select (ADCS1:ADCS0 Bits)                   |        | CCPR1H:CCPR1L Registers                        |         |    |

| Configuring the Module                            |        | Software Interrupt                             |         |    |

| Conversion Clock (Tad)                            |        | Special Event Trigger                          |         |    |

| Conversion Status (GO/DONE Bit)                   |        | Timer1 Mode Selection                          |         |    |

| Conversions                                       |        | Configuration Bits                             |         |    |

| Converter Characteristics                         |        | Conversion Considerations                      |         |    |

| Module On/Off (ADON Bit)                          |        | Customer Change Notification Service           |         |    |

| Port Configuration Control (PCFG2:PCFG0)          |        | Customer Notification Service                  |         |    |

| Sampling Requirements                             |        |                                                |         |    |

| Special Event Trigger (CCP)                       | 41, 50 | Customer Support                               | 1       | UI |

| Timing Diagram                                    | 87     | D                                              |         |    |

| Absolute Maximum Ratings                          | 73     | Poto Momony                                    |         | 40 |

| ADCON0 Register                                   | 11, 45 | Data Memory                                    |         |    |

| ADCS1:ADCS0 Bits                                  |        | Bank Select (RP1:RP0 Bits)                     |         |    |

| ADON Bit                                          | 45     | General Purpose Registers                      |         |    |

| CHS2:CHS0 Bits                                    | 45     | Register File Map                              |         |    |

| GO/DONE Bit                                       |        | Special Function Registers                     |         |    |

| ADCON1 Register                                   | ,      | DC Characteristics                             |         |    |

| PCFG2:PCFG0 Bits                                  |        | Development Support                            |         |    |

| ADRES Register                                    |        | Direct Addressing                              |         | 20 |

| Analog-to-Digital Converter. See A/D Architecture |        | E                                              |         |    |

| PIC16C712/716 Block Diagram                       |        | <del>-</del>                                   |         |    |

| Assembler                                         |        | Electrical Characteristics                     |         |    |

| MPASM Assembler                                   | 70     | Errata                                         |         |    |

| WII AGW AGGEMBIEL                                 | 70     | External Power-on Reset Circuit                |         | 55 |

| В                                                 |        | F                                              |         |    |

| Banking, Data Memory                              | 10 13  | •                                              |         |    |

| BOR. See Brown-out Reset                          | 10, 10 | Family of Devices                              |         |    |

| Brown-Out Reset (BOR)                             | 55     | PIC16C7XX                                      |         |    |

| Brown-out Reset (BOR)                             |        | Firmware Instructions                          |         | 67 |

| BOR Enable (BODEN Bit)                            |        | 1                                              |         |    |

| BOR Status (BOR Bit)                              |        |                                                |         |    |

| , ,                                               |        | I/O Ports                                      |         |    |

| Timing Diagram                                    | 03     | ID Locations                                   |         |    |

| C                                                 |        | In-Circuit Serial Programming™ (ICSP™)         | 51,     | 65 |

|                                                   |        | Indirect Addressing                            |         | 20 |

| C Compilers                                       | 70     | FSR Register                                   | 10, 11, | 20 |

| MPLAB C18                                         | _      | INDF Register                                  |         | 11 |

| MPLAB C30                                         |        | Instruction Format                             |         | 67 |

| Capture (CCP Module)                              |        | Instruction Set                                |         | 67 |

| Block Diagram                                     |        | Summary Table                                  |         | 68 |

| CCP Pin Configuration                             |        | INT Interrupt (RB0/INT). See Interrupt Sources |         |    |

| CCPR1H:CCPR1L Registers                           |        | INTCON Register                                | 11.     | 15 |

| Changing Between Capture Prescalers               | 40     | GIE Bit                                        |         |    |

| Software Interrupt                                |        | INTE Bit                                       |         |    |

| Timer1 Mode Selection                             | 40     | INTF Bit                                       |         |    |

| Capture/Compare/PWM (CCP)                         | 39     | PEIE Bit                                       |         |    |

| Capture Mode. See Capture                         |        | RBIE Bit                                       |         |    |

| CCP1CON Register                                  | 11, 39 | RBIF Bit                                       |         |    |

| CCPR1H Register                                   |        | TOIE Bit                                       | ,       |    |

| CCPR1L Register                                   | 11, 39 | TOIF Bit                                       |         |    |

| Compare Mode. See Compare                         |        | Internet Address                               |         |    |

|                                                   |        | III.011161 AUU1633                             | 1       | υI |