Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                           |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                  |

| Data Converters            | A/D 4x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 18-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c712-20e-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and Peripheral Modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is give in Table 2-1. The Special Function Registers can be classified into two sets; core (CPU) and peripheral. Those registers associated with the core functions are described in detail in this section. Those related to the operation of the peripheral features are described in detail in that peripheral feature section.

| Addr    | Name                    | Bit 7              | Bit 6                                                        | Bit 5         | Bit 4            | Bit 3         | Bit 2        | Bit 1         | Bit 0   | Value on:<br>POR,<br>BOR | Value on<br>all other<br>Resets (4) |

|---------|-------------------------|--------------------|--------------------------------------------------------------|---------------|------------------|---------------|--------------|---------------|---------|--------------------------|-------------------------------------|

| Bank 0  |                         |                    |                                                              |               |                  |               |              |               |         |                          |                                     |

| 00h     | INDF <sup>(1)</sup>     | Addressing         | this location                                                | uses conten   | ts of FSR to ac  | ldress data r | nemory (not  | a physical re | gister) | 0000 0000                | 0000 0000                           |

| 01h     | TMR0                    | Timer0 Mod         | lule's Registe                                               | er            |                  |               |              |               |         | XXXX XXXX                | uuuu uuuu                           |

| 02h     | PCL <sup>(1)</sup>      | Program Co         | ounter's (PC)                                                | Least Signif  | icant Byte       |               |              |               |         | 0000 0000                | 0000 0000                           |

| 03h     | STATUS <sup>(1)</sup>   | IRP <sup>(4)</sup> | RP1 <sup>(4)</sup>                                           | RP0           | TO               | PD            | Z            | DC            | С       | rr01 1xxx                | rr0q quuu                           |

| 04h     | FSR <sup>(1)</sup>      | Indirect Data      | a Memory A                                                   | ddress Pointe | er               |               |              |               |         | xxxx xxxx                | uuuu uuuu                           |

| 05h     | PORTA <sup>(5,6)</sup>  | _                  | —                                                            | (7)           | PORTA Data       | Latch when    | written: POR | TA pins wher  | n read  | xx xxxx                  | xu uuuu                             |

| 06h     | PORTB <sup>(5,6)</sup>  | PORTB Dat          | a Latch whe                                                  | n written: PC | ORTB pins whe    | n read        |              |               |         | xxxx xxxx                | uuuu uuuu                           |

| 07h     | DATACCP                 | (7)                | (7)                                                          | (7)           | (7)              | (7)           | DCCP         | (7)           | DT1CK   | xxxx xxxx                | xxxx xuxu                           |

| 08h-09h | _                       | Unimplemented      |                                                              |               |                  |               |              |               | -       | -                        |                                     |

| 0Ah     | PCLATH <sup>(1,2)</sup> | _                  | — — Write Buffer for the upper 5 bits of the Program Counter |               |                  |               |              |               | 0 0000  | 0 0000                   |                                     |

| 0Bh     | INTCON <sup>(1)</sup>   | GIE                | PEIE                                                         | TOIE          | INTE             | RBIE          | T0IF         | INTF          | RBIF    | 0000 000x                | 0000 000u                           |

| 0Ch     | PIR1                    | _                  | ADIF                                                         | —             | —                | _             | CCP1IF       | TMR2IF        | TMR1IF  | -0 0000                  | -0 0000                             |

| 0Dh     | _                       | Unimpleme          | nted                                                         |               |                  |               |              |               |         | -                        | -                                   |

| 0Eh     | TMR1L                   | Holding Reg        | gister for the                                               | Least Signifi | icant Byte of th | e 16-bit TMF  | 1 Register   |               |         | xxxx xxxx                | uuuu uuuu                           |

| 0Fh     | TMR1H                   | Holding Reg        | gister for the                                               | Most Signific | cant Byte of the | e 16-bit TMR  | 1 Register   |               |         | xxxx xxxx                | uuuu uuuu                           |

| 10h     | T1CON                   | _                  | —                                                            | T1CKPS1       | T1CKPS0          | T1OSCEN       | T1SYNC       | TMR1CS        | TMR10N  | 00 0000                  | uu uuuu                             |

| 11h     | TMR2                    | Timer2 Mod         | lule's Registe                                               | er            |                  |               |              |               |         | 0000 0000                | 0000 0000                           |

| 12h     | T2CON                   | _                  | TOUTPS3                                                      | TOUTPS2       | TOUTPS1          | TOUTPS0       | TMR2ON       | T2CKPS1       | T2CKPS0 | -000 0000                | -000 0000                           |

| 13h-14h |                         |                    |                                                              |               |                  |               |              |               |         |                          |                                     |

| 15h     | CCPR1L                  | Capture/Co         | mpare/PWM                                                    | Register1 (L  | SB)              |               |              |               |         | xxxx xxxx                | uuuu uuuu                           |

| 16h     | CCPR1H                  | Capture/Co         | mpare/PWM                                                    | Register1 (N  | MSB)             |               |              |               |         | xxxx xxxx                | uuuu uuuu                           |

| 17h     | CCP1CON                 | _                  | _                                                            | DC1B1         | DC1B0            | CCP1M3        | CCP1M2       | CCP1M1        | CCP1M0  | 00 0000                  | 00 0000                             |

| 18h-1Dh | _                       | Unimpleme          | nted                                                         |               |                  |               |              |               |         | -                        | -                                   |

| 1Eh     | ADRES                   | A/D Result I       | Register                                                     |               |                  |               |              |               |         | xxxx xxxx                | uuuu uuuu                           |

| 1Fh     | ADCON0                  | ADCS1              | ADCS0                                                        | CHS2          | CHS1             | CHS0          | GO/DONE      | _             | ADON    | 0000 00-0                | 0000 00-0                           |

Legend: x = unknown, u = unchanged, q = value depends on condition, --- = unimplemented, read as '0',

Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from either bank.

2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for PC<12:8> whose contents are transferred to the upper byte of the program counter.

3: Other (non Power-up) Resets include: external Reset through MCLR and the Watchdog Timer Reset.

4: The IRP and RP1 bits are reserved. Always maintain these bits clear.

5: On any device Reset, these pins are configured as inputs.

6: This is the value that will be in the port output latch.

7: Reserved bits; Do Not Use.

# 2.2.2.2 OPTION\_REG Register

The OPTION\_REG register is a readable and writable register, which contains various control bits to configure the TMR0 prescaler/WDT postscaler (single assignable register known also as the prescaler), the External INT Interrupt, TMR0 and the weak pull-ups on PORTB.

Note: To achieve a 1:1 prescaler assignment for the TMR0 register, assign the prescaler to the Watchdog Timer.

# FIGURE 2-5: OPTION\_REG REGISTER (ADDRESS 81h)

| R/W-1<br>RBPU | R/W-1                                                | R/W-1<br>T0CS                                                               | R/W-1<br>T0SE | R/W-1<br>PSA | R/W-1<br>PS2           | R/W-1<br>PS1 | R/W-1<br>PS0 | R = Readable bit                                                                      |

|---------------|------------------------------------------------------|-----------------------------------------------------------------------------|---------------|--------------|------------------------|--------------|--------------|---------------------------------------------------------------------------------------|

| it7           | INTEDG                                               | 1003                                                                        | 1032          | FGA          | F 32                   | -31          | bit0         | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR Reset |

| oit 7:        | <b>RBPU</b> : PO<br>1 = PORTE<br>0 = PORTE           | 3 pull-ups                                                                  | are disal     | oled         | lividual port          | latch valu   | es           |                                                                                       |

| oit 6:        | <b>INTEDG</b> : I<br>1 = Interru<br>0 = Interru      | pt on rising                                                                | g edge of     | f RB0/INT    |                        |              |              |                                                                                       |

| oit 5:        | <b>TOCS</b> : TMI<br>1 = Transit<br>0 = Interna      | ion on RA                                                                   | 4/T0CKI       | pin          | (OUT)                  |              |              |                                                                                       |

| bit 4:        |                                                      | ent on hig                                                                  | h-to-low      | transition   | on RA4/T0<br>on RA4/T0 |              |              |                                                                                       |

| bit 3:        | <b>PSA</b> : Pres<br>1 = Presca<br>0 = Presca        | ler is assi                                                                 | gned to t     | he WDT       | module                 |              |              |                                                                                       |

| bit 2-0:      | <b>PS2:PS0</b> :                                     | Prescaler                                                                   | Rate Sel      | ect bits     |                        |              |              |                                                                                       |

|               | Bit Value                                            | TMR0 Ra                                                                     | te WD         | Γ Rate       |                        |              |              |                                                                                       |

|               | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | 1 : 2<br>1 : 4<br>1 : 8<br>1 : 16<br>1 : 32<br>1 : 64<br>1 : 128<br>1 : 256 | 1 :<br>3 1 :  | 2            |                        |              |              |                                                                                       |

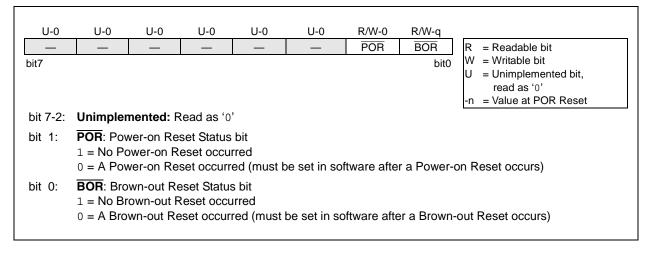

# 2.2.2.6 PCON Register

The Power Control (PCON) register contains a flag bit to allow differentiation between a Power-on Reset (POR) to an external MCLR Reset or WDT Reset. These devices contain an additional bit to differentiate a Brown-out Reset condition from a Power-on Reset condition. Note: If the BODEN Configuration bit is set, BOR is '1' on Power-on Reset. If the BODEN Configuration bit is clear, BOR is unknown on Power-on Reset. The BOR Status bit is a "don't care" and is

not necessarily predictable if the brown-out circuit is disabled (the BODEN Configuration bit is clear). BOR must then be set by the user and checked on subsequent resets to see if it is clear, indicating a brown-out has occurred.

# FIGURE 2-9: PCON REGISTER (ADDRESS 8Eh)

# 2.3 PCL and PCLATH

The Program Counter (PC) specifies the address of the instruction to fetch for execution. The PC is 13 bits wide. The low byte is called the PCL register. This register is readable and writable. The high byte is called the PCH register. This register contains the PC<12:8> bits and is not directly readable or writable. All updates to the PCH register go through the PCLATH register.

# 2.3.1 STACK

The stack allows a combination of up to 8 program calls and interrupts to occur. The stack contains the return address from this branch in program execution.

Mid-range devices have an 8-level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the Stack Pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not modified when the stack is PUSHed or POPed.

After the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

# 2.4 Program Memory Paging

The CALL and GOTO instructions provide 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction, the upper bit of the address is provided by PCLATH<3>. When doing a CALL or GOTO instruction, the user must ensure that the page select bit is programmed so that the desired program memory page is addressed. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is pushed onto the stack. Therefore, manipulation of the PCLATH<3> bit is not required for the return instructions (which POPs the address from the stack).

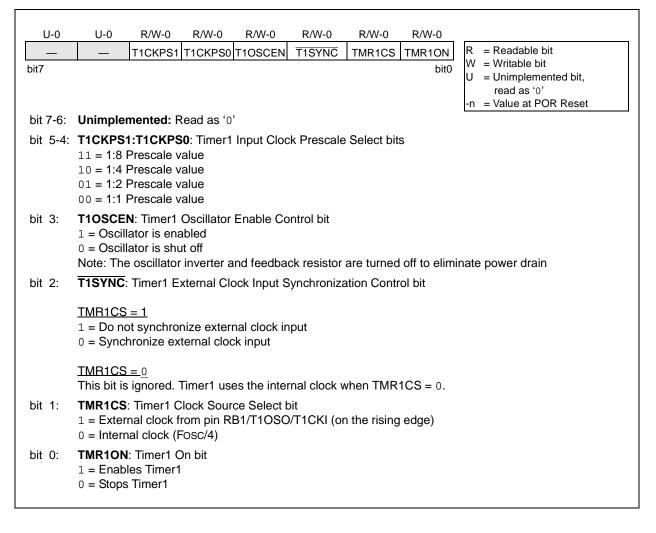

# 5.0 TIMER1 MODULE

The Timer1 module timer/counter has the following features:

- 16-bit timer/counter (Two 8-bit registers; TMR1H and TMR1L)

- · Readable and writable (Both registers)

- Internal or external clock select

- Interrupt on overflow from FFFFh to 0000h

- Reset from CCP module trigger

Timer1 has a control register, shown in Figure 5-1. Timer1 can be enabled/disabled by setting/clearing control bit TMR1ON (T1CON<0>).

Figure 5-2 is a simplified block diagram of the Timer1 module.

Additional information on timer modules is available in the PIC<sup>®</sup> Mid-Range Reference Manual, (DS33023).

# 5.1 Timer1 Operation

Timer1 can operate in one of these modes:

- · As a timer

- · As a synchronous counter

- · As an asynchronous counter

The operating mode is determined by the clock select bit, TMR1CS (T1CON<1>).

In timer mode, Timer1 increments every instruction cycle. In counter mode, it increments on every rising edge of the external clock input.

When the Timer1 oscillator is enabled (T1OSCEN is set), the RB2/T1OSI and RB1/T1OSO/T1CKI pins become inputs. That is, the TRISB<2:1> value is ignored.

Timer1 also has an internal "Reset input". This Reset can be generated by the CCP module (see Section 7.0 "Capture/Compare/PWM (CCP) Module(s)").

# FIGURE 5-1: T1CON: TIMER1 CONTROL REGISTER (ADDRESS 10h)

## 7.3.3 SET-UP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- 2. Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- 3. Make the CCP1 pin an output by clearing the TRISCCP<2> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

- 5. Configure the CCP1 module for PWM operation.

## TABLE 7-3:EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 20 MHz

| PWM Frequency              | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|----------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                  | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits)  | 10       | 10       | 10        | 8         | 7         | 5.5       |

| Address | Name    | Bit 7     | Bit 6                                             | Bit 5         | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|---------|---------|-----------|---------------------------------------------------|---------------|---------|---------|--------|---------|---------|-------------------------|---------------------------------|

| 07h     | DATACCP | —         | _                                                 |               |         |         | DCCP   |         | DT1CK   | xxxx xxxx               | xxxx xuxu                       |

| 0Bh,8Bh | INTCON  | GIE       | PEIE                                              | TOIE          | INTE    | RBIE    | TOIF   | INTF    | RBIF    | 0000 000x               | 0000 000u                       |

| 0Ch     | PIR1    | —         | ADIF                                              | _             | _       | _       | CCP1IF | TMR2IF  | TMR1IF  | -0000                   | -0000                           |

| 11h     | TMR2    | Timer2 Mc | Timer2 Module's Register                          |               |         |         |        |         |         | 0000 0000               | 0000 0000                       |

| 12h     | T2CON   | —         | TOUTPS3                                           | TOUTPS2       | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000               | -000 0000                       |

| 15h     | CCPR1L  | Capture/C | ompare/PWI                                        | V Register 1  | (LSB)   |         |        |         |         | xxxx xxxx               | uuuu uuuu                       |

| 16h     | CCPR1H  | Capture/C | ompare/PWI                                        | VI Register 1 | (MSB)   |         |        |         |         | xxxx xxxx               | uuuu uuuu                       |

| 17h     | CCP1CON | —         | _                                                 | DC1B1         | DC1B0   | CCP1M3  | CCP1M2 | CCP1M1  | CCP1M0  | 00 0000                 | 00 0000                         |

| 87h     | TRISCCP | —         |                                                   | _             | _       | _       | TCCP   | _       | TT1CK   | xxxx x1x1               | xxxx x1x1                       |

| 8Ch     | PIE1    | —         | ADIE                                              | _             | _       | _       | CCP1IE | TMR2IE  | TMR1IE  | -0000                   | -0000                           |

| 92h     | PR2     | Timer2 Mc | ner2 Module's Period Register 1111 1111 1111 1111 |               |         |         |        |         |         |                         | 1111 1111                       |

## TABLE 7-4: REGISTERS ASSOCIATED WITH PWM AND TIMER2

Legend: x = unknown, u = unchanged, — = unimplemented read as '0'. Shaded cells are not used by PWM and Timer2.

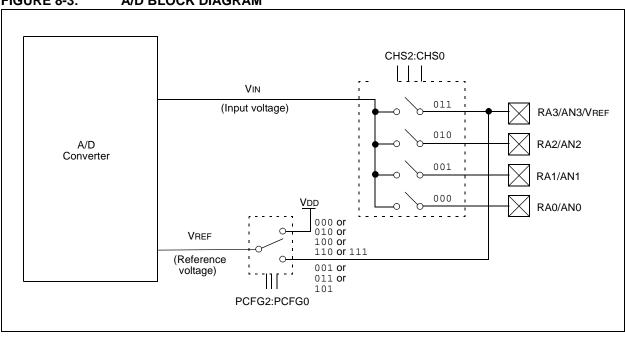

The ADRES register contains the result of the A/D conversion. When the A/D conversion is complete, the result is loaded into the ADRES register, the GO/DONE bit (ADCON0<2>) is cleared and the A/D Interrupt Flag bit ADIF is set. The block diagram of the A/D module is shown in Figure 8-3.

The value that is in the ADRES register is not modified for a Power-on Reset. The ADRES register will contain unknown data after a Power-on Reset.

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS bits selected as an input. To determine acquisition time, see **Section 8.1 "A/D Acquisition Requirements"**. After this acquisition time has elapsed, the A/D conversion can be started. The following steps should be followed for doing an A/D conversion:

- 1. Configure the A/D module:

- Configure analog pins/voltage reference/ and digital I/O (ADCON1)

- Select A/D input channel (ADCON0)

- Select A/D conversion clock (ADCON0)

- Turn on A/D module (ADCON0)

- 2. Configure A/D interrupt (if desired):

- Clear ADIF bit

- Set ADIE bit

- Set GIE bit

- 3. Wait the required acquisition time.

- 4. Start conversion:

- Set GO/DONE bit (ADCON0)

- 5. Wait for A/D conversion to complete, by either:

- Polling for the GO/DONE bit to be cleared

OR

- Waiting for the A/D interrupt

- Read A/D Result register (ADRES), clear bit ADIF if required.

- 7. For the next conversion, go to step 1 or step 2 as required. The A/D conversion time per bit is defined as TAD. A minimum wait of 2TAD is required before next acquisition starts.

## FIGURE 8-3: A/D BLOCK DIAGRAM

# 9.0 SPECIAL FEATURES OF THE CPU

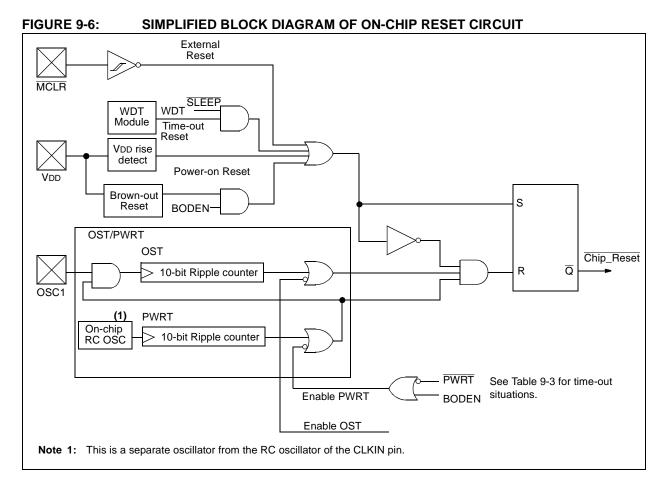

The PIC16C712/716 devices have a host of features intended to maximize system reliability, minimize cost through elimination of external components, provide power-saving operating modes and offer code protection. These are:

- OSC Selection

- Reset:

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- Sleep

- Code protection

- ID locations

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

These devices have a Watchdog Timer, which can be shut off only through Configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay on power-up only and is designed to keep the part in Reset while the power supply stabilizes. With these two timers on-chip, most applications need no external Reset circuitry. Sleep mode is designed to offer a very low-current Power-Down mode. The user can wake-up from Sleep through external Reset, Watchdog Timer Wake-up, or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost, while the LP crystal option saves power. A set of Configuration bits are used to select various options.

Additional information on special features is available in the  $PIC^{®}$  Mid-Range Reference Manual, (DS33023).

# 9.1 Configuration Bits

The Configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h-3FFFh), which can be accessed only during programming.

# PIC16C712/716

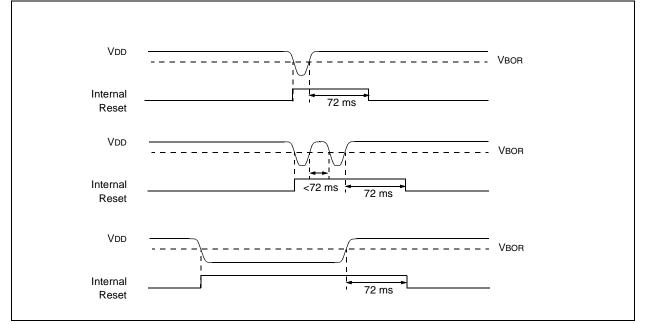

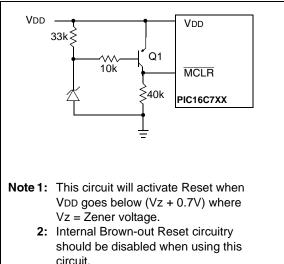

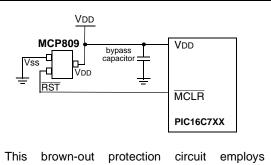

**EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2**

$$\frac{R1}{R1 + R2} = 0$$

- 2: Internal Brown-out Reset should be disabled when using this circuit.

- 3: Resistors should be adjusted for the characteristics of the transistor.

#### **FIGURE 9-10: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 3**

Microchip Technology's MCP809 microcontroller supervisor. The MCP8XX and MCP1XX families of supervisors provide push-pull and open collector outputs with both high and low active Reset pins. There are 7 different trip point selections to accommodate 5V and 3V systems

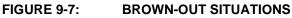

#### 9.8 **Time-out Sequence**

On power-up the time-out sequence is as follows: First PWRT time-out is invoked after the POR time delay has expired. Then OST is activated. The total time-out will vary based on oscillator configuration and the status of the PWRT. For example, in RC mode with the PWRT disabled, there will be no time-out at all. Figure 9-11, Figure 9-12, and Figure 9-13 depict time-out sequences on power-up.

Since the time-outs occur from the POR pulse, if MCLR is kept low long enough, the time-outs will expire. Then bringing MCLR high will begin execution immediately (Figure 9-13). This is useful for testing purposes or to synchronize more than one PIC16CXXX device operating in parallel.

Table 9-5 shows the Reset conditions for some Special Function Registers, while Table 9-6 shows the Reset conditions for all the registers.

# 9.16 In-Circuit Serial Programming™

PIC16CXXX microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

For complete details on serial programming, please refer to the In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) Guide, (DS30277).

# 11.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB® IDE Software

- Assemblers/Compilers/Linkers

- MPASM<sup>™</sup> Assembler

- MPLAB C18 and MPLAB C30 C Compilers

- MPLINK<sup>™</sup> Object Linker/

- MPLIB™ Object Librarian

- MPLAB ASM30 Assembler/Linker/Library

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- MPLAB ICE 4000 In-Circuit Emulator

- In-Circuit Debugger

- MPLAB ICD 2

- Device Programmers

- PICSTART<sup>®</sup> Plus Development Programmer

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration and Development Boards and Evaluation Kits

# 11.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> operating system-based application that contains:

- A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- · A full-featured editor with color-coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- High-level source code debugging

- Visual device initializer for easy register initialization

- · Mouse over variable inspection

- Drag and drop variables from source to watch windows

- · Extensive on-line help

- Integration of select third party tools, such as HI-TECH Software C Compilers and IAR C Compilers

The MPLAB IDE allows you to:

- Edit your source files (either assembly or C)

- One touch assemble (or compile) and download to PIC MCU emulator and simulator tools (automatically updates all project information)

- Debug using:

- Source files (assembly or C)

- Mixed assembly and C

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

# 11.2 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for all PIC MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

# 11.3 MPLAB C18 and MPLAB C30 C Compilers

The MPLAB C18 and MPLAB C30 Code Development Systems are complete ANSI C compilers for Microchip's PIC18 family of microcontrollers and dsPIC30F family of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use not found with other compilers.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

# 11.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 11.5 MPLAB ASM30 Assembler, Linker and Librarian

MPLAB ASM30 Assembler produces relocatable machine code from symbolic assembly language for dsPIC30F devices. MPLAB C30 C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- Support for the entire dsPIC30F instruction set

- · Support for fixed-point and floating-point data

- · Command line interface

- Rich directive set

- Flexible macro language

- MPLAB IDE compatibility

# 11.6 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC<sup>®</sup> DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, as well as internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C18 and MPLAB C30 C Compilers, and the MPASM and MPLAB ASM30 Assemblers. The software simulator offers the flexibility to develop and debug code outside of the laboratory environment, making it an excellent, economical software development tool.

| DC CHA       | RACTE | RISTICS                                                | Operating<br>Operating<br>" <b>DC Char</b>                                                  | voltage | ature<br>-4<br>-4<br>VDD rang<br><b>tics: PIC1</b> | 0°C ≤<br>0°C ≤<br>0°C ≤<br>le as de<br>6C712/ |                                                                   |  |  |  |

|--------------|-------|--------------------------------------------------------|---------------------------------------------------------------------------------------------|---------|----------------------------------------------------|-----------------------------------------------|-------------------------------------------------------------------|--|--|--|

|              |       |                                                        | Extended)" and Section 12.2 "DC Characteristics: PIC16LC71 716-04 (Commercial, Industrial)" |         |                                                    |                                               |                                                                   |  |  |  |

| Param<br>No. | Sym.  | Characteristic                                         | Min.                                                                                        | Typ†    | Max.                                               | Units                                         | Conditions                                                        |  |  |  |

| D080         | Vol   | Output Low Voltage<br>I/O ports                        |                                                                                             | _       | 0.6                                                | V                                             | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +85°C                       |  |  |  |

|              |       |                                                        | —                                                                                           | —       | 0.6                                                | V                                             | IOL = 7.0 mA, VDD = 4.5V,<br>-40°C to +125°C                      |  |  |  |

| D083         |       | OSC2/CLKOUT<br>(RC Osc mode)                           | —                                                                                           | —       | 0.6                                                | V                                             | IOL = 1.6 mA, VDD = 4.5V,<br>-40°C to +85°C                       |  |  |  |

|              |       |                                                        | —                                                                                           | —       | 0.6                                                | V                                             | IOL = 1.2 mA, VDD = 4.5V,<br>-40°C to +125°C                      |  |  |  |

| D090         | Vон   | Output High Voltage<br>I/O ports (Note 3)              | Vdd-0.7                                                                                     | _       | _                                                  | V                                             | IOH = -3.0 mA, VDD = 4.5V,<br>-40°С to +85°С                      |  |  |  |

|              |       |                                                        | Vdd-0.7                                                                                     | —       | _                                                  | V                                             | IOH = -2.5 mA, VDD = 4.5V,<br>-40°С to +125°С                     |  |  |  |

| D092         |       | OSC2/CLKOUT (RC Osc<br>mode)                           | Vdd-0.7                                                                                     | —       | _                                                  | V                                             | IOH = -1.3 mA, VDD = 4.5V,<br>-40°С to +85°С                      |  |  |  |

|              |       |                                                        | Vdd-0.7                                                                                     | —       | —                                                  | V                                             | IOH = -1.0 mA, VDD = 4.5V,<br>-40°С to +125°С                     |  |  |  |

| D150*        | Vod   | Open-Drain High Voltage                                | _                                                                                           | _       | 8.5                                                | V                                             | RA4 pin                                                           |  |  |  |

| D100         | Cosc2 | Capacitive Loading Specs on<br>Output Pins<br>OSC2 pin |                                                                                             | _       | 15                                                 | pF                                            | In XT, HS and LP modes when external clock is used to drive OSC1. |  |  |  |

| D101         | Сю    | All I/O pins and OSC2 (in RC mode)                     | _                                                                                           | —       | 50                                                 | pF                                            |                                                                   |  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC Oscillator mode, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC MCU be driven with external clock in RC mode.

2: The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

# PIC16C712/716

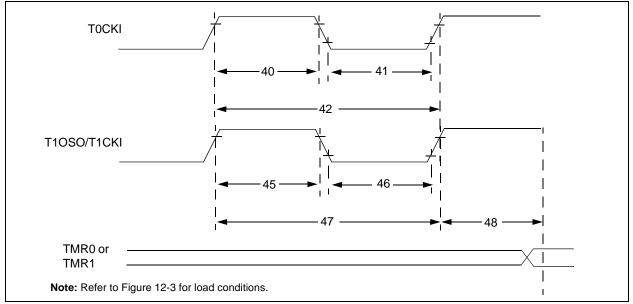

# FIGURE 12-8: TIMER0 AND TIMER1 EXTERNAL CLOCK TIMINGS

| TABLE 12-5: TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS | \$ |

|-----------------------------------------------------------|----|

|-----------------------------------------------------------|----|

| Param<br>No. | Sym.      | Characteristic                                 |                      |                | Min.                                             | Тур† | Max.  | Units | Conditions                         |  |

|--------------|-----------|------------------------------------------------|----------------------|----------------|--------------------------------------------------|------|-------|-------|------------------------------------|--|

| 40*          | Tt0H      | T0CKI High Pulse V                             | High Pulse Width     |                | 0.5TCY + 20                                      | _    | _     | ns    | Must also meet                     |  |

|              |           |                                                |                      | With Prescaler | 10                                               | _    | _     | ns    | parameter 42                       |  |

| 41*          | Tt0L      | T0CKI Low Pulse W                              | /idth                | No Prescaler   | 0.5TCY + 20                                      | —    | —     | ns    | Must also meet                     |  |

|              |           |                                                |                      | With Prescaler | 10                                               | —    | —     | ns    | parameter 42                       |  |

| 42*          | Tt0P      | T0CKI Period                                   |                      | No Prescaler   | TCY + 40                                         | —    | —     | ns    |                                    |  |

|              |           |                                                |                      | With Prescaler | Greater of:<br>20 or <u>Tcy + 40</u><br>N        | -    | —     | ns    | N = prescale value<br>(2, 4,, 256) |  |

| 45*          | Tt1H      | T1CKI High Time                                | Synchronous, P       | Prescaler = 1  | 0.5TCY + 20                                      | -    | _     | ns    | Must also meet                     |  |

|              |           | -                                              | Synchronous,         | Standard       | 15                                               | —    | —     | ns    | parameter 47                       |  |

|              |           |                                                | Prescaler =<br>2,4,8 | Extended (LC)  | 25                                               | —    | —     | ns    |                                    |  |

|              |           |                                                | Asynchronous         | Standard       | 30                                               | —    | —     | ns    |                                    |  |

|              |           |                                                |                      | Extended (LC)  | 50                                               | —    | —     | ns    |                                    |  |

| 46*          | Tt1L      | T1CKI Low Time                                 | Synchronous, P       | rescaler = 1   | 0.5TCY + 20                                      | -    | —     | ns    | Must also meet                     |  |

|              |           |                                                | Synchronous,         | Standard       | 15                                               | —    |       | ns    | parameter 47                       |  |

|              |           |                                                | Prescaler =<br>2,4,8 | Extended (LC)  | 25                                               | —    | —     | ns    |                                    |  |

|              |           |                                                | Asynchronous         | Standard       | 30                                               | —    |       | ns    |                                    |  |

|              |           |                                                |                      | Extended (LC)  | 50                                               | —    |       | ns    |                                    |  |

| 47*          | Tt1P      | T1CKI input period                             | Synchronous          | Standard       | <u>Greater of:</u><br>30 OR <u>TCY + 40</u><br>N | -    | —     | ns    | N = prescale value<br>(1, 2, 4, 8) |  |

|              |           |                                                |                      | Extended (LC)  | <u>Greater of:</u><br>50 OR <u>TCY + 40</u><br>N |      |       |       | N = prescale value<br>(1, 2, 4, 8) |  |

|              |           |                                                | Asynchronous         | Standard       | 60                                               | —    |       | ns    |                                    |  |

|              |           |                                                |                      | Extended (LC)  | 100                                              | -    | _     | ns    |                                    |  |

|              | Ft1       | Timer1 oscillator inp<br>(oscillator enabled b |                      |                | DC                                               | —    | 200   | kHz   |                                    |  |

| 48           | TCKEZtmr' | 1 Delay from external                          | clock edge to tir    | ner increment  | 2Tosc                                            | —    | 7Tosc | —     |                                    |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# TABLE 12-7:A/D CONVERTER CHARACTERISTICS:<br/>PIC16C712/716-04 (COMMERCIAL, INDUSTRIAL, EXTENDED)<br/>PIC16C712/716-20 (COMMERCIAL, INDUSTRIAL, EXTENDED)<br/>PIC16LC712/716-04 (COMMERCIAL, INDUSTRIAL)

| Param<br>No. | Sym.                             | Characteristic                              |               | Min.                   | Тур†   | Max.       | Units                                                                                                                              | Conditions                               |

|--------------|----------------------------------|---------------------------------------------|---------------|------------------------|--------|------------|------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| A01          | NR                               | Resolution                                  | _             | _                      | 8-bits | bit        | VREF = VDD = 5.12V,<br>VSS £ VAIN £ VREF                                                                                           |                                          |

| A02          | EABS                             | Total Absolute error                        | _             | _                      | < ± 1  | LSb        | VREF = VDD = 5.12V,<br>VSS £ VAIN £ VREF                                                                                           |                                          |

| A03          | EIL                              | Integral linearity error                    |               | —                      | -      | < ± 1      | LSb                                                                                                                                | VREF = VDD = 5.12V,<br>VSS £ VAIN £ VREF |

| A04          | Edl                              | Differential linearity erro                 | or            | _                      | _      | < ± 1      | LSb                                                                                                                                | VREF = VDD = 5.12V,<br>VSS £ VAIN £ VREF |

| A05          | Efs                              | Full scale error                            | —             | _                      | < ± 1  | LSb        | VREF = VDD = 5.12V,<br>VSS £ VAIN £ VREF                                                                                           |                                          |

| A06          | EOFF                             | Offset error                                | —             | _                      | < ± 1  | LSb        | VREF = VDD = 5.12V,<br>VSS £ VAIN £ VREF                                                                                           |                                          |

| A10          | —                                | Monotonicity                                | _             | guaranteed<br>(Note 3) | _      | _          | VSS £ VAIN £ VREF                                                                                                                  |                                          |

| A20          | VREF                             | Reference voltage                           |               | 2.5V                   | —      | Vdd + 0.3  | V                                                                                                                                  |                                          |

| A25          | VAIN                             | Analog input voltage                        |               | Vss - 0.3              |        | Vref + 0.3 | V                                                                                                                                  |                                          |

| A30          | ZAIN                             | Recommended impeda<br>analog voltage source | nce of        | —                      | _      | 10.0       | kΩ                                                                                                                                 |                                          |

| A40          | IAD                              | A/D conversion cur-                         | Standard      | _                      | 180    | _          | μΑ                                                                                                                                 | Average current consump-                 |

|              |                                  | rent (VDD)                                  | Extended (LC) | —                      | 90     | _          | μA                                                                                                                                 | tion when A/D is on.<br><b>(Note 1)</b>  |

| A50          | IREF VREF input current (Note 2) |                                             | 10            | _                      | 1000   | μΑ         | During VAIN acquisition.<br>Based on differential of<br>VHOLD to VAIN to charge<br>CHOLD, see Section 9.1<br>"Configuration Bits". |                                          |

|              |                                  |                                             |               | —                      | _      | 10         | μΑ                                                                                                                                 | During A/D Conversion cycle              |

2: \* These parameters are characterized but not tested.

3: † Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: When A/D is off, it will not consume any current other than minor leakage current.

The power-down current spec includes any such leakage from the A/D module.

2: VREF current is from RA3 pin or VDD pin, whichever is selected as reference input.

3: The A/D conversion result never decreases with an increase in the Input Voltage, and has no missing codes.

# PIC16C712/716

NOTES:

# PIC16C712/716

| TMR1L Register 11, 31                    |

|------------------------------------------|

| Timer2                                   |

| Block Diagram 36                         |

| Postscaler. See Postscaler, Timer2       |

| PR2 Register 12, 36, 42                  |

| Prescaler. See Prescaler, Timer2         |

| T2CON Register 11, 36                    |

| TMR2 Register 11, 36                     |

| TMR2 to PR2 Match Enable (TMR2IE Bit) 16 |

| TMR2 to PR2 Match Flag (TMR2IF Bit)      |

| TMR2 to PR2 Match Interrupt 36, 37, 42   |

| Timing Diagrams                          |

| Time-out Sequence on Power-up60          |

| Wake-up from Sleep via Interrupt65       |

| Timing Diagrams and Specifications       |

| A/D Conversion                           |

| Brown-out Reset (BOR) 83                 |

| Capture/Compare/PWM (CCP) 85             |

| CLKOUT and I/O                           |

| External Clock                           |

| Oscillator Start-up Timer (OST)          |

| Power-up Timer (PWRT)                    |

| Reset                                    |

| Timer0 and Timer1                        |

| Watchdog Timer (WDT)                     |

|                                          |

# W

| W Register                                    |

|-----------------------------------------------|

| Wake-up from Sleep 51   Wake-up from Sleep 64 |

|                                               |

| Interrupts                                    |

|                                               |

| Timing Diagram                                |

| WDT Reset 59                                  |

| Watchdog Timer (WDT) 51, 63                   |

| Block Diagram 63                              |

| Enable (WDTE Bit) 52, 63                      |

| Postscaler. See Postscaler, WDT               |

| Programming Considerations 63                 |

| RC Oscillator 63                              |

| Time-out Period 63                            |

| Timing Diagram 83                             |

| WDT Reset, Normal Operation 54, 58, 59        |

| WDT Reset, Sleep 54, 58, 59                   |

| WWW Address 101                               |

| WWW, On-Line Support 3                        |

# THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

# **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support

NOTES: