Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E-XF

| 2014110                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                           |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                  |

| Data Converters            | A/D 4x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 18-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c712t-04-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.2.2.4 PIE1 Register

This register contains the individual enable bits for the peripheral interrupts.

Note: Bit PEIE (INTCON<6>) must be set to enable any peripheral interrupt.

### FIGURE 2-7: PIE1 REGISTER (ADDRESS 8Ch)

| U-0      | R/W-0                                                                                                                                     | U-0        | U-0         | R/W-0      | R/W-0  | R/W-0  | R/W-0  |                                                                                      |  |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------|------------|--------|--------|--------|--------------------------------------------------------------------------------------|--|--|

|          | ADIE                                                                                                                                      | —          |             | —          | CCP1IE | TMR2IE | TMR1IE | R = Readable bit                                                                     |  |  |

| bit7     |                                                                                                                                           |            |             |            |        |        | bit0   | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>-n = Value at POR Reset |  |  |

| bit 7:   | Unimpler                                                                                                                                  | nented: R  | ead as '0   | ,          |        |        |        |                                                                                      |  |  |

| bit 6:   | ADIE: A/E<br>1 = Enabl<br>0 = Disab                                                                                                       | es the A/E | ) interrupt |            | bit    |        |        |                                                                                      |  |  |

| bit 5-3: | Unimpler                                                                                                                                  | nented: R  | ead as '0   | 1          |        |        |        |                                                                                      |  |  |

| bit 2:   | <b>CCP1IE</b> : 0<br>1 = Enabl<br>0 = Disab                                                                                               | es the CC  | P1 interru  | pt         |        |        |        |                                                                                      |  |  |

| bit 1:   | TMR2IE:<br>1 = Enabl<br>0 = Disab                                                                                                         | es the TM  | R2 to PR    | 2 match in | •      |        |        |                                                                                      |  |  |

| bit 0:   | <b>TMR1IE</b> : TMR1 Overflow Interrupt Enable bit<br>1 = Enables the TMR1 overflow interrupt<br>0 = Disables the TMR1 overflow interrupt |            |             |            |        |        |        |                                                                                      |  |  |

|          |                                                                                                                                           |            |             |            |        |        |        |                                                                                      |  |  |

# 7.0 CAPTURE/COMPARE/PWM (CCP) MODULE(S)

Each CCP (Capture/Compare/PWM) module contains a 16-bit register, which can operate as a 16-bit capture register, as a 16-bit compare register or as a PWM master/slave Duty Cycle register. Table 7-1 shows the timer resources of the CCP module modes.

Capture/Compare/PWM Register 1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. All are readable and writable.

### FIGURE 7-1: CCP1CON REGISTER (ADDRESS 17h)

U-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 DC1B1 DC1B0 CCP1M3 CCP1M2 CCP1M1 CCP1M0 R = Readable bit W = Writable bit bit7 bit0 U = Unimplemented bit, read as '0' -n = Value at POR Reset bit 7-6: Unimplemented: Read as '0' bit 5-4: DC1B1:DC1B0: PWM Least Significant bits Capture Mode: Unused Compare Mode: Unused PWM Mode: These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPR1L. bit 3-0: CCP1M3:CCP1M0: CCP1 Mode Select bits 0000 = Capture/Compare/PWM off (resets CCP1 module) 0100 = Capture mode, every falling edge 0101 = Capture mode, every rising edge 0110 = Capture mode, every 4th rising edge 0111 = Capture mode, every 16th rising edge 1000 = Compare mode, set output on match (CCP1IF bit is set) 1001 = Compare mode, clear output on match (CCP1IF bit is set) 1010 = Compare mode, generate software interrupt on match (CCP1IF bit is set, CCP1 pin is unaffected) 1011 = Compare mode, trigger special event (CCP1IF bit is set; CCP1 resets TMR1 and starts an A/D conversion (if A/D module is enabled)) 11xx = PWM mode

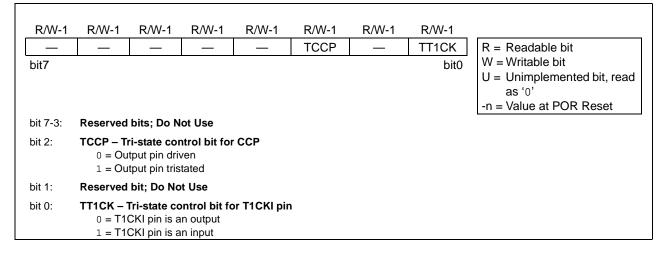

#### FIGURE 7-2: TRISCCP REGISTER (ADDRESS 87H)

Additional information on the CCP module is available in the PIC<sup>®</sup> Mid-Range Reference Manual, (DS33023).

# TABLE 7-1:CCP MODE – TIMER<br/>RESOURCE

| CCP Mode | Timer Resource |  |  |  |  |  |  |  |  |

|----------|----------------|--|--|--|--|--|--|--|--|

| Capture  | Timer1         |  |  |  |  |  |  |  |  |

| Compare  | Timer1         |  |  |  |  |  |  |  |  |

| PWM      | Timer2         |  |  |  |  |  |  |  |  |

|          |                |  |  |  |  |  |  |  |  |

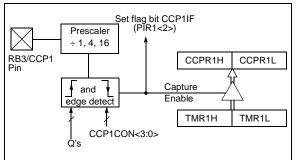

# 7.1 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on pin RB3/CCP1. An event is defined as:

- every falling edge

- every rising edge

- every 4th rising edge

- every 16th rising edge

An event is selected by control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit CCP1IF (PIR1<2>) is set. It must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value will be lost.

#### FIGURE 7-3:

#### CAPTURE MODE OPERATION BLOCK DIAGRAM

# 7.1.1 CCP PIN CONFIGURATION

In Capture mode, the CCP output must be disabled by setting the TRISCCP<2> bit.

**Note:** If the RB3/CCP1 is configured as an output by clearing the TRISCCP<2> bit, a write to the DCCP bit can cause a capture condition.

## 7.1.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

#### 7.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit CCP1IE (PIE1<2>) clear to avoid false interrupts and should clear the flag bit CCP1IF following any such change in Operating mode.

# 7.1.4 CCP PRESCALER

There are four prescaler settings, specified by bits CCP1M3:CCP1M0. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. This means that any Reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore the first capture may be from a non-zero prescaler. Example 7-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

### EXAMPLE 7-1: CHANGING BETWEEN CAPTURE PRESCALERS

| CLRF  | CCP1CON     | ;Turn CCP module off    |

|-------|-------------|-------------------------|

| MOVLW | NEW_CAPT_PS | ;Load the W reg with    |

|       |             | ; the new prescaler     |

|       |             | ; mode value and CCP ON |

| MOVWF | CCP1CON     | ;Load CCP1CON with this |

|       |             | ; value                 |

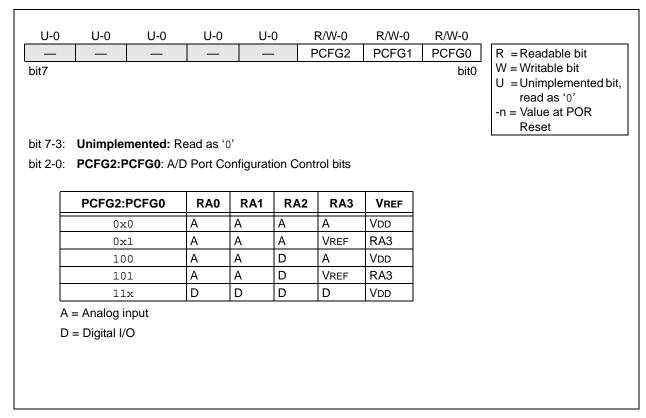

# 8.0 ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

The Analog-to-Digital (A/D) Converter module has four inputs.

The A/D allows conversion of an analog input signal to a corresponding 8-bit digital number (refer to Application Note AN546 for use of A/D Converter). The output of the sample and hold is the input into the converter, which generates the result via successive approximation. The analog reference voltage is software selectable to either the device's positive supply voltage (VDD) or the voltage level on the RA3/AN3/VREF pin.

The A/D converter has a unique feature of being able to operate while the device is in Sleep mode. To operate in Sleep, the A/D conversion clock must be derived from the A/D's internal RC oscillator. Additional information on the A/D module is available in the PIC<sup>®</sup> Mid-Range Reference Manual, (DS33023).

The A/D module has three registers. These registers are:

- A/D Result Register (ADRES)

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 (ADCON1)

A device Reset forces all registers to their Reset state. This forces the A/D module to be turned off, and any conversion is aborted.

The ADCON0 register, shown in Figure 8-1, controls the operation of the A/D module. The ADCON1 register, shown in Figure 8-2, configures the functions of the port pins. The port pins can be configured as analog inputs (RA3 can also be a voltage reference) or as digital I/O.

| R/W-0         | R/W-0                                     | R/W-0                                                    | R/W-0                | R/W-0      | R/W-0                             | U-0       | R/W-0        |                                                                                                          |

|---------------|-------------------------------------------|----------------------------------------------------------|----------------------|------------|-----------------------------------|-----------|--------------|----------------------------------------------------------------------------------------------------------|

| ADCS1<br>bit7 | ADCS0                                     | CHS2                                                     | CHS1                 | CHS0       | GO/DONE                           |           | ADON<br>bit0 | R = Readable bit<br>W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>-n = Value at POR Reset |

| bit 7-6:      | 00 = Fos<br>01 = Fos<br>10 = Fos          | c/2<br>c/8<br>c/32                                       |                      |            | s Select bits<br>al ADC RC os     | cillator) |              |                                                                                                          |

| bit 5-3:      |                                           | annel 0, (F<br>annel 1, (F<br>annel 2, (F<br>annel 3, (F | RA2/AN2)<br>RA3/AN3) | I Select b | its                               |           |              |                                                                                                          |

| bit 2:        | GO/DON                                    | E: A/D Co                                                | nversion S           | Status bit |                                   |           |              |                                                                                                          |

|               |                                           | onversion<br>conversio                                   | on not in            |            | this bit starts<br>(This bit is a |           |              | by hardware when the A/D                                                                                 |

| bit 1:        | Unimpler                                  | mented: F                                                | Read as '0           | ,          |                                   |           |              |                                                                                                          |

| bit 0:        | <b>ADON</b> : A<br>1 = A/D c<br>0 = A/D c | onverter r                                               | nodule is d          |            |                                   |           |              |                                                                                                          |

FIGURE 8-1: ADCON0 REGISTER (ADDRESS 1Fh)

### FIGURE 8-2: ADCON1 REGISTER (ADDRESS 9Fh)

### 9.4 Power-On Reset (POR)

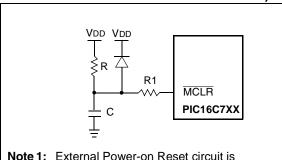

A Power-on Reset pulse is generated on-chip when VDD rise is detected (to a level of 1.5V-2.1V). To take advantage of the POR, just tie the MCLR pin directly (or through a resistor) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset. A maximum rise time for VDD is specified (parameter D004). For a slow rise time, see Figure 9-5.

When the device starts normal operation (exits the Reset condition), device operating parameters (voltage, frequency, temperature,...) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met. Brown-out Reset may be used to meet the startup conditions.

#### FIGURE 9-5:

#### EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- te1: External Power-on Reset circuit is required only if VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- **2:** R < 40 kΩ is recommended to make sure that voltage drop across R does not violate the device's electrical specification.

- **3:**  $R1 = 100\Omega$  to  $1 k\Omega$  will limit any current flowing into  $\overline{MCLR}$  from external capacitor C in the event of  $\overline{MCLR}/VPP$  pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

#### 9.5 Power-up Timer (PWRT)

The Power-up Timer provides a fixed nominal time-out (parameter #33), on power-up only, from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in Reset as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an acceptable level. A Configuration bit is provided to enable/disable the PWRT.

The power-up time delay will vary from chip to chip due to VDD, temperature, and process variation. See DC parameters for details.

## 9.6 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over (parameter #32). This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from Sleep.

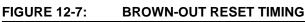

### 9.7 Brown-Out Reset (BOR)

The PIC16C712/716 members have on-chip Brownout Reset circuitry. A Configuration bit, BODEN, can disable (if clear/programmed) or enable (if set) the Brown-out Reset circuitry. If VDD falls below 4.0V, refer to VBOR parameter D005(VBOR) for a time greater than parameter (TBOR) in Table 12-6. The brown-out situation will reset the chip. A Reset is not guaranteed to occur if VDD falls below 4.0V for less than parameter (TBOR).

On any Reset (Power-on, Brown-out, Watchdog, etc.) the chip will remain in Reset until VDD rises above VBOR. The Power-up Timer will now be invoked and will keep the chip in Reset an additional 72 ms.

If VDD drops below VBOR while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be re-initialized. Once VDD rises above VBOR, the Power-Up Timer will execute a 72 ms Reset. The Power-up Timer should always be enabled when Brown-out Reset is enabled. Figure 9-7 shows typical Brown-out situations.

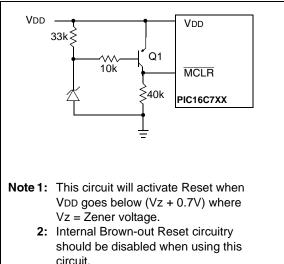

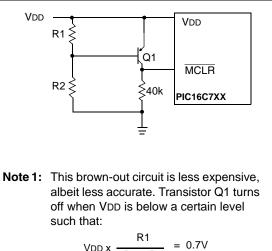

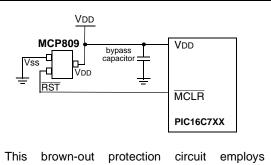

For operations where the desired brown-out voltage is other than 4V, an external brown-out circuit must be used. Figure 9-8, 9-9 and 9-10 show examples of external brown-out protection circuits.

**EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2**

$$\frac{R1}{R1 + R2} = 0$$

- 2: Internal Brown-out Reset should be disabled when using this circuit.

- 3: Resistors should be adjusted for the characteristics of the transistor.

#### **FIGURE 9-10:** EXTERNAL BROWN-OUT **PROTECTION CIRCUIT 3**

Microchip Technology's MCP809 microcontroller supervisor. The MCP8XX and MCP1XX families of supervisors provide push-pull and open collector outputs with both high and low active Reset pins. There are 7 different trip point selections to accommodate 5V and 3V systems

#### 9.8 **Time-out Sequence**

On power-up the time-out sequence is as follows: First PWRT time-out is invoked after the POR time delay has expired. Then OST is activated. The total time-out will vary based on oscillator configuration and the status of the PWRT. For example, in RC mode with the PWRT disabled, there will be no time-out at all. Figure 9-11, Figure 9-12, and Figure 9-13 depict time-out sequences on power-up.

Since the time-outs occur from the POR pulse, if MCLR is kept low long enough, the time-outs will expire. Then bringing MCLR high will begin execution immediately (Figure 9-13). This is useful for testing purposes or to synchronize more than one PIC16CXXX device operating in parallel.

Table 9-5 shows the Reset conditions for some Special Function Registers, while Table 9-6 shows the Reset conditions for all the registers.

#### 9.10.1 INT INTERRUPT

External interrupt on RB0/INT pin is edge triggered, either rising if bit INTEDG (OPTION\_REG<6>) is set, or falling if the INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, flag bit INTF (INTCON<1>) is set. This interrupt can be disabled by clearing enable bit INTE (INTCON<4>). Flag bit INTF must be cleared in software in the Interrupt Service Routine before re-enabling this interrupt. The INT interrupt can wake-up the processor from Sleep, if bit INTE was set prior to going into Sleep. The status of global interrupt enable bit GIE decides whether or not the processor branches to the interrupt vector following wake-up. See **Section 9.13** "**Power-down Mode** (**Sleep**)" for details on Sleep mode.

#### 9.10.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit T0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit T0IE (INTCON<5>). (Section 4.0 "Timer0 Module")

#### 9.10.3 PORTB INTCON CHANGE

An input change on PORTB<7:4> sets flag bit RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit RBIE (INTCON<4>). (Section 3.2 "PORTB and the TRISB Register")

#### 9.11 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt, (i.e., W register and STATUS register). This will have to be implemented in software.

Example 9-1 stores and restores the W and STATUS registers. The register, W\_TEMP, must be defined in each bank and must be defined at the same offset from the bank base address (i.e., if W\_TEMP is defined at 0x20 in bank 0, it must also be defined at 0xA0 in bank 1).

The example:

- a) Stores the W register.

- b) Stores the STATUS register in bank 0.

- c) Stores the PCLATH register.

- d) Executes the Interrupt Service Routine code (User-generated).

- e) Restores the STATUS register (and bank select bit).

- f) Restores the W and PCLATH registers.

| MOVWF  | W_TEMP         | ;Copy W to TEMP register, could be bank one or zero     |

|--------|----------------|---------------------------------------------------------|

| SWAPF  | STATUS,W       | ;Swap status to be saved into W                         |

| CLRF   | STATUS         | ;bank 0, regardless of current bank, Clears IRP,RP1,RP0 |

| MOVWF  | STATUS_TEMP    | ;Save status to bank zero STATUS_TEMP register          |

| MOVF   | PCLATH, W      | ;Only required if using pages 1, 2 and/or 3             |

| MOVWF  | PCLATH_TEMP    | ;Save PCLATH into W                                     |

| CLRF   | PCLATH         | ;Page zero, regardless of current page                  |

| BCF    | STATUS, IRP    | ;Return to Bank 0                                       |

| MOVF   | FSR, W         | ;Copy FSR to W                                          |

| MOVWF  | FSR_TEMP       | ;Copy FSR from W to FSR_TEMP                            |

| :      |                |                                                         |

| :(ISR) |                |                                                         |

| :      |                |                                                         |

| MOVF   | PCLATH_TEMP, W | ;Restore PCLATH                                         |

| MOVWF  | PCLATH         | ;Move W into PCLATH                                     |

| SWAPF  | STATUS_TEMP,W  | ;Swap STATUS_TEMP register into W                       |

|        |                | ;(sets bank to original state)                          |

| MOVWF  | STATUS         | ;Move W into STATUS register                            |

| SWAPF  | W_TEMP,F       | ;Swap W_TEMP                                            |

| SWAPF  | W TEMP,W       | ;Swap W TEMP into W                                     |

#### EXAMPLE 9-1: SAVING STATUS, W, AND PCLATH REGISTERS IN RAM

## 11.2 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for all PIC MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB IDE projects

- User-defined macros to streamline

assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

### 11.3 MPLAB C18 and MPLAB C30 C Compilers

The MPLAB C18 and MPLAB C30 Code Development Systems are complete ANSI C compilers for Microchip's PIC18 family of microcontrollers and dsPIC30F family of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use not found with other compilers.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

### 11.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 11.5 MPLAB ASM30 Assembler, Linker and Librarian

MPLAB ASM30 Assembler produces relocatable machine code from symbolic assembly language for dsPIC30F devices. MPLAB C30 C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- Support for the entire dsPIC30F instruction set

- · Support for fixed-point and floating-point data

- · Command line interface

- Rich directive set

- Flexible macro language

- MPLAB IDE compatibility

### 11.6 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC<sup>®</sup> DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, as well as internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C18 and MPLAB C30 C Compilers, and the MPASM and MPLAB ASM30 Assemblers. The software simulator offers the flexibility to develop and debug code outside of the laboratory environment, making it an excellent, economical software development tool.

### 11.11 PICSTART Plus Development Programmer

The PICSTART Plus Development Programmer is an easy-to-use, low-cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient. The PICSTART Plus Development Programmer supports most PIC devices in DIP packages up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus Development Programmer is CE compliant.

## 11.12 Demonstration, Development and Evaluation Boards

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart<sup>®</sup> battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Check the Microchip web page (www.microchip.com) and the latest *"Product Selector Guide"* (DS00148) for the complete list of demonstration, development and evaluation kits.

### 12.1 DC Characteristics: PIC16C712/716-04 (Commercial, Industrial, Extended) PIC16C712/716-20 (Commercial, Industrial, Extended)

| DC CHA                | Standard Operating Condit<br>Operating temperature |                                                                                                                                                  |                     |                           | $ \begin{array}{llllllllllllllllllllllllllllllllllll$ |                          |                                                                                                                                                                            |

|-----------------------|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------------|-------------------------------------------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.          | Sym.                                               | Characteristic                                                                                                                                   | Min.                | Тур†                      | Max.                                                  | Units                    | Conditions                                                                                                                                                                 |

| D001<br>D001A         | Vdd                                                | Supply Voltage                                                                                                                                   | 4.0<br>4.5<br>VBOR* |                           | 5.5<br>5.5<br>5.5                                     | V<br>V<br>V              | XT, RC and LP osc mode<br>HS osc mode<br>BOR enabled <sup>(7)</sup>                                                                                                        |

| D002*                 | Vdr                                                | RAM Data Retention Voltage <sup>(1)</sup>                                                                                                        | _                   | 1.5                       |                                                       | V                        |                                                                                                                                                                            |

| D003                  | VPOR                                               | VDD Start Voltage to ensure inter-<br>nal Power-on Reset signal                                                                                  | —                   | Vss                       | —                                                     | V                        | See section on Power-on Reset for details                                                                                                                                  |

| D004*<br>D004A*       | SVDD                                               | VDD Rise Rate to ensure internal<br>Power-on Reset signal                                                                                        | 0.05<br>TBD         | _                         | _                                                     | V/ms                     | PWRT enabled (PWRTE bit clear)<br>PWRT disabled (PWRTE bit set)<br>See section on Power-on Reset for details                                                               |

| D005                  | VBOR                                               | Brown-out Reset<br>voltage trip point                                                                                                            | 3.65                | —                         | 4.35                                                  | V                        | BODEN bit set                                                                                                                                                              |

| D010<br>D013          | IDD                                                | Supply Current <sup>(2,5)</sup>                                                                                                                  | _                   | 0.8<br>4.0                | 2.5<br>8.0                                            | mA<br>mA                 | Fosc = 4 MHz, VDD = 4.0V<br>Fosc = 20 MHz, VDD = 4.0V                                                                                                                      |

| D020<br>D021<br>D021B | IPD                                                | Power-down Current <sup>(3,5)</sup>                                                                                                              | <br>                | 10.5<br>1.5<br>1.5<br>2.5 | 42<br>16<br>19<br>19                                  | μΑ<br>μΑ<br>μΑ<br>μΑ     | VDD = 4.0V, WDT enabled, -40°C to +85°C<br>VDD = 4.0V, WDT disabled, 0°C to +70°C<br>VDD = 4.0V, WDT disabled, -40°C to +85°C<br>VDD = 4.0V, WDT disabled, -40°C to +125°C |

| D022*<br>D022A*       | ΔİWDT<br>ΔİBOR                                     | Module Differential Current <sup>(6)</sup><br>Watchdog Timer<br>Brown-out Reset                                                                  |                     | 6.0<br>TBD                | 20<br>200                                             | μΑ<br>μΑ                 | WDTE bit set, VDD = 4.0V<br>BODEN bit set, VDD = 5.0V                                                                                                                      |

| 1A                    | Fosc                                               | LP Oscillator Operating Frequency<br>RC Oscillator Operating Frequency<br>XT Oscillator Operating Frequency<br>HS Oscillator Operating Frequency | 0<br>0<br>0<br>0    |                           | 200<br>4<br>4<br>20                                   | KHz<br>MHz<br>MHz<br>MHz | All temperatures<br>All temperatures<br>All temperatures<br>All temperatures                                                                                               |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD,

- MCLR = VDD; WDT enabled/disabled as specified.

- **3:** The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD and Vss.

4: For RC Osc mode, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kOhm.

5: Timer1 oscillator (when enabled) adds approximately 20 µA to the specification. This value is from characterization and is for design guidance only. This is not tested.

6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

7: This is the voltage where the device enters the Brown-out Reset. When BOR is enabled, the device will operate correctly to this trip point.

#### 12.4.2 TIMING CONDITIONS

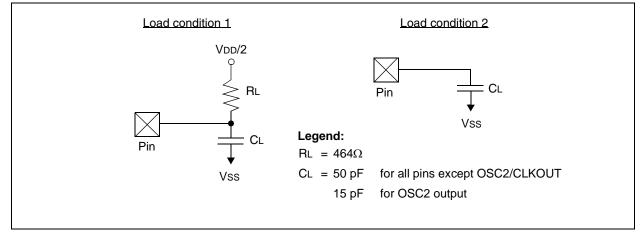

The temperature and voltages specified in Table 12-1 apply to all timing specifications, unless otherwise noted. Figure 12-3 specifies the load conditions for the timing specifications.

#### TABLE 12-1: TEMPERATURE AND VOLTAGE SPECIFICATIONS – AC

|                                                         | Standard Operating Cond   | Standard Operating Conditions (unless otherwise stated) |                  |           |                                      |  |  |  |  |  |

|---------------------------------------------------------|---------------------------|---------------------------------------------------------|------------------|-----------|--------------------------------------|--|--|--|--|--|

|                                                         | Operating temperature     | 0°C                                                     | $\leq$ Ta $\leq$ | +70°C     | for commercial                       |  |  |  |  |  |

|                                                         |                           | -40°C                                                   | $\leq$ Ta $\leq$ | +85°C     | for industrial                       |  |  |  |  |  |

|                                                         |                           | -40°C                                                   | $\leq$ Ta $\leq$ | +125°C    | for extended                         |  |  |  |  |  |

| AC CHARACTERISTICS                                      | Operating voltage VDD ran | ge as de                                                | escribed         | in DC spe | ec Section 12.1 "DC Characteristics: |  |  |  |  |  |

|                                                         | PIC16C712/716-04 (Comr    | nercial,                                                | Industri         | al, Exten | ded) PIC16C712/716-20 (Commercial,   |  |  |  |  |  |

|                                                         | Industrial, Extended)" an | d Sectio                                                | on 12.2 '        | 'DC Char  | acteristics: PIC16LC712/716-04 (Com- |  |  |  |  |  |

|                                                         | mercial, Industrial)".    |                                                         |                  |           |                                      |  |  |  |  |  |

| LC parts operate for commercial/industrial temp's only. |                           |                                                         |                  |           |                                      |  |  |  |  |  |

#### FIGURE 12-3: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

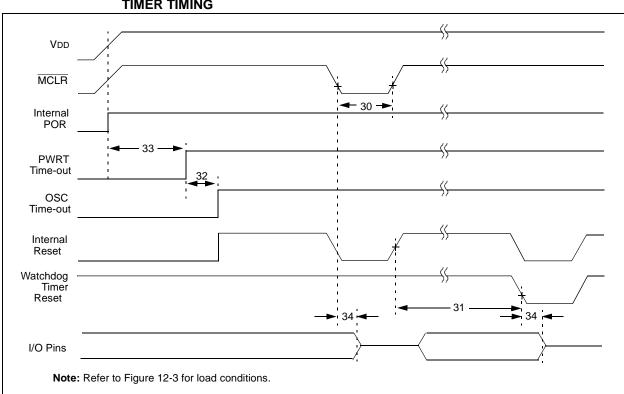

# FIGURE 12-6: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

# TABLE 12-4:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER,<br/>AND BROWN-OUT RESET REQUIREMENTS

| Parameter<br>No. | Sym.  | Characteristic                                   | Min. | Тур†      | Max. | Units | Conditions                |

|------------------|-------|--------------------------------------------------|------|-----------|------|-------|---------------------------|

| 30               | TmcL  | MCLR Pulse Width (low)                           | 2    | —         |      | μs    | VDD = 5V, -40°C to +125°C |

| 31*              | Twdt  | Watchdog Timer Time-out Period<br>(No Prescaler) | 7    | 18        | 33   | ms    | VDD = 5V, -40°C to +125°C |

| 32               | Tost  | Oscillation Start-up Timer Period                | _    | 1024 Tosc |      | —     | Tosc = OSC1 period        |

| 33*              | TPWRT | Power-up Timer Period                            | 28   | 72        | 132  | ms    | VDD = 5V, -40°C to +125°C |

| 34               | Tıoz  | I/O High-impedance from MCLR<br>Low or WDT Reset |      | _         | 2.1  | μs    |                           |

| 35               | TBOR  | Brown-out Reset Pulse Width                      | 100  | —         |      | μs    | $VDD \le BVDD (D005)$     |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

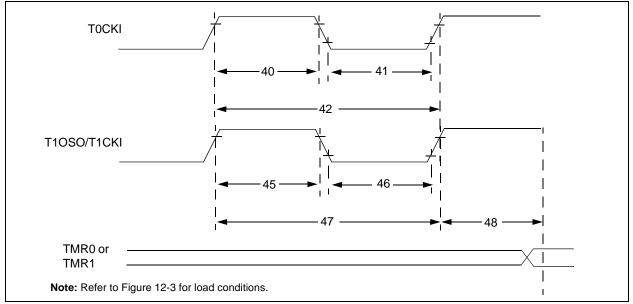

#### FIGURE 12-8: TIMER0 AND TIMER1 EXTERNAL CLOCK TIMINGS

| TABLE 12-5: TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS | \$ |

|-----------------------------------------------------------|----|

|-----------------------------------------------------------|----|

| Param<br>No. | Sym.      | Characteristic                                 |                            |                | Min.                                             | Тур† | Max.  | Units | Conditions                         |

|--------------|-----------|------------------------------------------------|----------------------------|----------------|--------------------------------------------------|------|-------|-------|------------------------------------|

| 40*          | Tt0H      | T0CKI High Pulse V                             | Vidth                      | No Prescaler   | 0.5TCY + 20                                      | _    | _     | ns    | Must also meet                     |

|              |           |                                                |                            | With Prescaler | 10                                               | _    | _     | ns    | parameter 42                       |

| 41*          | Tt0L      | T0CKI Low Pulse W                              | /idth                      | No Prescaler   | 0.5TCY + 20                                      | —    | —     | ns    | Must also meet                     |

|              |           |                                                |                            | With Prescaler | 10                                               | —    | —     | ns    | parameter 42                       |

| 42*          | Tt0P      | T0CKI Period                                   |                            | No Prescaler   | TCY + 40                                         | —    | —     | ns    |                                    |

|              |           |                                                |                            | With Prescaler | Greater of:<br>20 or <u>Tcy + 40</u><br>N        | -    | —     | ns    | N = prescale value<br>(2, 4,, 256) |

| 45*          | Tt1H      | T1CKI High Time                                | Synchronous, P             | Prescaler = 1  | 0.5TCY + 20                                      | -    | _     | ns    | Must also meet                     |

|              |           | -                                              | Synchronous,               | Standard       | 15                                               | —    | —     | ns    | parameter 47                       |

|              |           |                                                | Prescaler =<br>2,4,8       | Extended (LC)  | 25                                               | —    | —     | ns    |                                    |

|              |           |                                                | Asynchronous               | Standard       | 30                                               | —    | —     | ns    |                                    |

|              |           |                                                |                            | Extended (LC)  | 50                                               | —    | —     | ns    |                                    |

| 46*          | Tt1L      | T1CKI Low Time                                 | Synchronous, Prescaler = 1 |                | 0.5TCY + 20                                      | -    | —     | ns    | Must also meet                     |

|              |           |                                                | Synchronous,               | Standard       | 15                                               | —    |       | ns    | parameter 47                       |

|              |           |                                                | Prescaler =<br>2,4,8       | Extended (LC)  | 25                                               | —    | —     | ns    |                                    |

|              |           |                                                | Asynchronous               | Standard       | 30                                               | —    |       | ns    |                                    |

|              |           |                                                |                            | Extended (LC)  | 50                                               | —    |       | ns    |                                    |

| 47*          | Tt1P      | T1CKI input period                             | Synchronous                | Standard       | <u>Greater of:</u><br>30 OR <u>TCY + 40</u><br>N | -    | —     | ns    | N = prescale value<br>(1, 2, 4, 8) |

|              |           |                                                |                            | Extended (LC)  | <u>Greater of:</u><br>50 OR <u>TCY + 40</u><br>N |      |       |       | N = prescale value<br>(1, 2, 4, 8) |

|              |           |                                                | Asynchronous               | Standard       | 60                                               | —    |       | ns    |                                    |

|              |           |                                                |                            | Extended (LC)  | 100                                              | -    | _     | ns    |                                    |

|              | Ft1       | Timer1 oscillator inp<br>(oscillator enabled b |                            |                | DC                                               | —    | 200   | kHz   |                                    |

| 48           | TCKEZtmr' | 1 Delay from external                          | clock edge to tir          | ner increment  | 2Tosc                                            | —    | 7Tosc | —     |                                    |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

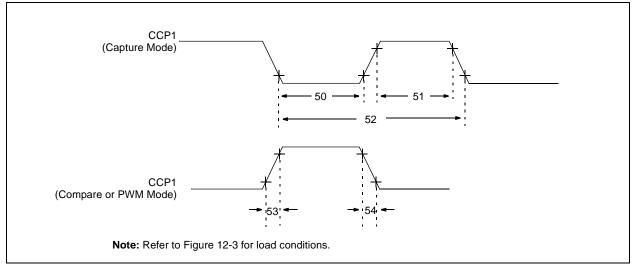

#### TABLE 12-6: CAPTURE/COMPARE/PWM REQUIREMENTS

| Param<br>No. | Sym.                              | Characteristic      |                |               | Min                   | Тур† | Max | Units | Conditions                         |

|--------------|-----------------------------------|---------------------|----------------|---------------|-----------------------|------|-----|-------|------------------------------------|

| 50*          | TccL                              | CCP1 input low      | No Prescaler   |               | 0.5TCY + 20           | -    | _   | ns    |                                    |

|              |                                   | time                | With Prescaler | Standard      | 10                    | -    | _   | ns    |                                    |

|              |                                   |                     |                | Extended (LC) | 20                    | -    | _   | ns    |                                    |

| 51*          | TccH CCP1 input high No Prescaler |                     | ·              | 0.5Tcy + 20   | —                     |      | ns  |       |                                    |

|              | time                              | time \              | With Prescaler | Standard      | 10                    | -    | _   | ns    |                                    |

|              |                                   |                     |                | Extended (LC) | 20                    | -    | _   | ns    |                                    |

| 52*          | TccP                              | CCP1 input period   |                |               | <u>3Tcy + 40</u><br>N | —    | _   | ns    | N = prescale value<br>(1,4, or 16) |

| 53*          | TccR                              | CCP1 output rise ti | me             | Standard      | —                     | 10   | 25  | ns    |                                    |

|              |                                   |                     |                | Extended (LC) | —                     | 25   | 45  | ns    |                                    |

| 54*          | TccF CCP1 output fall time        |                     | Standard       | —             | 10                    | 25   | ns  |       |                                    |

|              |                                   |                     |                | Extended (LC) | —                     | 25   | 45  | ns    |                                    |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

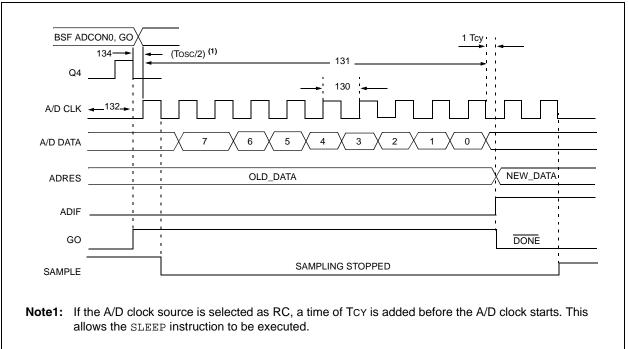

#### TABLE 12-8: A/D CONVERSION REQUIREMENTS

| Param<br>No. | Sym. | Characteristic                                    |               | Min.     | Тур†     | Max. | Units | Conditions                                                                                                                                                                                                                    |

|--------------|------|---------------------------------------------------|---------------|----------|----------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 130          | TAD  | A/D clock period                                  | Standard      | 1.6      |          | _    | μS    | Tosc based, VREF $\geq$ 3.0V                                                                                                                                                                                                  |

|              |      |                                                   | Extended (LC) | 2.0      | —        | _    | μS    | Tosc based, VREF full range                                                                                                                                                                                                   |

|              |      |                                                   | Standard      | 2.0      | 4.0      | 6.0  | μS    | A/D RC Mode                                                                                                                                                                                                                   |

|              |      |                                                   | Extended (LC) | 3.0      | 6.0      | 9.0  | μS    | A/D RC Mode                                                                                                                                                                                                                   |

| 131          | TCNV | Conversion time (not including S/H time) (Note 1) |               | 11       | —        | 11   | Tad   |                                                                                                                                                                                                                               |

| 132          | TACQ | Acquisition time                                  |               | (Note 2) | 20       | _    | μS    |                                                                                                                                                                                                                               |

|              |      |                                                   |               | 5*       | _        | _    | μs    | The minimum time is the amplifier<br>settling time. This may be used if<br>the "new" input voltage has not<br>changed by more than 1 LSb (i.e.,<br>20.0 mV @ 5.12V) from the last<br>sampled voltage (as stated on<br>CHOLD). |

| 134          | TGO  | Q4 to A/D clock start                             |               | _        | Tosc/2 § | _    |       | If the A/D clock source is selected<br>as RC, a time of Tcy is added<br>before the A/D clock starts. This<br>allows the SLEEP instruction to be<br>executed.                                                                  |

| 135          | Tswc | Switching from conve                              | 1.5 §         | —        | _        | TAD  |       |                                                                                                                                                                                                                               |

: \* These parameters are characterized but not tested.

: † Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

: § This specification ensured by design.

Note 1: ADRES register may be read on the following TCY cycle.

2: See Section 9.1 "Configuration Bits" for min. conditions.

NOTES:

| TMR1L Register 11, 31                    |

|------------------------------------------|

| Timer2                                   |

| Block Diagram 36                         |

| Postscaler. See Postscaler, Timer2       |

| PR2 Register 12, 36, 42                  |

| Prescaler. See Prescaler, Timer2         |

| T2CON Register 11, 36                    |

| TMR2 Register 11, 36                     |

| TMR2 to PR2 Match Enable (TMR2IE Bit) 16 |

| TMR2 to PR2 Match Flag (TMR2IF Bit)      |

| TMR2 to PR2 Match Interrupt 36, 37, 42   |

| Timing Diagrams                          |

| Time-out Sequence on Power-up60          |

| Wake-up from Sleep via Interrupt         |

| Timing Diagrams and Specifications       |

| A/D Conversion                           |

| Brown-out Reset (BOR) 83                 |

| Capture/Compare/PWM (CCP) 85             |

| CLKOUT and I/O                           |

| External Clock                           |

| Oscillator Start-up Timer (OST)          |

| Power-up Timer (PWRT)                    |

| Reset                                    |

| Timer0 and Timer1                        |

| Watchdog Timer (WDT)                     |

|                                          |

### W

| W Register                             |   |

|----------------------------------------|---|

| Wake-up from Sleep                     |   |

| Wake-up from Sleep                     |   |

| Interrupts                             |   |

| MCLR Reset 59                          |   |

| Timing Diagram 65                      | 5 |

| WDT Reset 59                           | ) |

| Watchdog Timer (WDT) 51, 63            | 3 |

| Block Diagram 63                       | 3 |

| Enable (WDTE Bit) 52, 63               | 3 |

| Postscaler. See Postscaler, WDT        |   |

| Programming Considerations 63          | - |

| RC Oscillator 63                       |   |

| Time-out Period 63                     | 3 |

| Timing Diagram 83                      | 3 |

| WDT Reset, Normal Operation 54, 58, 59 | ) |

| WDT Reset, Sleep 54, 58, 59            | ) |

| WWW Address 101                        | L |

| WWW, On-Line Support 3                 | 3 |

# **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| TO:<br>RE: |                                                        | Total Pages Sent                       |

|------------|--------------------------------------------------------|----------------------------------------|

| Fro        | m: Name                                                |                                        |

|            | Company                                                |                                        |

|            | Address                                                |                                        |

|            | City / State / ZIP / Country                           |                                        |

|            | Telephone: ()                                          | FAX: ()                                |

|            | lication (optional):                                   |                                        |

| Wo         | uld you like a reply?YN                                |                                        |

| Dev        | rice: PIC16C712/716                                    | Literature Number: DS41106C            |

| Que        | ostions:                                               |                                        |

| 1.         | What are the best features of this document?           |                                        |

|            |                                                        |                                        |

| 2.         | How does this document meet your hardware and soft     | ware development needs?                |

|            |                                                        |                                        |

|            |                                                        |                                        |

| 3.         | Do you find the organization of this document easy to  | follow? If not, why?                   |

|            |                                                        |                                        |

| 4          | What additions to the document do you think would er   | phance the structure and subject?      |

| 4.         | what additions to the document do you think would en   |                                        |

|            |                                                        |                                        |

| 5.         | What deletions from the document could be made with    | nout affecting the overall usefulness? |

|            |                                                        |                                        |

|            |                                                        |                                        |

| 6.         | Is there any incorrect or misleading information (what | and where)?                            |

|            |                                                        |                                        |

| 7.         | How would you improve this document?                   |                                        |

|            |                                                        |                                        |

|            |                                                        |                                        |

## PIC16C712/716 PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.<br> <br>Device Fi | <u>-XX X</u><br>     <br>requency Temperatur<br>Range Range                                                                                          | /XX<br> <br>e Package         | XXX<br> <br>Pattern | Í F<br>P  | •<br>PIC16C716 – 04/P 301 = Commercial temp.,<br>PDIP package, 4 MHz, normal VDD limits, QTP<br>attern #301.                                                               |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|---------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device:                    | PIC16C712 <sup>(1)</sup> , PIC16C7<br>PIC16LC712 <sup>(1)</sup> , PIC16L<br>PIC16C716 <sup>(1)</sup> , PIC16C7<br>PIC16LC716 <sup>(1)</sup> , PIC16L | C712T <sup>(2)</sup> :VDD rar | nge 2.5V to 5.5V    | р<br>с) F | PIC16LC712 – 04I/SO = Industrial temp., SOIC<br>vackage, 200 kHz, Extended VDD limits.<br>PIC16C712 – 20I/P = Industrial temp., PDIP<br>vackage, 20MHz, normal VDD limits. |

| Frequency Range:           | 04 = 4 MHz<br>20 = 20 MHz                                                                                                                            |                               |                     | Note 1    | : C = CMOS<br>LC = Low Power CMOS<br>I: T = in tape and reel – SOIC, SSOP<br>packages only.                                                                                |

| Temperature<br>Range:      | blank = $0^{\circ}$ C to<br>I = -40^{\circ}C to +1<br>E = -40^{\circ}C to +12                                                                        |                               | I)                  |           | LC extended temperature device is not<br>offered.  LC is not offered at 20 MHz                                                                                             |

| Package:                   | JW = Windowed<br>SO = SOIC<br>P = PDIP<br>SS = SSOP                                                                                                  | CERDIP                        |                     |           |                                                                                                                                                                            |

| Pattern:                   | QTP, SQTP, Code or Sp<br>(blank otherwise)                                                                                                           | ecial Requiremer              | nts                 |           |                                                                                                                                                                            |

\* JW Devices are UV erasable and can be programmed to any device configuration. JW Devices meet the electrical requirement of each oscillator type (including LC devices).

#### Sales and Support

#### Data Sheets

Products supported by a preliminary Data Sheet may have an errata sheet describing minor operational differences and recommended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:

- 1. Your local Microchip sales office

- 2. The Microchip Worldwide Site (www.microchip.com)