Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 13                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                 |

| Data Converters            | A/D 4x8b                                                                  |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 18-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c716-04-so |

| Key Features<br>PIC <sup>®</sup> Mid-Range Reference Manual (DS33023) | PIC16C712            | PIC16C716            |

|-----------------------------------------------------------------------|----------------------|----------------------|

| Operating Frequency                                                   | DC – 20 MHz          | DC – 20 MHz          |

| Resets (and Delays)                                                   | POR, BOR (PWRT, OST) | POR, BOR (PWRT, OST) |

| Program Memory (14-bit words)                                         | 1K                   | 2K                   |

| Data Memory (bytes)                                                   | 128                  | 128                  |

| Interrupts                                                            | 7                    | 7                    |

| I/O Ports                                                             | Ports A,B            | Ports A,B            |

| Timers                                                                | 3                    | 3                    |

| Capture/Compare/PWM modules                                           | 1                    | 1                    |

| 8-bit Analog-to-Digital Module                                        | 4 input channels     | 4 input channels     |

#### **PIC16C7XX FAMILY OF DEVICES**

|             |                                                                               | PIC16C710                           | PIC16C71            | PIC16C711                           | PIC16C712                           | PIC16C715                           | PIC16C716                           | PIC16C72A                  | PIC16C73B                      |

|-------------|-------------------------------------------------------------------------------|-------------------------------------|---------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|----------------------------|--------------------------------|

| Clock       | Maximum Frequency of Operation (MHz)                                          | 20                                  | 20                  | 20                                  | 20                                  | 20                                  | 20                                  | 20                         | 20                             |

| Memory      | EPROM Program<br>Memory<br>(x14 words)                                        | 512                                 | 1K                  | 1K                                  | 1K                                  | 2K                                  | 2K                                  | 2K                         | 4K                             |

|             | Data Memory (bytes)                                                           | 36                                  | 36                  | 68                                  | 128                                 | 128                                 | 128                                 | 128                        | 192                            |

|             | Timer Module(s)                                                               | TMR0                                | TMR0                | TMR0                                | TMR0<br>TMR1<br>TMR2                | TMR0                                | TMR0<br>TMR1<br>TMR2                | TMR0<br>TMR1<br>TMR2       | TMR0<br>TMR1<br>TMR2           |

| Peripherals | Capture/Compare/<br>PWM Module(s)                                             | _                                   | _                   | _                                   | 1                                   | _                                   | 1                                   | 1                          | 2                              |

|             | Serial Port(s)<br>(SPI <sup>TM</sup> /I <sup>2</sup> C <sup>TM</sup> , USART) | _                                   | _                   | _                                   | _                                   | _                                   | _                                   | SPI/I <sup>2</sup> C       | SPI/I <sup>2</sup> C,<br>USART |

|             | A/D Converter (8-bit)<br>Channels                                             | 4                                   | 4                   | 4                                   | 4                                   | 4                                   | 4                                   | 5                          | 5                              |

|             | Interrupt Sources                                                             | 4                                   | 4                   | 4                                   | 7                                   | 4                                   | 7                                   | 8                          | 11                             |

|             | I/O Pins                                                                      | 13                                  | 13                  | 13                                  | 13                                  | 13                                  | 13                                  | 22                         | 22                             |

|             | Voltage Range (Volts)                                                         | 2.5-6.0                             | 3.0-6.0             | 2.5-6.0                             | 2.5-5.5                             | 2.5-5.5                             | 2.5-5.5                             | 2.5-5.5                    | 2.5-5.5                        |

| Features    | In-Circuit Serial<br>Programming™                                             | Yes                                 | Yes                 | Yes                                 | Yes                                 | Yes                                 | Yes                                 | Yes                        | Yes                            |

|             | Brown-out Reset                                                               | Yes                                 | _                   | Yes                                 | Yes                                 | Yes                                 | Yes                                 | Yes                        | Yes                            |

|             | Packages                                                                      | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 28-pin SDIP,<br>SOIC, SSOP | 28-pin SDIP,<br>SOIC           |

#### 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and Peripheral Modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is give in Table 2-1. The Special Function Registers can be classified into two sets; core (CPU) and peripheral. Those registers associated with the core functions are described in detail in this section. Those related to the operation of the peripheral features are described in detail in that peripheral feature section.

TABLE 2-1: SPECIAL FUNCTION REGISTER SUMMARY

| Addr    | Name                    | Bit 7                                                                                     | Bit 6              | Bit 5         | Bit 4            | Bit 3         | Bit 2           | Bit 1         | Bit 0     | Value on:<br>POR,<br>BOR | Value on<br>all other<br>Resets (4) |

|---------|-------------------------|-------------------------------------------------------------------------------------------|--------------------|---------------|------------------|---------------|-----------------|---------------|-----------|--------------------------|-------------------------------------|

| Bank 0  |                         |                                                                                           |                    |               |                  |               |                 |               |           |                          |                                     |

| 00h     | INDF <sup>(1)</sup>     | Addressing                                                                                | this location      | uses conten   | ts of FSR to ac  | ddress data r | nemory (not     | a physical re | gister)   | 0000 0000                | 0000 0000                           |

| 01h     | TMR0                    | Timer0 Mod                                                                                | lule's Registe     | er            |                  |               |                 |               |           | xxxx xxxx                | uuuu uuuu                           |

| 02h     | PCL <sup>(1)</sup>      | Program Co                                                                                | ounter's (PC)      | Least Signif  | icant Byte       |               |                 |               |           | 0000 0000                | 0000 0000                           |

| 03h     | STATUS <sup>(1)</sup>   | IRP <sup>(4)</sup>                                                                        | RP1 <sup>(4)</sup> | RP0           | TO               | PD            | Z               | DC            | С         | rr01 1xxx                | rr0q quuu                           |

| 04h     | FSR <sup>(1)</sup>      | Indirect Data                                                                             | a Memory Ad        | dress Pointe  | er               |               |                 |               |           | xxxx xxxx                | uuuu uuuu                           |

| 05h     | PORTA <sup>(5,6)</sup>  | _                                                                                         | _                  | (7)           | PORTA Data       | Latch when    | written: POR    | TA pins wher  | n read    | xx xxxx                  | xu uuuu                             |

| 06h     | PORTB <sup>(5,6)</sup>  | PORTB Dat                                                                                 | a Latch whe        | n written: PC | RTB pins whe     | n read        |                 |               |           | xxxx xxxx                | uuuu uuuu                           |

| 07h     | DATACCP                 | (7)                                                                                       | (7)                | (7)           | (7)              | (7)           | DCCP            | (7)           | DT1CK     | xxxx xxxx                | xxxx xuxu                           |

| 08h-09h | _                       | Unimpleme                                                                                 | nted               |               |                  |               |                 |               |           | -                        | -                                   |

| 0Ah     | PCLATH <sup>(1,2)</sup> | _                                                                                         | _                  | _             | Write Buffer fo  | or the upper  | 5 bits of the F | Program Cou   | ınter     | 0 0000                   | 0 0000                              |

| 0Bh     | INTCON <sup>(1)</sup>   | GIE                                                                                       | PEIE               | TOIE          | INTE             | RBIE          | TOIF            | INTF          | RBIF      | 0000 000x                | 0000 000u                           |

| 0Ch     | PIR1                    | _                                                                                         | ADIF               | ı             | _                | _             | CCP1IF          | TMR2IF        | TMR1IF    | -0 0000                  | -0 0000                             |

| 0Dh     | -                       | Unimpleme                                                                                 | nted               |               |                  |               |                 |               |           | -                        | -                                   |

| 0Eh     | TMR1L                   | Holding Reg                                                                               | gister for the     | Least Signifi | cant Byte of th  | e 16-bit TMF  | R1 Register     |               |           | xxxx xxxx                | uuuu uuuu                           |

| 0Fh     | TMR1H                   | Holding Reg                                                                               | gister for the     | Most Signific | cant Byte of the | e 16-bit TMR  | 1 Register      |               |           | xxxx xxxx                | uuuu uuuu                           |

| 10h     | T1CON                   | _                                                                                         | -                  | T1CKPS1       | T1CKPS0          | T1OSCEN       | T1SYNC          | TMR1CS        | TMR10N    | 00 0000                  | uu uuuu                             |

| 11h     | TMR2                    | Timer2 Mod                                                                                | lule's Registe     | er            |                  |               |                 |               |           | 0000 0000                | 0000 0000                           |

| 12h     | T2CON                   | _                                                                                         | TOUTPS3            | TOUTPS2       | TOUTPS1          | TOUTPS0       | TMR2ON          | T2CKPS1       | T2CKPS0   | -000 0000                | -000 0000                           |

| 13h-14h |                         |                                                                                           |                    |               |                  |               |                 |               |           |                          |                                     |

| 15h     | CCPR1L                  | Capture/Co                                                                                | mpare/PWM          | Register1 (L  | SB)              |               |                 |               |           | xxxx xxxx                | uuuu uuuu                           |

| 16h     | CCPR1H                  | Capture/Compare/PWM Register1 (MSB)                                                       |                    |               |                  |               |                 | xxxx xxxx     | uuuu uuuu |                          |                                     |

| 17h     | CCP1CON                 | —         DC1B1         DC1B0         ССР1М3         ССР1М2         ССР1М1         ССР1М0 |                    |               |                  |               |                 |               | 00 0000   | 00 0000                  |                                     |

| 18h-1Dh | _                       | Unimplemented                                                                             |                    |               |                  |               |                 |               | -         | -                        |                                     |

| 1Eh     | ADRES                   | A/D Result                                                                                | Register           |               |                  |               |                 |               |           | xxxx xxxx                | uuuu uuuu                           |

| 1Fh     | ADCON0                  | ADCS1                                                                                     | ADCS0              | CHS2          | CHS1             | CHS0          | GO/DONE         |               | ADON      | 0000 00-0                | 0000 00-0                           |

**Legend:** x = unknown, u = unchanged, q = value depends on condition, — = unimplemented, read as '0', Shaded locations are unimplemented, read as '0'.

- Note 1: These registers can be addressed from either bank.

- 2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for PC<12:8> whose contents are transferred to the upper byte of the program counter.

- 3: Other (non Power-up) Resets include: external Reset through MCLR and the Watchdog Timer Reset.

- 4: The IRP and RP1 bits are reserved. Always maintain these bits clear.

- 5: On any device Reset, these pins are configured as inputs.

- 6: This is the value that will be in the port output latch.

- 7: Reserved bits; Do Not Use.

#### 2.2.2.3 INTCON Register

The INTCON Register is a readable and writable register which contains various enable and flag bits for the TMR0 register overflow, RB Port change and External RB0/INT pin interrupts.

Note:

Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### FIGURE 2-6: INTCON REGISTER (ADDRESS 0Bh, 8Bh)

| R/W-0   | R/W-0     | R/W-0                        | R/W-0       | R/W-0   | R/W-0              | R/W-0        | R/W-x         |                                       |

|---------|-----------|------------------------------|-------------|---------|--------------------|--------------|---------------|---------------------------------------|

| GIE     | PEIE      | T0IE                         | INTE        | RBIE    | T0IF               | INTF         | RBIF          | R = Readable bit                      |

| bit7    |           |                              |             |         |                    |              | bit0          | W = Writable bit                      |

|         |           |                              |             |         |                    |              |               | U = Unimplemented bit,<br>read as '0' |

|         |           |                              |             |         |                    |              |               | -n = Value at POR Reset               |

| bit 7:  | GIE: Glob | oal Interrup                 | ot Enable   | bit     |                    |              |               |                                       |

|         |           | les all unm                  |             | errupts |                    |              |               |                                       |

|         | 0 = Disab | les all inte                 | rrupts      |         |                    |              |               |                                       |

| bit 6:  |           | ripheral In                  |             |         |                    |              |               |                                       |

|         |           | les all unm                  |             |         | terrupts           |              |               |                                       |

|         | 0 = Disab | les all per                  | ipheral int | errupts |                    |              |               |                                       |

| bit 5:  |           | R0 Overflo                   |             |         | bit                |              |               |                                       |

|         |           | les the TM                   |             | •       |                    |              |               |                                       |

|         |           | les the TN                   |             | •       |                    |              |               |                                       |

| bit 4:  |           | 30/INT Ext                   |             |         |                    |              |               |                                       |

|         |           | les the RB                   |             |         | •                  |              |               |                                       |

|         |           | les the RE                   |             |         | •                  |              |               |                                       |

| bit 3:  |           | Port Cha                     |             |         |                    |              |               |                                       |

|         |           | les the RB<br>les the RE     | •           | •       | •                  |              |               |                                       |

| 1.11.0  |           |                              | •           | Ü       | •                  |              |               |                                       |

| bit 2:  |           | R0 Overflo                   |             |         |                    | d in aaftuur | \ra\          |                                       |

|         |           | ) register (<br>) register ( |             |         | st be cleare       | u in Soliwa  | ire)          |                                       |

| late A. |           | ŭ                            |             |         | - : 4              |              |               |                                       |

| bit 1:  |           | O/INT Exte                   |             |         | oit<br>urred (must | he cleare    | d in coftwa   | ro)                                   |

|         |           | RB0/INT ex                   |             | •       | •                  | De cicare    | a iii soitwai |                                       |

| bit 0:  |           | Port Cha                     |             | •       |                    |              |               |                                       |

| DIL U.  |           |                              |             |         | n<br>hanged stat   | e (must be   | e cleared in  | software)                             |

|         |           |                              |             |         | anged state        |              | 2.00.00 111   |                                       |

|         |           |                              | •           |         | -                  |              |               |                                       |

TABLE 5-1: TMR1 MODULE AND PORTB OPERATION

| TMR1<br>Module<br>Mode | Clock Source      | Control Bits                   | TMR1 Module Operation                                                                                                                                                                                                                                         | PORTB<2:1> Operation                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|------------------------|-------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Off                    | N/A               | T1CON =xx 0x00                 | Off                                                                                                                                                                                                                                                           | PORTB<2:1> function as normal I/O                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| Timer                  | Fosc/4            | T1CON =xx 0x01                 | TMR1 module uses the main oscillator as clock source. TMR1ON can turn on or turn off Timer1.                                                                                                                                                                  | PORTB<2:1> function as normal I/O                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| Counter                | External circuit  | T1CON =xx 0x11<br>TR1SCCP =x-1 | TMR1 module uses the external signal on the RB1/T1OSO/T1CKI pin as a clock source. TMR1ON can turn on or turn off Timer1. DT1CK can read the signal on the RB1/T1OSO/T1CKI pin.                                                                               | PORTB<2> functions as normal I/O. PORTB<1> always reads '0' when configured as input. If PORTB<1> is configured as output, reading PORTB<1> will read the data latch. Writing to PORTB<1> will always store the                                                                                                                                                                                                                                              |  |  |

|                        | Firmware          | T1CON =xx 0x11<br>TR1SCCP =x-0 | DATACCP<0> bit drives RB1/<br>T1OSO/T1CKI and produces<br>the TMR1 clock source.<br>TMR1ON can turn on or turn off<br>Timer1. The DATACCP<0> bit,<br>DT1CK, can read and write to<br>the RB1/T1OSO/T1CKI pin.                                                 | result in the data latch, but not to<br>the RB1/T1OSO/T1CKI pin. If<br>the TMR1CS bit is cleared<br>(TMR1 reverts to the timer<br>mode), then pin PORTB<1> will<br>be driven with the value in the<br>data latch.                                                                                                                                                                                                                                            |  |  |

|                        | Timer1 oscillator | T1CON =xx 1x11                 | RB1/T1OSO/T1CKI and RB2/T1OSI are configured as a 2 pin crystal oscillator. RB1/T1OSI/T1CKI is the clock input for TMR1. TMR1ON can turn on or turn off Timer1. DATACCP<1>bit, DT1CK, always reads '0' as input and can not write to the RB1/T1OSO/T1CK1 pin. | PORTB<2:1> always read '0' when configured as inputs. If PORTB<2:1> are configured as outputs, reading PORTB<2:1> will read the data latches. Writing to PORTB<2:1> will always store the result in the data latches, but not to the RB2/T1OSI and RB1/T1OSO/T1CKI pins. If the TMR1CS and T1OSCEN bits are cleared (TMR1 reverts to the timer mode and TMR1 oscillator is disabled), then pin PORTB<2:1> will be driven with the value in the data latches. |  |  |

**NOTES:**

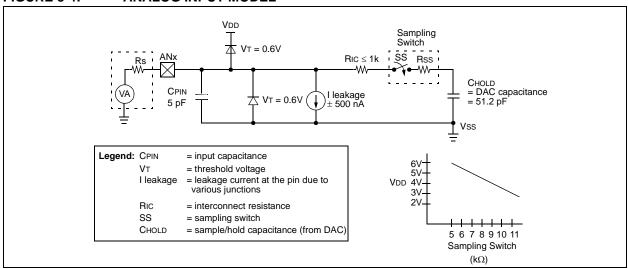

#### 8.1 A/D Acquisition Requirements

For the A/D converter to meet its specified accuracy, the Charge Holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 8-4. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD). The source impedance affects the offset voltage at the analog input (due to pin leakage current). The maximum recommended impedance for analog sources is 10  $k\Omega$ . After the analog input channel is selected (changed) this acquisition must be done before the conversion can be started.

To calculate the minimum acquisition time, TACQ, see the PIC<sup>®</sup> Mid-Range Reference Manual, (DS33023). This equation calculates the acquisition time to within 1/2 LSb error (512 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified accuracy.

When the conversion is started, the holding capacitor is disconnected from the input pin.

FIGURE 8-4: ANALOG INPUT MODEL

Note:

#### FIGURE 9-1: CONFIGURATION WORD

CP1 CP0 CP1 CP0 CP1 CP0 BODEN CP1 CP0 PWRTE WDTE FOSC1 FOSC0 Register: CONFIG Address2007h bit13 bit0 bit 13-8, 5-4: CP1:CP0: Code Protection bits (2) Code Protection for 2K Program memory (PIC16C716) 11 = Programming code protection off 10 = 0400h-07FFh code protected 01 = 0200h-07FFh code protected 00 = 0000h-07FFh code protected bit 13-8, 5-4: Code Protection for 1K Program memory bits (PIC16C712) 11 = Programming code protection off 10 = Programming code protection off 01 = 0200h-03FFh code-protected 00 = 0000h-03FFh code-protected bit 7: Unimplemented: Read as '1' bit 6: **BODEN**: Brown-out Reset Enable bit (1) 1 = BOR enabled 0 = BOR disabled **PWRTE**: Power-up Timer Enable bit (1) bit 3: 1 = PWRT disabled 0 = PWRT enabled bit 2: WDTE: Watchdog Timer Enable bit 1 = WDT enabled 0 = WDT disabled FOSC1:FOSC0: Oscillator Selection bits bit 1-0: 11 = RC oscillator 10 = HS oscillator 01 = XT oscillator 00 = LP oscillator Enabling Brown-out Reset automatically enables Power-up Timer (PWRT) regardless of the value of bit PWRTE. Note 1: Ensure the Power-up Timer is enabled anytime Brown-out Reset is enabled. 2: All of the CP1:CP0 pairs have to be given the same value to enable the code protection scheme listed.

#### 9.2 Oscillator Configurations

#### 9.2.1 OSCILLATOR TYPES

The PIC16CXXX can be operated in four different Oscillator modes. The user can program two Configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low-Power Crystal

- XT Crystal/Resonator

- HS High-Speed Crystal/Resonator

- RC Resistor/Capacitor

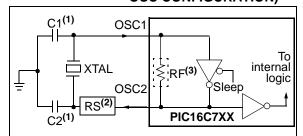

# 9.2.2 CRYSTAL OSCILLATOR/CERAMIC RESONATORS

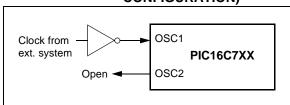

In XT, LP or HS modes, a crystal or ceramic resonator is connected to the OSC1/CLKIN and OSC2/CLKOUT pins to establish oscillation (Figure 9-2). The PIC16CXXX oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source to drive the OSC1/CLKIN pin (Figure 9-3).

FIGURE 9-2: CRYSTAL/CERAMIC

RESONATOR OPERATION

(HS, XT OR LP

OSC CONFIGURATION)

- Note 1: See Table 9-1 and Table 9-2 for recommended values of C1 and C2.

- 2: A series resistor (RS) may be required for AT strip cut crystals.

- **3:** RF varies with the crystal chosen.

FIGURE 9-3: EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC CONFIGURATION)

TABLE 9-1: CERAMIC RESONATORS

| Ranges Tested:                                 |                            |           |           |  |  |  |  |  |  |

|------------------------------------------------|----------------------------|-----------|-----------|--|--|--|--|--|--|

| Mode Freq OSC1 OSC2                            |                            |           |           |  |  |  |  |  |  |

| XT                                             | 455 kHz                    | 68-100 pF | 68-100 pF |  |  |  |  |  |  |

|                                                | 2.0 MHz                    | 15-68 pF  | 15-68 pF  |  |  |  |  |  |  |

|                                                | 4.0 MHz                    | 15-68 pF  | 15-68 pF  |  |  |  |  |  |  |

| HS                                             | 8.0 MHz                    | 10-68 pF  | 10-68 pF  |  |  |  |  |  |  |

|                                                | 16.0 MHz 10-22 pF 10-22 pF |           |           |  |  |  |  |  |  |

| These values are for design guidance only. See |                            |           |           |  |  |  |  |  |  |

| no                                             | tes at bottom of           | f page.   |           |  |  |  |  |  |  |

TABLE 9-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR

| Osc Type | Crystal<br>Freq | Cap. Range<br>C1 | Cap. Range<br>C2 |

|----------|-----------------|------------------|------------------|

| LP       | 32 kHz          | 33 pF            | 33 pF            |

|          | 200 kHz         | 15 pF            | 15 pF            |

| XT       | 200 kHz         | 47-68 pF         | 47-68 pF         |

|          | 1 MHz           | 15 pF            | 15 pF            |

|          | 4 MHz           | 15 pF            | 15 pF            |

| HS       | 4 MHz           | 15 pF            | 15 pF            |

|          | 8 MHz           | 15-33 pF         | 15-33 pF         |

|          | 20 MHz          | 15-33 pF         | 15-33 pF         |

These values are for design guidance only. See notes at bottom of page.

- **Note 1:** Recommended values of C1 and C2 are identical to the ranges tested (Table 9-1).

- 2: Higher capacitance increases the stability of the oscillator, but also increases the start-up time.

- 3: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- **4:** Rs may be required in HS mode, as well as XT mode to avoid overdriving crystals with low drive level specification.

#### 9.10.1 INT INTERRUPT

External interrupt on RB0/INT pin is edge triggered, either rising if bit INTEDG (OPTION\_REG<6>) is set, or falling if the INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, flag bit INTF (INTCON<1>) is set. This interrupt can be disabled by clearing enable bit INTE (INTCON<4>). Flag bit INTF must be cleared in software in the Interrupt Service Routine before re-enabling this interrupt. The INT interrupt can wake-up the processor from Sleep, if bit INTE was set prior to going into Sleep. The status of global interrupt enable bit GIE decides whether or not the processor branches to the interrupt vector following wake-up. See Section 9.13 "Power-down Mode (Sleep)" for details on Sleep mode.

#### 9.10.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit T0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit T0IE (INTCON<5>). (Section 4.0 "Timer0 Module")

#### 9.10.3 PORTB INTCON CHANGE

An input change on PORTB<7:4> sets flag bit RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit RBIE (INTCON<4>). (Section 3.2 "PORTB and the TRISB Register")

#### 9.11 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt, (i.e., W register and STATUS register). This will have to be implemented in software.

Example 9-1 stores and restores the W and STATUS registers. The register, W\_TEMP, must be defined in each bank and must be defined at the same offset from the bank base address (i.e., if W\_TEMP is defined at 0x20 in bank 0, it must also be defined at 0xA0 in bank 1).

#### The example:

- a) Stores the W register.

- b) Stores the STATUS register in bank 0.

- c) Stores the PCLATH register.

- Executes the Interrupt Service Routine code (User-generated).

- Restores the STATUS register (and bank select bit).

- Restores the W and PCLATH registers.

#### EXAMPLE 9-1: SAVING STATUS, W, AND PCLATH REGISTERS IN RAM

```

MOVWF

W TEMP

;Copy W to TEMP register, could be bank one or zero

SWAPF

STATUS, W

;Swap status to be saved into W

; bank 0, regardless of current bank, Clears IRP, RP1, RP0

CLRF

STATUS

MOVWF

STATUS_TEMP

; Save status to bank zero STATUS_TEMP register

PCLATH, W

MOVF

;Only required if using pages 1, 2 and/or 3

MOVWF

PCLATH TEMP

;Save PCLATH into W

CLRF

PCLATH

; Page zero, regardless of current page

STATUS, IRP

;Return to Bank 0

BCF

MOVF

FSR, W

;Copy FSR to W

MOVWF

FSR TEMP

; Copy FSR from W to FSR_TEMP

:(ISR)

PCLATH TEMP, W

MOVE

Restore PCLATH

; Move W into PCLATH

MOVWF

PCLATH

SWAPF

STATUS_TEMP,W

;Swap STATUS_TEMP register into W

; (sets bank to original state)

MOVWF

STATUS

; Move W into STATUS register

; Swap W TEMP

SWAPF

W TEMP, F

W_TEMP,W

;Swap W_TEMP into W

SWAPF

```

#### 9.12 Watchdog Timer (WDT)

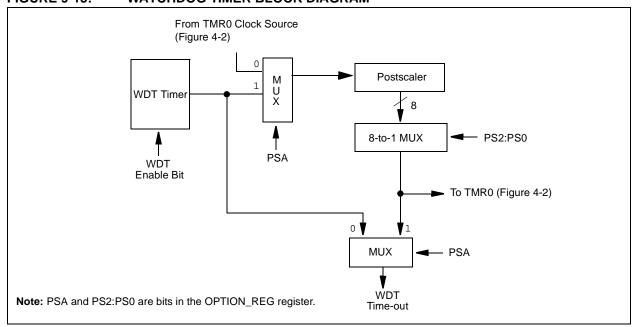

The Watchdog Timer is as a free running, on-chip, RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. That means that the WDT will run, even if the clock on the OSC1/CLKIN and OSC2/CLKOUT pins of the device have been stopped, for example, by execution of a SLEEP instruction.

During normal operation, a WDT Time-out generates a device Reset (Watchdog Timer Reset). If the device is in Sleep mode, a WDT Time-out causes the device to wake-up and continue with normal operation (Watchdog Timer Wake-up). The TO bit in the STATUS register will be cleared upon a Watchdog Timer Time-out.

The WDT can be permanently disabled by clearing Configuration bit WDTE (Section 9.1 "Configuration Bits").

WDT time-out period values may be found in the Electrical Specifications section under TWDT (parameter #31). Values for the WDT prescaler (actually a postscaler, but shared with the Timer0 prescaler) may be assigned using the OPTION\_REG register.

Note: The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device Reset condition.

When a CLRWDT instruction is executed and the prescaler is assigned to the WDT, the prescaler count will be cleared, but the prescaler assignment is not changed.

FIGURE 9-15: WATCHDOG TIMER BLOCK DIAGRAM

Note:

#### FIGURE 9-16: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address | Name         | Bits 13:8 | Bit 7 | Bit 6                | Bit 5 | Bit 4 | Bit 3                | Bit 2 | Bit 1 | Bit 0 |

|---------|--------------|-----------|-------|----------------------|-------|-------|----------------------|-------|-------|-------|

| 2007h   | Config. bits | (1)       | -     | BODEN <sup>(1)</sup> | CP1   | CP0   | PWRTE <sup>(1)</sup> | WDTE  | FOSC1 | FOSC0 |

| 81h     | OPTION_REG   | N/A       | RBPU  | INTEDG               | T0CS  | T0SE  | PSA                  | PS2   | PS1   | PS0   |

Legend: Shaded cells are not used by the Watchdog Timer.

Note 1: See Figure 9-1 for operation of these bits.

#### 10.0 INSTRUCTION SET SUMMARY

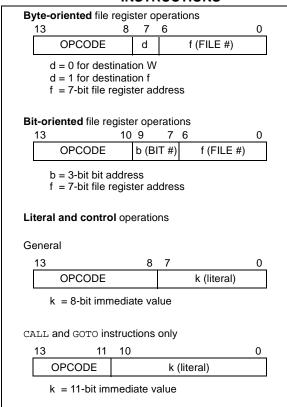

Each PIC16CXXX instruction is a 14-bit word divided into an OPCODE which specifies the instruction type and one or more operands which further specify the operation of the instruction. The PIC16CXXX instruction set summary in Table 10-2 lists **byte-oriented**, **bit-oriented**, and **literal and control** operations. Table 10-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven bit constant or literal value.

TABLE 10-1: OPCODE FIELD DESCRIPTIONS

| Field           | Description                                                                                                                                                        |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f               | Register file address (0x00 to 0x7F)                                                                                                                               |

| W               | Working register (accumulator)                                                                                                                                     |

| b               | Bit address within an 8-bit file register                                                                                                                          |

| k               | Literal field, constant data or label                                                                                                                              |

| x               | Don't care location (= 0 or 1) The assembler will generate code with x = 0. It is the recommended form of use for compatibility with all Microchip software tools. |

| d               | Destination select; d = 0: store result in W, d = 1: store result in file register f. Default is d = 1                                                             |

| PC              | Program Counter                                                                                                                                                    |

| TO              | Time-out bit                                                                                                                                                       |

| $\overline{PD}$ | Power-down bit                                                                                                                                                     |

| Z               | Zero bit                                                                                                                                                           |

| DC              | Digit Carry bit                                                                                                                                                    |

| С               | Carry bit                                                                                                                                                          |

The instruction set is highly orthogonal and is grouped into three basic categories:

- Byte-oriented operations

- · Bit-oriented operations

- Literal and control operations

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles with the second cycle executed as a NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu s$ . If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu s$ .

Table 10-2 lists the instructions recognized by the MPASM assembler.

Figure 10-1 shows the general formats that the instructions can have.

**Note:** To maintain upward compatibility with future PIC16CXXX products, <u>do not use</u> the OPTION and TRIS instructions.

All examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

FIGURE 10-1: GENERAL FORMAT FOR INSTRUCTIONS

A description of each instruction is available in the PIC<sup>®</sup> Mid-Range Reference Manual, (DS33023).

#### **AC (Timing) Characteristics** 12.4

#### 12.4.1 TIMING PARAMETER SYMBOLOGY

The timing parameter symbols have been created using one of the following formats:

- 1. TppS2ppS

| 2. TppS |                                      |     |                |

|---------|--------------------------------------|-----|----------------|

| T       |                                      |     |                |

| F       | Frequency                            | Т   | Time           |

| Lowerd  | ase letters (pp) and their meanings: |     |                |

| pp      |                                      |     |                |

| СС      | CCP1                                 | osc | OSC1           |

| ck      | CLKOUT                               | rd  | RD             |

| cs      | <del>CS</del>                        | rw  | RD or WR       |

| di      | SDI                                  | sc  | SCK            |

| do      | SDO                                  | SS  | SS             |

| dt      | Data in                              | tO  | TOCKI          |

| io      | I/O port                             | t1  | T1CKI          |

| mc      | MCLR                                 | wr  | WR             |

| Upperd  | ase letters and their meanings:      |     |                |

| S       |                                      |     |                |

| F       | Fall                                 | Р   | Period         |

| Н       | High                                 | R   | Rise           |

| I       | Invalid (High-impedance)             | V   | Valid          |

| L       | Low                                  | Z   | High-impedance |

#### 12.4.2 TIMING CONDITIONS

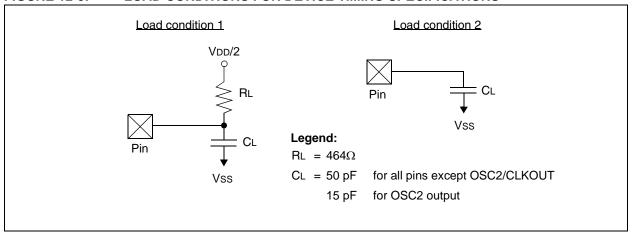

The temperature and voltages specified in Table 12-1 apply to all timing specifications, unless otherwise noted. Figure 12-3 specifies the load conditions for the timing specifications.

#### TABLE 12-1: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

Standard Operating Conditions (unless otherwise stated)

Operating temperature

0°C ≤ TA ≤ +70°C for commercial

-40°C ≤ TA ≤ +85°C for industrial

-40°C ≤ TA ≤ +125°C for extended

AC CHARACTERISTICS

Operating voltage VDD range as described in DC spec Section 12.1 "DC Characteristics:

PIC16C712/716-04 (Commercial, Industrial, Extended) PIC16C712/716-20 (Commercial, Industrial, Extended)" and Section 12.2 "DC Characteristics: PIC16LC712/716-04 (Commercial, Industrial)".

LC parts operate for commercial/industrial temp's only.

#### FIGURE 12-3: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

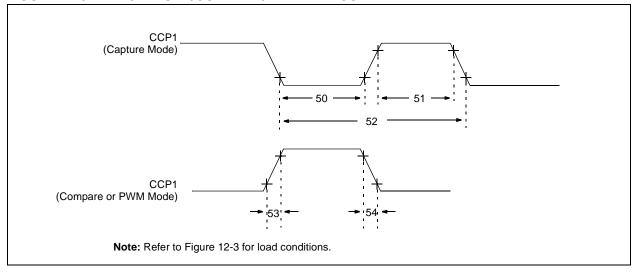

FIGURE 12-9: CAPTURE/COMPARE/PWM TIMINGS

TABLE 12-6: CAPTURE/COMPARE/PWM REQUIREMENTS

| Param<br>No. | Sym.                        | Characteristic        |                | Min            | Тур†           | Max | Units | Conditions |                                 |  |

|--------------|-----------------------------|-----------------------|----------------|----------------|----------------|-----|-------|------------|---------------------------------|--|

| 50*          | TccL                        | CCP1 input low        | No Prescaler   |                | 0.5Tcy + 20    | _   | _     | ns         |                                 |  |

|              |                             | time                  | With Prescaler | Standard       | 10             | _   | _     | ns         |                                 |  |

|              |                             |                       |                | Extended (LC)  | 20             | _   | _     | ns         |                                 |  |

| 51*          | 51* TccH CCP1 input high No |                       | No Prescaler   |                | 0.5Tcy + 20    | _   | _     | ns         |                                 |  |

|              | time                        |                       | time           | With Prescaler | Standard       | 10  | _     | _          | ns                              |  |

|              |                             |                       |                | Extended (LC)  | 20             | _   | _     | ns         |                                 |  |

| 52*          | TccP                        | CCP1 input period     |                |                | 3Tcy + 40<br>N | _   | _     | ns         | N = prescale value (1,4, or 16) |  |

| 53*          | TccR                        | CCP1 output rise ti   | me             | Standard       | _              | 10  | 25    | ns         |                                 |  |

|              |                             |                       |                |                | _              | 25  | 45    | ns         |                                 |  |

| 54*          | TccF                        | CCP1 output fall time |                | Standard       | _              | 10  | 25    | ns         |                                 |  |

|              |                             |                       |                | Extended (LC)  | _              | 25  | 45    | ns         |                                 |  |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

#### 13.2 **Package Details**

The following sections give the technical details of the packages.

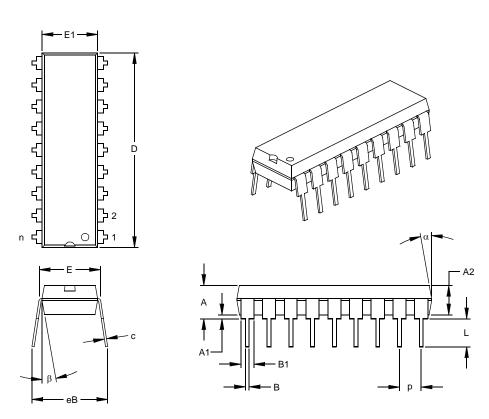

#### 18-Lead Plastic Dual In-line (P) – 300 mil (PDIP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units  | INCHES* |             |      | MILLIMETERS |       |       |

|----------------------------|--------|---------|-------------|------|-------------|-------|-------|

| Dimension                  | Limits | MIN     | MIN NOM MAX |      | MIN NOM     |       | MAX   |

| Number of Pins             | n      |         | 18          |      |             | 18    |       |

| Pitch                      | р      |         | .100        |      |             | 2.54  |       |

| Top to Seating Plane       | Α      | .140    | .155        | .170 | 3.56        | 3.94  | 4.32  |

| Molded Package Thickness   | A2     | .115    | .130        | .145 | 2.92        | 3.30  | 3.68  |

| Base to Seating Plane      | A1     | .015    |             |      | 0.38        |       |       |

| Shoulder to Shoulder Width | Е      | .300    | .313        | .325 | 7.62        | 7.94  | 8.26  |

| Molded Package Width       | E1     | .240    | .250        | .260 | 6.10        | 6.35  | 6.60  |

| Overall Length             | D      | .890    | .898        | .905 | 22.61       | 22.80 | 22.99 |

| Tip to Seating Plane       | L      | .125    | .130        | .135 | 3.18        | 3.30  | 3.43  |

| Lead Thickness             | С      | .008    | .012        | .015 | 0.20        | 0.29  | 0.38  |

| Upper Lead Width           | B1     | .045    | .058        | .070 | 1.14        | 1.46  | 1.78  |

| Lower Lead Width           | В      | .014    | .018        | .022 | 0.36        | 0.46  | 0.56  |

| Overall Row Spacing §      | eВ     | .310    | .370        | .430 | 7.87        | 9.40  | 10.92 |

| Mold Draft Angle Top       | α      | 5       | 10          | 15   | 5           | 10    | 15    |

| Mold Draft Angle Bottom    | β      | 5       | 10          | 15   | 5           | 10    | 15    |

<sup>\*</sup> Controlling Parameter

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010" (0.254mm) per side.

JEDEC Equivalent: MS-001

Drawing No. C04-007

<sup>§</sup> Significant Characteristic

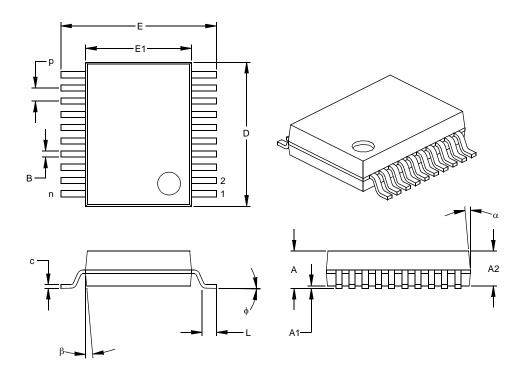

### 20-Lead Plastic Shrink Small Outline (SS) - 209 mil, 5.30 mm (SSOP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units | INCHES* |      |      | MILLIMETERS |        |        |

|--------------------------|-------|---------|------|------|-------------|--------|--------|

| Dimension Limits         |       | MIN     | MOM  | MAX  | MIN         | NOM    | MAX    |

| Number of Pins           | n     |         | 20   |      |             | 20     |        |

| Pitch                    | р     |         | .026 |      |             | 0.65   |        |

| Overall Height           | Α     | .068    | .073 | .078 | 1.73        | 1.85   | 1.98   |

| Molded Package Thickness | A2    | .064    | .068 | .072 | 1.63        | 1.73   | 1.83   |

| Standoff §               | A1    | .002    | .006 | .010 | 0.05        | 0.15   | 0.25   |

| Overall Width            | Е     | .299    | .309 | .322 | 7.59        | 7.85   | 8.18   |

| Molded Package Width     | E1    | .201    | .207 | .212 | 5.11        | 5.25   | 5.38   |

| Overall Length           | D     | .278    | .284 | .289 | 7.06        | 7.20   | 7.34   |

| Foot Length              | L     | .022    | .030 | .037 | 0.56        | 0.75   | 0.94   |

| Lead Thickness           | С     | .004    | .007 | .010 | 0.10        | 0.18   | 0.25   |

| Foot Angle               | ф     | 0       | 4    | 8    | 0.00        | 101.60 | 203.20 |

| Lead Width               | В     | .010    | .013 | .015 | 0.25        | 0.32   | 0.38   |

| Mold Draft Angle Top     | α     | 0       | 5    | 10   | 0           | 5      | 10     |

| Mold Draft Angle Bottom  | β     | 0       | 5    | 10   | 0           | 5      | 10     |

Controlling Parameter

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010" (0.254mm) per side.

JEDEC Equivalent: MO-150

Drawing No. C04-072

<sup>§</sup> Significant Characteristic

| Interrupt Sources                                         | . 51. 61  | XT                                                    | 53. | 58  |

|-----------------------------------------------------------|-----------|-------------------------------------------------------|-----|-----|

| A/D Conversion Complete                                   |           | Oscillator, Timer1                                    | ,   |     |

| Block Diagram                                             |           | Oscillator, WDT                                       |     |     |

| Capture Complete (CCP)                                    |           | Р                                                     |     |     |

| Compare Complete (CCP)                                    | 41        | •                                                     |     |     |

| Interrupt-on-Change (RB7:RB4)                             |           | Packaging                                             |     |     |

| RB0/INT Pin, External                                     |           | Details                                               |     |     |

| TMR0 Overflow                                             |           | Paging, Program Memory                                |     |     |

| TMR1 Overflow                                             |           | PCON Register                                         |     |     |

| TMR2 to PR2 Match                                         |           | BOR BitPOR Bit                                        |     |     |

| TMR2 to PR2 Match (PWM)                                   |           | PICSTART Plus Development Programmer                  |     |     |

| Interrupts, Context Saving During Interrupts, Enable Bits | 62        | PIE1 Register                                         |     |     |

| A/D Converter Enable (ADIE Bit)                           | 16        | ADIE Bit                                              |     |     |

| CCP1 Enable (CCP1IE Bit)                                  |           | CCP1IE Bit                                            |     |     |

| Global Interrupt Enable (GIE Bit)                         |           | TMR1IE Bit                                            |     |     |

| Interrupt-on-Change (RB7:RB4) Enable                      | ,         | TMR2IE Bit                                            |     |     |

| (RBIE Bit)                                                | 15, 62    | Pin Functions                                         |     |     |

| Peripheral Interrupt Enable (PEIE Bit)                    |           | MCLR/VPP                                              |     | . 6 |

| RB0/INT Enable (INTE Bit)                                 | 15        | RA0/AN0                                               |     | . 6 |

| TMR0 Overflow Enable (T0IE Bit)                           | 15        | RA1/AN1                                               |     |     |

| TMR1 Overflow Enable (TMR1IE Bit)                         |           | RA2/AN2                                               |     |     |

| TMR2 to PR2 Match Enable (TMR2IE Bit)                     | 16        | RA3/AN3/VREF                                          |     |     |

| Interrupts, Flag Bits                                     |           | RA4/T0CKI                                             |     |     |

| A/D Converter Flag (ADIF Bit)                             |           | RB0/INT                                               |     |     |

| CCP1 Flag (CCP1IF Bit)                                    | 7, 40, 41 | RB1<br>RB2                                            |     |     |

| Interrupt-on-Change (RB7:RB4) Flag                        | - 04 60   | RB3                                                   |     |     |

| (RBIF Bit)                                                |           | RB4                                                   |     |     |

| TMR0 Overflow Flag (T0IF Bit)                             |           | RB5                                                   |     |     |

| TMR1 Overflow Flag (TMR1IF Bit)                           |           | RB6                                                   |     |     |

| TMR2 to PR2 Match Flag (TMR2IF Bit)                       |           | RB7                                                   |     |     |

|                                                           |           | VDD                                                   |     |     |

| M                                                         |           | Vss                                                   |     | . 7 |

| Master Clear (MCLR)                                       |           | Pinout Descriptions                                   |     |     |

| MCLR Reset, Normal Operation 54                           | 4, 58, 59 | PIC16C712/716 Pinout Description                      |     | 6   |

| MCLR Reset, Sleep                                         |           | PIR1 Register                                         |     |     |

| MCLR Reset, Sleep                                         | 54, 58    | ADIF Bit                                              |     |     |

| Memory Organization                                       | 4.0       | CCP1IF Bit                                            |     |     |

| Data Memory                                               |           | TMR1IF Bit                                            |     |     |

| Program Memory Microchip Internet Web Site                |           | TMR2IF Bit<br>Pointer, FSR                            |     |     |

| MPLAB ASM30 Assembler, Linker, Librarian                  |           | POR. See Power-on Reset                               |     | 20  |

| MPLAB ICD 2 In-Circuit Debugger                           |           | PORTA                                                 |     |     |

| MPLAB ICE 2000 High-Performance Universal                 |           | Initialization                                        |     | 21  |

| In-Circuit Emulator                                       | 71        | PORTA Register                                        |     |     |

| MPLAB ICE 4000 High-Performance Universal                 |           | RA3:RA0 Port Pins                                     |     |     |

| In-Circuit Emulator                                       | 71        | RA4/T0CKI Pin                                         |     | 22  |

| MPLAB Integrated Development Environment Softwa           | are 69    | TRISA Register                                        | 12, | 21  |

| MPLAB PM3 Device Programmer                               | 71        | PORTB                                                 |     |     |

| MPLINK Object Linker/MPLIB Object Librarian               | 70        | Block Diagram of RB1/T1OSO/T1CKI Pin                  |     |     |

| 0                                                         |           | Block Diagram of RB2/T10SI Pin                        |     | 25  |

|                                                           | 67        | Block Diagram of RB3/CCP1 Pin                         |     |     |

| OPCODE Field Descriptions                                 |           | Initialization                                        |     |     |

| OPTION_REG Register INTEDG Bit                            |           | PORTB Register                                        |     |     |

| PS2:PS0 Bits                                              |           | Pull-up Enable (RBPU Bit)                             |     |     |

| PSA Bit                                                   |           | RB0/INT Edge Select (INTEDG Bit)RB0/INT Pin, External |     |     |

| RBPU Bit                                                  |           | RB3:RB0 Port Pins                                     |     |     |

| TOCS Bit                                                  |           | RB7:RB4 Interrupt-on-Change                           |     |     |

| TOSE Bit                                                  |           | RB7:RB4 Interrupt-on-Change Enable (RBIE Bit)         |     |     |

| Oscillator Configuration                                  |           | RB7:RB4 Interrupt-on-Change Flag                      | ,   |     |

| HS                                                        |           | (RBIF Bit)                                            | 24, | 62  |

| LP                                                        |           | RB7:RB4 Port Pins                                     |     |     |

| RC 53                                                     |           | TRISB Register                                        | 12, | 23  |

| Selection (FOSC1:FOSC0 Bits)                              | 52        |                                                       |     |     |

| 11, 31       |

|--------------|

|              |

| 36           |

|              |

| . 12, 36, 42 |

|              |

| 11, 36       |

| 11, 36       |

| 16           |

| 17           |

| 36, 37, 42   |

|              |

| 60           |

| 65           |

| 81           |

| 87           |

| 83           |

| 85           |

| 82           |

| 81           |

| 83           |

| 83           |

| 83           |

| 84           |

| 83           |

|              |

#### W Wake-up from Sleep ...... 51 Wake-up from Sleep ...... 64 Interrupts ...... 58, 59 MCLR Reset ...... 59 Timing Diagram ...... 65 WDT Reset ......59 Watchdog Timer (WDT)...... 51, 63 Block Diagram ...... 63 Enable (WDTE Bit) ...... 52, 63 Postscaler, See Postscaler, WDT Timing Diagram ...... 83 WDT Reset, Normal Operation ...... 54, 58, 59 WDT Reset, Sleep...... 54, 58, 59 WWW Address ...... 101

#### **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| TO:<br>RE:                                                                    | Technical Publications Manager Reader Response         | Total Pages Sent                       |  |  |  |  |

|-------------------------------------------------------------------------------|--------------------------------------------------------|----------------------------------------|--|--|--|--|

|                                                                               | n: Name                                                |                                        |  |  |  |  |

| 1 101                                                                         | Company                                                |                                        |  |  |  |  |

|                                                                               | Address                                                |                                        |  |  |  |  |

|                                                                               | City / State / ZIP / Country                           |                                        |  |  |  |  |

|                                                                               | Telephone: ()                                          | FAX: ()                                |  |  |  |  |

| App                                                                           | lication (optional):                                   |                                        |  |  |  |  |

| Wou                                                                           | ıld you like a reply?YN                                |                                        |  |  |  |  |

| Dev                                                                           | ice: PIC16C712/716                                     | Literature Number: DS41106C            |  |  |  |  |

| Que                                                                           | stions:                                                |                                        |  |  |  |  |

| 1.                                                                            | What are the best features of this document?           |                                        |  |  |  |  |

| •                                                                             |                                                        |                                        |  |  |  |  |

| 2.                                                                            | How does this document meet your hardware and soft     | tware development needs?               |  |  |  |  |

| ,                                                                             |                                                        |                                        |  |  |  |  |

| 3. Do you find the organization of this document easy to follow? If not, why? |                                                        |                                        |  |  |  |  |

| ,                                                                             |                                                        |                                        |  |  |  |  |

| 4.                                                                            | What additions to the document do you think would er   | hance the structure and subject?       |  |  |  |  |

|                                                                               |                                                        |                                        |  |  |  |  |

| ,                                                                             |                                                        |                                        |  |  |  |  |

| 5.                                                                            | What deletions from the document could be made with    | nout affecting the overall usefulness? |  |  |  |  |

| •                                                                             |                                                        |                                        |  |  |  |  |

| 6.                                                                            | Is there any incorrect or misleading information (what | and where)?                            |  |  |  |  |

| •                                                                             |                                                        |                                        |  |  |  |  |

| 7.                                                                            | How would you improve this document?                   |                                        |  |  |  |  |

|                                                                               |                                                        |                                        |  |  |  |  |

|                                                                               |                                                        |                                        |  |  |  |  |

| P | IC1 | 6C7 | 712 | <i> </i> 71 | 6 |

|---|-----|-----|-----|-------------|---|

|   |     |     |     |             |   |

|   | _   | _ | _ | $\sim$ |   |

|---|-----|---|---|--------|---|

| N | ( ) |   | _ | •      | - |

|   |     |   |   |        |   |