Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 13                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                 |

| Data Converters            | A/D 4x8b                                                                  |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 18-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c716-04e-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

| 1.0   | Device Overview                          | 5  |

|-------|------------------------------------------|----|

| 2.0   | Memory Organization                      | 9  |

| 3.0   | I/O Ports                                | 21 |

| 4.0   | I/O Ports<br>Timer0 Module               | 29 |

| 5.0   | Timer1 Module                            |    |

| 6.0   | Timer2 Module                            | 36 |

| 7.0   | Capture/Compare/PWM (CCP) Module(s)      | 39 |

| 8.0   | Analog-to-Digital Converter (A/D) Module | 45 |

| 9.0   | Special Features of the CPU              | 51 |

| 10.0  | Instruction Set Summary                  | 67 |

| 11.0  | Development Support.                     | 69 |

| 12.0  | Electrical Characteristics               | 73 |

| 13.0  | Packaging Information                    | 89 |

| Revis | ion History                              | 95 |

| Conv  | ersion Considerations                    | 95 |

| Migra | tion from Base-line to Mid-Range Devices | 95 |

| Index |                                          | 97 |

| On-Li | ne Support1                              | 01 |

| Read  | ne Support1<br>er Response               | 02 |

|       | SC712/716 Product Identification System  |    |

### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

### 2.2.2.3 INTCON Register

The INTCON Register is a readable and writable register which contains various enable and flag bits for the TMR0 register overflow, RB Port change and External RB0/INT pin interrupts. **Note:** Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

### FIGURE 2-6: INTCON REGISTER (ADDRESS 0Bh, 8Bh)

| R/W-0       | R/W-0                                                                                                                                                                      | R/W-0       | R/W-0                                      | R/W-0       | R/W-0        | R/W-0        | R/W-x        |                                                                                                                                                 |  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------------------------------------|-------------|--------------|--------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|

| GIE<br>bit7 | PEIE                                                                                                                                                                       | TOIE        | INTE                                       | RBIE        | TOIF         | INTF         | RBIF<br>bit0 | <ul> <li>R = Readable bit</li> <li>W = Writable bit</li> <li>U = Unimplemented bit,<br/>read as '0'</li> <li>-n = Value at POR Reset</li> </ul> |  |

| bit 7:      | 1 = Enabl                                                                                                                                                                  |             | pt Enable<br>nasked int<br>errupts         |             |              |              |              |                                                                                                                                                 |  |

| bit 6:      | 1 = Enabl                                                                                                                                                                  | les all unn | terrupt En<br>nasked pe<br>ipheral int     | ripheral in | terrupts     |              |              |                                                                                                                                                 |  |

| bit 5:      | 1 = Enabl                                                                                                                                                                  | les the TM  | ow Interruj<br>1R0 interru<br>/IR0 interru | ıpt         | bit          |              |              |                                                                                                                                                 |  |

| bit 4:      | <b>IINTE</b> : RB0/INT External Interrupt Enable bit<br>1 = Enables the RB0/INT external interrupt<br>0 = Disables the RB0/INT external interrupt                          |             |                                            |             |              |              |              |                                                                                                                                                 |  |

| bit 3:      | <b>RBIE</b> : RB Port Change Interrupt Enable bit<br>1 = Enables the RB port change interrupt<br>0 = Disables the RB port change interrupt                                 |             |                                            |             |              |              |              |                                                                                                                                                 |  |

| bit 2:      | 1 = TMR0                                                                                                                                                                   | ) register  | ow Interrup<br>has overflo<br>did not ove  | owed (mus   | st be cleare | ed in softwa | are)         |                                                                                                                                                 |  |

| bit 1:      | INTF: RB0/INT External Interrupt Flag bit<br>1 = The RB0/INT external interrupt occurred (must be cleared in software)<br>0 = The RB0/INT external interrupt did not occur |             |                                            |             |              |              |              |                                                                                                                                                 |  |

| bit 0:      | 1 = At lea                                                                                                                                                                 | st one of   |                                            | B4 pins cl  |              |              | e cleared in | software)                                                                                                                                       |  |

### 2.2.2.5 PIR1 Register

This register contains the individual flag bits for the peripheral interrupts.

# **Note:** Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

### FIGURE 2-8: PIR1 REGISTER (ADDRESS 0Ch)

| U-0      | R/W-0                                                                                                                                                                                                                                                                                                                                                                | U-0       | U-0       | R/W-0 | R/W-0        | R/W-0       | R/W-0          |                                       |  |  |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------|-------|--------------|-------------|----------------|---------------------------------------|--|--|

| <br>bit7 | ADIF                                                                                                                                                                                                                                                                                                                                                                 | _         | _         | _     | CCP1IF       | TMR2IF      | TMR1IF<br>bit0 | U = Unimplemented bit,<br>read as '0' |  |  |

| bit 7:   | Unimpler                                                                                                                                                                                                                                                                                                                                                             | nented: R | ead as '0 | ,     |              |             |                | -n = Value at POR Reset               |  |  |

| bit 6:   |                                                                                                                                                                                                                                                                                                                                                                      | D convers | ion compl |       | t be cleared | d in softwa | re)            |                                       |  |  |

| bit 5-3: | Unimpler                                                                                                                                                                                                                                                                                                                                                             | nented: R | ead as '0 | ,     |              |             |                |                                       |  |  |

| bit 2:   | CCP1IF: CCP1 Interrupt Flag bit<br><u>Capture Mode:</u><br>1 = A TMR1 register capture occurred (must be cleared in software)<br>0 = No TMR1 register capture occurred<br><u>Compare Mode:</u><br>1 = A TMR1 register compare match occurred (must be cleared in software)<br>0 = No TMR1 register compare match occurred<br><u>PWM Mode:</u><br>Unused in this mode |           |           |       |              |             |                |                                       |  |  |

| bit 1:   | <b>TMR2IF</b> : TMR2 to PR2 Match Interrupt Flag bit<br>1 = TMR2 to PR2 match occurred (must be cleared in software)<br>0 = No TMR2 to PR2 match occurred                                                                                                                                                                                                            |           |           |       |              |             |                |                                       |  |  |

| bit 0:   | TMR1IF: TMR1 Overflow Interrupt Flag bit<br>1 = TMR1 register overflowed (must be cleared in software)<br>0 = TMR1 register did not overflow                                                                                                                                                                                                                         |           |           |       |              |             |                |                                       |  |  |

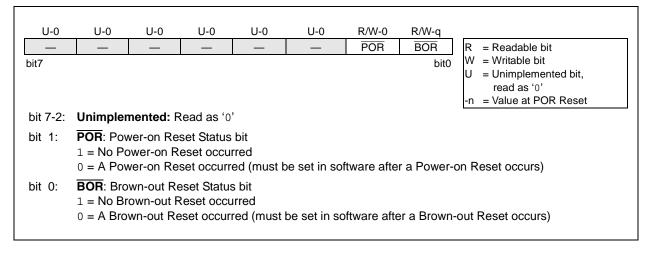

### 2.2.2.6 PCON Register

The Power Control (PCON) register contains a flag bit to allow differentiation between a Power-on Reset (POR) to an external MCLR Reset or WDT Reset. These devices contain an additional bit to differentiate a Brown-out Reset condition from a Power-on Reset condition. Note: If the BODEN Configuration bit is set, BOR is '1' on Power-on Reset. If the BODEN Configuration bit is clear, BOR is unknown on Power-on Reset. The BOR Status bit is a "don't care" and is

not necessarily predictable if the brown-out circuit is disabled (the BODEN Configuration bit is clear). BOR must then be set by the user and checked on subsequent resets to see if it is clear, indicating a brown-out has occurred.

### FIGURE 2-9: PCON REGISTER (ADDRESS 8Eh)

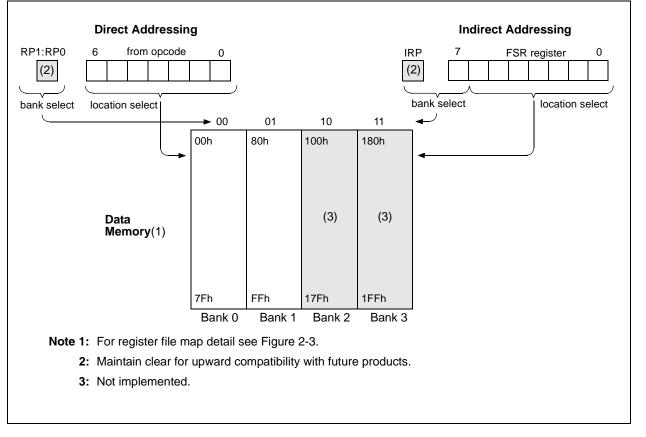

### 2.5 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a *pointer*). This is indirect addressing.

### EXAMPLE 2-1: INDIRECT ADDRESSING

- Register file 05 contains the value 10h

- Register file 06 contains the value 0Ah

- · Load the value 05 into the FSR register

- A read of the INDF register will return the value of 10h

- Increment the value of the FSR register by one (FSR = 06)

- A read of the INDR register now will return the value of 0Ah.

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF register indirectly results in a no-operation (although Status bits may be affected).

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 2-2.

### FIGURE 2-10: DIRECT/INDIRECT ADDRESSING

### 2: HOW TO CLEAR RAM USING INDIRECT ADDRESSING

| NEXT     | CLRF<br>INCF<br>BTFSS | FSR<br>INDF<br>FSR<br>FSR,4 | ;inc pointer<br>;all done?        |

|----------|-----------------------|-----------------------------|-----------------------------------|

| CONTINUE | GOTO<br>:             | NEXT                        | ;NO, clear next<br>;YES, continue |

An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 2-10. However, IRP is not used in the PIC16C712/716.

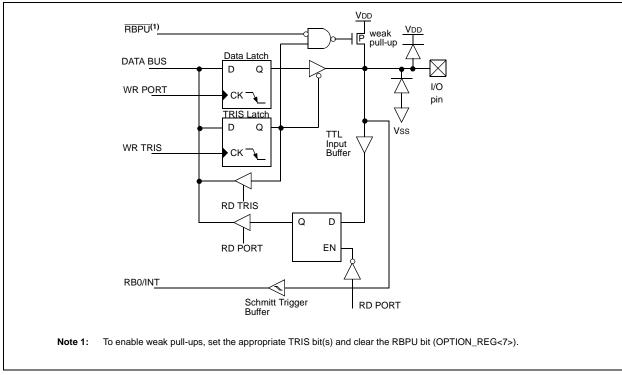

### 3.2 PORTB and the TRISB Register

PORTB is an 8-bit wide bidirectional port. The corresponding data direction register is TRISB. Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input, (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output, (i.e., put the contents of the output latch on the selected pin).

| BCF   | STATUS, RPO | i                       |

|-------|-------------|-------------------------|

| CLRF  | PORTB       | ; Initialize PORTB by   |

|       |             | ; clearing output       |

|       |             | ; data latches          |

| BSF   | STATUS, RPO | ; Select Bank 1         |

| MOVLW | 0xCF        | ; Value used to         |

|       |             | ; initialize data       |

|       |             | ; direction             |

| MOVWF | TRISB       | ; Set RB<3:0> as inputs |

|       |             | ; RB<5:4> as outputs    |

|       |             | ; RB<7:6> as inputs     |

|       |             |                         |

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit RBPU (OPTION\_REG<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

### FIGURE 3-3: BLOCK DIAGRAM OF RB0 PIN

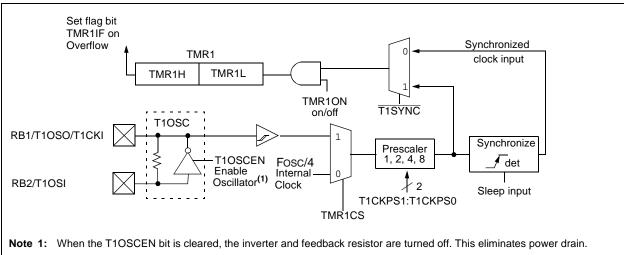

### 5.2 Timer1 Module and PORTB Operation

When Timer1 is configured as timer running from the main oscillator, PORTB<2:1> operate as normal I/O lines. When Timer1 is configured to function as a counter however, the clock source selection may affect the operation of PORTB<2:1>. Multiplexing details of the Timer1 clock selection on PORTB are shown in Figure 3-4 and Figure 3-5.

The clock source for Timer1 in the Counter mode can be from one of the following:

- 1. External circuit connected to the RB1/T1OSO/ T1CKI pin

- 2. Firmware controlled DATACCP<0> bit, DT1CKI

- 3. Timer1 oscillator

Table 5-1 shows the details of Timer1 mode selections, control bit settings, TMR1 and PORTB operations.

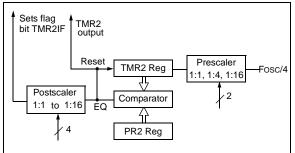

### 6.0 TIMER2 MODULE

The Timer2 module timer has the following features:

- 8-bit timer (TMR2 register)

- 8-bit period register (PR2)

- Readable and writable (both registers)

- Software programmable prescaler (1:1, 1:4, 1:16)

- Software programmable postscaler (1:1 to 1:16)

- Interrupt on TMR2 match of PR2

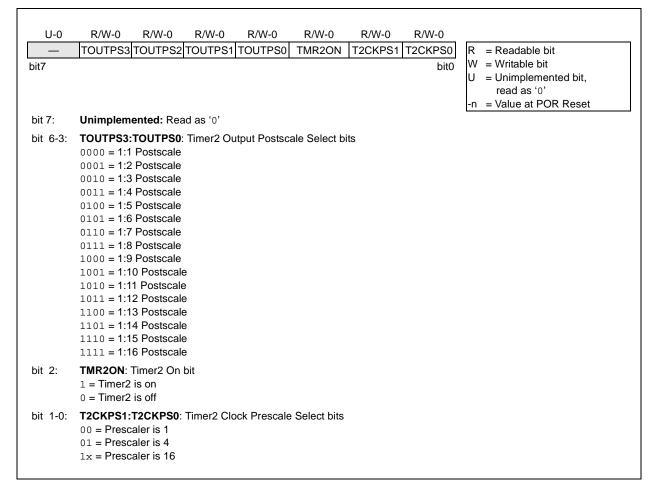

Timer2 has a control register, shown in Figure 6-1. Timer2 can be shut off by clearing control bit TMR2ON (T2CON<2>) to minimize power consumption.

Figure 6-2 is a simplified block diagram of the Timer2 module.

Additional information on timer modules is available in the PIC<sup>®</sup> Mid-Range Reference Manual, (DS33023).

### FIGURE 6-1: T2CON: TIMER2 CONTROL REGISTER (ADDRESS 12h)

### FIGURE 6-2: TIMER2 BLOCK DIAGRAM

# PIC16C712/716

NOTES:

### 8.4 A/D Conversions

| Note: | The GO/DONE bit should NOT be set in        |

|-------|---------------------------------------------|

|       | the same instruction that turns on the A/D. |

### 8.5 Use of the CCP Trigger

An A/D conversion can be started by the "Special Event Trigger" of the CCP1 module. This requires that the CCP1M3:CCP1M0 bits (CCP1CON<3:0>) be programmed as 1011 and that the A/D module is enabled (ADON bit is set). When the trigger occurs, the GO/DONE bit will be set, starting the A/D conversion, and the Timer1 counter will be reset to zero. Timer1 is reset to automatically repeat the A/D acquisition period with minimal software overhead (moving the ADRES to the desired location). The appropriate analog input channel must be selected and the minimum acquisition done before the "Special Event Trigger" sets the GO/ DONE bit (starts a conversion).

If the A/D module is not enabled (ADON is cleared), then the "Special Event Trigger" will be ignored by the A/D module, but will still reset the Timer1 counter.

| Address | Name   | Bit 7    | Bit 6       | Bit 5 | Bit 4                         | Bit 3 | Bit 2   | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on all other Resets |

|---------|--------|----------|-------------|-------|-------------------------------|-------|---------|--------|--------|-------------------------|---------------------------|

| 05h     | PORTA  |          | _           | (1)   | RA4                           | RA3   | RA2     | RA1    | RA0    | xx xxxx                 | xu uuuu                   |

| 0Bh,8Bh | INTCON | GIE      | PEIE        | TOIE  | INTE                          | RBIE  | TOIF    | INTF   | RBIF   | 0000 000x               | 0000 000u                 |

| 0Ch     | PIR1   | _        | ADIF        | _     | —                             | —     | CCP1IF  | TMR2IF | TMR1IF | -0000                   | -0000                     |

| 1Eh     | ADRES  | A/D Resu | ult Registe | er    |                               |       |         |        |        | xxxx xxxx               | uuuu uuuu                 |

| 1Fh     | ADCON0 | ADCS1    | ADCS0       | CHS2  | CHS1                          | CHS0  | GO/DONE | _      | ADON   | 0000 00-0               | 0000 00-0                 |

| 85h     | TRISA  | _        | _           | (1)   | PORTA Data Direction Register |       |         |        |        | 1 1111                  | 1 1111                    |

| 8Ch     | PIE1   | _        | ADIE        | _     | —                             | —     | CCP1IE  | TMR2IE | TMR1IE | -0000                   | -0 0000                   |

| 9Fh     | ADCON1 |          | _           | _     | _                             | _     | PCFG2   | PCFG1  | PCFG0  | 000                     | 000                       |

TABLE 8-2: SUMMARY OF A/D REGISTERS

**Legend:** x = unknown, u = unchanged, — = unimplemented read as '0'. Shaded cells are not used for A/D conversion. **Note 1:** Reserved bits: Do Not Use.

DS41106C-page 50

# PIC16C712/716

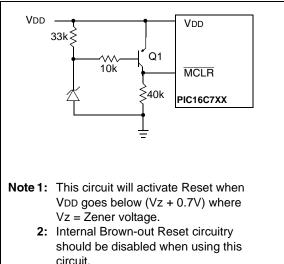

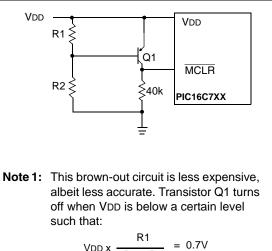

**EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2**

$$\frac{R1}{R1 + R2} = 0$$

- 2: Internal Brown-out Reset should be disabled when using this circuit.

- 3: Resistors should be adjusted for the characteristics of the transistor.

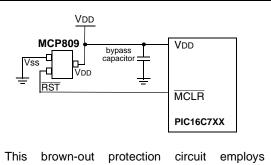

### **FIGURE 9-10:** EXTERNAL BROWN-OUT **PROTECTION CIRCUIT 3**

Microchip Technology's MCP809 microcontroller supervisor. The MCP8XX and MCP1XX families of supervisors provide push-pull and open collector outputs with both high and low active Reset pins. There are 7 different trip point selections to accommodate 5V and 3V systems

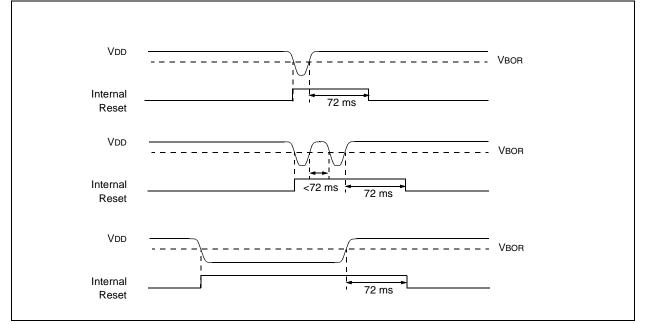

#### 9.8 **Time-out Sequence**

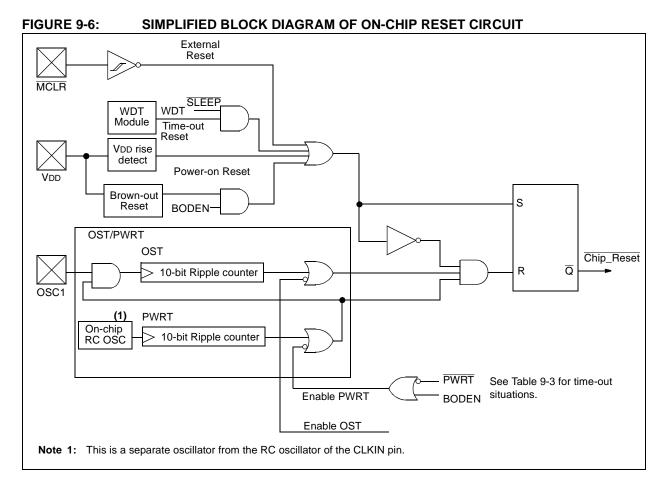

On power-up the time-out sequence is as follows: First PWRT time-out is invoked after the POR time delay has expired. Then OST is activated. The total time-out will vary based on oscillator configuration and the status of the PWRT. For example, in RC mode with the PWRT disabled, there will be no time-out at all. Figure 9-11, Figure 9-12, and Figure 9-13 depict time-out sequences on power-up.

Since the time-outs occur from the POR pulse, if MCLR is kept low long enough, the time-outs will expire. Then bringing MCLR high will begin execution immediately (Figure 9-13). This is useful for testing purposes or to synchronize more than one PIC16CXXX device operating in parallel.

Table 9-5 shows the Reset conditions for some Special Function Registers, while Table 9-6 shows the Reset conditions for all the registers.

### 9.9 Power Control/Status Register (PCON)

The Power Control/Status Register, PCON has two bits.

Bit 0 is Brown-out Reset Status bit,  $\overline{\text{BOR}}$ . If the BODEN Configuration bit is set,  $\overline{\text{BOR}}$  is '1' on Power-on Reset. If the BODEN Configuration bit is clear,  $\overline{\text{BOR}}$  is unknown on Power-on Reset. The BOR Status bit is a "don't care" and is not necessarily predictable if the brown-out circuit is disabled (the BODEN Configuration bit is clear). BOR must then be set by the user and checked on subsequent Resets to see if it is clear, indicating a brown-out has occurred.

Bit 1 is  $\overrightarrow{\text{POR}}$  (Power-on Reset Status bit). It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

### TABLE 9-3:TIME-OUT IN VARIOUS SITUATIONS

| Oscillator Configuration | Power              | -up      | Brown-out        | Wake-up from |  |

|--------------------------|--------------------|----------|------------------|--------------|--|

| Oscillator Configuration | PWRTE = 0PWRTE = 1 |          | Brown-out        | Sleep        |  |

| XT, HS, LP               | 72 ms + 1024Tosc   | 1024Tosc | 72 ms + 1024Tosc | 1024Tosc     |  |

| RC                       | 72 ms              | _        | 72 ms            | —            |  |

### TABLE 9-4: STATUS BITS AND THEIR SIGNIFICANCE

| POR | BOR | TO | PD |                                                         |

|-----|-----|----|----|---------------------------------------------------------|

| 0   | x   | 1  | 1  | Power-on Reset                                          |

| 0   | x   | 0  | x  | Illegal, TO is set on POR                               |

| 0   | x   | x  | 0  | Illegal, PD is set on POR                               |

| 1   | 0   | 1  | 1  | Brown-out Reset                                         |

| 1   | 1   | 0  | 1  | WDT Reset                                               |

| 1   | 1   | 0  | 0  | WDT Wake-up                                             |

| 1   | 1   | u  | u  | MCLR Reset during normal operation                      |

| 1   | 1   | 1  | 0  | MCLR Reset during Sleep or interrupt wake-up from Sleep |

### TABLE 9-5: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uu               |

| MCLR Reset during Sleep            | 000h                  | 0001 Ouuu          | uu               |

| WDT Reset                          | 000h                  | 0000 luuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 Ouuu          | uu               |

| Brown-out Reset                    | 000h                  | 0001 luuu          | u0               |

| Interrupt wake-up from Sleep       | PC + 1 <sup>(1)</sup> | uuul Ouuu          | uu               |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit read as '0'.

Note 1: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

| Register             | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset | Wake-up via WDT or<br>Interrupt |

|----------------------|------------------------------------|--------------------------|---------------------------------|

| W                    | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| INDF                 | N/A                                | N/A                      | N/A                             |

| TMR0                 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| PCL                  | 0000h                              | 0000h                    | PC + 1 <sup>(2)</sup>           |

| STATUS               | 0001 1xxx                          | 000q quuu <b>(3)</b>     | uuuq quuu <b>(3)</b>            |

| FSR                  | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| PORTA <sup>(4)</sup> | 0x 0000                            | xx xxxx                  | xu uuuu                         |

| PORTB <sup>(5)</sup> | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| DATACCP              | x-x                                | u-u                      | u-u                             |

| PCLATH               | 0 0000                             | 0 0000                   | u uuuu                          |

| INTCON               | 0000 -00x                          | 0000 -00u                | uuuu –uuu <b>(1)</b>            |

|                      | 0000                               | 0000                     | uuuu <b>(1)</b>                 |

| PIR1                 | -0 0000                            | -0 0000                  | -u uuuu <b>(1)</b>              |

| TMR1L                | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| TMR1H                | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| T1CON                | 00 0000                            | uu uuuu                  | uu uuuu                         |

| TMR2                 | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| T2CON                | -000 0000                          | -000 0000                | -uuu uuuu                       |

| CCPR1L               | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| CCPR1H               | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| CCP1CON              | 00 0000                            | 00 0000                  | uu uuuu                         |

| ADRES                | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |

| ADCON0               | 0000 00-0                          | 0000 00-0                | uuuu uu-u                       |

| OPTION_REG           | 1111 1111                          | 1111 1111                | นนนน นนนน                       |

| TRISA                | 11 1111                            | 11 1111                  | uu uuuu                         |

| TRISB                | 1111 1111                          | 1111 1111                | uuuu uuuu                       |

| TRISCCP              | xxxx x1x1                          | xxxx x1x1                | xxxx xuxu                       |

|                      | 0000                               | 0000                     | uuuu                            |

| PIE1                 | -0 0000                            | -0 0000                  | -u uuuu                         |

| PCON                 | 0q                                 | uq                       | uq                              |

| PR2                  | 1111 1111                          | 1111 1111                | 1111 1111                       |

| ADCON1               | 000                                | 000                      | uuu                             |

### TABLE 9-6: INITIALIZATION CONDITIONS FOR ALL REGISTERS OF THE PIC16C712/716

**Legend:** u = unchanged, x = unknown, -= unimplemented bit, read as '0', q = value depends on condition

Note 1: One or more bits in INTCON and/or PIR1 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

**3:** See Table 9-5 for Reset value for specific condition.

4: On any device Reset, these pins are configured as inputs.

5: This is the value that will be in the port output latch.

### 9.10 Interrupts

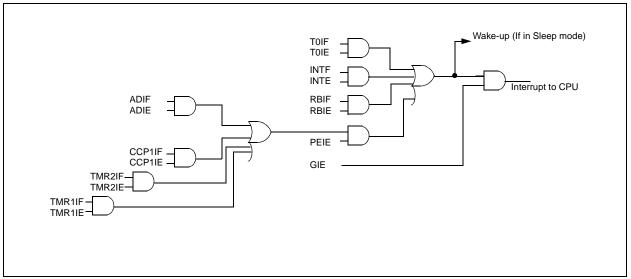

The PIC16C712/716 devices have up to 7 sources of interrupt. The Interrupt Control Register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

| Note: | Individual interrupt flag bits are set regard- |

|-------|------------------------------------------------|

|       | less of the status of their corresponding      |

|       | mask bit or the GIE bit.                       |

A Global Interrupt Enable bit, GIE (INTCON<7>) enables (if set) all unmasked interrupts or disables (if cleared) all interrupts. When bit GIE is enabled, and an interrupt's flag bit and mask bit are set, the interrupt will vector immediately. Individual interrupts can be disabled through their corresponding enable bits in various registers. Individual interrupt bits are set, regardless of the status of the GIE bit. The GIE bit is cleared on Reset.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine, as well as sets the GIE bit, which re-enables interrupts.

The RB0/INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flags are contained in the Special Function Registers, PIR1 and PIR2. The corresponding interrupt enable bits are contained in Special Function Registers, PIE1 and PIE2, and the peripheral interrupt enable bit is contained in Special Function Register, INTCON.

When an interrupt is responded to, the GIE bit is cleared to disable any further interrupt, the return address is pushed onto the stack and the PC is loaded with 0004h. Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs. The latency is the same for one or two cycle instructions. Individual interrupt flag bits are set, regardless of the status of their corresponding mask bit or the GIE bit.

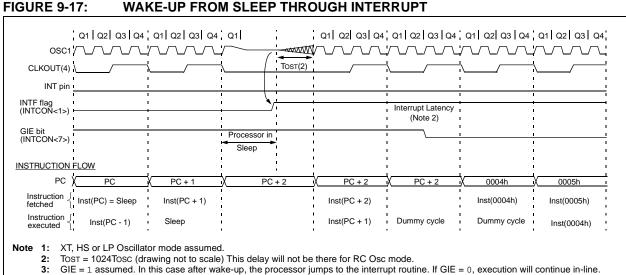

### FIGURE 9-14: INTERRUPT LOGIC

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

#### WAKE-UP USING INTERRUPTS 9.13.2

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

· If the interrupt occurs before the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the  $\overline{TO}$  bit will not be set and  $\overline{PD}$  bits will not be cleared.

• If the interrupt occurs during or after the execution of a SLEEP instruction, the device will immediately wake-up from Sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the  $\overline{PD}$  bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a **SLEEP** instruction.

4:

CLKOUT is not available in these osc modes, but shown here for timing reference.

### 9.14 Program Verification/Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

| Note: | Microchip                    | does | not | recommend | code |  |  |  |

|-------|------------------------------|------|-----|-----------|------|--|--|--|

|       | protecting windowed devices. |      |     |           |      |  |  |  |

#### **ID** Locations 9.15

Four memory locations (2000h-2003h) are designated as ID locations where the user can store checksum or other code-identification numbers. These locations are not accessible during normal execution, but are readable and writable during Program/Verify. It is recommended that only the 4 Least Significant bits of the ID location are used.

For ROM devices, these values are submitted along with the ROM code.

# PIC16C712/716

### TABLE 10-2: PIC16CXXX INSTRUCTION SET

| Mnemonic,<br>Operands |        | Description                  | Cycles | 14-Bit Opcode |      |      |      | Status   | Notes |

|-----------------------|--------|------------------------------|--------|---------------|------|------|------|----------|-------|

|                       |        |                              |        | MSb           |      |      | LSb  | Affected |       |

| BYTE-ORIE             | NTED   | FILE REGISTER OPERATIONS     |        |               |      |      |      |          |       |

| ADDWF                 | f, d   | Add W and f                  | 1      | 00            | 0111 | dfff | ffff | C,DC,Z   | 1,2   |

| ANDWF                 | f, d   | AND W with f                 | 1      | 00            | 0101 | dfff | ffff | Z        | 1,2   |

| CLRF                  | f      | Clear f                      | 1      | 00            | 0001 | lfff | ffff | Z        | 2     |

| CLRW                  | -      | Clear W                      | 1      | 00            | 0001 | 0000 | 0011 | Z        |       |

| COMF                  | f, d   | Complement f                 | 1      | 00            | 1001 | dfff | ffff | Z        | 1,2   |

| DECF                  | f, d   | Decrement f                  | 1      | 00            | 0011 | dfff | ffff | Z        | 1,2   |

| DECFSZ                | f, d   | Decrement f, Skip if 0       | 1(2)   | 00            | 1011 | dfff | ffff |          | 1,2,3 |

| INCF                  | f, d   | Increment f                  | 1      | 00            | 1010 | dfff | ffff | Z        | 1,2   |

| INCFSZ                | f, d   | Increment f, Skip if 0       | 1(2)   | 00            | 1111 | dfff | ffff |          | 1,2,3 |

| IORWF                 | f, d   | Inclusive OR W with f        | 1      | 00            | 0100 | dfff | ffff | Z        | 1,2   |

| MOVF                  | f, d   | Move f                       | 1      | 00            | 1000 | dfff | ffff | Z        | 1,2   |

| MOVWF                 | f      | Move W to f                  | 1      | 00            | 0000 | lfff | ffff |          |       |

| NOP                   | -      | No Operation                 | 1      | 00            | 0000 | 0xx0 | 0000 |          |       |

| RLF                   | f, d   | Rotate Left f through Carry  | 1      | 00            | 1101 | dfff | ffff | С        | 1,2   |

| RRF                   | f, d   | Rotate Right f through Carry | 1      | 00            | 1100 | dfff | ffff | С        | 1,2   |

| SUBWF                 | f, d   | Subtract W from f            | 1      | 00            | 0010 | dfff | ffff | C,DC,Z   | 1,2   |

| SWAPF                 | f, d   | Swap nibbles in f            | 1      | 00            | 1110 | dfff | ffff |          | 1,2   |

| XORWF                 | f, d   | Exclusive OR W with f        | 1      | 00            | 0110 | dfff | ffff | Z        | 1,2   |

| BIT-ORIEN             | ed fil | E REGISTER OPERATIONS        | 1      |               |      |      |      |          |       |

| BCF                   | f, b   | Bit Clear f                  | 1      | 01            | 00bb | bfff | ffff |          | 1,2   |

| BSF                   | f, b   | Bit Set f                    | 1      | 01            | 01bb | bfff | ffff |          | 1,2   |

| BTFSC                 | f, b   | Bit Test f, Skip if Clear    | 1 (2)  | 01            | 10bb | bfff | ffff |          | 3     |

| BTFSS                 | f, b   | Bit Test f, Skip if Set      | 1 (2)  | 01            | 11bb | bfff | ffff |          | 3     |

| LITERAL A             | ND CO  | NTROL OPERATIONS             |        | 1             |      |      |      | I        |       |

| ADDLW                 | k      | Add literal and W            | 1      | 11            | 111x | kkkk | kkkk | C,DC,Z   |       |

| ANDLW                 | k      | AND literal with W           | 1      | 11            | 1001 | kkkk | kkkk | Z        |       |

| CALL                  | k      | Call subroutine              | 2      | 10            | 0kkk | kkkk | kkkk |          |       |

| CLRWDT                | -      | Clear Watchdog Timer         | 1      | 00            | 0000 | 0110 | 0100 | TO,PD    |       |

| GOTO                  | k      | Go to address                | 2      | 10            | 1kkk | kkkk | kkkk |          |       |

| IORLW                 | k      | Inclusive OR literal with W  | 1      | 11            | 1000 | kkkk | kkkk | Z        |       |

| MOVLW                 | k      | Move literal to W            | 1      | 11            | 00xx | kkkk | kkkk |          |       |

| RETFIE                | -      | Return from interrupt        | 2      | 00            | 0000 | 0000 | 1001 |          |       |

| RETLW                 | k      | Return with literal in W     | 2      | 11            | 01xx | kkkk | kkkk |          |       |

| RETURN                | -      | Return from Subroutine       | 2      | 00            | 0000 | 0000 | 1000 |          |       |

| SLEEP                 | -      | Go into standby mode         | 1      | 00            | 0000 | 0110 | 0011 | TO,PD    |       |

| SUBLW                 | k      | Subtract W from literal      | 1      | 11            | 110x |      | kkkk | C,DC,Z   |       |

|                       |        |                              | 1      |               |      |      |      | , -, -   |       |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

**3:** If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

## 12.0 ELECTRICAL CHARACTERISTICS

### Absolute Maximum Ratings (†)

| Ambient temperature under bias                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 55°C to +125°C                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| Ambient temperature under bias<br>Storage temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 65°C to +150°C                                          |

| Voltage on any pin with respect to Vss (except VDD, MCLR, and RA4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0.3V to (VDD + 0.3V)                                    |

| Voltage on VDD with respect to Vss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0.3V to +7.5V                                           |

| Voltage on MCLR with respect to Vss (Note 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0V to +13.25V                                           |

| Voltage on RA4 with respect to Vss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0V to +8.5V                                             |

| Total power dissipation (Note 1) (PDIP and SOIC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1.0W                                                    |

| Total power dissipation (Note 1) (SSOP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                         |

| Maximum current out of Vss pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 300 mA                                                  |

| Maximum current into VDD pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                         |

| Input clamp current, Iк (VI < 0 or VI > VDD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ±20 mA                                                  |

| Output clamp current, loк (Vo < 0 or Vo > VDD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ±20 mA                                                  |

| Maximum output current sunk by any I/O pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                         |

| Maximum output current sourced by any I/O pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 25 mA                                                   |