Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2010                       |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                  |

| Data Converters            | A/D 4x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 18-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c716-04i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1-1: P       | IC16C712/71 |         | DESCRIP  |                     |                                                                 |

|--------------------|-------------|---------|----------|---------------------|-----------------------------------------------------------------|

| Pin                | PIC16C      | 712/716 | Pin      | Buffer              |                                                                 |

| Name               | DIP, SOIC   | SSOP    | Туре     | Туре                | Description                                                     |

| MCLR/VPP           | 4           | 4       |          |                     |                                                                 |

| MCLR               |             |         | I        | ST                  | Master clear (Reset) input. This pin is                         |

| VPP                |             |         | Р        |                     | an active low Reset to the device.<br>Programming voltage input |

| OSC1/CLKIN         | 16          | 18      | Г        |                     |                                                                 |

| OSCI/CLKIN<br>OSCI | 10          | 10      | 1        | ST                  | Oscillator crystal input or external clock                      |

| 0001               |             |         |          | 01                  | source input. ST buffer when config-                            |

|                    |             |         |          |                     | ured in RC mode. CMOS otherwise.                                |

| CLKIN              |             |         | I        | CMOS                | External clock source input.                                    |

|                    |             |         |          |                     |                                                                 |

| OSC2/CLKOUT        | 15          | 17      |          |                     |                                                                 |

| OSC2               |             |         | 0        | _                   | Oscillator crystal output. Connects to                          |

|                    |             |         |          |                     | crystal or resonator in crystal oscillator mode.                |

| CLKOUT             |             |         | 0        |                     | In RC mode, OSC2 pin outputs                                    |

| GEROOT             |             |         | Ŭ        |                     | CLKOUT which has 1/4 the frequency                              |

|                    |             |         |          |                     | of OSC1, and denotes the instruction                            |

|                    |             |         |          |                     | cycle rate.                                                     |

|                    |             |         |          |                     | PORTA is a bidirectional I/O port.                              |

| RA0/AN0            | 17          | 19      |          |                     |                                                                 |

| RA0                |             |         | I/O      | TTL                 | Digital I/O                                                     |

| AN0                |             |         | I        | Analog              | Analog input 0                                                  |

| RA1/AN1            | 18          | 20      | 1/0      |                     |                                                                 |

| RA1<br>AN1         |             |         | I/O<br>I | TTL<br>Analog       | Digital I/O<br>Analog input 1                                   |

|                    |             | 4       | I        | Analog              | Analog input 1                                                  |

| RA2/AN2<br>RA2     | 1           | 1       | I/O      | TTL                 | Digital I/O                                                     |

| AN2                |             |         | 1/0      | Analog              | Analog input 2                                                  |

| RA3/AN3/VREF       | 2           | 2       | •        | ,                   |                                                                 |

| RA3                | 2           | £       | I/O      | TTL                 | Digital I/O                                                     |

| AN3                |             |         | I        | Analog              | Analog input 3                                                  |

| VREF               |             |         | I        | Analog              | A/D Reference Voltage input.                                    |

| RA4/T0CKI          | 3           | 3       |          |                     |                                                                 |

| RA4                |             |         | I/O      | ST/OD               | Digital I/O. Open drain when configured                         |

| TOOK               |             |         |          | OT                  | as output.                                                      |

| TOCKI              |             | input C | I        | ST<br>OS compatible | Timer0 external clock input                                     |

# TABLE 1-1: PIC16C712/716 PINOUT DESCRIPTION

Legend:

TTL = TTL-compatible input

CMOS = CMOS compatible input or output

ST = Schmitt Trigger input with CMOS levels

OD = Open drain output

SM = SMBus compatible input. An external resistor is required if this pin is used as an output

NPU = N-channel pull-up

PU = Weak internal pull-up

No-P diode = No P-diode to VDD

AN = Analog input or output

I = input

O = output

P = Power

L = LCD Driver

#### 2.2 **Data Memory Organization**

The data memory is partitioned into multiple banks which contain the General Purpose Registers and the Special Function Registers. Bits RP1 and RP0 are the bank select bits.

| RP1 <sup>(1)</sup> | RP0 (STATUS<6:5>)                        |

|--------------------|------------------------------------------|

| = 00 $\rightarrow$ | Bank 0                                   |

| = 01 $\rightarrow$ | Bank 1                                   |

| = 10 $\rightarrow$ | Bank 2 (not implemented)                 |

| = 11 $\rightarrow$ | Bank 3 (not implemented)                 |

| Note 1:            | Maintain this bit clear to ensure upward |

|                    | compatibility with future products.      |

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers, implemented as static RAM. All implemented banks contain Special Function Registers. Some "high use" Special Function Registers from one bank may be mirrored in another bank for code reduction and quicker access.

#### GENERAL PURPOSE REGISTER 2.2.1 FILE

The register file can be accessed either directly, or indirectly through the File Select Register FSR (see Section 2.5 "Indirect Addressing, INDF and FSR Registers").

| IGURE 2-3: | REGISTER  | FILE MAP |

|------------|-----------|----------|

|            | ILCOOL EI |          |

|   | F  | lle |   |

|---|----|-----|---|

| ٨ | 44 | roc | • |

F

| File                                    |                     |                       | File    |  |  |  |  |  |  |

|-----------------------------------------|---------------------|-----------------------|---------|--|--|--|--|--|--|

| Address                                 | (1)                 | (1)                   | Address |  |  |  |  |  |  |

| 00h                                     | INDF <sup>(1)</sup> | INDF <sup>(1)</sup>   | 80h     |  |  |  |  |  |  |

| 01h                                     | TMR0                | OPTION_REG            | 81h     |  |  |  |  |  |  |

| 02h                                     | PCL                 | PCL                   | 82h     |  |  |  |  |  |  |

| 03h                                     | STATUS              | STATUS                | 83h     |  |  |  |  |  |  |

| 04h                                     | FSR                 | FSR                   | 84h     |  |  |  |  |  |  |

| 05h                                     | PORTA               | TRISA                 | 85h     |  |  |  |  |  |  |

| 06h                                     | PORTB               | TRISB                 | 86h     |  |  |  |  |  |  |

| 07h                                     | DATACCP             | TRISCCP               | 87h     |  |  |  |  |  |  |

| 08h                                     |                     |                       | 88h     |  |  |  |  |  |  |

| 09h                                     |                     |                       | 89h     |  |  |  |  |  |  |

| 0Ah                                     | PCLATH              | PCLATH                | 8Ah     |  |  |  |  |  |  |

| 0Bh                                     | INTCON              | INTCON                | 8Bh     |  |  |  |  |  |  |

| 0Ch                                     | PIR1                | PIE1                  | 8Ch     |  |  |  |  |  |  |

| 0Dh                                     |                     |                       | 8Dh     |  |  |  |  |  |  |

| 0Eh                                     | TMR1L               | PCON                  | 8Eh     |  |  |  |  |  |  |

| 0Fh                                     | TMR1H               |                       | 8Fh     |  |  |  |  |  |  |

| 10h                                     | T1CON               |                       | 90h     |  |  |  |  |  |  |

| 11h                                     | TMR2                |                       | 91h     |  |  |  |  |  |  |

| 12h                                     | T2CON               | PR2                   | 92h     |  |  |  |  |  |  |

| 13h                                     |                     |                       | 93h     |  |  |  |  |  |  |

| 14h                                     |                     |                       | 94h     |  |  |  |  |  |  |

| 15h                                     | CCPR1L              |                       | 95h     |  |  |  |  |  |  |

| 16h                                     | CCPR1H              |                       | 96h     |  |  |  |  |  |  |

| 17h                                     | CCP1CON             |                       | 97h     |  |  |  |  |  |  |

| 18h                                     |                     |                       | 98h     |  |  |  |  |  |  |

| 19h                                     |                     |                       | 99h     |  |  |  |  |  |  |

| 1Ah                                     |                     |                       | 9Ah     |  |  |  |  |  |  |

| 1Bh                                     |                     |                       | 9Bh     |  |  |  |  |  |  |

| 1Ch                                     |                     |                       | 9Ch     |  |  |  |  |  |  |

| 1Dh                                     |                     |                       | 9Dh     |  |  |  |  |  |  |

| 1Eh                                     | ADRES               |                       | 9Eh     |  |  |  |  |  |  |

| 1Fh                                     | ADCON0              | ADCON1                | 9Fh     |  |  |  |  |  |  |

| 20h                                     |                     | General               | A0h     |  |  |  |  |  |  |

|                                         |                     | Purpose               |         |  |  |  |  |  |  |

|                                         | General<br>Purpose  | Registers<br>32 Bytes | BFh     |  |  |  |  |  |  |

|                                         | Registers           | JZ Dytes              | C0h     |  |  |  |  |  |  |

|                                         | 96 Bytes            |                       | COII    |  |  |  |  |  |  |

| 7Fh                                     |                     |                       | FFh     |  |  |  |  |  |  |

|                                         | Bank 0              | Bank 1                | I       |  |  |  |  |  |  |

| Un                                      |                     | ata memory loc        | ations. |  |  |  |  |  |  |

|                                         | l as '0'.           | .,                    | ,       |  |  |  |  |  |  |

| <b>Note 1:</b> Not a physical register. |                     |                       |         |  |  |  |  |  |  |

# 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and Peripheral Modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is give in Table 2-1. The Special Function Registers can be classified into two sets; core (CPU) and peripheral. Those registers associated with the core functions are described in detail in this section. Those related to the operation of the peripheral features are described in detail in that peripheral feature section.

| Addr    | Name                    | Bit 7              | Bit 6              | Bit 5         | Bit 4            | Bit 3        | Bit 2           | Bit 1        | Bit 0   | Value on:<br>POR,<br>BOR | Value on<br>all other<br>Resets (4) |

|---------|-------------------------|--------------------|--------------------|---------------|------------------|--------------|-----------------|--------------|---------|--------------------------|-------------------------------------|

| Bank 0  |                         |                    |                    |               |                  |              |                 |              |         |                          |                                     |

| 00h     | INDF <sup>(1)</sup>     | Addressing         | gister)            | 0000 0000     | 0000 0000        |              |                 |              |         |                          |                                     |

| 01h     | TMR0                    | Timer0 Mod         | lule's Registe     | er            |                  |              |                 |              |         | XXXX XXXX                | uuuu uuuu                           |

| 02h     | PCL <sup>(1)</sup>      | Program Co         | ounter's (PC)      | Least Signif  | icant Byte       |              |                 |              |         | 0000 0000                | 0000 0000                           |

| 03h     | STATUS <sup>(1)</sup>   | IRP <sup>(4)</sup> | RP1 <sup>(4)</sup> | RP0           | TO               | PD           | Z               | DC           | С       | rr01 1xxx                | rr0q quuu                           |

| 04h     | FSR <sup>(1)</sup>      | Indirect Data      | a Memory A         | ddress Pointe | er               |              |                 |              |         | xxxx xxxx                | uuuu uuuu                           |

| 05h     | PORTA <sup>(5,6)</sup>  | _                  | —                  | (7)           | PORTA Data       | Latch when   | written: POR    | TA pins wher | n read  | xx xxxx                  | xu uuuu                             |

| 06h     | PORTB <sup>(5,6)</sup>  | PORTB Dat          | a Latch whe        | n written: PC | ORTB pins whe    | n read       |                 |              |         | xxxx xxxx                | uuuu uuuu                           |

| 07h     | DATACCP                 | (7)                | (7)                | (7)           | (7)              | (7)          | DCCP            | (7)          | DT1CK   | xxxx xxxx                | xxxx xuxu                           |

| 08h-09h | _                       | Unimpleme          | nted               |               |                  |              |                 |              |         | -                        | -                                   |

| 0Ah     | PCLATH <sup>(1,2)</sup> | _                  | —                  | —             | Write Buffer fo  | or the upper | 5 bits of the F | Program Cou  | inter   | 0 0000                   | 0 0000                              |

| 0Bh     | INTCON <sup>(1)</sup>   | GIE                | PEIE               | TOIE          | INTE             | RBIE         | T0IF            | INTF         | RBIF    | 0000 000x                | 0000 000u                           |

| 0Ch     | PIR1                    | _                  | ADIF               | —             | —                | _            | CCP1IF          | TMR2IF       | TMR1IF  | -0 0000                  | -0 0000                             |

| 0Dh     | _                       | Unimpleme          | nted               |               |                  |              |                 |              |         | -                        | -                                   |

| 0Eh     | TMR1L                   | Holding Reg        | gister for the     | Least Signifi | icant Byte of th | e 16-bit TMF | 1 Register      |              |         | xxxx xxxx                | uuuu uuuu                           |

| 0Fh     | TMR1H                   | Holding Reg        | gister for the     | Most Signific | cant Byte of the | e 16-bit TMR | 1 Register      |              |         | xxxx xxxx                | uuuu uuuu                           |

| 10h     | T1CON                   | _                  | —                  | T1CKPS1       | T1CKPS0          | T1OSCEN      | T1SYNC          | TMR1CS       | TMR10N  | 00 0000                  | uu uuuu                             |

| 11h     | TMR2                    | Timer2 Mod         | lule's Registe     | er            |                  |              |                 |              |         | 0000 0000                | 0000 0000                           |

| 12h     | T2CON                   | _                  | TOUTPS3            | TOUTPS2       | TOUTPS1          | TOUTPS0      | TMR2ON          | T2CKPS1      | T2CKPS0 | -000 0000                | -000 0000                           |

| 13h-14h |                         |                    |                    |               |                  |              |                 |              |         |                          |                                     |

| 15h     | CCPR1L                  | Capture/Co         | mpare/PWM          | Register1 (L  | SB)              |              |                 |              |         | xxxx xxxx                | uuuu uuuu                           |

| 16h     | CCPR1H                  | Capture/Co         | mpare/PWM          | Register1 (N  | MSB)             |              |                 |              |         | xxxx xxxx                | uuuu uuuu                           |

| 17h     | CCP1CON                 | _                  | _                  | DC1B1         | DC1B0            | CCP1M3       | CCP1M2          | CCP1M1       | CCP1M0  | 00 0000                  | 00 0000                             |

| 18h-1Dh | _                       | Unimplemented      |                    |               |                  |              |                 |              |         |                          | -                                   |

| 1Eh     | ADRES                   | A/D Result I       | Register           |               |                  |              |                 |              |         | xxxx xxxx                | uuuu uuuu                           |

| 1Fh     | ADCON0                  | ADCS1              | ADCS0              | CHS2          | CHS1             | CHS0         | GO/DONE         | _            | ADON    | 0000 00-0                | 0000 00-0                           |

Legend: x = unknown, u = unchanged, q = value depends on condition, --- = unimplemented, read as '0',

Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from either bank.

2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for PC<12:8> whose contents are transferred to the upper byte of the program counter.

3: Other (non Power-up) Resets include: external Reset through MCLR and the Watchdog Timer Reset.

4: The IRP and RP1 bits are reserved. Always maintain these bits clear.

5: On any device Reset, these pins are configured as inputs.

6: This is the value that will be in the port output latch.

7: Reserved bits; Do Not Use.

# PIC16C712/716

| Addr    | Name                    | Bit 7              | Bit 6              | Bit 5        | Bit 4           | Bit 3         | Bit 2           | Bit 1         | Bit 0   | Value on:<br>POR,<br>BOR | Value on<br>all other<br>Resets (4) |

|---------|-------------------------|--------------------|--------------------|--------------|-----------------|---------------|-----------------|---------------|---------|--------------------------|-------------------------------------|

| Bank 1  |                         |                    |                    |              |                 |               |                 |               |         |                          |                                     |

| 80h     | INDF <sup>(1)</sup>     | Addressing         | this location      | uses conten  | ts of FSR to ac | ldress data r | nemory (not     | a physical re | gister) | 0000 0000                | 0000 0000                           |

| 81h     | OPTION_<br>REG          | RBPU               | INTEDG             | TOCS         | TOSE            | PSA           | PS2             | PS1           | PS0     | 1111 1111                | 1111 1111                           |

| 82h     | PCL <sup>(1)</sup>      | Program Co         | ounter's (PC)      | Least Signif | ficant Byte     |               |                 |               |         | 0000 0000                | 0000 0000                           |

| 83h     | STATUS <sup>(1)</sup>   | IRP <sup>(4)</sup> | RP1 <sup>(4)</sup> | RP0          | TO              | PD            | Z               | DC            | С       | rr01 1xxx                | rr0q quuu                           |

| 84h     | FSR <sup>(1)</sup>      | Indirect Dat       | a Memory Ac        | dress Pointe | er              |               |                 |               |         | xxxx xxxx                | uuuu uuuu                           |

| 85h     | TRISA                   | -                  | _                  | (7)          | PORTA Data      | Direction Re  | gister          |               |         | x1 1111                  | x1 1111                             |

| 86h     | TRISB                   | PORTB Dat          | a Direction F      | Register     |                 |               |                 |               |         | 1111 1111                | 1111 1111                           |

| 87h     | TRISCCP                 | (7)                | (7)                | (7)          | (7)             | (7)           | TCCP            | (7)           | TT1CK   | xxxx x1x1                | xxxx x1x1                           |

| 88h-89h | _                       | Unimpleme          | nted               |              |                 |               |                 |               |         | -                        | -                                   |

| 8Ah     | PCLATH <sup>(1,2)</sup> | _                  | _                  | _            | Write Buffer fo | or the upper  | 5 bits of the I | Program Cou   | inter   | 0 0000                   | 0 0000                              |

| 8Bh     | INTCON <sup>(1)</sup>   | GIE                | PEIE               | TOIE         | INTE            | RBIE          | T0IF            | INTF          | RBIF    | 0000 000x                | 0000 000u                           |

| 8Ch     | PIE1                    | _                  | ADIE               | _            | _               | —             | CCP1IE          | TMR2IE        | TMR1IE  | -0000                    | -0000                               |

| 8Dh     | _                       | Unimpleme          | nted               |              |                 |               |                 |               |         | -                        | -                                   |

| 8Eh     | PCON                    | _                  | _                  | _            | _               | —             | _               | POR           | BOR     | dd                       | uu                                  |

| 8Fh-91h | _                       | Unimpleme          | nted               |              |                 |               |                 |               |         | -                        | -                                   |

| 92h     | PR2                     | Timer2 Peri        | od Register        |              |                 |               |                 |               |         | 1111 1111                | 1111 1111                           |

| 93h-9Eh | _                       | Unimpleme          | nted               |              |                 |               |                 |               |         | -                        | -                                   |

| 9Fh     | ADCON1                  | _                  | _                  | —            | _               | —             | PCFG2           | PCFG1         | PCFG0   | 000                      | 000                                 |

## TABLE 2-1: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend: x = unknown, u = unchanged, q = value depends on condition, — = unimplemented, read as '0',

Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from either bank.

2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for PC<12:8> whose contents are transferred to the upper byte of the program counter.

3: Other (non Power-up) Resets include: external Reset through MCLR and the Watchdog Timer Reset.

4: The IRP and RP1 bits are reserved. Always maintain these bits clear.

5: On any device Reset, these pins are configured as inputs.

**6:** This is the value that will be in the port output latch.

7: Reserved bits; Do Not Use.

#### 2.2.2.3 INTCON Register

The INTCON Register is a readable and writable register which contains various enable and flag bits for the TMR0 register overflow, RB Port change and External RB0/INT pin interrupts. **Note:** Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### FIGURE 2-6: INTCON REGISTER (ADDRESS 0Bh, 8Bh)

| R/W-0       | R/W-0                                                                                                                 | R/W-0       | R/W-0                                       | R/W-0       | R/W-0        | R/W-0        | R/W-x        |                                                                                                                                                 |  |  |  |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------|-------------|---------------------------------------------|-------------|--------------|--------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| GIE<br>bit7 | PEIE                                                                                                                  | TOIE        | INTE                                        | RBIE        | TOIF         | INTF         | RBIF<br>bit0 | <ul> <li>R = Readable bit</li> <li>W = Writable bit</li> <li>U = Unimplemented bit,<br/>read as '0'</li> <li>-n = Value at POR Reset</li> </ul> |  |  |  |  |

| bit 7:      | 1 = Enabl                                                                                                             |             | pt Enable<br>nasked int<br>errupts          |             |              |              |              |                                                                                                                                                 |  |  |  |  |

| bit 6:      | 1 = Enabl                                                                                                             | les all unn | terrupt En<br>nasked pe<br>ipheral int      | ripheral in | terrupts     |              |              |                                                                                                                                                 |  |  |  |  |

| bit 5:      | <b>TOIE</b> : TMR0 Overflow Interrupt Enable bit<br>1 = Enables the TMR0 interrupt<br>0 = Disables the TMR0 interrupt |             |                                             |             |              |              |              |                                                                                                                                                 |  |  |  |  |

| bit 4:      |                                                                                                                       | les the RE  | ternal Inte<br>80/INT exte<br>30/INT ext    | ernal inter | rupt         |              |              |                                                                                                                                                 |  |  |  |  |

| bit 3:      | 1 = Enabl                                                                                                             | les the RE  | nge Interr<br>8 port char<br>3 port cha     | ige interru | pt           |              |              |                                                                                                                                                 |  |  |  |  |

| bit 2:      | 1 = TMR0                                                                                                              | ) register  | ow Interrup<br>has overflo<br>did not ove   | owed (mus   | st be cleare | ed in softwa | are)         |                                                                                                                                                 |  |  |  |  |

| bit 1:      | 1 = The F                                                                                                             | RB0/INT e   | ernal Inter<br>xternal inte<br>xternal inte | errupt occ  | urred (mus   | t be cleare  | d in softwar | re)                                                                                                                                             |  |  |  |  |

| bit 0:      | 1 = At lea                                                                                                            | st one of   |                                             | B4 pins cl  |              |              | e cleared in | software)                                                                                                                                       |  |  |  |  |

| Name         | Bit#  | Buffer | Function                                        |

|--------------|-------|--------|-------------------------------------------------|

| RA0/AN0      | bit 0 | TTL    | Input/output or analog input                    |

| RA1/AN1      | bit 1 | TTL    | Input/output or analog input                    |

| RA2/AN2      | bit 2 | TTL    | Input/output or analog input                    |

| RA3/AN3/VREF | bit 3 | TTL    | Input/output or analog input or VREF            |

|              |       |        | Input/output or external clock input for Timer0 |

| RA4/T0CKI    | bit 4 | ST     | Output is open drain type                       |

#### TABLE 3-1: PORTA FUNCTIONS

**Legend:** TTL = TTL input, ST = Schmitt Trigger input

# TABLE 3-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2     | Bit 1    | Bit 0 | Value on<br>POR,<br>BOR | Value on all other Resets |

|---------|--------|-------|-------|-------|-------|--------|-----------|----------|-------|-------------------------|---------------------------|

| 05h     | PORTA  |       |       | _(1)  | RA4   | RA3    | RA2       | RA1      | RA0   | xx xxxx                 | xu uuuu                   |

| 85h     | TRISA  | _     | —     | _(1)  | PORT  | A Data | Direction | Register |       | 11 1111                 | 11 1111                   |

| 9Fh     | ADCON1 | _     |       |       |       |        | PCFG2     | PCFG1    | PCFG0 | 000                     | 000                       |

Legend: x = unknown, u = unchanged, — = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

Note 1: Reserved bits; Do Not Use.

# 3.2 PORTB and the TRISB Register

PORTB is an 8-bit wide bidirectional port. The corresponding data direction register is TRISB. Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input, (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output, (i.e., put the contents of the output latch on the selected pin).

| BCF   | STATUS, RPO | i                       |

|-------|-------------|-------------------------|

| CLRF  | PORTB       | ; Initialize PORTB by   |

|       |             | ; clearing output       |

|       |             | ; data latches          |

| BSF   | STATUS, RPO | ; Select Bank 1         |

| MOVLW | 0xCF        | ; Value used to         |

|       |             | ; initialize data       |

|       |             | ; direction             |

| MOVWF | TRISB       | ; Set RB<3:0> as inputs |

|       |             | ; RB<5:4> as outputs    |

|       |             | ; RB<7:6> as inputs     |

|       |             |                         |

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit RBPU (OPTION\_REG<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

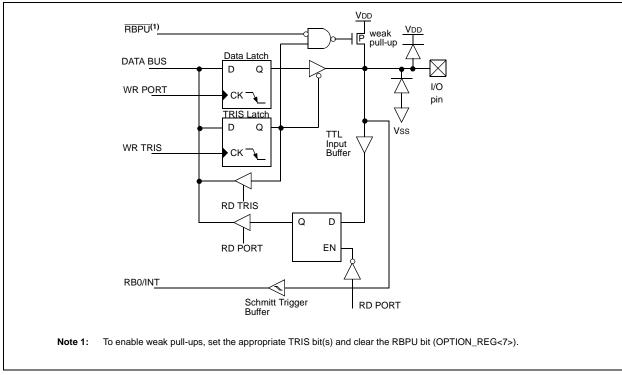

# FIGURE 3-3: BLOCK DIAGRAM OF RB0 PIN

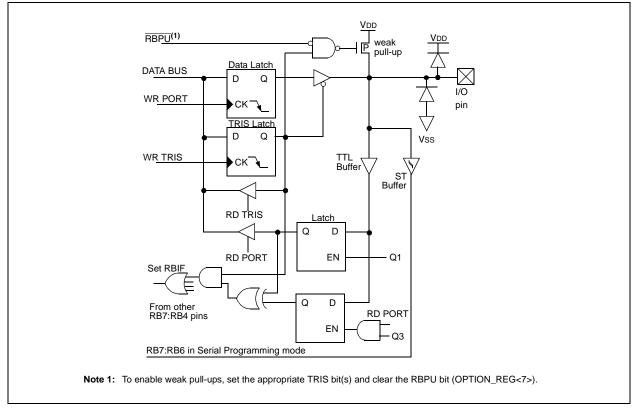

#### FIGURE 3-7: BLOCK DIAGRAM OF RB7:RB4 PINS

#### TABLE 3-3: PORTB FUNCTIONS

| Name                | Bit#  | Buffer                | Function                                                                                                                                                              |

|---------------------|-------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RB0/INT             | bit 0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input. Internal software programmable weak pull-up.                                                                            |

| RB1/T1OS0/<br>T1CKI | bit 1 | TTL/ST <sup>(1)</sup> | Input/output pin or Timer1 oscillator output, or Timer1 clock input. Internal software programmable weak pull-up. See Timer1 section for detailed operation.          |

| RB2/T1OSI           | bit 2 | TTL/ST <sup>(1)</sup> | Input/output pin or Timer1 oscillator input. Internal software programmable weak pull-up. See Timer1 section for detailed operation.                                  |

| RB3/CCP1            | bit 3 | TTL/ST <sup>(1)</sup> | Input/output pin or Capture 1 input, or Compare 1 output, or PWM1 output.<br>Internal software programmable weak pull-up. See CCP1 section for<br>detailed operation. |

| RB4                 | bit 4 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                                                                             |

| RB5                 | bit 5 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                                                                             |

| RB6                 | bit 6 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up. Serial programming clock.                                                   |

| RB7                 | bit 7 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up. Serial programming data.                                                    |

Legend: TTL = TTL input, ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt or peripheral input.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

| TMR1<br>Module<br>Mode | Clock Source      | Control Bits                   | TMR1 Module Operation                                                                                                                                                                                                                                                                    | PORTB<2:1> Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|------------------------|-------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Off                    | N/A               | T1CON =xx 0x00                 | Off                                                                                                                                                                                                                                                                                      | PORTB<2:1> function as normal I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| Timer                  | Fosc/4            | T1CON =xx 0x01                 | TMR1 module uses the main<br>oscillator as clock source.<br>TMR1ON can turn on or turn off<br>Timer1.                                                                                                                                                                                    | PORTB<2:1> function as normal I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| Counter                | External circuit  | T1CON =xx 0x11<br>TR1SCCP =x-1 | TMR1 module uses the external PORTB<2> functions as                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|                        | Firmware          | T1CON =xx 0x11<br>TR1SCCP =x-0 | DATACCP<0> bit drives RB1/<br>T1OSO/T1CKI and produces<br>the TMR1 clock source.<br>TMR1ON can turn on or turn off<br>Timer1. The DATACCP<0> bit,<br>DT1CK, can read and write to<br>the RB1/T1OSO/T1CKI pin.                                                                            | result in the data latch, but not to<br>the RB1/T1OSO/T1CKI pin. If<br>the TMR1CS bit is cleared<br>(TMR1 reverts to the timer<br>mode), then pin PORTB<1> will<br>be driven with the value in the<br>data latch.                                                                                                                                                                                                                                                                                            |  |  |  |

|                        | Timer1 oscillator | T1CON =xx 1x11                 | RB1/T1OSO/T1CKI and RB2/<br>T1OSI are configured as a 2 pin<br>crystal oscillator. RB1/T1OSI/<br>T1CKI is the clock input for<br>TMR1. TMR1ON can turn on or<br>turn off Timer1. DATACCP<1><br>bit, DT1CK, always reads '0' as<br>input and can not write to the<br>RB1/T1OSO/T1CK1 pin. | PORTB<2:1> always read '0'<br>when configured as inputs. If<br>PORTB<2:1> are configured as<br>outputs, reading PORTB<2:1><br>will read the data latches. Writ-<br>ing to PORTB<2:1> will always<br>store the result in the data<br>latches, but not to the RB2/<br>T1OSI and RB1/T1OSO/T1CKI<br>pins. If the TMR1CS and<br>T1OSCEN bits are cleared<br>(TMR1 reverts to the timer mode<br>and TMR1 oscillator is disabled),<br>then pin PORTB<2:1> will be<br>driven with the value in the data<br>latches. |  |  |  |

TABLE 5-1: TMR1 MODULE AND PORTB OPERATION

# 9.0 SPECIAL FEATURES OF THE CPU

The PIC16C712/716 devices have a host of features intended to maximize system reliability, minimize cost through elimination of external components, provide power-saving operating modes and offer code protection. These are:

- OSC Selection

- Reset:

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- Sleep

- Code protection

- ID locations

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

These devices have a Watchdog Timer, which can be shut off only through Configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay on power-up only and is designed to keep the part in Reset while the power supply stabilizes. With these two timers on-chip, most applications need no external Reset circuitry. Sleep mode is designed to offer a very low-current Power-Down mode. The user can wake-up from Sleep through external Reset, Watchdog Timer Wake-up, or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost, while the LP crystal option saves power. A set of Configuration bits are used to select various options.

Additional information on special features is available in the  $PIC^{®}$  Mid-Range Reference Manual, (DS33023).

# 9.1 Configuration Bits

The Configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h-3FFFh), which can be accessed only during programming.

## 9.9 Power Control/Status Register (PCON)

The Power Control/Status Register, PCON has two bits.

Bit 0 is Brown-out Reset Status bit,  $\overline{\text{BOR}}$ . If the BODEN Configuration bit is set,  $\overline{\text{BOR}}$  is '1' on Power-on Reset. If the BODEN Configuration bit is clear,  $\overline{\text{BOR}}$  is unknown on Power-on Reset. The BOR Status bit is a "don't care" and is not necessarily predictable if the brown-out circuit is disabled (the BODEN Configuration bit is clear). BOR must then be set by the user and checked on subsequent Resets to see if it is clear, indicating a brown-out has occurred.

Bit 1 is  $\overrightarrow{\text{POR}}$  (Power-on Reset Status bit). It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

# TABLE 9-3:TIME-OUT IN VARIOUS SITUATIONS

| Oscillator Configuration | Power              | -up      | Brown-out        | Wake-up from |  |

|--------------------------|--------------------|----------|------------------|--------------|--|

| Oscillator Configuration | PWRTE = 0PWRTE = 1 |          | Brown-out        | Sleep        |  |

| XT, HS, LP               | 72 ms + 1024Tosc   | 1024Tosc | 72 ms + 1024Tosc | 1024Tosc     |  |

| RC                       | 72 ms              | _        | 72 ms            | —            |  |

## TABLE 9-4: STATUS BITS AND THEIR SIGNIFICANCE

| POR | BOR | TO | PD |                                                         |

|-----|-----|----|----|---------------------------------------------------------|

| 0   | x   | 1  | 1  | Power-on Reset                                          |

| 0   | x   | 0  | x  | Illegal, TO is set on POR                               |

| 0   | x   | x  | 0  | Illegal, PD is set on POR                               |

| 1   | 0   | 1  | 1  | Brown-out Reset                                         |

| 1   | 1   | 0  | 1  | WDT Reset                                               |

| 1   | 1   | 0  | 0  | WDT Wake-up                                             |

| 1   | 1   | u  | u  | MCLR Reset during normal operation                      |

| 1   | 1   | 1  | 0  | MCLR Reset during Sleep or interrupt wake-up from Sleep |

#### TABLE 9-5: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uu               |

| MCLR Reset during Sleep            | 000h                  | 0001 Ouuu          | uu               |

| WDT Reset                          | 000h                  | 0000 luuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 Ouuu          | uu               |

| Brown-out Reset                    | 000h                  | 0001 luuu          | u0               |

| Interrupt wake-up from Sleep       | PC + 1 <sup>(1)</sup> | uuul Ouuu          | uu               |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit read as '0'.

Note 1: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

# 11.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB® IDE Software

- Assemblers/Compilers/Linkers

- MPASM<sup>™</sup> Assembler

- MPLAB C18 and MPLAB C30 C Compilers

- MPLINK<sup>™</sup> Object Linker/

- MPLIB™ Object Librarian

- MPLAB ASM30 Assembler/Linker/Library

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- MPLAB ICE 4000 In-Circuit Emulator

- In-Circuit Debugger

- MPLAB ICD 2

- Device Programmers

- PICSTART<sup>®</sup> Plus Development Programmer

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration and Development Boards and Evaluation Kits

# 11.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> operating system-based application that contains:

- A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- · A full-featured editor with color-coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- High-level source code debugging

- Visual device initializer for easy register initialization

- · Mouse over variable inspection

- Drag and drop variables from source to watch windows

- · Extensive on-line help

- Integration of select third party tools, such as HI-TECH Software C Compilers and IAR C Compilers

The MPLAB IDE allows you to:

- Edit your source files (either assembly or C)

- One touch assemble (or compile) and download to PIC MCU emulator and simulator tools (automatically updates all project information)

- Debug using:

- Source files (assembly or C)

- Mixed assembly and C

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

# 11.2 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for all PIC MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

# 11.3 MPLAB C18 and MPLAB C30 C Compilers

The MPLAB C18 and MPLAB C30 Code Development Systems are complete ANSI C compilers for Microchip's PIC18 family of microcontrollers and dsPIC30F family of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use not found with other compilers.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

# 11.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 11.5 MPLAB ASM30 Assembler, Linker and Librarian

MPLAB ASM30 Assembler produces relocatable machine code from symbolic assembly language for dsPIC30F devices. MPLAB C30 C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- Support for the entire dsPIC30F instruction set

- · Support for fixed-point and floating-point data

- · Command line interface

- Rich directive set

- Flexible macro language

- MPLAB IDE compatibility

# 11.6 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC<sup>®</sup> DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, as well as internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C18 and MPLAB C30 C Compilers, and the MPASM and MPLAB ASM30 Assemblers. The software simulator offers the flexibility to develop and debug code outside of the laboratory environment, making it an excellent, economical software development tool.

# 12.1 DC Characteristics: PIC16C712/716-04 (Commercial, Industrial, Extended) PIC16C712/716-20 (Commercial, Industrial, Extended)

| DC CHA                | DC CHARACTERISTICS |                                                                                                                                                  |                     | Standard Operating Con<br>Operating temperature |                      |                          | $ \begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                      |

|-----------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------------------------------------------|----------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.          | Sym.               | Characteristic                                                                                                                                   | Min.                | Тур†                                            | Max.                 | Units                    | Conditions                                                                                                                                                                 |

| D001<br>D001A         | Vdd                | Supply Voltage                                                                                                                                   | 4.0<br>4.5<br>VBOR* |                                                 | 5.5<br>5.5<br>5.5    | V<br>V<br>V              | XT, RC and LP osc mode<br>HS osc mode<br>BOR enabled <sup>(7)</sup>                                                                                                        |

| D002*                 | Vdr                | RAM Data Retention Voltage <sup>(1)</sup>                                                                                                        | _                   | 1.5                                             |                      | V                        |                                                                                                                                                                            |

| D003                  | VPOR               | VDD Start Voltage to ensure inter-<br>nal Power-on Reset signal                                                                                  | —                   | Vss                                             | —                    | V                        | See section on Power-on Reset for details                                                                                                                                  |

| D004*<br>D004A*       | SVDD               | VDD Rise Rate to ensure internal<br>Power-on Reset signal                                                                                        | 0.05<br>TBD         | _                                               | _                    | V/ms                     | PWRT enabled (PWRTE bit clear)<br>PWRT disabled (PWRTE bit set)<br>See section on Power-on Reset for details                                                               |

| D005                  | VBOR               | Brown-out Reset<br>voltage trip point                                                                                                            | 3.65                | —                                               | 4.35                 | V                        | BODEN bit set                                                                                                                                                              |

| D010<br>D013          | IDD                | Supply Current <sup>(2,5)</sup>                                                                                                                  | _                   | 0.8<br>4.0                                      | 2.5<br>8.0           | mA<br>mA                 | Fosc = 4 MHz, VDD = 4.0V<br>Fosc = 20 MHz, VDD = 4.0V                                                                                                                      |

| D020<br>D021<br>D021B | IPD                | Power-down Current <sup>(3,5)</sup>                                                                                                              | <br>                | 10.5<br>1.5<br>1.5<br>2.5                       | 42<br>16<br>19<br>19 | μΑ<br>μΑ<br>μΑ<br>μΑ     | VDD = 4.0V, WDT enabled, -40°C to +85°C<br>VDD = 4.0V, WDT disabled, 0°C to +70°C<br>VDD = 4.0V, WDT disabled, -40°C to +85°C<br>VDD = 4.0V, WDT disabled, -40°C to +125°C |

| D022*<br>D022A*       | ΔİWDT<br>ΔİBOR     | Module Differential Current <sup>(6)</sup><br>Watchdog Timer<br>Brown-out Reset                                                                  |                     | 6.0<br>TBD                                      | 20<br>200            | μΑ<br>μΑ                 | WDTE bit set, VDD = 4.0V<br>BODEN bit set, VDD = 5.0V                                                                                                                      |

| 1A                    | Fosc               | LP Oscillator Operating Frequency<br>RC Oscillator Operating Frequency<br>XT Oscillator Operating Frequency<br>HS Oscillator Operating Frequency | 0<br>0<br>0<br>0    |                                                 | 200<br>4<br>4<br>20  | KHz<br>MHz<br>MHz<br>MHz | All temperatures<br>All temperatures<br>All temperatures<br>All temperatures                                                                                               |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD,

- MCLR = VDD; WDT enabled/disabled as specified.

- **3:** The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD and Vss.

4: For RC Osc mode, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kOhm.

5: Timer1 oscillator (when enabled) adds approximately 20 µA to the specification. This value is from characterization and is for design guidance only. This is not tested.

6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

7: This is the voltage where the device enters the Brown-out Reset. When BOR is enabled, the device will operate correctly to this trip point.

# 12.4.3 TIMING DIAGRAMS AND SPECIFICATIONS

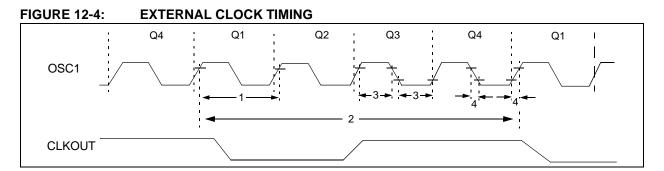

## TABLE 12-2: EXTERNAL CLOCK TIMING REQUIREMENTS

| Param<br>No. | Sym.  | Characteristic                   | Min. | Тур† | Max.   | Units | Conditions          |

|--------------|-------|----------------------------------|------|------|--------|-------|---------------------|

| 1A           | Fosc  | External CLKIN Frequency         | DC   | _    | 4      | MHz   | RC and XT osc modes |

|              |       | (Note 1)                         | DC   | —    | 4      | MHz   | HS osc mode (-04)   |

|              |       |                                  | DC   | —    | 20     | MHz   | HS osc mode (-20)   |

|              |       |                                  | DC   | —    | 200    | kHz   | LP osc mode         |

|              |       | Oscillator Frequency             | DC   | _    | 4      | MHz   | RC osc mode         |

|              |       | (Note 1)                         | 0.1  | —    | 4      | MHz   | XT osc mode         |

|              |       |                                  |      | —    | 20     | MHz   | HS osc mode         |

|              |       |                                  | 5    | —    | 200    | kHz   | LP osc mode         |

| 1            | Tosc  | External CLKIN Period            | 250  | _    | _      | ns    | RC and XT osc modes |

|              |       | (Note 1)                         | 250  | —    | —      | ns    | HS osc mode (-04)   |

|              |       |                                  | 50   | —    | —      | ns    | HS osc mode (-20)   |

|              |       |                                  | 5    | —    | —      | μs    | LP osc mode         |

|              |       | Oscillator Period                | 250  | _    | _      | ns    | RC osc mode         |

|              |       | (Note 1)                         | 250  | —    | 10,000 | ns    | XT osc mode         |

|              |       |                                  | 250  | —    | 250    | ns    | HS osc mode (-04)   |

|              |       |                                  | 50   | —    | 250    | ns    | HS osc mode (-20)   |

|              |       |                                  | 5    | _    | _      | μS    | LP osc mode         |

| 2            | TCY   | Instruction Cycle Time (Note 1)  | 200  | _    | DC     | ns    | Tcy = 4/Fosc        |

| 3*           | TosL, | External Clock in (OSC1) High or | 100  | _    | -      | ns    | XT oscillator       |

|              | TosH  | Low Time                         | 2.5  | —    | —      | μS    | LP oscillator       |

|              |       |                                  | 15   |      |        | ns    | HS oscillator       |

| 4*           | TosR, | External Clock in (OSC1) Rise or | _    | _    | 25     | ns    | XT oscillator       |

|              | TosF  | Fall Time                        | —    | —    | 50     | ns    | LP oscillator       |

|              |       |                                  | —    | —    | 15     | ns    | HS oscillator       |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note1:** Instruction cycle period (TCY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin.

When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

# PIC16C712/716

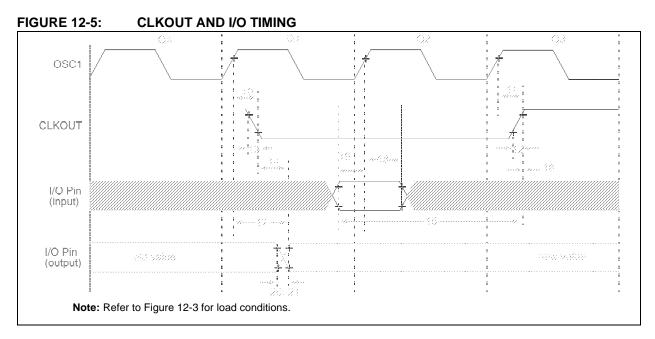

# TABLE 12-3: CLKOUT AND I/O TIMING REQUIREMENTS

| Param<br>No. | Sym.     | Characteristic                    | Min.          | Тур† | Max. | Units       | Conditions |        |

|--------------|----------|-----------------------------------|---------------|------|------|-------------|------------|--------|

| 10*          | TosH2ckL | OSC1↑ to CLKOUT↓                  | _             | 75   | 200  | ns          | Note 1     |        |

| 11*          | TosH2ckH | OSC1¦ to CLKOUT¦                  |               | —    | 75   | 200         | ns         | Note 1 |

| 12*          | TckR     | CLKOUT rise time                  |               | _    | 35   | 100         | ns         | Note 1 |

| 13*          | TckF     | CLKOUT fall time                  |               | —    | 35   | 100         | ns         | Note 1 |

| 14*          | TckL2ioV | CLKOUT Ø to Port out valid        |               | —    | _    | 0.5TCY + 20 | ns         | Note 1 |

| 15*          | TioV2ckH | Port in valid before CLKOUT       | Tosc + 200    |      | _    | ns          | Note 1     |        |

| 16*          | TckH2iol | Port in hold after CLKOUT {       | 0             |      | _    | ns          | Note 1     |        |

| 17*          | TosH2ioV | OSC1¦ (Q1 cycle) to Port out val  | id            | —    | 50   | 150         | ns         |        |

| 18*          | TosH2iol | OSC1¦ (Q2 cycle) to Port input    | Standard      | 100  |      | _           | ns         |        |

| 18A*         |          | invalid (I/O in hold time)        | Extended (LC) | 200  |      | _           | ns         |        |

| 19*          | TioV2osH | Port input valid to OSC11 (I/O in | setup time)   | 0    |      | _           | ns         |        |

| 20*          | TioR     | Port output rise time             | Standard      | _    | 10   | 40          | ns         |        |

| 20A*         |          |                                   | Extended (LC) | —    |      | 80          | ns         |        |

| 21*          | TioF     | Port output fall time             | Standard      | —    | 10   | 40          | ns         |        |

| 21A*         | 1        |                                   | Extended (LC) | —    | —    | 80          | ns         |        |

| 22††*        | TINP     | INT pin high or low time          |               | Тсү  | -    | —           | ns         |        |

| 23††*        | Trbp     | RB7:RB4 change INT high or low    | v time        | Тсү  | —    | —           | ns         |        |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

†† These parameters are asynchronous events not related to any internal clock edge.

Note1: Measurements are taken in RC mode where CLKOUT output is 4 x Tosc.

# **13.0 PACKAGING INFORMATION**

# 13.1 Package Marking Information

#### 18-Lead PDIP

#### 18-Lead CERDIP Windowed

# 18-Lead SOIC (.300")

## 20-Lead SSOP

## Example

## Example

# Example

| Legen | d: XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>*                                                                                                                                                        | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (e3)<br>can be found on the outer packaging for this package. |  |  |  |  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Note: | : In the event the full Microchip part number cannot be marked on one line<br>be carried over to the next line, thus limiting the number of ava<br>characters for customer-specific information. |                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

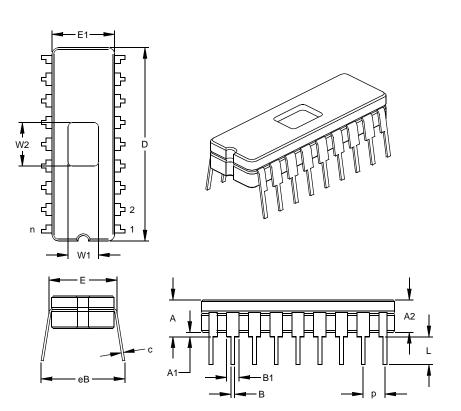

# 18-Lead Ceramic Dual In-line with Window (JW) - 300 mil (CERDIP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units |      |      |      | MILLIMETERS |       |       |  |

|----------------------------|-------|------|------|------|-------------|-------|-------|--|

| Dimensio                   | MIN   | NOM  | MAX  | MIN  | NOM         | MAX   |       |  |

| Number of Pins             | n     |      | 18   |      |             | 18    |       |  |

| Pitch                      | р     |      | .100 |      |             | 2.54  |       |  |

| Top to Seating Plane       | Α     | .170 | .183 | .195 | 4.32        | 4.64  | 4.95  |  |

| Ceramic Package Height     | A2    | .155 | .160 | .165 | 3.94        | 4.06  | 4.19  |  |

| Standoff                   | A1    | .015 | .023 | .030 | 0.38        | 0.57  | 0.76  |  |

| Shoulder to Shoulder Width | Е     | .300 | .313 | .325 | 7.62        | 7.94  | 8.26  |  |

| Ceramic Pkg. Width         | E1    | .285 | .290 | .295 | 7.24        | 7.37  | 7.49  |  |

| Overall Length             | D     | .880 | .900 | .920 | 22.35       | 22.86 | 23.37 |  |

| Tip to Seating Plane       | L     | .125 | .138 | .150 | 3.18        | 3.49  | 3.81  |  |

| Lead Thickness             | С     | .008 | .010 | .012 | 0.20        | 0.25  | 0.30  |  |

| Upper Lead Width           | B1    | .050 | .055 | .060 | 1.27        | 1.40  | 1.52  |  |

| Lower Lead Width           | В     | .016 | .019 | .021 | 0.41        | 0.47  | 0.53  |  |

| Overall Row Spacing §      | eB    | .345 | .385 | .425 | 8.76        | 9.78  | 10.80 |  |

| Window Width               | W1    | .130 | .140 | .150 | 3.30        | 3.56  | 3.81  |  |

| Window Length              | W2    | .190 | .200 | .210 | 4.83        | 5.08  | 5.33  |  |

\* Controlling Parameter

§ Significant Characteristic

JEDEC Equivalent: MO-036

Drawing No. C04-010

# APPENDIX A: REVISION HISTORY

| Version | Date | Revision Description                                                                                                                                                                                                                    |

|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A       | 2/99 | This is a new data sheet. How-<br>ever, the devices described in this<br>data sheet are the upgrades to<br>the devices found in the<br><i>PIC16C6X Data Sheet</i> ,<br>DS30234, and the <i>PIC16C7X</i><br><i>Data Sheet</i> , DS30390. |

| В       | 9/05 | Removed Preliminary Status.                                                                                                                                                                                                             |