Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 13                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                 |

| Data Converters            | A/D 4x8b                                                                  |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 20-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c716-20-ss |

### **Table of Contents**

| 1.0   | Device Overview                                 | 5    |

|-------|-------------------------------------------------|------|

| 2.0   | Memory Organization                             | 9    |

| 3.0   | I/O Ports                                       | . 21 |

| 4.0   | I/O Ports Timer0 Module                         | . 29 |

| 5.0   | Timer1 Module                                   | . 31 |

| 6.0   | Timer2 Module                                   | . 36 |

| 7.0   | Capture/Compare/PWM (CCP) Module(s)             | . 39 |

| 8.0   | Analog-to-Digital Converter (A/D) Module        |      |

| 9.0   | Special Features of the CPU                     |      |

| 10.0  | Instruction Set Summary                         | . 67 |

| 11.0  | Development Support  Electrical Characteristics | . 69 |

| 12.0  | Electrical Characteristics                      | . 73 |

| 13.0  | Packaging Information                           | . 89 |

| Revis | ion History                                     | . 95 |

| Conv  | ersion Considerations                           | . 95 |

|       | tion from Base-line to Mid-Range Devices        |      |

| Index |                                                 | . 97 |

| On-Li | ne Support                                      | 101  |

| Read  | er Response                                     | 102  |

| PIC1  | 6C712/716 Product Identification System         | 103  |

|       |                                                 |      |

### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

### **Errata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

TABLE 1-1: PIC16C712/716 PINOUT DESCRIPTION

| Pin                                | PIC16C712/716 |      | Pin           | Buffer                  |                                                                                                                  |  |

|------------------------------------|---------------|------|---------------|-------------------------|------------------------------------------------------------------------------------------------------------------|--|

| Name                               | DIP, SOIC     | SSOP | Туре          | Туре                    | Description                                                                                                      |  |

| MCLR/VPP<br>MCLR<br>VPP            | 4             | 4    | l<br>P        | ST                      | Master clear (Reset) input. This pin is an active low Reset to the device. Programming voltage input             |  |

| OSC1/CLKIN<br>OSC1                 | 16            | 18   | I             | ST                      | Oscillator crystal input or external clock source input. ST buffer when config-                                  |  |

| CLKIN                              |               |      | I             | CMOS                    | ured in RC mode. CMOS otherwise. External clock source input.                                                    |  |

| OSC2/CLKOUT<br>OSC2                | 15            | 17   | 0             | _                       | Oscillator crystal output. Connects to crystal or resonator in crystal oscillator mode.                          |  |

| CLKOUT                             |               |      | 0             | _                       | In RC mode, OSC2 pin outputs CLKOUT which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate. |  |

|                                    |               |      |               |                         | PORTA is a bidirectional I/O port.                                                                               |  |

| RA0/AN0<br>RA0<br>AN0              | 17            | 19   | I/O<br>I      | TTL<br>Analog           | Digital I/O<br>Analog input 0                                                                                    |  |

| RA1/AN1<br>RA1<br>AN1              | 18            | 20   | I/O<br>I      | TTL<br>Analog           | Digital I/O<br>Analog input 1                                                                                    |  |

| RA2/AN2<br>RA2<br>AN2              | 1             | 1    | I/O<br>I      | TTL<br>Analog           | Digital I/O<br>Analog input 2                                                                                    |  |

| RA3/AN3/VREF<br>RA3<br>AN3<br>VREF | 2             | 2    | I/O<br>I<br>I | TTL<br>Analog<br>Analog | Digital I/O Analog input 3 A/D Reference Voltage input.                                                          |  |

| RA4/T0CKI<br>RA4                   | 3             | 3    | I/O           | ST/OD                   | Digital I/O. Open drain when configured as output.                                                               |  |

| T0CKI                              |               |      | I             | ST                      | Timer0 external clock input                                                                                      |  |

**Legend:** TTL = TTL-compatible input CMOS = CMOS compatible input or output

ST = Schmitt Trigger input with CMOS levels

OD = Open drain output

SM = SMBus compatible input. An external resistor is required if this pin is used as an output

I = input O = output P = Power L = LCD Driver

### 2.0 MEMORY ORGANIZATION

There are two memory blocks in each of these PIC<sup>®</sup> microcontroller devices. Each block (Program Memory and Data Memory) has its own bus so that concurrent access can occur.

Additional information on device memory may be found in the PIC<sup>®</sup> Mid-Range Reference Manual, (DS33023).

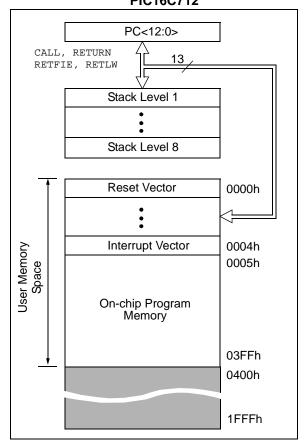

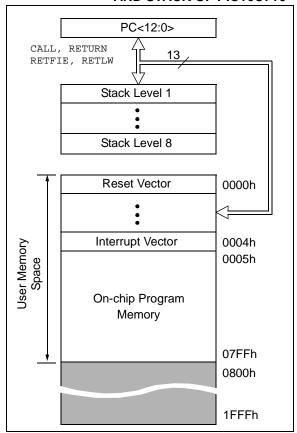

### 2.1 Program Memory Organization

The PIC16C712/716 has a 13-bit Program Counter (PC) capable of addressing an 8K x 14 program memory space. PIC16C712 has 1K x 14 words of program memory and PIC16C716 has 2K x 14 words of program memory. Accessing a location above the physically implemented address will cause a wraparound.

The Reset vector is at 0000h and the interrupt vector is at 0004h.

FIGURE 2-1: PROGRAM MEMORY MAP AND STACK OF THE PIC16C712

FIGURE 2-2: PROGRAM MEMORY MAP

AND STACK OF PIC16C716

### 2.2.2.5 PIR1 Register

This register contains the individual flag bits for the peripheral interrupts.

Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

### FIGURE 2-8: PIR1 REGISTER (ADDRESS 0Ch)

| FIGURE 2 | :-8:                                                                                                                                          | PIRTRI                                                                 | EGISTER                                              | (ADDRI                   | 233 UCN)   |       |       |                  |  |  |  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|------------------------------------------------------|--------------------------|------------|-------|-------|------------------|--|--|--|

| U-0      | R/W-0                                                                                                                                         | U-0                                                                    | U-0                                                  | R/W-0                    | R/W-0      | R/W-0 | R/W-0 |                  |  |  |  |

| U-0      |                                                                                                                                               |                                                                        | U-0                                                  | K/W-0                    |            |       |       | P - Peadable bit |  |  |  |

| bit7     | ADIF — — CCP1IF TMR2IF TMR1IF bit0  R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR Reset              |                                                                        |                                                      |                          |            |       |       |                  |  |  |  |

| bit 6:   | ADIF: A/D Converter Interrupt Flag bit  1 = An A/D conversion completed (must be cleared in software)  0 = The A/D conversion is not complete |                                                                        |                                                      |                          |            |       |       |                  |  |  |  |

| bit 5-3: | Unimpler                                                                                                                                      | nented: R                                                              | Read as '0                                           | ,                        |            |       |       |                  |  |  |  |

| bit 2:   | 0 = No TN<br><u>Compare</u><br>1 = A TMI<br>0 = No TN<br><u>PWM Mod</u>                                                                       | Mode:<br>R1 registe<br>MR1 regist<br>Mode:<br>R1 registe<br>MR1 regist | er capture<br>ter capture<br>er compare<br>ter compa | occurred (<br>e occurred | curred (mu |       | ,     | vare)            |  |  |  |

Note:

0 = No TMR2 to PR2 match occurred

bit 1:

bit 0: TMR1IF: TMR1 Overflow Interrupt Flag bit

TMR2IF: TMR2 to PR2 Match Interrupt Flag bit

1 = TMR2 to PR2 match occurred (must be cleared in software)

- 1 = TMR1 register overflowed (must be cleared in software)

- 0 = TMR1 register did not overflow

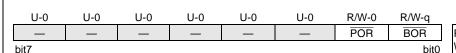

### 2.2.2.6 PCON Register

The Power Control (PCON) register contains a flag bit to allow differentiation between a Power-on Reset (POR) to an external MCLR Reset or WDT Reset. These devices contain an additional bit to differentiate a Brown-out Reset condition from a Power-on Reset condition.

Note: If the BODEN Configuration bit is set, BOR is '1' on Power-on Reset. If the BODEN

Configuration bit is clear, BOR is unknown

on Power-on Reset.

The BOR Status bit is a "don't care" and is not necessarily predictable if the brown-out circuit is disabled (the BODEN Configuration bit is clear). BOR must then be set by the user and checked on subsequent resets to see if it is clear, indicating a brown-out has occurred.

### FIGURE 2-9: PCON REGISTER (ADDRESS 8Eh)

R = Readable bit

N = Writable bit

J = Unimplemented bit, read as '0'

-n = Value at POR Reset

bit 7-2: Unimplemented: Read as '0'

bit 1: **POR**: Power-on Reset Status bit

1 = No Power-on Reset occurred

0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

bit 0: BOR: Brown-out Reset Status bit

1 = No Brown-out Reset occurred

0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs)

TABLE 3-1: PORTA FUNCTIONS

| Name         | Bit#  | Buffer | Function                                        |  |  |  |

|--------------|-------|--------|-------------------------------------------------|--|--|--|

| RA0/AN0      | bit 0 | TTL    | Input/output or analog input                    |  |  |  |

| RA1/AN1      | bit 1 | TTL    | Input/output or analog input                    |  |  |  |

| RA2/AN2      | bit 2 | TTL    | nput/output or analog input                     |  |  |  |

| RA3/AN3/VREF | bit 3 | TTL    | Input/output or analog input or VREF            |  |  |  |

|              |       |        | Input/output or external clock input for Timer0 |  |  |  |

| RA4/T0CKI    | bit 4 | ST     | Output is open drain type                       |  |  |  |

**Legend:** TTL = TTL input, ST = Schmitt Trigger input

### TABLE 3-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3                         | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR,<br>BOR | Value on all other Resets |

|---------|--------|-------|-------|-------|-------|-------------------------------|-------|-------|-------|-------------------------|---------------------------|

| 05h     | PORTA  | _     | _     | _(1)  | RA4   | RA3                           | RA2   | RA1   | RA0   | xx xxxx                 | xu uuuu                   |

| 85h     | TRISA  | _     | _     | (1)   | PORT  | PORTA Data Direction Register |       |       |       | 11 1111                 | 11 1111                   |

| 9Fh     | ADCON1 | _     | _     | _     | _     | _                             | PCFG2 | PCFG1 | PCFG0 | 000                     | 000                       |

**Legend:** x = unknown, u = unchanged, — = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

Note 1: Reserved bits; Do Not Use.

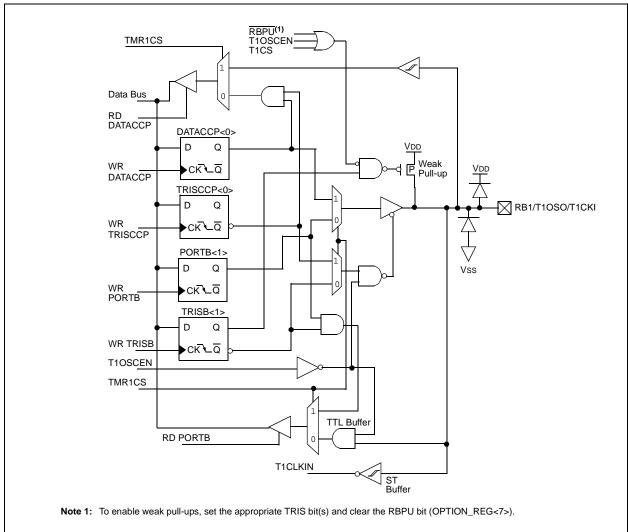

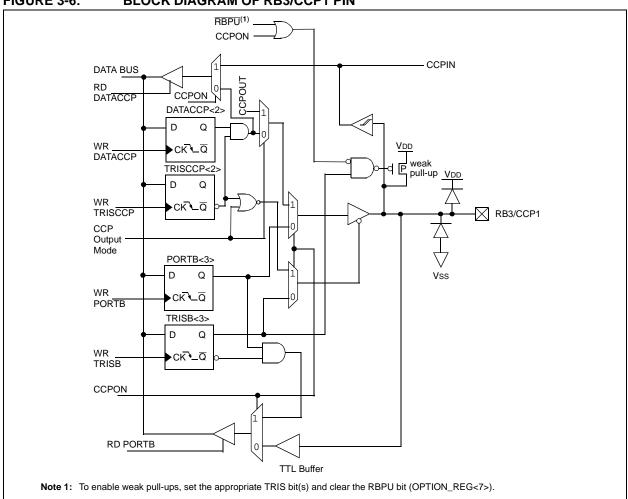

PORTB pins RB3:RB1 are multiplexed with several peripheral functions (Table 3-3). PORTB pins RB3:RB0 have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTB pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override is in effect while the peripheral is enabled, read-modify-write instructions (BSF, BCF, XORWF) with TRISB as destination should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

Four of PORTB's pins, RB7:RB4, have an interrupt-onchange feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupton-change comparison). The input pins, RB7:RB4, are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RB Port Change Interrupt with flag bit RBIF (INTCON<0>).

This interrupt can wake the device from Sleep. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

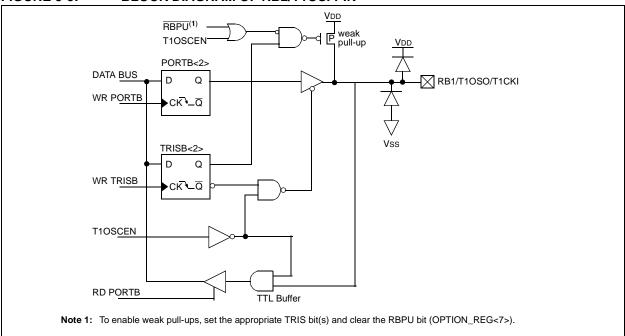

FIGURE 3-4: BLOCK DIAGRAM OF RB1/T10S0/T1CKI PIN

FIGURE 3-5: BLOCK DIAGRAM OF RB2/T10SI PIN

### FIGURE 3-6: BLOCK DIAGRAM OF RB3/CCP1 PIN

TABLE 5-1: TMR1 MODULE AND PORTB OPERATION

| TMR1<br>Module<br>Mode | Clock Source                            | Control Bits                   | TMR1 Module Operation                                                                                                                                                                                                                                         | PORTB<2:1> Operation                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------------|-----------------------------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Off                    | N/A                                     | T1CON =xx 0x00                 | Off                                                                                                                                                                                                                                                           | PORTB<2:1> function as normal I/O                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Timer                  | Fosc/4                                  | T1CON =xx 0x01                 | TMR1 module uses the main oscillator as clock source. TMR1ON can turn on or turn off Timer1.                                                                                                                                                                  | PORTB<2:1> function as normal I/O                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Counter                | External circuit                        | T1CON =xx 0x11<br>TR1SCCP =x-1 | TMR1 module uses the external signal on the RB1/T1OSO/T1CKI pin as a clock source. TMR1ON can turn on or turn off Timer1. DT1CK can read the signal on the RB1/T1OSO/T1CKI pin.                                                                               | PORTB<2> functions as normal I/O. PORTB<1> always reads '0' when configured as input. If PORTB<1> is configured as output, reading PORTB<1> will read the data latch. Writing to PORTB<1> will always store the                                                                                                                                                                                                                                              |

|                        | Firmware T1CON =xx 0x11<br>TR1SCCP =x-0 |                                | DATACCP<0> bit drives RB1/<br>T1OSO/T1CKI and produces<br>the TMR1 clock source.<br>TMR1ON can turn on or turn off<br>Timer1. The DATACCP<0> bit,<br>DT1CK, can read and write to<br>the RB1/T1OSO/T1CKI pin.                                                 | result in the data latch, but not to the RB1/T1OSO/T1CKI pin. If the TMR1CS bit is cleared (TMR1 reverts to the timer mode), then pin PORTB<1> will be driven with the value in the data latch.                                                                                                                                                                                                                                                              |

|                        | Timer1 oscillator                       | T1CON =xx 1x11                 | RB1/T1OSO/T1CKI and RB2/T1OSI are configured as a 2 pin crystal oscillator. RB1/T1OSI/T1CKI is the clock input for TMR1. TMR1ON can turn on or turn off Timer1. DATACCP<1>bit, DT1CK, always reads '0' as input and can not write to the RB1/T1OSO/T1CK1 pin. | PORTB<2:1> always read '0' when configured as inputs. If PORTB<2:1> are configured as outputs, reading PORTB<2:1> will read the data latches. Writing to PORTB<2:1> will always store the result in the data latches, but not to the RB2/T1OSI and RB1/T1OSO/T1CKI pins. If the TMR1CS and T1OSCEN bits are cleared (TMR1 reverts to the timer mode and TMR1 oscillator is disabled), then pin PORTB<2:1> will be driven with the value in the data latches. |

# 7.0 CAPTURE/COMPARE/PWM (CCP) MODULE(S)

Each CCP (Capture/Compare/PWM) module contains a 16-bit register, which can operate as a 16-bit capture register, as a 16-bit compare register or as a PWM master/slave Duty Cycle register. Table 7-1 shows the timer resources of the CCP module modes.

Capture/Compare/PWM Register 1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. All are readable and writable.

Additional information on the CCP module is available in the PIC<sup>®</sup> Mid-Range Reference Manual, (DS33023).

TABLE 7-1: CCP MODE – TIMER RESOURCE

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

### FIGURE 7-1: CCP1CON REGISTER (ADDRESS 17h)

|          |                                                                                                                                                                                                                                 |                                                                                                   |                                                                                                                                         |                                                                                                     | <u> </u>                                                                              |                                          |                        |                                                                             |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------|------------------------|-----------------------------------------------------------------------------|--|--|

| U-0      | U-0                                                                                                                                                                                                                             | R/W-0<br>DC1B1                                                                                    | R/W-0<br>DC1B0                                                                                                                          | R/W-0                                                                                               | R/W-0<br>CCP1M2                                                                       | R/W-0                                    | R/W-0<br>CCP1M0        | R = Readable bit                                                            |  |  |

| bit 7-6: | Unim                                                                                                                                                                                                                            |                                                                                                   |                                                                                                                                         |                                                                                                     | CCF IIVIZ                                                                             | CCPTIVIT                                 | bit0                   | W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR Reset |  |  |

|          | bit 7-6: Unimplemented: Read as '0' bit 5-4: DC1B1:DC1B0: PWM Least Significant bits Capture Mode: Unused Compare Mode: Unused PWM Mode: These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPR1L. |                                                                                                   |                                                                                                                                         |                                                                                                     |                                                                                       |                                          |                        |                                                                             |  |  |

| bit 3-0: | 0000<br>0100<br>0101<br>0110<br>0111<br>1000<br>1001<br>1010                                                                                                                                                                    | = Capture<br>= Capture<br>= Capture<br>= Capture<br>= Capture<br>= Compai<br>= Compai<br>= Compai | e/Compare<br>e mode, ev<br>e mode, ev<br>e mode, ev<br>e mode, ev<br>e mode, s<br>re mode, c<br>e mode, g<br>re mode, t<br>sion (if A/E | very falling of very rising every 4th rising every 16th rise set output occlear output lenerate sof | resets CCP dedge and gedge sing edge an match (CC on match (tware interruial event (C | CP1IF bit is<br>CCP1IF bit iupt on matcl | is set)<br>h (CCP1IF b | it is set, CCP1 pin is unaffected)<br>resets TMR1 and starts an A/D         |  |  |

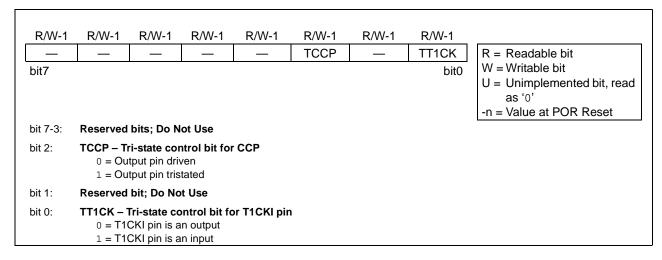

### FIGURE 7-2: TRISCCP REGISTER (ADDRESS 87H)

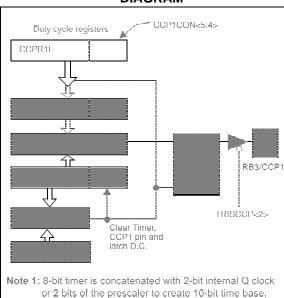

### 7.3 PWM Mode

In Pulse Width Modulation (PWM) mode, the CCP1 pin produces up to a 10-bit resolution PWM output. Since the CCP1 pin is multiplexed with the PORTB data latch, the TRISCCP<2> bit must be cleared to make the CCP1 pin an output.

Note: Clearing the CCP1CON register will force the CCP1 PWM output latch to the default low level. This is neither the PORTB I/O data latch nor the DATACCP latch.

Figure 7-5 shows a simplified block diagram of the CCP module in PWM mode.

For a step by step procedure on how to set up the CCP module for PWM operation, see **Section 7.3.3** "**Set-Up for PWM Operation**".

### FIGURE 7-5: SIMPLIFIED PWM BLOCK DIAGRAM

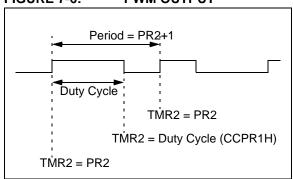

A PWM output (Figure 7-6) has a time base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is the inverse of the period (1/period).

### FIGURE 7-6: PWM OUTPUT

#### 7.3.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula:

PWM period =

$$[(PR2) + 1] \cdot 4 \cdot TOSC \cdot (TMR2 \text{ prescale value})$$

PWM frequency is defined as 1 / [PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP1 pin is set (exception: if PWM duty cycle = 0%, the CCP1 pin will not be set)

- The PWM duty cycle is latched from CCPR1L into CCPR1H

Note: The Timer2 postscaler (see Section 6.0 "Timer2 Module") is not used in the determination of the PWM frequency. The postscaler could be used to have a servo update rate at a different frequency than the PWM output.

### 7.3.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPR1L register and to the CCP1CON<5:4> bits. Up to 10-bit resolution is available. The CCPR1L contains the eight MSbs and the CCP1CON<5:4> contains the two LSbs. This 10-bit value is represented by CCPR1L:CCP1CON<5:4>. The following equation is used to calculate the PWM duty cycle in time:

CCPR1L and CCP1CON<5:4> can be written to at any time, but the duty cycle value is not latched into CCPR1H until after a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPR1H is a read-only register.

The CCPR1H register and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering is essential for glitchless PWM operation.

When the CCPR1H and 2-bit latch match TMR2 concatenated with an internal 2-bit Q clock or 2 bits of the TMR2 prescaler, the CCP1 pin is cleared.

Maximum PWM resolution (bits) for a given PWM frequency:

$$= \frac{\log(\frac{Fosc}{Fpwm})}{\log(2)}$$

bits

**Note:** If the PWM duty cycle value is longer than the PWM period the CCP1 pin will not be cleared.

For an example PWM period and duty cycle calculation, see the PIC<sup>®</sup> Mid-Range Reference Manual, (DS33023).

### FIGURE 8-2: ADCON1 REGISTER (ADDRESS 9Fh)

|     |     |     |     |     | PCFG2 | DCEC1 | DCEC0 |

|-----|-----|-----|-----|-----|-------|-------|-------|

| U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 |

bit7

R = Readable bit

W = Writable bit

bit0

U = Unimplemented bit, read as '0'

-n = Value at POR Reset

bit 7-3: Unimplemented: Read as '0'

bit 2-0: PCFG2:PCFG0: A/D Port Configuration Control bits

| PCFG2:PCFG0 | RA0 | RA1 | RA2 | RA3  | VREF |

|-------------|-----|-----|-----|------|------|

| 0x0         | Α   | Α   | Α   | Α    | Vdd  |

| 0x1         | Α   | Α   | Α   | VREF | RA3  |

| 100         | Α   | Α   | D   | Α    | VDD  |

| 101         | Α   | Α   | D   | VREF | RA3  |

| 11x         | D   | D   | D   | D    | Vdd  |

A = Analog input

D = Digital I/O

### 9.9 Power Control/Status Register (PCON)

The Power Control/Status Register, PCON has two bits.

Bit 0 is Brown-out Reset Status bit, BOR. If the BODEN Configuration bit is set, BOR is '1' on Power-on Reset. If the BODEN Configuration bit is clear, BOR is unknown on Power-on Reset.

The BOR Status bit is a "don't care" and is not necessarily predictable if the brown-out circuit is disabled (the BODEN Configuration bit is clear). BOR must then be set by the user and checked on subsequent Resets to see if it is clear, indicating a brown-out has occurred.

Bit 1 is POR (Power-on Reset Status bit). It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

TABLE 9-3: TIME-OUT IN VARIOUS SITUATIONS

| Oscillator Configuration | Power            | -up       | Brown-out        | Wake-up from |  |

|--------------------------|------------------|-----------|------------------|--------------|--|

| Oscillator Configuration | PWRTE = 0        | PWRTE = 1 | Brown-out        | Sleep        |  |

| XT, HS, LP               | 72 ms + 1024Tosc | 1024Tosc  | 72 ms + 1024Tosc | 1024Tosc     |  |

| RC                       | 72 ms            |           | 72 ms            | _            |  |

TABLE 9-4: STATUS BITS AND THEIR SIGNIFICANCE

| POR | BOR | TO | PD |                                                         |

|-----|-----|----|----|---------------------------------------------------------|

| 0   | х   | 1  | 1  | Power-on Reset                                          |

| 0   | х   | 0  | х  | Illegal, TO is set on POR                               |

| 0   | х   | х  | 0  | Illegal, PD is set on POR                               |

| 1   | 0   | 1  | 1  | Brown-out Reset                                         |

| 1   | 1   | 0  | 1  | WDT Reset                                               |

| 1   | 1   | 0  | 0  | WDT Wake-up                                             |

| 1   | 1   | u  | u  | MCLR Reset during normal operation                      |

| 1   | 1   | 1  | 0  | MCLR Reset during Sleep or interrupt wake-up from Sleep |

TABLE 9-5: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uu               |

| MCLR Reset during Sleep            | 000h                  | 0001 0uuu          | uu               |

| WDT Reset                          | 000h                  | 0000 1uuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | uu               |

| Brown-out Reset                    | 000h                  | 0001 1uuu          | u0               |

| Interrupt wake-up from Sleep       | PC + 1 <sup>(1)</sup> | uuu1 0uuu          | uu               |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit read as '0'.

**Note 1:** When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

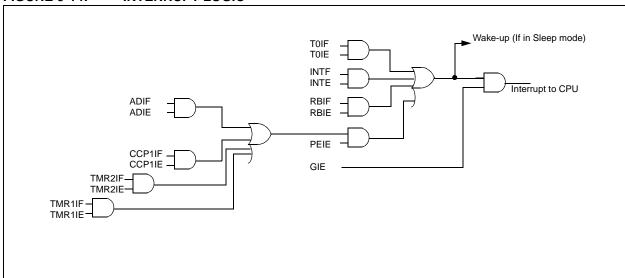

### 9.10 Interrupts

The PIC16C712/716 devices have up to 7 sources of interrupt. The Interrupt Control Register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

**Note:** Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

A Global Interrupt Enable bit, GIE (INTCON<7>) enables (if set) all unmasked interrupts or disables (if cleared) all interrupts. When bit GIE is enabled, and an interrupt's flag bit and mask bit are set, the interrupt will vector immediately. Individual interrupts can be disabled through their corresponding enable bits in various registers. Individual interrupt bits are set, regardless of the status of the GIE bit. The GIE bit is cleared on Reset.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine, as well as sets the GIE bit, which re-enables interrupts.

The RB0/INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flags are contained in the Special Function Registers, PIR1 and PIR2. The corresponding interrupt enable bits are contained in Special Function Registers, PIE1 and PIE2, and the peripheral interrupt enable bit is contained in Special Function Register, INTCON.

When an interrupt is responded to, the GIE bit is cleared to disable any further interrupt, the return address is pushed onto the stack and the PC is loaded with 0004h. Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs. The latency is the same for one or two cycle instructions. Individual interrupt flag bits are set, regardless of the status of their corresponding mask bit or the GIE bit.

FIGURE 9-14: INTERRUPT LOGIC

## 12.1 DC Characteristics: PIC16C712/716-04 (Commercial, Industrial, Extended) PIC16C712/716-20 (Commercial, Industrial, Extended)

| DC CHARACTERISTICS    |                | Standard Operating Co<br>Operating temperature                                                                                                   |                     |                           | 0°<br>-40°<br>-40°   | C ≤ Ta ≤ +85°C for industrial |                                                                                                                                                                   |  |  |

|-----------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------------|----------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Param<br>No.          | Sym.           | Characteristic                                                                                                                                   | Min.                | Тур†                      | Max.                 | Units                         | Conditions                                                                                                                                                        |  |  |

| D001<br>D001A         | VDD            | Supply Voltage                                                                                                                                   | 4.0<br>4.5<br>VBOR* |                           | 5.5<br>5.5<br>5.5    | V<br>V<br>V                   | XT, RC and LP osc mode HS osc mode BOR enabled <sup>(7)</sup>                                                                                                     |  |  |

| D002*                 | VDR            | RAM Data Retention Voltage <sup>(1)</sup>                                                                                                        | _                   | 1.5                       | _                    | V                             |                                                                                                                                                                   |  |  |

| D003                  | VPOR           | VDD Start Voltage to ensure internal Power-on Reset signal                                                                                       | _                   | Vss                       | _                    | V                             | See section on Power-on Reset for details                                                                                                                         |  |  |

| D004*<br>D004A*       | SVDD           | VDD Rise Rate to ensure internal<br>Power-on Reset signal                                                                                        | 0.05<br>TBD         | _                         | _                    | V/ms                          | PWRT enabled (PWRTE bit clear) PWRT disabled (PWRTE bit set) See section on Power-on Reset for details                                                            |  |  |

| D005                  | VBOR           | Brown-out Reset<br>voltage trip point                                                                                                            | 3.65                | _                         | 4.35                 | V                             | BODEN bit set                                                                                                                                                     |  |  |

| D010<br>D013          | IDD            | Supply Current <sup>(2,5)</sup>                                                                                                                  |                     | 0.8<br>4.0                | 2.5<br>8.0           | mA<br>mA                      | FOSC = 4 MHz, VDD = 4.0V<br>FOSC = 20 MHz, VDD = 4.0V                                                                                                             |  |  |

| D020<br>D021<br>D021B | IPD            | Power-down Current <sup>(3,5)</sup>                                                                                                              | _<br>_<br>_<br>_    | 10.5<br>1.5<br>1.5<br>2.5 | 42<br>16<br>19<br>19 | μΑ<br>μΑ<br>μΑ<br>μΑ          | VDD = 4.0V, WDT enabled, -40°C to +85°C VDD = 4.0V, WDT disabled, 0°C to +70°C VDD = 4.0V, WDT disabled, -40°C to +85°C VDD = 4.0V, WDT disabled, -40°C to +125°C |  |  |

| D022*<br>D022A*       | Δlwdt<br>Δlbor | Module Differential Current <sup>(6)</sup> Watchdog Timer Brown-out Reset                                                                        |                     | 6.0<br>TBD                | 20<br>200            | μ <b>Α</b><br>μ <b>Α</b>      | WDTE bit set, VDD = 4.0V<br>BODEN bit set, VDD = 5.0V                                                                                                             |  |  |

| 1A                    | Fosc           | LP Oscillator Operating Frequency<br>RC Oscillator Operating Frequency<br>XT Oscillator Operating Frequency<br>HS Oscillator Operating Frequency | 0<br>0<br>0<br>0    | _<br>_<br>_<br>_          | 200<br>4<br>4<br>20  | KHz<br>MHz<br>MHz<br>MHz      | All temperatures All temperatures All temperatures All temperatures                                                                                               |  |  |

<sup>\*</sup> These parameters are characterized but not tested.

Note1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD,

MCLR = VDD; WDT enabled/disabled as specified.

- 3: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD and Vss.

- 4: For RC Osc mode, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kOhm.

- 5: Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: This is the voltage where the device enters the Brown-out Reset. When BOR is enabled, the device will operate correctly to this trip point.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

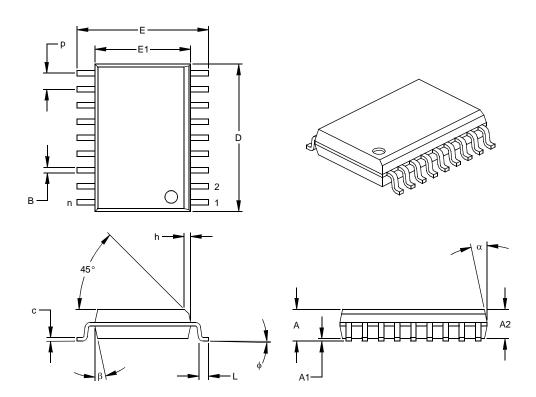

### 18-Lead Plastic Small Outline (SO) - Wide, 300 mil (SOIC)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          |     | INCHES* |      | MILLIMETERS |       |       |       |

|--------------------------|-----|---------|------|-------------|-------|-------|-------|

| Dimension                | MIN | NOM     | MAX  | MIN         | NOM   | MAX   |       |

| Number of Pins           | n   |         | 18   |             |       | 18    |       |

| Pitch                    | р   |         | .050 |             |       | 1.27  |       |

| Overall Height           | Α   | .093    | .099 | .104        | 2.36  | 2.50  | 2.64  |

| Molded Package Thickness | A2  | .088    | .091 | .094        | 2.24  | 2.31  | 2.39  |

| Standoff §               | A1  | .004    | .008 | .012        | 0.10  | 0.20  | 0.30  |

| Overall Width            | Е   | .394    | .407 | .420        | 10.01 | 10.34 | 10.67 |

| Molded Package Width     | E1  | .291    | .295 | .299        | 7.39  | 7.49  | 7.59  |

| Overall Length           | D   | .446    | .454 | .462        | 11.33 | 11.53 | 11.73 |

| Chamfer Distance         | h   | .010    | .020 | .029        | 0.25  | 0.50  | 0.74  |

| Foot Length              | L   | .016    | .033 | .050        | 0.41  | 0.84  | 1.27  |

| Foot Angle               | ф   | 0       | 4    | 8           | 0     | 4     | 8     |

| Lead Thickness           | С   | .009    | .011 | .012        | 0.23  | 0.27  | 0.30  |

| Lead Width               | В   | .014    | .017 | .020        | 0.36  | 0.42  | 0.51  |

| Mold Draft Angle Top     | α   | 0       | 12   | 15          | 0     | 12    | 15    |

| Mold Draft Angle Bottom  | β   | 0       | 12   | 15          | 0     | 12    | 15    |

<sup>\*</sup> Controlling Parameter

#### Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010" (0.254mm) per side. JEDEC Equivalent: MS-013

Drawing No. C04-051

<sup>§</sup> Significant Characteristic

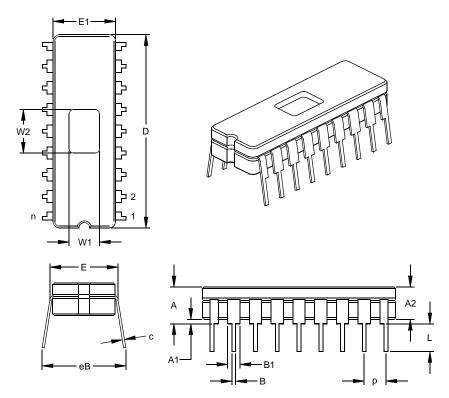

### 18-Lead Ceramic Dual In-line with Window (JW) - 300 mil (CERDIP)

For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | INCHES* |      |      | MILLIMETERS |       |       |       |

|----------------------------|---------|------|------|-------------|-------|-------|-------|

| Dimensio                   | MIN     | NOM  | MAX  | MIN         | NOM   | MAX   |       |

| Number of Pins             | n       |      | 18   |             |       | 18    |       |

| Pitch                      | р       |      | .100 |             |       | 2.54  |       |

| Top to Seating Plane       | Α       | .170 | .183 | .195        | 4.32  | 4.64  | 4.95  |

| Ceramic Package Height     | A2      | .155 | .160 | .165        | 3.94  | 4.06  | 4.19  |

| Standoff                   | A1      | .015 | .023 | .030        | 0.38  | 0.57  | 0.76  |

| Shoulder to Shoulder Width | Е       | .300 | .313 | .325        | 7.62  | 7.94  | 8.26  |

| Ceramic Pkg. Width         | E1      | .285 | .290 | .295        | 7.24  | 7.37  | 7.49  |

| Overall Length             | D       | .880 | .900 | .920        | 22.35 | 22.86 | 23.37 |

| Tip to Seating Plane       | L       | .125 | .138 | .150        | 3.18  | 3.49  | 3.81  |

| Lead Thickness             | С       | .008 | .010 | .012        | 0.20  | 0.25  | 0.30  |

| Upper Lead Width           | B1      | .050 | .055 | .060        | 1.27  | 1.40  | 1.52  |

| Lower Lead Width           | В       | .016 | .019 | .021        | 0.41  | 0.47  | 0.53  |

| Overall Row Spacing §      | eВ      | .345 | .385 | .425        | 8.76  | 9.78  | 10.80 |

| Window Width               | W1      | .130 | .140 | .150        | 3.30  | 3.56  | 3.81  |

| Window Length W            |         | .190 | .200 | .210        | 4.83  | 5.08  | 5.33  |

<sup>\*</sup> Controlling Parameter § Significant Characteristic JEDEC Equivalent: MO-036 Drawing No. C04-010

### **INDEX**

| A                                                 |        | Enable (CCP1IE Bit)                            |         |    |

|---------------------------------------------------|--------|------------------------------------------------|---------|----|

| A/D                                               | 45     | Flag (CCP1IF Bit)                              |         | 17 |

| A/D Converter Enable (ADIE Bit)                   |        | PWM Mode. See PWM                              |         |    |

| A/D Converter Flag (ADIF Bit)                     |        | Timer Resources                                |         | 39 |

| A/D Converter Interrupt, Configuring              |        | Timing Diagram                                 |         | 85 |

| ADCON0 Register                                   |        | CCP1CON Register                               |         | 39 |

| ADCON1 Register                                   |        | CCP1M3:CCP1M0 Bits                             |         | 39 |

| ADRES Register                                    |        | CCP1X:CCP1Y Bits                               |         | 39 |

|                                                   |        | Code Protection                                | 51,     | 65 |

| Analog Port Pins, Configuring                     |        | CP1:CP0 Bits                                   |         | 52 |

| Block Diagram Analog Innut Model                  |        | Compare (CCP Module)                           |         |    |

| Block Diagram, Analog Input Model                 |        | Block Diagram                                  |         |    |

| Channel Select (CHS2:CHS0 Bits)                   |        | CCP Pin Configuration                          |         |    |

| Clock Select (ADCS1:ADCS0 Bits)                   |        | CCPR1H:CCPR1L Registers                        |         |    |

| Configuring the Module                            |        | Software Interrupt                             |         |    |

| Conversion Clock (Tad)                            |        | Special Event Trigger                          |         |    |

| Conversion Status (GO/DONE Bit)                   |        | Timer1 Mode Selection                          |         |    |

| Conversions                                       |        | Configuration Bits                             |         |    |

| Converter Characteristics                         |        | Conversion Considerations                      |         |    |

| Module On/Off (ADON Bit)                          |        | Customer Change Notification Service           |         |    |

| Port Configuration Control (PCFG2:PCFG0           |        | Customer Notification Service                  |         |    |

| Sampling Requirements                             |        |                                                |         |    |

| Special Event Trigger (CCP)                       | 41, 50 | Customer Support                               | 1       | UI |

| Timing Diagram                                    | 87     | D                                              |         |    |

| Absolute Maximum Ratings                          | 73     | Poto Momoni                                    |         | 40 |

| ADCON0 Register                                   | 11, 45 | Data Memory                                    |         |    |

| ADCS1:ADCS0 Bits                                  |        | Bank Select (RP1:RP0 Bits)                     |         |    |

| ADON Bit                                          | 45     | General Purpose Registers                      |         |    |

| CHS2:CHS0 Bits                                    | 45     | Register File Map                              |         |    |

| GO/DONE Bit                                       |        | Special Function Registers                     |         |    |

| ADCON1 Register                                   | •      | DC Characteristics                             |         |    |

| PCFG2:PCFG0 Bits                                  |        | Development Support                            |         |    |

| ADRES Register                                    |        | Direct Addressing                              |         | 20 |

| Analog-to-Digital Converter. See A/D Architecture |        | E                                              |         |    |

| PIC16C712/716 Block Diagram                       |        | <del>-</del>                                   |         |    |

| Assembler                                         |        | Electrical Characteristics                     |         |    |

| MPASM Assembler                                   | 70     | Errata                                         |         |    |

| WII AGWI AGGCIIIDIGI                              | 70     | External Power-on Reset Circuit                |         | 55 |

| В                                                 |        | F                                              |         |    |

| Banking, Data Memory                              | 10 13  | •                                              |         |    |

| BOR. See Brown-out Reset                          | 10, 13 | Family of Devices                              |         |    |

| Brown-Out Reset (BOR)                             | 55     | PIC16C7XX                                      |         |    |

| Brown-out Reset (BOR)                             |        | Firmware Instructions                          |         | 67 |

| BOR Enable (BODEN Bit)                            |        | 1                                              |         |    |

|                                                   |        | 1                                              |         |    |

| BOR Status (BOR Bit)                              |        | I/O Ports                                      |         |    |

| Timing Diagram                                    | 83     | ID Locations                                   | 51,     | 65 |

| C                                                 |        | In-Circuit Serial Programming™ (ICSP™)         | 51,     | 65 |

|                                                   |        | Indirect Addressing                            |         | 20 |

| C Compilers                                       | 70     | FSR Register                                   | 10, 11, | 20 |

| MPLAB C18                                         | _      | INDF Register                                  |         | 11 |

| MPLAB C30                                         |        | Instruction Format                             |         |    |

| Capture (CCP Module)                              |        | Instruction Set                                |         | 67 |

| Block Diagram                                     |        | Summary Table                                  |         | 68 |

| CCP Pin Configuration                             | 40     | INT Interrupt (RB0/INT). See Interrupt Sources |         |    |

| CCPR1H:CCPR1L Registers                           | 40     | INTCON Register                                | 11.     | 15 |

| Changing Between Capture Prescalers               | 40     | GIE Bit                                        |         |    |

| Software Interrupt                                |        | INTE Bit                                       |         |    |

| Timer1 Mode Selection                             | 40     | INTF Bit                                       |         |    |

| Capture/Compare/PWM (CCP)                         | 39     | PEIE Bit                                       |         |    |

| Capture Mode. See Capture                         |        | RBIE Bit                                       |         |    |

| CCP1CON Register                                  | 11, 39 | RBIF Bit                                       |         |    |

| CCPR1H Register                                   |        | TOIE Bit                                       | ,       |    |

| CCPR1L Register                                   |        |                                                |         |    |

| Compare Mode. See Compare                         | •      | TOIF Bit                                       |         |    |

| •                                                 |        | Internet Address                               | 1       | UI |

| PORTC                                    | Brown-out Reset (BOR). See Brown-out Reset (BOR) |            |

|------------------------------------------|--------------------------------------------------|------------|

| TRISC Register 12                        | MCLR Reset. See MCLR                             |            |

| Postscaler, Timer2                       | Power-on Reset (POR). See Power-on Reset (POR)   |            |

| Select (TOUTPS3:TOUTPS0 Bits)            | Reset Conditions for All Registers 5             | 59         |

| Postscaler, WDT                          | Reset Conditions for PCON Register 5             | 58         |

| Assignment (PSA Bit) 14, 29              | Reset Conditions for Program Counter5            |            |

| Block Diagram30                          | Reset Conditions for STATUS Register 5           |            |

| Rate Select (PS2:PS0 Bits) 14, 29        | Timing Diagram8                                  |            |

| Switching Between Timer0 and WDT 30      | WDT Reset. See Watchdog Timer (WDT)              |            |

| Power-down Mode. See Sleep               | Revision History9                                | <b>)</b> 5 |

| Power-on Reset (POR) 51, 54, 55, 58, 59  | ·                                                |            |

| Oscillator Start-up Timer (OST)          | S                                                |            |

| POR Status (POR Bit)                     | Sleep 6                                          | 34         |

| Power Control (PCON) Register 58         | Sleep                                            |            |

| Power-down (PD Bit)                      | Software Simulator (MPLAB SIM)                   |            |

| Power-on Reset Circuit, External         | Special Event Trigger. See Compare               | ٠          |

| ·                                        | Special Features of the CPU                      | <b>5</b> 1 |

| Power-up Timer (PWRT) 51, 55             | Special Function Registers                       |            |

| PWRT Enable (PWRTE Bit)                  |                                                  |            |

| Time-out (TO Bit)                        | Speed, Operating                                 |            |

| Time-out Sequence 57                     | Stack                                            |            |

| Time-out Sequence on Power-up 60         | STATUS Register 11, 13, 6                        |            |

| Timing Diagram 83                        | C Bit                                            |            |

| Prescaler, Capture 40                    | DC Bit 1                                         |            |

| Prescaler, Timer0                        | <u>IRP</u> Bit 1                                 | 13         |

| Assignment (PSA Bit) 14, 29              | PD Bit 13, 5                                     |            |

| Block Diagram 30                         | RP1:RP0 Bits 1                                   | 13         |

| Rate Select (PS2:PS0 Bits) 14, 29        | TO Bit 13, 5                                     | 54         |

| Switching Between Timer0 and WDT 30      | Z Bit 1                                          | 13         |

| Prescaler, Timer1                        | <u> </u>                                         |            |

| Select (T1CKPS1:T1CKPS0 Bits)            | Т                                                |            |

| Prescaler, Timer2                        | T1CON Register 11, 3                             | 31         |

| Select (T2CKPS1:T2CKPS0 Bits)            | T1CKPS1:T1CKPS0 Bits                             |            |

|                                          | T1OSCEN Bit                                      |            |

| Product Identification System            | T1SYNC Bit                                       |            |

| Program Counter                          | TMR1CS Bit                                       |            |

| PCL Register                             | TMR1ON Bit                                       |            |

| PCLATH Register 11, 19, 62               |                                                  |            |

| Reset Conditions 58                      | T2CON Register                                   |            |

| Program Memory 9                         | T2CKPS1:T2CKPS0 Bits                             |            |

| Interrupt Vector9                        | TMR2ON Bit                                       |            |

| Paging 9, 19                             | TOUTPS3:TOUTPS0 Bits                             |            |

| Program Memory Map 9                     | Timer0 2                                         |            |

| Reset Vector 9                           | Block Diagram2                                   |            |

| Program Verification 65                  | Clock Source Edge Select (T0SE Bit) 14, 2        | 29         |

| Programming, Device Instructions 67      | Clock Source Select (T0CS Bit) 14, 2             | 29         |

| PWM (CCP Module) 42                      | Overflow Enable (T0IE Bit) 1                     | 5          |

| Block Diagram 42                         | Overflow Flag (T0IF Bit) 15, 6                   | 32         |

| CCPR1H:CCPR1L Registers                  | Overflow Interrupt                               | 32         |

| Duty Cycle                               | Prescaler. See Prescaler, Timer0                 |            |

| Example Frequencies/Resolutions          | Timing Diagram 8                                 | 34         |

|                                          | TMR0 Register 1                                  |            |

| Output Diagram                           | Timer1                                           |            |

| Period                                   | Block Diagram                                    |            |

| Set-Up for PWM Operation                 | Capacitor Selection                              |            |

| TMR2 to PR2 Match                        |                                                  |            |

| TMR2 to PR2 Match Enable (TMR2IE Bit) 16 | Clock Source Select (TMR1CS Bit)                 |            |

| TMR2 to PR2 Match Flag (TMR2IF Bit)17    | External Clock Input Sync (T1SYNC Bit)           |            |

| 0                                        | Module On/Off (TMR1ON Bit)                       |            |

| Q                                        | Oscillator                                       |            |

| Q-Clock                                  | Oscillator Enable (T1OSCEN Bit)                  |            |

| R                                        | Overflow Enable (TMR1IE Bit) 1                   |            |

|                                          | Overflow Flag (TMR1IF Bit)1                      |            |

| RAM. See Data Memory                     | Overflow Interrupt 31, 3                         | 34         |

| Reader Response                          | Prescaler. See Prescaler, Timer1                 |            |

| Register File                            | Special Event Trigger (CCP)                      | ļ1         |

| Register File Map 10                     | T1CON Register 11, 3                             |            |

| Reset51, 54                              | Timing Diagram 8                                 |            |

| Block Diagram56                          | TMR1H Register                                   |            |

| 5                                        |                                                  |            |

### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our

knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data

Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not

mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### **Trademarks**

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MTP, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

Analog-for-the-Digital Age, Application Maestro, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, SQI, Serial Quad I/O, Total Endurance, TSHARC, UniWinDriver, WiperLock, ZENA and Z-Scale are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

GestIC and ULPP are registered trademarks of Microchip Technology Germany II GmbH & Co. & KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 1999-2013, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

ISBN: 9781620769751

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.