Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detuils                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 13                                                                        |

| Program Memory Size        | 3.5КВ (2К х 14)                                                           |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                 |

| Data Converters            | A/D 4x8b                                                                  |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 18-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c716-20i-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

| 1.0   | Device Overview                          | 5  |

|-------|------------------------------------------|----|

| 2.0   | Memory Organization                      | 9  |

| 3.0   | I/O Ports                                | 21 |

| 4.0   | I/O Ports<br>Timer0 Module               | 29 |

| 5.0   | Timer1 Module                            |    |

| 6.0   | Timer2 Module                            | 36 |

| 7.0   | Capture/Compare/PWM (CCP) Module(s)      | 39 |

| 8.0   | Analog-to-Digital Converter (A/D) Module | 45 |

| 9.0   | Special Features of the CPU              | 51 |

| 10.0  | Instruction Set Summary                  | 67 |

| 11.0  | Development Support.                     | 69 |

| 12.0  | Electrical Characteristics               | 73 |

| 13.0  | Packaging Information                    | 89 |

| Revis | ion History                              | 95 |

| Conv  | ersion Considerations                    | 95 |

| Migra | tion from Base-line to Mid-Range Devices | 95 |

| Index |                                          | 97 |

| On-Li | ne Support1                              | 01 |

| Read  | ne Support1<br>er Response               | 02 |

|       | SC712/716 Product Identification System  |    |

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

| Pin                       | PIC16C    | 712/716 | Pin        | Buffer    |                                                                                                               |

|---------------------------|-----------|---------|------------|-----------|---------------------------------------------------------------------------------------------------------------|

| Name                      | DIP, SOIC | SSOP    | Туре       | Туре      | Description                                                                                                   |

|                           |           |         |            |           | PORTB is a bidirectional I/O port. PORTB can be software programmed for internal weak pull-ups on all inputs. |

| RB0/INT<br>RB0<br>INT     | 6         | 7       | I/O<br>I   | TTL<br>ST | Digital I/O<br>External Interrupt                                                                             |

| RB1/T1OSO/T1CKI<br>RB1    | 7         | 8       |            |           |                                                                                                               |

| T1OSO<br>T1CKI            |           |         | I/O<br>O   | TTL       | Digital I/O<br>Timer1 oscillator output. Connects to                                                          |

|                           |           | _       | I          | ST        | crystal in oscillator mode.<br>Timer1 external clock input.                                                   |

| RB2/T1OSI<br>RB2<br>T1OSI | 8         | 9       | I/O<br>I   | TTL<br>—  | Digital I/O<br>Timer1 oscillator input. Connects to<br>crystal in oscillator mode.                            |

| RB3/CCP1<br>RB3<br>CCP1   | 9         | 10      | I/O<br>I/O | TTL<br>ST | Digital I/O<br>Capture1 input, Compare1 output,<br>PWM1 output.                                               |

| RB4                       | 10        | 12      | I/O        | TTL       | Digital I/O<br>Interrupt on change pin.                                                                       |

| RB5                       | 11        | 12      | I/O        | TTL       | Digital I/O<br>Interrupt on change pin.                                                                       |

| RB6                       | 12        | 13      | I/O        | TTL       | Digital I/O<br>Interrupt on change pin.                                                                       |

| RB7                       | 13        | 14      | l<br>I/O   | ST<br>TTL | ICSP programming clock.<br>Digital I/O                                                                        |

|                           |           |         | I/O        | ST        | Interrupt on change pin.<br>ICSP programming data.                                                            |

| Vss                       | 5         | 5, 6    | Р          | —         | Ground reference for logic and I/O pins.                                                                      |

| Vdd                       | 14        | 15, 16  | Р          | _         | Positive supply for logic and I/O pins.                                                                       |

| TABLE 1-1: | PIC16C712/716 PINOUT DESCRIPTION (CONTINUE) | D) |

|------------|---------------------------------------------|----|

|            |                                             | -, |

**Legend:** TTL = TTL-compatible input CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels

OD = Open drain output

SM = SMBus compatible input. An external resistor is required if this pin is used as an output

NPU = N-channel pull-up PU = Weak internal pull-up

No-P diode = No P-diode to VDD AN = Analog input or output

I = input O = output

P = Power L = LCD Driver

| Addr    | Name                    | Bit 7                                | Bit 6                                                  | Bit 5        | Bit 4           | Bit 3         | Bit 2           | Bit 1         | Bit 0     | Value on:<br>POR,<br>BOR | Value on<br>all other<br>Resets (4) |

|---------|-------------------------|--------------------------------------|--------------------------------------------------------|--------------|-----------------|---------------|-----------------|---------------|-----------|--------------------------|-------------------------------------|

| Bank 1  |                         |                                      |                                                        |              |                 |               |                 |               |           |                          |                                     |

| 80h     | INDF <sup>(1)</sup>     | Addressing                           | this location                                          | uses conten  | ts of FSR to ac | ldress data r | nemory (not     | a physical re | gister)   | 0000 0000                | 0000 0000                           |

| 81h     | OPTION_<br>REG          | RBPU                                 | INTEDG                                                 | TOCS         | TOSE            | PSA           | 1111 1111       | 1111 1111     |           |                          |                                     |

| 82h     | PCL <sup>(1)</sup>      | Program Co                           | ounter's (PC)                                          | Least Signif | ficant Byte     |               |                 | 0000 0000     | 0000 0000 |                          |                                     |

| 83h     | STATUS <sup>(1)</sup>   | IRP <sup>(4)</sup>                   | RP1 <sup>(4)</sup>                                     | RP0          | TO              | PD            | Z               | DC            | С         | rr01 1xxx                | rr0q quuu                           |

| 84h     | FSR <sup>(1)</sup>      | Indirect Data Memory Address Pointer |                                                        |              |                 |               |                 |               |           | xxxx xxxx                | uuuu uuuu                           |

| 85h     | TRISA                   | -                                    | — — — — ( <sup>7</sup> ) PORTA Data Direction Register |              |                 |               |                 |               |           | x1 1111                  | x1 1111                             |

| 86h     | TRISB                   | PORTB Data Direction Register        |                                                        |              |                 |               |                 |               |           | 1111 1111                | 1111 1111                           |

| 87h     | TRISCCP                 | (7)                                  | (7)(7)(7)(7)(7) TCCP(7) TT1CK                          |              |                 |               |                 |               |           | xxxx x1x1                | xxxx x1x1                           |

| 88h-89h | _                       | Unimpleme                            | nted                                                   |              |                 |               |                 |               |           | -                        | -                                   |

| 8Ah     | PCLATH <sup>(1,2)</sup> | _                                    | _                                                      | _            | Write Buffer fo | or the upper  | 5 bits of the F | Program Cou   | inter     | 0 0000                   | 0 0000                              |

| 8Bh     | INTCON <sup>(1)</sup>   | GIE                                  | PEIE                                                   | TOIE         | INTE            | RBIE          | T0IF            | INTF          | RBIF      | 0000 000x                | 0000 000u                           |

| 8Ch     | PIE1                    | _                                    | ADIE                                                   | _            | _               | —             | CCP1IE          | TMR2IE        | TMR1IE    | -0000                    | -0000                               |

| 8Dh     | _                       | Unimpleme                            | nted                                                   |              |                 |               |                 |               |           | -                        | -                                   |

| 8Eh     | PCON                    | _                                    | _                                                      | _            | _               | —             | _               | POR           | BOR       | dd                       | uu                                  |

| 8Fh-91h | _                       | Unimpleme                            | nted                                                   |              |                 |               |                 |               |           | -                        | -                                   |

| 92h     | PR2                     | Timer2 Peri                          | od Register                                            |              |                 |               |                 |               |           | 1111 1111                | 1111 1111                           |

| 93h-9Eh | _                       | Unimpleme                            | nted                                                   |              |                 |               |                 |               |           | -                        | -                                   |

| 9Fh     | ADCON1                  | _                                    | _                                                      | —            | _               | —             | PCFG2           | PCFG1         | PCFG0     | 000                      | 000                                 |

#### TABLE 2-1: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend: x = unknown, u = unchanged, q = value depends on condition, — = unimplemented, read as '0',

Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from either bank.

2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for PC<12:8> whose contents are transferred to the upper byte of the program counter.

3: Other (non Power-up) Resets include: external Reset through MCLR and the Watchdog Timer Reset.

4: The IRP and RP1 bits are reserved. Always maintain these bits clear.

5: On any device Reset, these pins are configured as inputs.

**6:** This is the value that will be in the port output latch.

7: Reserved bits; Do Not Use.

#### 2.2.2.4 PIE1 Register

This register contains the individual enable bits for the peripheral interrupts.

Note: Bit PEIE (INTCON<6>) must be set to enable any peripheral interrupt.

### FIGURE 2-7: PIE1 REGISTER (ADDRESS 8Ch)

| U-0      | R/W-0                                                                                                                                                 | U-0        | U-0         | R/W-0 | R/W-0  | R/W-0  | R/W-0  |                                                                                      |  |  |  |  |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------|-------|--------|--------|--------|--------------------------------------------------------------------------------------|--|--|--|--|--|

|          | ADIE                                                                                                                                                  | —          |             | —     | CCP1IE | TMR2IE | TMR1IE | R = Readable bit                                                                     |  |  |  |  |  |

| bit7     |                                                                                                                                                       |            |             |       |        |        | bit0   | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>-n = Value at POR Reset |  |  |  |  |  |

| bit 7:   | Unimpler                                                                                                                                              | nented: R  | ead as '0   | ,     |        |        |        |                                                                                      |  |  |  |  |  |

| bit 6:   | ADIE: A/E<br>1 = Enabl<br>0 = Disab                                                                                                                   | es the A/E | ) interrupt |       | bit    |        |        |                                                                                      |  |  |  |  |  |

| bit 5-3: | -3: Unimplemented: Read as '0'                                                                                                                        |            |             |       |        |        |        |                                                                                      |  |  |  |  |  |

| bit 2:   | CCP1IE: CCP1 Interrupt Enable bit<br>1 = Enables the CCP1 interrupt<br>0 = Disables the CCP1 interrupt                                                |            |             |       |        |        |        |                                                                                      |  |  |  |  |  |

| bit 1:   | <b>TMR2IE</b> : TMR2 to PR2 Match Interrupt Enable bit<br>1 = Enables the TMR2 to PR2 match interrupt<br>0 = Disables the TMR2 to PR2 match interrupt |            |             |       |        |        |        |                                                                                      |  |  |  |  |  |

| bit 0:   |                                                                                                                                                       |            |             |       |        |        |        |                                                                                      |  |  |  |  |  |

|          |                                                                                                                                                       |            |             |       |        |        |        |                                                                                      |  |  |  |  |  |

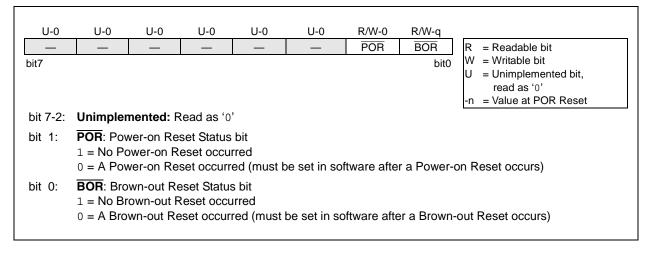

#### 2.2.2.6 PCON Register

The Power Control (PCON) register contains a flag bit to allow differentiation between a Power-on Reset (POR) to an external MCLR Reset or WDT Reset. These devices contain an additional bit to differentiate a Brown-out Reset condition from a Power-on Reset condition. Note: If the BODEN Configuration bit is set, BOR is '1' on Power-on Reset. If the BODEN Configuration bit is clear, BOR is unknown on Power-on Reset. The BOR Status bit is a "don't care" and is

not necessarily predictable if the brown-out circuit is disabled (the BODEN Configuration bit is clear). BOR must then be set by the user and checked on subsequent resets to see if it is clear, indicating a brown-out has occurred.

#### FIGURE 2-9: PCON REGISTER (ADDRESS 8Eh)

### 2.3 PCL and PCLATH

The Program Counter (PC) specifies the address of the instruction to fetch for execution. The PC is 13 bits wide. The low byte is called the PCL register. This register is readable and writable. The high byte is called the PCH register. This register contains the PC<12:8> bits and is not directly readable or writable. All updates to the PCH register go through the PCLATH register.

#### 2.3.1 STACK

The stack allows a combination of up to 8 program calls and interrupts to occur. The stack contains the return address from this branch in program execution.

Mid-range devices have an 8-level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the Stack Pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not modified when the stack is PUSHed or POPed.

After the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

### 2.4 Program Memory Paging

The CALL and GOTO instructions provide 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction, the upper bit of the address is provided by PCLATH<3>. When doing a CALL or GOTO instruction, the user must ensure that the page select bit is programmed so that the desired program memory page is addressed. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is pushed onto the stack. Therefore, manipulation of the PCLATH<3> bit is not required for the return instructions (which POPs the address from the stack).

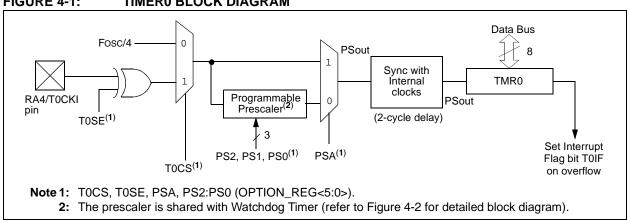

#### 4.0 **TIMER0 MODULE**

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- · Internal or external clock select

- Edge select for external clock

- 8-bit software programmable prescaler

- · Interrupt on overflow from FFh to 00h

Figure 4-1 is a simplified block diagram of the Timer0 module.

Additional information on timer modules is available in the PIC<sup>®</sup> Mid-Range Reference Manual, (DS33023).

#### 4.1 **Timer0** Operation

Timer0 can operate as a timer or as a counter.

Timer mode is selected by clearing bit T0CS (OPTION\_REG<5>). In timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting bit T0CS (OPTION\_REG<5>). In Counter mode, Timer0 will increment on every rising or falling edge of pin RA4/ T0CKI. The incrementing edge is determined by the Edge Select Timer0 Source bit TOSE (OPTION\_REG<4>). Clearing bit T0SE selects the rising edge. Restrictions on the external clock input are discussed below.

When an external clock input is used for Timer0, it must meet certain requirements. The requirements ensure the external clock can be synchronized with the internal phase clock (Tosc). Also, there is a delay in the actual incrementing of Timer0 after synchronization.

Additional information on external clock requirements is available in the PIC<sup>®</sup> Mid-Range Reference Manual, (DS33023).

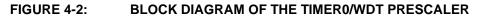

#### 4.2 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module or as a postscaler for the Watchdog Timer, respectively (Figure 4-2). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that there is only one prescaler available, which is mutually exclusively shared between the Timer0 module and the Watchdog Timer. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer and vice-versa.

The prescaler is not readable or writable.

The PSA and PS2:PS0 bits (OPTION\_REG<3:0>) determine the prescaler assignment and prescale ratio.

Clearing bit PSA will assign the prescaler to the Timer0 module. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4, ..., 1:256 are selectable.

Setting bit PSA will assign the prescaler to the Watchdog Timer (WDT). When the prescaler is assigned to the WDT, prescale values of 1:1, 1:2, ..., 1:128 are selectable.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT.

Note: Writing to TMR0 when the prescaler is assigned to Timer0 will clear the prescaler count, but will not change the prescaler assignment.

#### FIGURE 4-1: TIMER0 BLOCK DIAGRAM

#### 4.2.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on the fly" during program execution).

Note: To avoid an unintended device Reset, a specific instruction sequence (shown in the PIC<sup>®</sup> Mid-Range Reference Manual, DS33023) must be executed when changing the prescaler assignment from Timer0 to the WDT. This sequence must be followed even if the WDT is disabled.

### 4.3 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h. This overflow sets bit T0IF (INTCON<2>). The interrupt can be masked by clearing bit T0IE (INTCON<5>). Bit T0IF must be cleared in software by the Timer0 module Interrupt Service Routine before re-enabling this interrupt. The TMR0 interrupt cannot awaken the processor from Sleep since the timer is shut off during Sleep.

#### TABLE 4-1: REGISTERS ASSOCIATED WITH TIMER0

| Address | Name       | Bit 7  | Bit 6      | Bit 5    | Bit 4 | Bit 3                         | Bit 2 | Bit 1 | Bit 0     | Value on:<br>POR,<br>BOR | Value on all other Resets |

|---------|------------|--------|------------|----------|-------|-------------------------------|-------|-------|-----------|--------------------------|---------------------------|

| 01h     | TMR0       | Timer0 | Module's F | Register |       |                               |       |       |           | xxxx xxxx                | uuuu uuuu                 |

| 0Bh,8Bh | INTCON     | GIE    | PEIE       | TOIE     | INTE  | RBIE                          | T0IF  | INTF  | 0000 000x | 0000 000u                |                           |

| 81h     | OPTION_REG | RBPU   | INTEDG     | TOCS     | T0SE  | PSA PS2 PS1 PS0               |       |       |           | 1111 1111                | 1111 1111                 |

| 85h     | TRISA      |        | —          | (1)      | Bit 4 | PORTA Data Direction Register |       |       |           | 11 1111                  | 11 1111                   |

**Legend:** x = unknown, u = unchanged, — = unimplemented locations read as '0'. Shaded cells are not used by Timer0. **Note 1:** Reserved bit; Do Not Use.

### 6.1 Timer2 Operation

Timer2 can be used as the PWM time base for PWM mode of the CCP module.

The TMR2 register is readable and writable, and is cleared on any device Reset.

The input clock (Fosc/4) has a prescale option of 1:1, 1:4 or 1:16, selected by control bits T2CKPS1:T2CKPS0 (T2CON<1:0>).

The match output of TMR2 goes through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling inclusive) to generate a TMR2 interrupt (latched in flag bit TMR2IF, (PIR1<1>)).

The prescaler and postscaler counters are cleared when any of the following occurs:

- a write to the TMR2 register

- a write to the T2CON register

- any device Reset (Power-on Reset, MCLR Reset, Watchdog Timer Reset, or Brown-out Reset)

TMR2 is not cleared when T2CON is written.

#### 6.2 Timer2 Interrupt

The Timer2 module has an 8-bit period register PR2. Timer2 increments from 00h until it matches PR2 and then resets to 00h on the next increment cycle. PR2 is a readable and writable register. The PR2 register is initialized to FFh upon Reset.

| TABLE 6-1:         REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER |

|------------------------------------------------------------------------|

|------------------------------------------------------------------------|

| Address | Name   | Bit 7       | Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 |         |         |         |        |         |         |           | Value on<br>all other<br>Resets |

|---------|--------|-------------|-------------------------------------------------|---------|---------|---------|--------|---------|---------|-----------|---------------------------------|

| 0Bh,8Bh | INTCON | GIE         | PEIE                                            | TOIE    | INTE    | RBIE    | TOIF   | INTF    | RBIF    | 0000 000x | 0000 000u                       |

| 0Ch     | PIR1   | —           | ADIF                                            |         |         | _       | CCP1IF | TMR2IF  | TMR1IF  | -00000    | 0000 -000                       |

| 8Ch     | PIE1   | _           | ADIE                                            | _       | _       | _       | CCP1IE | TMR2IE  | TMR1IE  | -0000     | 0000 -000                       |

| 11h     | TMR2   | Timer2 Mod  | imer2 Module's Register                         |         |         |         |        |         |         |           | 0000 0000                       |

| 12h     | T2CON  | _           | TOUTPS3                                         | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000 | -000 0000                       |

| 92h     | PR2    | Timer2 Peri | Fimer2 Period Register                          |         |         |         |        |         |         |           | 1111 1111                       |

Legend: x = unknown, u = unchanged, — = unimplemented read as '0'. Shaded cells are not used by the Timer2 module.

## 7.0 CAPTURE/COMPARE/PWM (CCP) MODULE(S)

Each CCP (Capture/Compare/PWM) module contains a 16-bit register, which can operate as a 16-bit capture register, as a 16-bit compare register or as a PWM master/slave Duty Cycle register. Table 7-1 shows the timer resources of the CCP module modes.

Capture/Compare/PWM Register 1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. All are readable and writable.

### FIGURE 7-1: CCP1CON REGISTER (ADDRESS 17h)

U-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 DC1B1 DC1B0 CCP1M3 CCP1M2 CCP1M1 CCP1M0 R = Readable bit W = Writable bit bit7 bit0 U = Unimplemented bit, read as '0' -n = Value at POR Reset bit 7-6: Unimplemented: Read as '0' bit 5-4: DC1B1:DC1B0: PWM Least Significant bits Capture Mode: Unused Compare Mode: Unused PWM Mode: These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPR1L. bit 3-0: CCP1M3:CCP1M0: CCP1 Mode Select bits 0000 = Capture/Compare/PWM off (resets CCP1 module) 0100 = Capture mode, every falling edge 0101 = Capture mode, every rising edge 0110 = Capture mode, every 4th rising edge 0111 = Capture mode, every 16th rising edge 1000 = Compare mode, set output on match (CCP1IF bit is set) 1001 = Compare mode, clear output on match (CCP1IF bit is set) 1010 = Compare mode, generate software interrupt on match (CCP1IF bit is set, CCP1 pin is unaffected) 1011 = Compare mode, trigger special event (CCP1IF bit is set; CCP1 resets TMR1 and starts an A/D conversion (if A/D module is enabled)) 11xx = PWM mode

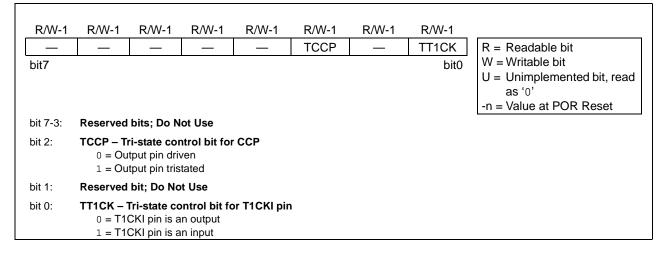

#### FIGURE 7-2: TRISCCP REGISTER (ADDRESS 87H)

Additional information on the CCP module is available in the PIC<sup>®</sup> Mid-Range Reference Manual, (DS33023).

## TABLE 7-1:CCP MODE – TIMER<br/>RESOURCE

| CCP Mode<br>Capture<br>Compare<br>PWM | Timer Resource |

|---------------------------------------|----------------|

|                                       | Timer1         |

| Compare                               | Timer1         |

| PWM                                   | Timer2         |

|                                       |                |

#### 7.3.3 SET-UP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- 2. Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- 3. Make the CCP1 pin an output by clearing the TRISCCP<2> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

- 5. Configure the CCP1 module for PWM operation.

#### TABLE 7-3:EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 20 MHz

| PWM Frequency              | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|----------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                  | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits)  | 10       | 10       | 10        | 8         | 7         | 5.5       |

| Address | Name    | Bit 7     | Bit 6                                | Bit 5         | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|---------|---------|-----------|--------------------------------------|---------------|---------|---------|--------|---------|---------|-------------------------|---------------------------------|

| 07h     | DATACCP | —         | _                                    |               |         |         | DCCP   |         | DT1CK   | xxxx xxxx               | xxxx xuxu                       |

| 0Bh,8Bh | INTCON  | GIE       | PEIE                                 | TOIE          | INTE    | RBIE    | TOIF   | INTF    | RBIF    | 0000 000x               | 0000 000u                       |

| 0Ch     | PIR1    | —         | ADIF                                 | _             | _       | _       | CCP1IF | TMR2IF  | TMR1IF  | -0000                   | -0000                           |

| 11h     | TMR2    | Timer2 Mc | Timer2 Module's Register             |               |         |         |        |         |         |                         | 0000 0000                       |

| 12h     | T2CON   | —         | TOUTPS3                              | TOUTPS2       | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000               | -000 0000                       |

| 15h     | CCPR1L  | Capture/C | Capture/Compare/PWM Register 1 (LSB) |               |         |         |        |         |         | xxxx xxxx               | uuuu uuuu                       |

| 16h     | CCPR1H  | Capture/C | ompare/PWI                           | VI Register 1 | (MSB)   |         |        |         |         | xxxx xxxx               | uuuu uuuu                       |

| 17h     | CCP1CON | —         | _                                    | DC1B1         | DC1B0   | CCP1M3  | CCP1M2 | CCP1M1  | CCP1M0  | 00 0000                 | 00 0000                         |

| 87h     | TRISCCP | —         |                                      | _             | _       | _       | TCCP   | _       | TT1CK   | xxxx x1x1               | xxxx x1x1                       |

| 8Ch     | PIE1    | —         | ADIE                                 | _             | _       | _       | CCP1IE | TMR2IE  | TMR1IE  | -0000                   | -0000                           |

| 92h     | PR2     | Timer2 Mc | dule's Period                        | d Register    |         |         |        |         |         | 1111 1111               | 1111 1111                       |

#### TABLE 7-4: REGISTERS ASSOCIATED WITH PWM AND TIMER2

Legend: x = unknown, u = unchanged, — = unimplemented read as '0'. Shaded cells are not used by PWM and Timer2.

### 7.4 CCP1 Module and PORTB Operation

When the CCP module is disabled, PORTB<3> operates as a normal I/O pin. When the CCP module is enabled, PORTB<3> operation is affected. Multiplexing details of the CCP1 module are shown on PORTB<3>, refer to Figure 3.6.

Table 7-5 below shows the effects of the CCP module operation on PORTB<3>

| CCP1<br>Module<br>Mode | Control Bits                     | CCP1 Module Operation                                                                                                                                            | PORTB<3> Operation                                                                                                                           |

|------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Off                    | CCP1CON =xx 0000                 | Off                                                                                                                                                              | PORTB<3> functions as normal I/O.                                                                                                            |

| Capture                | CCP1CON =xx 01xx<br>TRISCCP =1-x | The CCP1 module will capture an event<br>on the RB3/CCP1 pin which is driven by<br>an external circuit. The DCCP bit can<br>read the signal on the RB3/CCP1 pin. | PORTB<3> always reads '0' when<br>configured as input. If PORTB<3> is<br>configured as output, reading<br>PORTB<3> will read the data latch. |

|                        | CCP1CON =xx 01xx<br>TRISCCP =0-x | The CCP1 module will capture an event<br>on the RB3/CCP1 pin which is driven by<br>the DCCP bit. The DCCP bit can read<br>the signal on the RB3/CCP1 pin.        | Writing to PORTB<3> will always store the result in the data latch, but it does not drive the RB3/CCP1 pin.                                  |

| Compare                | CCP1CON =xx 10xx<br>TRISCCP =0-x | The CCP1 module produces an output<br>on the RB3/CCP1 pin when a compare<br>event occurs. The DCCP bit can read<br>the signal on the RB3/CCP1 pin.               |                                                                                                                                              |

| PWM                    | CCP1CON =xx 11xx<br>TRISCCP =0-x | The CCP1 module produces the PWM signal on the RB3/CCP1 pin. The DCCP bit can read the signal on the RB3/CCP1 pin.                                               |                                                                                                                                              |

TABLE 7-5: CCP1 MODULE AND PORTB OPERATION

#### 9.9 Power Control/Status Register (PCON)

The Power Control/Status Register, PCON has two bits.

Bit 0 is Brown-out Reset Status bit,  $\overline{\text{BOR}}$ . If the BODEN Configuration bit is set,  $\overline{\text{BOR}}$  is '1' on Power-on Reset. If the BODEN Configuration bit is clear,  $\overline{\text{BOR}}$  is unknown on Power-on Reset. The BOR Status bit is a "don't care" and is not necessarily predictable if the brown-out circuit is disabled (the BODEN Configuration bit is clear). BOR must then be set by the user and checked on subsequent Resets to see if it is clear, indicating a brown-out has occurred.

Bit 1 is  $\overrightarrow{\text{POR}}$  (Power-on Reset Status bit). It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

### TABLE 9-3:TIME-OUT IN VARIOUS SITUATIONS

| Oscillator Configuration | Power            | -up              | Brown-out        | Wake-up from<br>Sleep |  |

|--------------------------|------------------|------------------|------------------|-----------------------|--|

| Oscillator Configuration | <b>PWRTE</b> = 0 | <b>PWRTE</b> = 1 | Brown-out        |                       |  |

| XT, HS, LP               | 72 ms + 1024Tosc | 1024Tosc         | 72 ms + 1024Tosc | 1024Tosc              |  |

| RC                       | 72 ms            |                  | 72 ms            | —                     |  |

#### TABLE 9-4: STATUS BITS AND THEIR SIGNIFICANCE

| POR | BOR | TO | PD |                                                         |  |

|-----|-----|----|----|---------------------------------------------------------|--|

| 0   | x   | 1  | 1  | Power-on Reset                                          |  |

| 0   | x   | 0  | x  | Illegal, TO is set on POR                               |  |

| 0   | x   | x  | 0  | Illegal, PD is set on POR                               |  |

| 1   | 0   | 1  | 1  | Brown-out Reset                                         |  |

| 1   | 1   | 0  | 1  | VDT Reset                                               |  |

| 1   | 1   | 0  | 0  | NDT Wake-up                                             |  |

| 1   | 1   | u  | u  | MCLR Reset during normal operation                      |  |

| 1   | 1   | 1  | 0  | MCLR Reset during Sleep or interrupt wake-up from Sleep |  |

#### TABLE 9-5: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uu               |

| MCLR Reset during Sleep            | 000h                  | 0001 Ouuu          | uu               |

| WDT Reset                          | 000h                  | 0000 luuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 Ouuu          | uu               |

| Brown-out Reset                    | 000h                  | 0001 luuu          | u0               |

| Interrupt wake-up from Sleep       | PC + 1 <sup>(1)</sup> | uuul Ouuu          | uu               |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit read as '0'.

Note 1: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

| Register             | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset | Wake-up via WDT or<br>Interrupt |

|----------------------|------------------------------------|--------------------------|---------------------------------|

| W                    | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| INDF                 | N/A                                | N/A                      | N/A                             |

| TMR0                 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| PCL                  | 0000h                              | 0000h                    | PC + 1 <sup>(2)</sup>           |

| STATUS               | 0001 1xxx                          | 000q quuu <b>(3)</b>     | uuuq quuu <b>(3)</b>            |

| FSR                  | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| PORTA <sup>(4)</sup> | 0x 0000                            | xx xxxx                  | xu uuuu                         |

| PORTB <sup>(5)</sup> | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| DATACCP              | x-x                                | u-u                      | u-u                             |

| PCLATH               | 0 0000                             | 0 0000                   | u uuuu                          |

| INTCON               | 0000 -00x                          | 0000 -00u                | uuuu –uuu <b>(1)</b>            |

|                      | 0000                               | 0000                     | uuuu <b>(1)</b>                 |

| PIR1                 | -0 0000                            | -0 0000                  | -u uuuu <b>(1)</b>              |

| TMR1L                | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |

| TMR1H                | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |

| T1CON                | 00 0000                            | uu uuuu                  | uu uuuu                         |

| TMR2                 | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| T2CON                | -000 0000                          | -000 0000                | -uuu uuuu                       |

| CCPR1L               | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| CCPR1H               | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| CCP1CON              | 00 0000                            | 00 0000                  | uu uuuu                         |

| ADRES                | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| ADCON0               | 0000 00-0                          | 0000 00-0                | uuuu uu-u                       |

| OPTION_REG           | 1111 1111                          | 1111 1111                | uuuu uuuu                       |

| TRISA                | 11 1111                            | 11 1111                  | uu uuuu                         |

| TRISB                | 1111 1111                          | 1111 1111                | uuuu uuuu                       |

| TRISCCP              | xxxx x1x1                          | xxxx x1x1                | xxxx xuxu                       |

|                      | 0000                               | 0000                     | uuuu                            |

| PIE1                 | -0 0000                            | -0 0000                  | -u uuuu                         |

| PCON                 | 0q                                 | uq                       | uq                              |

| PR2                  | 1111 1111                          | 1111 1111                | 1111 1111                       |

| ADCON1               | 000                                | 000                      | uuu                             |

#### TABLE 9-6: INITIALIZATION CONDITIONS FOR ALL REGISTERS OF THE PIC16C712/716

**Legend:** u = unchanged, x = unknown, -= unimplemented bit, read as '0', q = value depends on condition

Note 1: One or more bits in INTCON and/or PIR1 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

**3:** See Table 9-5 for Reset value for specific condition.

4: On any device Reset, these pins are configured as inputs.

5: This is the value that will be in the port output latch.

#### TABLE 10-2: PIC16CXXX INSTRUCTION SET

| Mnemonic, |        | Description                  |       | 14-Bit Opcode |      |      |      | Status   | Notes |

|-----------|--------|------------------------------|-------|---------------|------|------|------|----------|-------|

| Operands  |        |                              |       | MSb           |      |      | LSb  | Affected |       |

| BYTE-ORIE | NTED   | FILE REGISTER OPERATIONS     |       |               |      |      |      |          |       |

| ADDWF     | f, d   | Add W and f                  | 1     | 00            | 0111 | dfff | ffff | C,DC,Z   | 1,2   |

| ANDWF     | f, d   | AND W with f                 | 1     | 00            | 0101 | dfff | ffff | Z        | 1,2   |

| CLRF      | f      | Clear f                      | 1     | 00            | 0001 | lfff | ffff | Z        | 2     |

| CLRW      | -      | Clear W                      | 1     | 00            | 0001 | 0000 | 0011 | Z        |       |

| COMF      | f, d   | Complement f                 | 1     | 00            | 1001 | dfff | ffff | Z        | 1,2   |

| DECF      | f, d   | Decrement f                  | 1     | 00            | 0011 | dfff | ffff | Z        | 1,2   |

| DECFSZ    | f, d   | Decrement f, Skip if 0       | 1(2)  | 00            | 1011 | dfff | ffff |          | 1,2,3 |

| INCF      | f, d   | Increment f                  | 1     | 00            | 1010 | dfff | ffff | Z        | 1,2   |

| INCFSZ    | f, d   | Increment f, Skip if 0       | 1(2)  | 00            | 1111 | dfff | ffff |          | 1,2,3 |

| IORWF     | f, d   | Inclusive OR W with f        | 1     | 00            | 0100 | dfff | ffff | Z        | 1,2   |

| MOVF      | f, d   | Move f                       | 1     | 00            | 1000 | dfff | ffff | Z        | 1,2   |

| MOVWF     | f      | Move W to f                  | 1     | 00            | 0000 | lfff | ffff |          |       |

| NOP       | -      | No Operation                 | 1     | 00            | 0000 | 0xx0 | 0000 |          |       |

| RLF       | f, d   | Rotate Left f through Carry  | 1     | 00            | 1101 | dfff | ffff | С        | 1,2   |

| RRF       | f, d   | Rotate Right f through Carry | 1     | 00            | 1100 | dfff | ffff | С        | 1,2   |

| SUBWF     | f, d   | Subtract W from f            | 1     | 00            | 0010 | dfff | ffff | C,DC,Z   | 1,2   |

| SWAPF     | f, d   | Swap nibbles in f            | 1     | 00            | 1110 | dfff | ffff |          | 1,2   |

| XORWF     | f, d   | Exclusive OR W with f        | 1     | 00            | 0110 | dfff | ffff | Z        | 1,2   |

| BIT-ORIEN | ed fil | E REGISTER OPERATIONS        |       | I             |      |      |      |          |       |

| BCF       | f, b   | Bit Clear f                  | 1     | 01            | 00bb | bfff | ffff |          | 1,2   |

| BSF       | f, b   | Bit Set f                    | 1     | 01            | 01bb | bfff | ffff |          | 1,2   |

| BTFSC     | f, b   | Bit Test f, Skip if Clear    | 1 (2) | 01            | 10bb | bfff | ffff |          | 3     |

| BTFSS     | f, b   | Bit Test f, Skip if Set      | 1 (2) | 01            | 11bb | bfff | ffff |          | 3     |

| LITERAL A | ND CO  | NTROL OPERATIONS             |       | 1             |      |      |      | I        |       |

| ADDLW     | k      | Add literal and W            | 1     | 11            | 111x | kkkk | kkkk | C,DC,Z   |       |

| ANDLW     | k      | AND literal with W           | 1     | 11            | 1001 | kkkk | kkkk | Z        |       |

| CALL      | k      | Call subroutine              | 2     | 10            | 0kkk | kkkk | kkkk |          |       |

| CLRWDT    | -      | Clear Watchdog Timer         | 1     | 00            | 0000 | 0110 | 0100 | TO,PD    |       |

| GOTO      | k      | Go to address                | 2     | 10            | 1kkk | kkkk | kkkk |          |       |

| IORLW     | k      | Inclusive OR literal with W  | 1     | 11            | 1000 | kkkk | kkkk | Z        |       |

| MOVLW     | k      | Move literal to W            | 1     | 11            | 00xx | kkkk | kkkk |          |       |

| RETFIE    | -      | Return from interrupt        | 2     | 00            | 0000 | 0000 | 1001 |          |       |

| RETLW     | k      | Return with literal in W     | 2     | 11            | 01xx | kkkk | kkkk |          |       |

| RETURN    | -      | Return from Subroutine       | 2     | 00            | 0000 | 0000 | 1000 |          |       |

| SLEEP     | -      | Go into standby mode         | 1     | 00            | 0000 | 0110 | 0011 | TO,PD    |       |

| SUBLW     | k      | Subtract W from literal      | 1     | 11            | 110x |      | kkkk | C,DC,Z   |       |

|           |        |                              | 1     |               |      |      |      | , -, -   |       |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

**3:** If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

## 12.4 AC (Timing) Characteristics

#### 12.4.1 TIMING PARAMETER SYMBOLOGY

The timing parameter symbols have been created using one of the following formats:

| 1. | TppS2ppS |

|----|----------|

|----|----------|

2. TppS

| 2. 1990 |                                       |     |                |  |  |  |

|---------|---------------------------------------|-----|----------------|--|--|--|

| т       |                                       |     |                |  |  |  |

| F       | Frequency                             | Т   | Time           |  |  |  |

| Lowerc  | ase letters (pp) and their meanings:  | -   |                |  |  |  |

| рр      |                                       |     |                |  |  |  |

| сс      | CCP1                                  | OSC | OSC1           |  |  |  |

| ck      | CLKOUT                                | rd  | RD             |  |  |  |

| CS      | CS                                    | rw  | RD or WR       |  |  |  |

| di      | SDI                                   | SC  | SCK            |  |  |  |

| do      | SDO                                   | SS  | SS             |  |  |  |

| dt      | Data in                               | tO  | TOCKI          |  |  |  |

| io      | I/O port                              | t1  | T1CKI          |  |  |  |

| mc      | MCLR                                  | wr  | WR             |  |  |  |

| Upperc  | Uppercase letters and their meanings: |     |                |  |  |  |

| S       |                                       |     |                |  |  |  |

| F       | Fall                                  | Р   | Period         |  |  |  |

| н       | High                                  | R   | Rise           |  |  |  |

| I       | Invalid (High-impedance)              | V   | Valid          |  |  |  |

| L       | Low                                   | Z   | High-impedance |  |  |  |

NOTES:

NOTES:

## THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

### **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support

NOTES: